RoHS

HALOGEN

FREE GREEN

# Vishay Semiconductors

# Proximity Sensor With VCSEL in Single Package, I<sup>2</sup>C Interface

#### **DESCRIPTION**

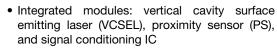

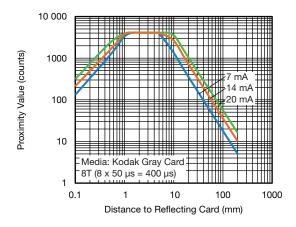

VCNL36687S integrates a proximity and a high power VCSEL (vertical-cavity surface-emitting laser) into one small package. It incorporates photodiodes, amplifiers, and analog to digital converting circuits into a single chip by CMOS process. PS programmable interrupt features of individual high and low thresholds offers the best utilization of resource and power saving on the microcontroller. With just 20 mA pulse current, the VCNL36687S can detect the Kodak Gray Card in a distance of 20 cm, where other sensors need 200 mA.

The 12 bits proximity sensing function uses an intelligent cancellation scheme, so that cross talk is eliminated effectivitely. To accelerate the PS response time, smart persistence prevents the misjudgment of proximity sensing but also allows for a fast response time. Active force mode, one time trigger by one instruction, is a feature offering more power saving.

PS functions are easily operated via the simple command format of  $I^2C$  (SMBus compatible) interface protocol. Operating voltage ranges from 1.65 V to 1.95 V. VCNL36687S is packaged in a lead (Pb)-free 8 pin molding package, which offers the best market-proven reliability quality.

### **APPLICATIONS**

- Proximity sensor especially for battery operated devices

- Mobile devices (e.g. smart phones, tablets) for touch screen locking, power saving etc.

- VR / AR headsets to detect if the headset has been put on or taken off

### **FEATURES**

- Package type: surface-mount

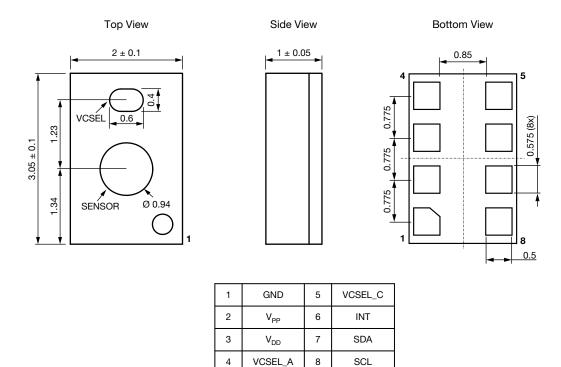

- Dimensions (L x W x H in mm): 3.05 x 2 x 1.0

- Smallest light hole opening design

- Supply voltage range V<sub>DD</sub>: 1.65 V to 1.95 V

- Communication via I2C interface

- I<sup>2</sup>C bus H-level range: 1.65 V to 3.6 V

- Floor life: 168 h, MSL 3, according to J-STD-020

- Material categorization: for definitions of compliance please see <a href="https://www.vishay.com/doc?99912">www.vishay.com/doc?99912</a>

### PROXIMITY FUNCTION

- Immunity to red glow (940 nm VCSEL)

- Programmable I<sub>VCSFI</sub> sink current

- Intelligent cancellation to reduce cross talk phenomenon

- Smart persistence scheme to reduce PS response time

- 12 bits PS output data

- Programmable interrupt function for PS with upper and lower thresholds

- Adjustable persistence to prevent false triggers for PS

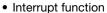

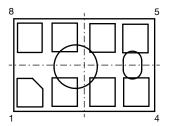

## **PIN DEFINITION**

| 1 | GND      | 5 | VCSEL_C |

|---|----------|---|---------|

| 2 | $V_{PP}$ | 6 | INT     |

| 3 | $V_{DD}$ | 7 | SDA     |

| 4 | VCSEL_A  | 8 | SCL     |

| PRODUCT SUMMARY |                            |                                   |                                              |                                                 |                          |                                                |  |

|-----------------|----------------------------|-----------------------------------|----------------------------------------------|-------------------------------------------------|--------------------------|------------------------------------------------|--|

| PART<br>NUMBER  | OPERATING<br>RANGE<br>(mm) | OPERATING<br>VOLTAGE RANGE<br>(V) | I <sup>2</sup> C BUS<br>VOLTAGE RANGE<br>(V) | VCSEL DRIVING<br>CURRENT <sup>(1)</sup><br>(mA) | OUTPUT<br>CODE           | ADC RESOLUTION<br>PROXIMITY /<br>AMBIENT LIGHT |  |

| VCNL36687S      | 200                        | 1.65 to 1.95                      | 1.65 to 3.6                                  | 20                                              | 12 bit, I <sup>2</sup> C | 12 bit / -                                     |  |

## Note

(1) Base on VCSEL period = 8 ms, 16 ms, 32 ms, and 64 ms

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

| ORDERING INFORMATION |               |                              |                           |  |  |  |

|----------------------|---------------|------------------------------|---------------------------|--|--|--|

| ORDERING CODE        | PACKAGING     | VOLUME (1)                   | REMARKS                   |  |  |  |

| VCNL36687S           | Tape and reel | MOQ: 2500 pcs, 2500 pcs/reel | 3.05 mm x 2.0 mm x 1.0 mm |  |  |  |

#### Note

(1) MOQ: minimum order quantity

| <b>ABSOLUTE MAXIMUM RATINGS</b> (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                |                  |      |      |      |  |  |

|----------------------------------------------------------------------------------------|----------------|------------------|------|------|------|--|--|

| PARAMETER                                                                              | TEST CONDITION | SYMBOL           | MIN. | MAX. | UNIT |  |  |

| Supply voltage                                                                         |                | $V_{DD}$         | 1.65 | 1.95 | V    |  |  |

| Operation temperature range                                                            |                | T <sub>amb</sub> | -40  | +85  | °C   |  |  |

| Storage temperature range                                                              |                | T <sub>stg</sub> | -40  | +85  | °C   |  |  |

| <b>BASIC CHARACTERISTICS</b> (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                                                                              |                      |      |      |      |       |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|------|------|------|-------|--|

| PARAMETER                                                                           | TEST CONDITION                                                               | SYMBOL               | MIN. | TYP. | MAX. | UNIT  |  |

| Cumply valtage                                                                      |                                                                              | $V_{DD}$             | 1.65 | 1.8  | 1.95 | V     |  |

| Supply voltage                                                                      |                                                                              | V <sub>PP</sub>      | 1.65 | 1.8  | 1.95 | V     |  |

| Supply current                                                                      | Excluding VCSEL driving                                                      | I <sub>DD</sub>      | -    | 160  | -    | μΑ    |  |

|                                                                                     | Light condition = dark;<br>V <sub>DD</sub> = 1.8 V, T <sub>amb</sub> = 25 °C | I <sub>DD</sub> (SD) | -    | 0.5  | -    | μΑ    |  |

| I <sup>2</sup> C supply voltage                                                     |                                                                              | V <sub>PULL UP</sub> | 1.65 | 1.8  | 3.6  | V     |  |

| I <sup>2</sup> C signal input, logic high                                           | V <sub>DD</sub> = 1.8 V                                                      | V <sub>IH</sub>      | 1.26 | -    | -    | V     |  |

| I <sup>2</sup> C signal input, logic low                                            | V <sub>DD</sub> = 1.8 V                                                      | V <sub>IL</sub>      | -    | -    | 0.73 | V     |  |

| Full PS counts                                                                      | 12-bit resolution                                                            |                      | -    | -    | 4095 | steps |  |

| Operating temperature                                                               |                                                                              | T <sub>amb</sub>     | -40  | -    | +85  | °C    |  |

| VCSEL driving voltage                                                               | (2)                                                                          |                      | 2.68 | -    | 4.8  | V     |  |

| VCSEL driving current                                                               | (1)                                                                          |                      | 7    | -    | 20   | mA    |  |

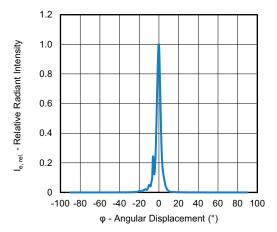

| PS view angle                                                                       | (3)                                                                          |                      | -    | 60   | =.   | 0     |  |

#### Notes

<sup>(2)</sup> Base on VCSEL current setting, VCSEL min. voltage need adjust, example as below

| ILD                                                             | 7 mA   | 11 mA  | 14 mA  | 17 mA  | 20 mA  |

|-----------------------------------------------------------------|--------|--------|--------|--------|--------|

| VCSEL current setting, V <sub>F</sub>                           | 2.08 V | 2.30 V | 2.43 V | 2.55 V | 2.69 V |

| VCSEL min. voltage, $V_{LD}$ ( $V_{LD} = V_F + 0.6 \text{ V}$ ) | 2.68 V | 2.90 V | 3.03 V | 3.15 V | 3.29 V |

$^{(3)}$  Shows total view angle of X-axis (X-axis: +10° to -50°; Y-axis:  $\pm$  45°)

<sup>(1)</sup> Base on VCSEL period = 8 ms, 16 ms, 32 ms, and 64 ms

INT <

SCL

SDA

Pin 8

Pin 7

**BLOCK DIAGRAM**

# Vishay Semiconductors

Pin 2 (n.c.)

## $V_{\rm DD}$ $V_{PP}$ Anode Pin 3 Pin 2 Pin 4 PS timing controller PS buffer VCSEL 🛨 🔀 DSP PS PD -o Cathode Pin 5 Oscillator Current driver Pin 6

I<sup>2</sup>C bus logic

control

Pin 1

GND

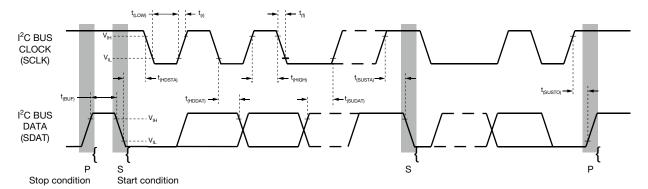

| I <sup>2</sup> C BUS TIMING CHARACTERISTICS (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                       |           |         |      |           |     |

|----------------------------------------------------------------------------------------------------|-----------------------|-----------|---------|------|-----------|-----|

| PARAMETER                                                                                          | SYMBOL                | STANDA    | RD MODE | FAST | UNIT      |     |

| PARAMETER                                                                                          | STINIBUL              | MIN. MAX. |         | MIN. | MIN. MAX. |     |

| Clock frequency                                                                                    | f <sub>(I2CCLK)</sub> | 10        | 100     | 10   | 400       | kHz |

| Bus free time between start and stop condition                                                     | t <sub>(BUF)</sub>    | 4.7       | -       | 1.3  | -         | μs  |

| Hold time after (repeated) start condition; after this period, the first clock is generated        | t <sub>(HDSTA)</sub>  | 4.0       | -       | 0.6  | -         | μs  |

| Repeated start condition setup time                                                                | t <sub>(SUSTA)</sub>  | 4.7       | -       | 0.6  | -         | μs  |

| Stop condition setup time                                                                          | t <sub>(SUSTO)</sub>  | 4.0       | -       | 0.6  | -         | μs  |

| Data hold time                                                                                     | t <sub>(HDDAT)</sub>  | -         | 3450    | -    | 900       | ns  |

| Data setup time                                                                                    | t <sub>(SUDAT)</sub>  | 250       | -       | 100  | -         | ns  |

| I <sup>2</sup> C clock (SCK) low period                                                            | t <sub>(LOW)</sub>    | 4.7       | -       | 1.3  | -         | μs  |

| I <sup>2</sup> C clock (SCK) high period                                                           | t <sub>(HIGH)</sub>   | 4.0       | -       | 0.6  | -         | μs  |

| Clock / data fall time                                                                             | t <sub>(f)</sub>      | =         | 300     | -    | 300       | ns  |

| Clock / data rise time                                                                             | t <sub>(r)</sub>      | -         | 1000    | -    | 300       | ns  |

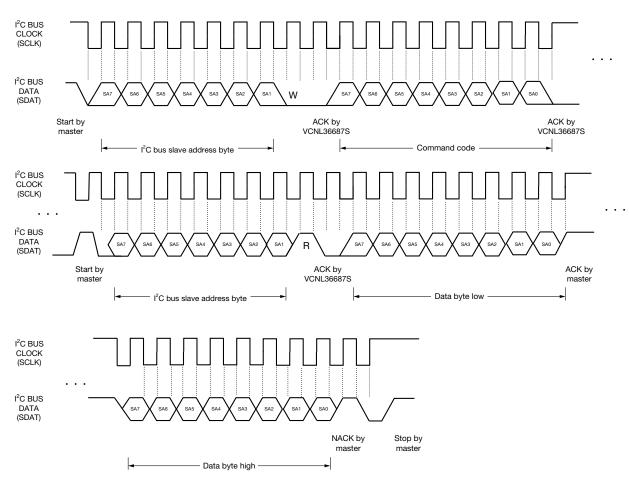

Fig. 1 - I<sup>2</sup>C Bus Timing Diagram

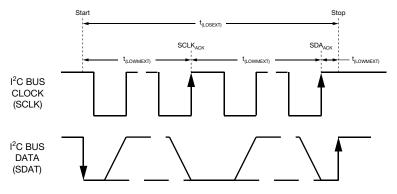

## PARAMETER TIMING INFORMATION

Fig. 2 - I<sup>2</sup>C Bus Timing for Sending Word Command Format

Fig. 3 - I<sup>2</sup>C Bus Timing for Receiving Word Command Format

# TYPICAL PERFORMANCE CHARACTERISTICS (T<sub>amb</sub> = 25 °C, unless otherwise specified)

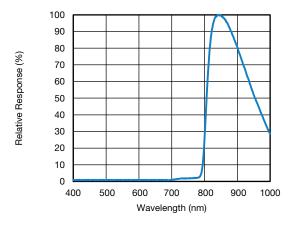

Fig. 4 - Normalized Spectral Response

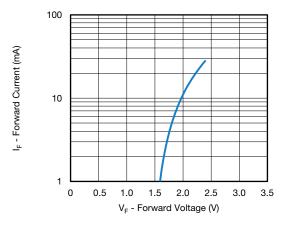

Fig. 5 - Forward Current vs. Forward Voltage

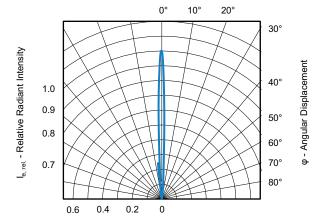

Fig. 6 - VCSEL Profile

VCNL36687S offers a high detection range already with very low pulse current of ≤ 20 mA.

Fig. 7 - Proximity Value vs. Distance; PS\_IT = 8T

For more information please study the application note "Designing the VCNL36687S Into an Application" (<a href="https://www.vishay.com/doc?84951">www.vishay.com/doc?84951</a>)

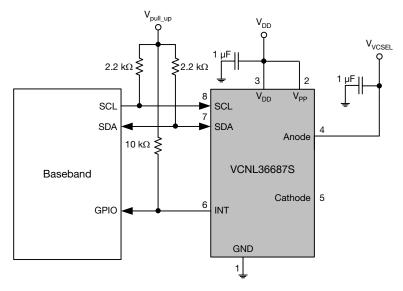

## **APPLICATION INFORMATION**

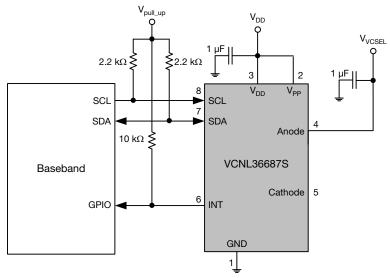

### Pin Connection with the Host

VCNL36687S integrates proximity sensor and VCSEL all together with an I<sup>2</sup>C interface. It is easy for the baseband (CPU) to access PS output data via I<sup>2</sup>C interface without additional software algorithms. The hardware schematic is shown in the following diagram.

Two additional capacitors in the circuit can be used for the following purposes: (1) the 1  $\mu$ F capacitor near the V<sub>DD</sub> pin is used for power supply noise rejection, (2) the 1  $\mu$ F capacitor is used to prevent the VCSEL voltage from instantly dropping when the VCSEL is turned on, and (3) 2.2  $k\Omega$  is suitable for the pull up resistor of  $l^2$ C except for the 10  $k\Omega$  applied on the INT pin.

Fig. 8 - Hardware Pin Connection Diagram

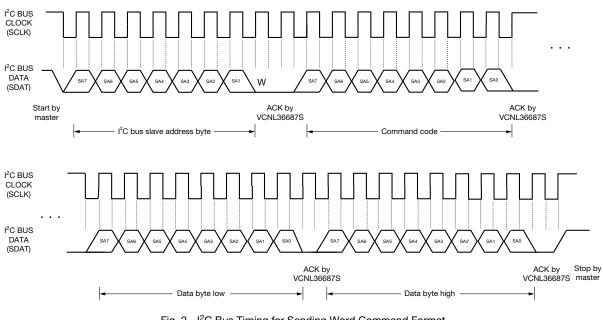

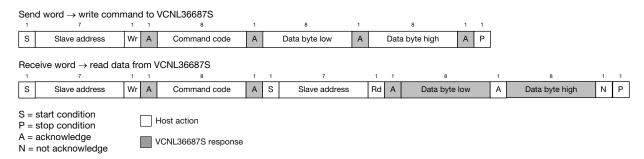

### **Digital Interface**

VCNL36687S applies single slave address 0x60 (HEX) of 7-bit addressing following I<sup>2</sup>C protocol. All operations can be controlled by the command register. The simple command structure helps users easily program the operation setting and latch the light data from VCNL36687S. As Fig. 9 shows, VCNL36687S's I<sup>2</sup>C command format is simple for read and write operations between VCNL36687S and the host. The white sections indicate host activity and the gray sections indicate VCNL36687S's acknowledgement of the host access activity. Write word and read word protocol is suitable for accessing registers particularly for 12-bit PS data. Interrupt can be cleared by reading data out from register: INT\_Flag. All command codes should follow read word and write word protocols.

Fig. 9 - Write Word and Read Word Protocol

## **Function Description**

For proximity sensor function, VCNL36687S supports different kinds of mechanical designs to achieve the best proximity detection performance for any color of object with more flexibility. The basic PS function settings, such as period, persistence, INT, and shut down are handled by the register: PS\_CONF1. Period controls the PS response time. Integration time represents the duration of the energy being received. The Interrupt is asserted when the PS detection levels over the high threshold level setting (register: PS\_THDH) or lower than low threshold (register: PS\_THDL). If the Interrupt function is enabled, the host reads the PS output data from VCNL36687S that saves host loading from periodically reading PS data. More than that, INT flag (register: INT\_Flag) indicates the behavior of INT triggered under different conditions. PS persistence (PS\_PERS) sets up the PS INT asserted conditions as long as the PS output value continually exceeds the threshold level. The intelligent cancellation level can be set on register: PS\_CANC to reduce the cross talk phenomenon.

VCNL36687S also supports easy use of proximity detection logic output mode that outputs just high / low levels saving loading from the host. Normal operation mode or proximity detection logic output mode can be selected on the register: PS\_MS. A smart persistence is provided to get faster PS response time and prevent false trigger for PS. Descriptions of each slave address operation are shown in Table 1.

| TABLE 1         | - COMMA                 | ND CODE A        | ND R | EGISTER          | DESCRIPTION                                                              |

|-----------------|-------------------------|------------------|------|------------------|--------------------------------------------------------------------------|

| COMMAND<br>CODE | DATE BYTE<br>LOW / HIGH | REGISTER<br>NAME | R/W  | DEFAULT<br>VALUE | FUNCTION DESCRIPTION                                                     |

| 0x03            | L                       | PS_CONF1         | R/W  | 0x01             | PS period, persistence, INT and smart persistence and function selection |

| 0.00            | Н                       | PS_CONF2         | R/W  | 0x00             | PS IT and start selection                                                |

| 0x04            | L                       | PS_CONF3         | R/W  | 0x00             | PS active force mode                                                     |

| 0X04            | Н                       | PS_CONF4         | R/W  | 0x00             | PS VCSEL current selection                                               |

| 0x05            | L                       | PS_THDL_L        | R/W  | 0x00             | PS low interrupt threshold setting LSB byte                              |

| 0x05            | Н                       | PS_THDL_M        | R/W  | 0x00             | PS low interrupt threshold setting MSB byte                              |

| 0x06            | L                       | PS_THDH_L        | R/W  | 0x00             | PS high interrupt threshold setting LSB byte                             |

| UXUG            | Н                       | PS_THDH_M        | R/W  | 0x00             | PS high interrupt threshold setting MSB byte                             |

| 0x07            | L                       | PS_CANC_L        | R/W  | 0x00             | PS cancellation level setting                                            |

| UXU7            | Н                       | PS_CANC_M        | R/W  | 0x00             | PS cancellation level setting                                            |

| 0x08            | L                       | PS_CONF5         | R/W  | 0x00             | PS power on start setting                                                |

| UXUO            | Н                       | Reserved         | R/W  | 0x00             | Reserved                                                                 |

| 0xF2            | L                       | PS_Data_L        | R    | 0x00             | PS LSB output data                                                       |

| UXFZ            | Н                       | PS_Data_M        | R    | 0x00             | PS MSB output data                                                       |

| 0xF3            | L                       | Reserved         | R    | 0x00             | Reserved                                                                 |

| UXFO            | Н                       | INT_Flag         | R    | 0x00             | PS interrupt flags                                                       |

| 0xF4            | L                       | ID_L             | R    | 0x88             | Device ID LSB                                                            |

| UXI 4           | Н                       | ID_M             | R    | 0x05             | Device ID MSB                                                            |

#### Note

· All of reserved register are used for internal test. Please keep as default setting

# **Command Register Format**

VCNL36687S provides an 8-bit command register for PS controlling independently. The description of each command format is shown in the following tables.

| TABLE 2 - REG | TABLE 2 - REGISTER: PS_CONF1 DESCRIPTION |                                                                                                                                  |  |  |  |  |

|---------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| REGISTER NAME |                                          | COMMAND CODE: 0x03_L (0x00 DATA BYTE LOW)                                                                                        |  |  |  |  |

| Command       | Bit                                      | Description                                                                                                                      |  |  |  |  |

| PS_Period     | 7:6                                      | (0 : 0) = 8 ms, (0 : 1) = 16 ms, (1 : 0) = 32 ms, (1 : 1) = 64 ms<br>PS sample period setting                                    |  |  |  |  |

| PS_PERS       | 5:4                                      | (0:0) = 1, (0:1) = 2, (1:0) = 3, (1:1) = 4<br>PS interrupt persistence setting                                                   |  |  |  |  |

| PS_INT        | 3:2                                      | (0 : 0) = interrupt disable, (0 : 1) = interrupt disable, (1 : 0) = interrupt enable, (1 : 1) = trigger by logic high / low mode |  |  |  |  |

| PS_SMART_PERS | 1                                        | 0 = disable ; 1 = enable PS smart persistence                                                                                    |  |  |  |  |

| PS_SD         | 0                                        | 0 = PS power on, 1 = PS shut down, default = 1                                                                                   |  |  |  |  |

| TABLE 3 - RE | TABLE 3 - REGISTER: PS_CONF2 DESCRIPTION |                                                                       |  |  |  |  |

|--------------|------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

|              |                                          | COMMAND CODE: 0x03_H (0x03 DATA BYTE HIGH)                            |  |  |  |  |

| Command      | Bit                                      | Description                                                           |  |  |  |  |

| PS_IT        | 7:6                                      | (0:0) = 1T, (0:1) = 2T, (1:0) = 4T, (1:1) = 8T                        |  |  |  |  |

| PS_MPS       | 5:4                                      | (0:0) = 1, (0:1) = 2, (1:0) = 4, (1:1) = 8;<br>PS multi-pulse setting |  |  |  |  |

| PS_ITB       | 3                                        | 0 = 25 μs, 1 = 50 μs, PS IT bank setting                              |  |  |  |  |

| Reserved     | 2:0                                      | Default = 0                                                           |  |  |  |  |

| TABLE 4 - RE | TABLE 4 - REGISTER: PS_CONF3 DESCRIPTION |                                                                                                                                                                                   |  |  |  |

|--------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|              |                                          | COMMAND CODE: 0x04_L (0x04 DATA BYTE LOW)                                                                                                                                         |  |  |  |

| Register     | Bit                                      | Description                                                                                                                                                                       |  |  |  |

| Reserved     | 7                                        | 0                                                                                                                                                                                 |  |  |  |

| PS_AF        | 6                                        | 0 = auto mode; 1 = force mode                                                                                                                                                     |  |  |  |

| PS_FOR_Trig  | 5                                        | 0 = no PS active force mode trigger, 1 = trigger one time cycle VCNL36687S output one cycle data every time host writes in "1" to sensor. The state returns to "0" automatically. |  |  |  |

| Reserved     | 4                                        | 0                                                                                                                                                                                 |  |  |  |

| Reserved     | 3:0                                      | (0:0:0:0)                                                                                                                                                                         |  |  |  |

| TABLE 5 - RE | TABLE 5 - REGISTER: PS_CONF4 DESCRIPTION |                                                                                                                                                                             |  |  |  |  |

|--------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              |                                          | COMMAND CODE: 0x04_H (0x04 DATA BYTE HIGH)                                                                                                                                  |  |  |  |  |

| Register     | Bit                                      | Description                                                                                                                                                                 |  |  |  |  |

| PS_SC_EN     | 7                                        | 0 = turn off sunlight cancel; 1 = turn on sunlight cancel; PS sunlight cancel function enable setting                                                                       |  |  |  |  |

| PS_SC_CUR    | 6:5                                      | $(0:0) = 1 \times \text{typical sunlight cancel current}, (0:1) = 2 \times \text{typical sunlight cancel current}, (1:0) = 4 \times \text{typical sunlight cancel current}$ |  |  |  |  |

| PS_HD        | 4                                        | 0 = PS output is 12 bits, 1 = PS output is 16 bits                                                                                                                          |  |  |  |  |

| Reserved     | 3                                        | 0                                                                                                                                                                           |  |  |  |  |

| VCSEL_I      | 2:0                                      | (0 : 0 : 0) = 7 mA; (0 : 0 : 1) = 11 mA; (0 : 1 : 0) = 14 mA; (0 : 1 : 1) = 17 mA; (1 : 0 : 0) = 20 mA; VCSEL current selection setting                                     |  |  |  |  |

| TABLE 6 - REGISTER: PS_THDL_L AND PS_THDL_M DESCRIPTION |                                                                            |                                                           |  |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

|                                                         | COMMAND CODE: 0x05_L (0x05 DATA BYTE LOW) AND 0x05_H (0x05 DATA BYTE HIGH) |                                                           |  |  |  |  |  |  |

| Command                                                 | Bit                                                                        | Description                                               |  |  |  |  |  |  |

| PS_THDL_L                                               | 7:0                                                                        | 0x00 to 0xFF, PS interrupt low threshold setting_LSB byte |  |  |  |  |  |  |

| PS_THDL_M                                               | 7:0                                                                        | 0x00 to 0x0F, PS interrupt low threshold setting_MSB byte |  |  |  |  |  |  |

| TABLE 7 - REGISTER: PS_THDL_L AND PS_THDL_M DESCRIPTION |                                                                            |                                                            |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

|                                                         | COMMAND CODE: 0x06_L (0x06 DATA BYTE LOW) AND 0x06_H (0x06 DATA BYTE HIGH) |                                                            |  |  |  |  |  |

| Command                                                 | Bit                                                                        | Description                                                |  |  |  |  |  |

| PS_THDH_L                                               | 7:0                                                                        | 0x00 to 0xFF, PS interrupt high threshold setting_LSB byte |  |  |  |  |  |

| PS_THDH_M                                               | 7:0                                                                        | 0x00 to 0x0F, PS interrupt high threshold setting_MSB byte |  |  |  |  |  |

| TABLE 8 - REGISTER: PS_CANC_L AND PS_CANC_M DESCRIPTION                    |     |                                                          |  |  |  |  |

|----------------------------------------------------------------------------|-----|----------------------------------------------------------|--|--|--|--|

| COMMAND CODE: 0x07_L (0x07 DATA BYTE LOW) AND 0x07_H (0x07 DATA BYTE HIGH) |     |                                                          |  |  |  |  |

| Command                                                                    | Bit | Description                                              |  |  |  |  |

| PS_CANC_L                                                                  | 7:0 | 0x00 to 0xFF, PS cancellation level setting_LSB byte     |  |  |  |  |

| PS_CANC_M                                                                  | 7:0 | 0x00 to 0x0F, PS MSB cancellation level setting_MSB byte |  |  |  |  |

| TABLE 9 - REGISTER: PS_CONF5 DESCRIPTION |                                                                            |                                      |  |  |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------|--------------------------------------|--|--|--|--|--|

|                                          | COMMAND CODE: 0x08_L (0x08 DATA BYTE LOW) AND 0x08_H (0x08 DATA BYTE HIGH) |                                      |  |  |  |  |  |

| Register                                 | Bit                                                                        | Description                          |  |  |  |  |  |

| Reserved _L                              | 7:1                                                                        | Reserved                             |  |  |  |  |  |

| POR_S                                    | 0                                                                          | When use PS function, must write "1" |  |  |  |  |  |

| Reserved_M                               | 7:0                                                                        | Reserved                             |  |  |  |  |  |

| TABLE 10 - READ OUT REGISTER DESCRIPTION |                                      |                   |                                                                                                                                                                                                         |  |  |  |  |

|------------------------------------------|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Register                                 | Command Code                         | Bit               | Description                                                                                                                                                                                             |  |  |  |  |

| PS_Data_L                                | 0xF2_L (0xF2 data byte low)          | 7:0               | 0x00 to 0xFF, PS LSB output data                                                                                                                                                                        |  |  |  |  |

| PS_Data_M                                | 0xF2_H (0xF2 data byte high)         | 7:0               | 3:0 PS output code 6:4 reserved 7:"0" Normal output, "1" enter sunlight protection mode PS_Data_L= 00000000 PS_Data_M= 1000000                                                                          |  |  |  |  |

| Reserved                                 | 0xF3_L (0xF3 data byte low)          | 7:0               | Default = 0x00                                                                                                                                                                                          |  |  |  |  |

| INT_Flag                                 | NT_Flag 0xF3_H (0xF3 data byte high) |                   | Reserved Reserved Reserved PS_SPFLAG, PS entering protection mode Reserved Reserved Reserved PS_IF_CLOSE, PS rises above PS_THDH INT trigger event PS_IF_AWAY, PS drops below PS_THDL INT trigger event |  |  |  |  |

| ID_L                                     | 0xF4_L (F4H data byte low)           | 7:0               | 88H for MP version sample<br>Device ID LSB byte                                                                                                                                                         |  |  |  |  |

| ID_M                                     | 0xF4_H (F4H data byte high)          | 7:6<br>5:4<br>3:0 | (0 : 0)<br>(0 : 0) slave address = 0x60<br>Version code (0 : 1 : 0 : 1); device ID MSB byte                                                                                                             |  |  |  |  |

## Initialization

VCNL36687S includes default values for each register. As long as power is on, it is ready to be controlled by host via I<sup>2</sup>C bus.

## **Threshold Window Setting**

- Programmable PS Threshold

VCNL36687S provides both high and low thresholds 12-bit data setting for PS (register: PS\_THDL, PS\_THDH).

- PS Persistence

The PS persistence function (PS\_PERS, 1\2\3\4) helps to avoid false trigger of the PS INT. For example, if PS\_PERS = 3 times, the PS INT will not be asserted unless the PS value is greater than the PS threshold (PS\_THDH) value for three periods of time continuously

• PS Active Force Mode

An extreme power saving way to use PS is to apply PS active force (register: PS\_CONF3 command: PS\_AF = 1) mode. Anytime host would like to read out just one of PS data, write in "1" at register: PS\_CONF3 command: PS\_FOR\_Trig. Without commands placed, there is no PS data output. VCNL36687S stays in standby mode constantly

PS Detection Object

Any color of object is detectable by VCNL36687S

#### **Data Access**

For PS data reading, it has to apply two bytes. One byte is for LSB, and the other byte is for MSB (4 bits) as shown in Table 11.

| TABLE 1  | TABLE 11 - VCNL36687S 12-BIT PS DATA FORMAT |                                                |                      |             |    |      |       |   |   |   |   |      |       |   |   |   |

|----------|---------------------------------------------|------------------------------------------------|----------------------|-------------|----|------|-------|---|---|---|---|------|-------|---|---|---|

|          | VCNL36687S                                  |                                                |                      |             |    |      |       |   |   |   |   |      |       |   |   |   |

| Bit      | 15                                          | 14                                             | 13                   | 12          | 11 | 10   | 9     | 8 | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

| Register | "1" er<br>m                                 | : "0" nor<br>nter sunli<br>node, PS<br>0000000 | ight prot<br>Soutput | ection<br>= |    | PS_C | )ataM |   |   |   |   | PS_[ | DataL |   |   |   |

## **Intelligent Cancellation**

VCNL36687S provides an intelligent cancellation method to reduce cross talk for the proximity sensor. The output data will be subtracted by the input value stored in register: PS\_CANC.

### Interruption (INT)

VCNL36687S has PS interrupt feature operated by a single pin "INT". The purpose of the interrupt feature is to actively inform the host once INT has been asserted. With the interrupt function applied, the host does not need to be constantly pulling data from the sensor, but to read data from the sensor while receiving interrupt request from the sensor.

## Interruption Flag

Register: INT\_Flag represents all of interrupt trigger status for PS. Any flag value changes from "0" to "1" state, the level of INT pin will be pulles low. As long as host reads INT\_Flag data, the bit will change from "1" state to "0" state after reading out, the INT level will be returned to high afterwards.

## PROXIMITY DETECTION LOGIC OUTPUT MODE

VCNL36687S provides a proximity detection logic output mode that uses INT pin (pin 6) as a proximity detection logic high / low output (register: PS\_INT = 3). When this mode is selected, the PS output (pin 6; INT/P<sub>OUT</sub>) is pulled low when an object is closing to be detected and returned to level high when the object moves away. Register: PS\_THDH\L defines how sensitive PS detection is.

### PROXIMITY DETECTION HYSTERESIS

A PS detection hysteresis is important that keeps PS state in a certain range of detection distance. For example, PS INT asserts when PS value over PS\_THDH. Host switches off panel backlight and then clears INT. When PS value is less than PS\_THDL, Host switches on panel backlight. Any PS value lower than PS\_THDH or higher than PS\_THDL, PS INT will not be asserted. Host does keep the same state.

# **PACKAGE INFORMATION**

Fig. 10 - VCNL36687S Package Dimensions

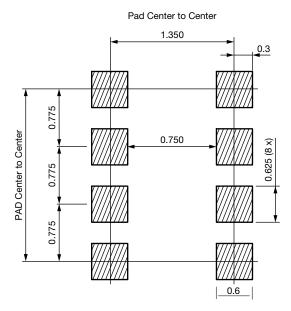

# **LAYOUT PAD INFORMATION**

Fig. 11 - VCNL36687S PCB Layout Footprint

# **APPLICATION CIRCUIT BLOCK REFERENCE**

Fig. 12 - VCNL36687S Application Circuit (normal operation with interrupt function)

| RECOMMENDED STORAGE AND REBAKING CONDITIONS |                                                          |   |     |        |  |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------|---|-----|--------|--|--|--|--|--|

| PARAMETER                                   | ARAMETER CONDITIONS MIN. MAX. UN                         |   |     |        |  |  |  |  |  |

| Storage temperature                         |                                                          | 5 | 50  | °C     |  |  |  |  |  |

| Relative humidity                           |                                                          | - | 60  | %      |  |  |  |  |  |

| Open time                                   |                                                          | - | 168 | h      |  |  |  |  |  |

| Total time                                  | From the date code on the aluminized envelope (unopened) | - | 12  | months |  |  |  |  |  |

| Rebaking                                    | Tape and reel: 60 °C                                     | - | 22  | h      |  |  |  |  |  |

|                                             | Tube: 60 °C                                              | - | 22  | h      |  |  |  |  |  |

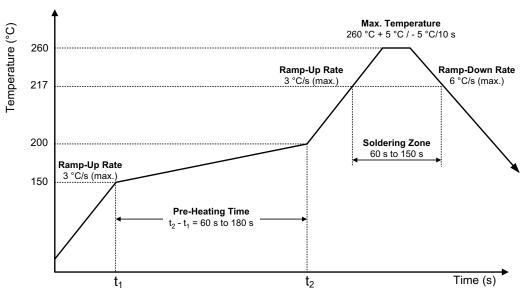

## RECOMMENDED INFRARED REFLOW

Soldering conditions which are based on J-STD-020 C

| IR REFLOW PROFILE CONDITION                |            |                                       |               |  |  |  |  |  |

|--------------------------------------------|------------|---------------------------------------|---------------|--|--|--|--|--|

| PARAMETER                                  | CONDITIONS | TEMPERATURE                           | TIME          |  |  |  |  |  |

| Peak temperature                           |            | 260 °C + 5 °C / - 5 °C (max.: 265 °C) | 10 s          |  |  |  |  |  |

| Preheat temperature range and timing       |            | 150 °C to 200 °C                      | 60 s to 180 s |  |  |  |  |  |

| Timing within 5 °C to peak temperature     |            | -                                     | 10 s to 30 s  |  |  |  |  |  |

| Timing maintained above temperature / time |            | 217 °C                                | 60 s to 150 s |  |  |  |  |  |

| Timing from 25 °C to peak temperature      |            | -                                     | 8 min (max.)  |  |  |  |  |  |

| Ramp-up rate                               |            | 3 °C/s (max.)                         | -             |  |  |  |  |  |

| Ramp-down rate                             |            | 6 °C/s (max.)                         | -             |  |  |  |  |  |

Recommend Normal Solder Reflow is 235 °C to 265 °C

Fig. 13 - VCNL36687S Solder Reflow Profile Chart

# RECOMMENDED IRON TIP SOLDERING CONDITION AND WARNING HANDLING

- 1. Solder the device with the following conditions:

- 1.1. Soldering temperature: 400 °C (max.)

- 1.2. Soldering time: 3 s (max.)

- 2. If the temperature of the method portion rises in addition to the residual stress between the leads, the possibility that an open or short circuit occurs due to the deformation or destruction of the resin increases

- 3. The following methods: VPS and wave soldering, have not been suggested for the component assembly

- 4. Cleaning method conditions:

- 4.1. Solvent: methyl alcohol, ethyl alcohol, isopropyl alcohol

- 4.2. Solvent temperature < 45 °C (max.)

- 4.3. Time: 3 min (min.)

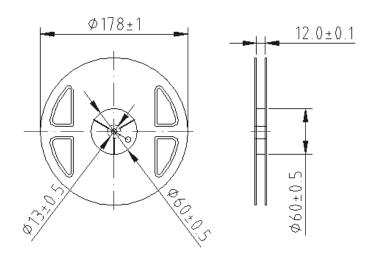

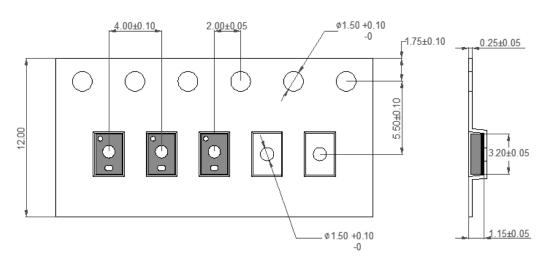

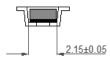

# TAPE PACKAGING INFORMATION in millimeters

# **Legal Disclaimer Notice**

Vishay

# **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.