## PFM™ in a VIA Package AC-DC Converter PFM4914xB6M24D0yzz CSS us C €

## Isolated AC-DC Converter with PFC

#### **Features & Benefits**

- Universal input (85 to 264V<sub>AC</sub>)

- 24V<sub>OUT</sub>, regulated, isolated

- 400W maximum power

- High efficiency

- Built-in EMI filtering

- Chassis mount or board mount packaging options

- Always-on, self-protecting converter control architecture

- SELV Output

- Two temperature grades including operation to -40°C

- Robust package

- Versatile thermal management

- Safe and reliable secondary-side energy storage

- High MTBF

- 127W/in<sup>3</sup> power density

- 4914 package

- External rectification and transient protection required

#### **Typical Applications**

- Small cell base stations

- Telecom switching equipment

- LED lighting

- Industrial power systems

| Product Ratings      |                                 |  |  |  |  |

|----------------------|---------------------------------|--|--|--|--|

| $V_{IN} = 85 - 264V$ | $P_{OUT} = up \text{ to } 400W$ |  |  |  |  |

| $V_{OUT} = 24V$      | I <sub>OUT</sub> = 16.67A       |  |  |  |  |

#### **Product Description**

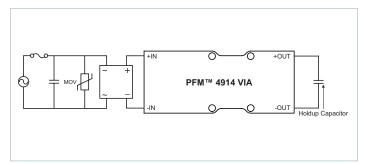

The PFM in a VIA package is a highly advanced 400W AC-DC converter operating from a rectified universal AC input which delivers an isolated and regulated Safety Extra Low Voltage (SELV) 24V secondary output.

This unique, ultra-low profile module incorporates AC-DC conversion, integrated filtering and transient surge protection in a chassis mount or PCB mount form factor.

The PFM in a VIA package enables a versatile two-sided thermal strategy which greatly simplifies thermal design challenges.

When combined with downstream Vicor DC-DC conversion components and regulators, the PFM in a VIA package allows the Power Design Engineer to employ a simple, low-profile design which will differentiate his end-system without compromising on cost or performance metrics.

#### **Part Ordering Information**

| Product<br>Function             | Package<br>Length        | Package<br>Width        | Package<br>Type                  | Input<br>Voltage   | Range<br>Ratio | Output<br>Voltage<br>(Range) | Max<br>Output<br>Current             | Product Grade | Optio                                       | n Field |

|---------------------------------|--------------------------|-------------------------|----------------------------------|--------------------|----------------|------------------------------|--------------------------------------|---------------|---------------------------------------------|---------|

| PFM                             | 49                       | 14                      | х                                | B6                 | М              | 24                           | D0                                   | У             | Z                                           | Z       |

| PFM =<br>Power Factor<br>Module | Length in<br>Inches x 10 | Width in<br>Inches x 10 | B = Board VIA<br>V = Chassis VIA | Internal Reference |                |                              | C = -20 to 100°C<br>T = -40 to 100°C | 04 = Short P  | s/Always On<br>in/Always On<br>in/Always On |         |

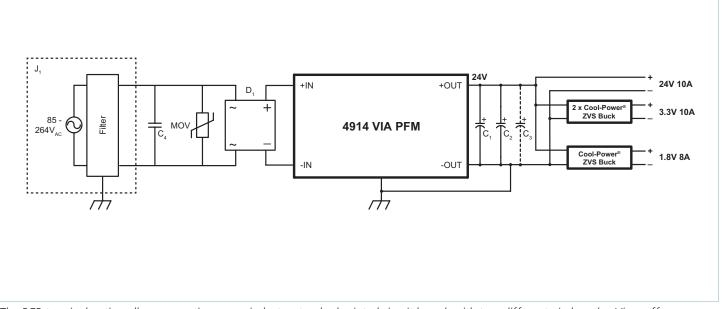

#### **Typical PCB Mount Applications**

The PCB terminal option allows mounting on an industry standard printed circuit board, with two different pin lengths. Vicor offers a variety of downstream DC-DC converters driven by the 24V output of the PFM in a VIA package. The 24V output is usable directly by loads that are tolerant of the PFC line ripple, such as fans, motors, relays, and some types of lighting. Use downstream DC-DC Point of Load converters where more precise regulation is required.

| Parts List for Typical PCB Mount Applications |                                                                                                       |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| J1                                            | Delta 06AR2 EMI Filter Entry Module, C14 6A 250V 5 x 20mm fuseholder                                  |  |  |  |  |

| F1 (mount in J1)                              | Littelfuse 0216008.MXP 8A 250V <sub>AC</sub> 5 x 20mm holder                                          |  |  |  |  |

| D1                                            | Fairchild GBPC1210W 12A 1000V PTH                                                                     |  |  |  |  |

|                                               | Nichicon UVR1V153MRD 15,000µF 35V 4.3A 25 x 50mm bent 90°, x 3pcs<br>or                               |  |  |  |  |

| C1, C2, (C3)                                  | CDE 380LX153M035A022 15,000µF 35V 5.6A 35 x 30mm snap in, x 3pcs<br>or                                |  |  |  |  |

|                                               | <b>Sic Safco</b> Cubisic LP A712062 22,000µF 35V 5.8A 45 x 75 x 12mm rectangular, x 2pcs<br><b>or</b> |  |  |  |  |

|                                               | <b>CDE</b> MLPE1566 22,000uF 35V 8.4A 45 x 76 x 12.5mm x 2pcs.                                        |  |  |  |  |

| C4                                            | <b>Panasonic</b> ECQ-U2A474ML 0.47µF 275V                                                             |  |  |  |  |

| MOV                                           | Littelfuse TMOV20RP300E VARISTOR 10kA 300V 250 J 20mm                                                 |  |  |  |  |

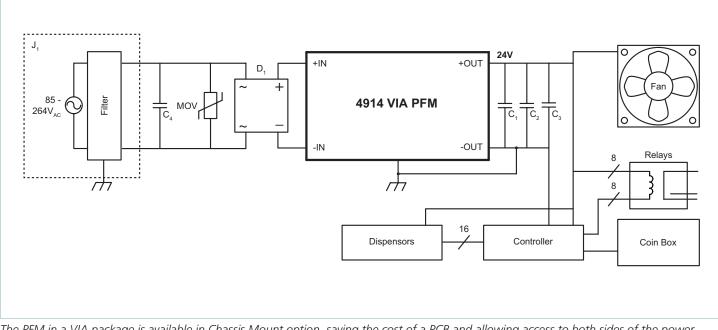

#### **Typical Chassis Mount Applications**

The PFM in a VIA package is available in Chassis Mount option, saving the cost of a PCB and allowing access to both sides of the power supply for cooling. The parts list below minimizes the number of interconnects required between necessary components, and selects components with terminals traditionally used for point to point chassis wiring.

| Parts List for Typical Chassis Mount Applications |                                                                       |  |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| J1                                                | Delta 06AR2 EMI Filter Entry Module, C14 6A 250V 5 x 20mm fuseholder  |  |  |  |  |

| F1 (mount in J1)                                  | Littelfuse 0216008.MXP 8A 250V <sub>AC</sub> 5 x 20mm holder          |  |  |  |  |

| D1                                                | Fairchild GBPC1210FS 12A 1000V 0.25" QC TERMINAL                      |  |  |  |  |

| C1, C2, C3                                        | Nichicon LNT1V153MSE 15,000μF 35V 5.1A 35 x 83mm screw terminal<br>or |  |  |  |  |

| C1                                                | Kemet ALS30A473KE040 47,000µF 40V 14.2A 51 x 84mm screw terminal      |  |  |  |  |

| C4                                                | <b>Panasonic</b> ECQ-U2A474ML 0.47µF 275V                             |  |  |  |  |

| MOV                                               | Littelfuse TMOV20RP300E VARISTOR 10kA 300V 250 J 20mm                 |  |  |  |  |

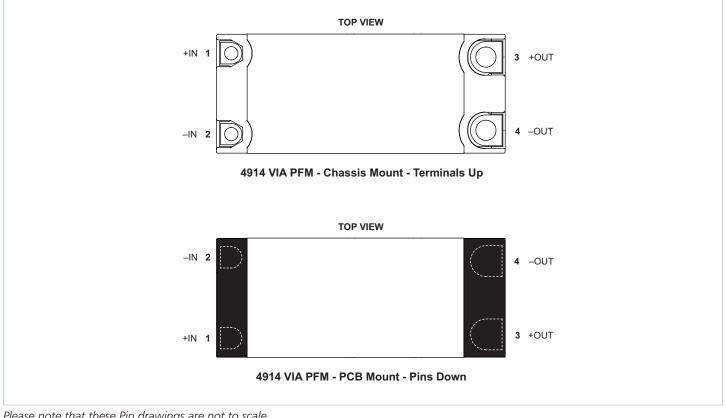

#### **Pin Configuration**

Please note that these Pin drawings are not to scale.

#### **Pin Descriptions**

| Pin Number | Signal Name | Туре                   | Function                       |

|------------|-------------|------------------------|--------------------------------|

| 1          | +IN         | INPUT POWER            | Positive input power terminal  |

| 2          | -IN         | INPUT POWER RETURN     | Negative input power terminal  |

| 3          | +OUT        | OUTPUT POWER           | Positive output power terminal |

| 4          | -OUT        | OUTPUT POWER<br>RETURN | Negative output power terminal |

#### **Absolute Maximum Ratings**

The absolute maximum ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to the device.

| Parameter                      | Comments                                                                        | Min  | Max      | Unit             |

|--------------------------------|---------------------------------------------------------------------------------|------|----------|------------------|

| Input Voltage +IN to -IN       | 1ms max                                                                         | 0    | 600      | V <sub>PK</sub>  |

| Input Voltage (+IN to –IN)     | Continuous, Rectified                                                           | 0    | 275      | V <sub>RMS</sub> |

| Output Voltage (+OUT to –OUT)  |                                                                                 | -0.5 | 29       | V <sub>DC</sub>  |

| Output Current                 |                                                                                 | 0.0  | 24.7     | А                |

| Screw Torque                   | 4 mounting, 2 input, 2 output                                                   |      | 4 (0.45) | N·m (in·lbs)     |

| Operating Junction Temperature | T-Grade                                                                         | -40  | 125      | °C               |

| Storage Temperature            | T-Grade                                                                         | -65  | 125      | °C               |

| Dielectric Withstand *         | See note below                                                                  |      |          |                  |

| Input-Case                     | Basic insulation                                                                | 2121 |          | V <sub>DC</sub>  |

| Input-Output                   | Reinforced insulation (Internal ChiP tested at $4242V_{DC}$ prior to assembly.) | 2121 |          | V <sub>DC</sub>  |

| Output-Case                    | Functional insulation                                                           | 707  |          | V <sub>DC</sub>  |

\* Please see Dielectric Withstand section. See page 19.

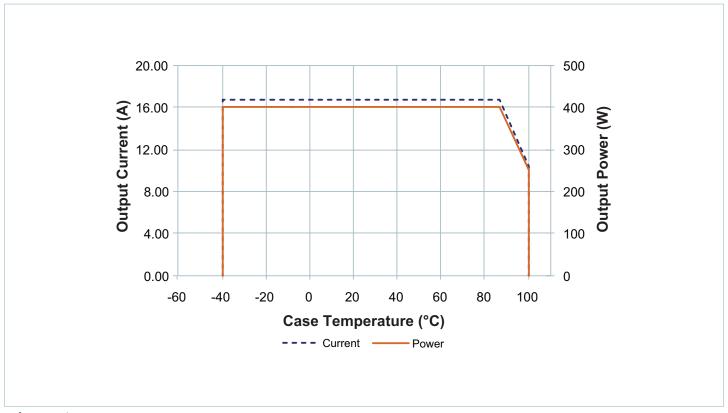

Safe Operating Area

#### **Electrical Specifications**

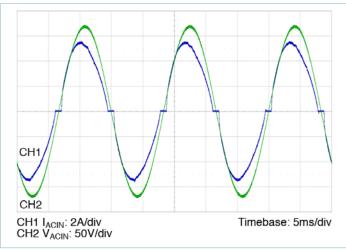

Specifications apply over all line and load conditions, 50Hz and 60Hz line frequencies,  $T_J = 25^{\circ}$ C, unless otherwise noted; **boldface** specifications apply over the temperature range of the specified product grade.  $C_{OUT}$  is 44,000µF ±20% unless otherwise specified.

| Attribute                                                   | Symbol                  | Conditions / Notes                                                                                                                   | Min   | Тур  | Мах   | Unit             |

|-------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

|                                                             |                         |                                                                                                                                      |       |      |       |                  |

| Input Voltage Range,                                        |                         | Power Input Specification                                                                                                            |       |      |       |                  |

| Continuous Operation                                        | V <sub>IN</sub>         |                                                                                                                                      | 85    |      | 264   | V <sub>RMS</sub> |

| Input Voltage Range,<br>Transient, Non-Operational (Peak)   | V <sub>IN</sub>         | 1ms                                                                                                                                  |       |      | 600   | V                |

| Input Voltage Cell Reconfiguration<br>Low-to-High Threshold | V <sub>IN-CR+</sub>     |                                                                                                                                      |       | 145  | 148   | V <sub>RMS</sub> |

| Input Voltage Cell Reconfiguration<br>High-to-Low Threshold | V <sub>IN-CR-</sub>     |                                                                                                                                      | 132   | 135  |       | V <sub>RMS</sub> |

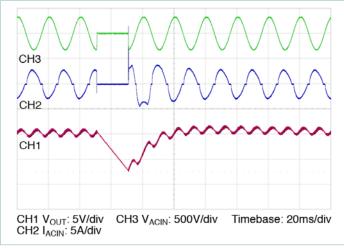

| Input Current (Peak)                                        | I <sub>INRP</sub>       | See Figure 8, Startup Waveforms                                                                                                      |       |      | 12    | А                |

| Source Line Frequency Range                                 | f <sub>line</sub>       |                                                                                                                                      | 47    |      | 63    | Hz               |

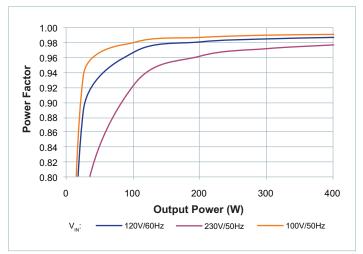

| Power Factor                                                | PF                      | Input power >200W                                                                                                                    |       | 0.96 |       | -                |

| Input Inductance, Maximum                                   | L <sub>IN</sub>         | Differential mode inductance, common mode<br>inductance may be higher. See section "Source<br>Inductance Considerations" on page 16. |       |      | 1     | mH               |

| Input Capacitance, Maximum                                  | C <sub>IN</sub>         | After bridge rectifier, between +IN and -IN                                                                                          |       |      | 1.5   | μF               |

|                                                             |                         | No Load Specification                                                                                                                |       |      |       |                  |

| Input Power – No Load, Maximum                              | P <sub>NL</sub>         | No Load Specification                                                                                                                |       |      | 7     | W                |

| input Power – No Load, Maximum                              | FNL                     |                                                                                                                                      |       |      | /     | VV               |

|                                                             |                         | Power Output Specification                                                                                                           |       |      |       |                  |

| Output Voltage Set Point                                    |                         | Power Output Specification<br>$V_{IN} = 230V_{RMS}$ , 100% load                                                                      | 23    | 24   | 25    | V                |

| Output Voltage, No Load                                     | V <sub>OUT</sub>        | Over all operating steady state line conditions.<br>Wider tolerance valid up to 50W output due to line<br>cycle skipping.            | 23    | 24   | 26    | V                |

| Output Voltage Range (Transient)                            | V <sub>OUT</sub>        | Non-faulting abnormal line and load transient conditions                                                                             | 15    |      | 28.8  | V                |

| Output Power                                                | P <sub>OUT</sub>        | See SOA on Page 5                                                                                                                    |       |      | 400   | W                |

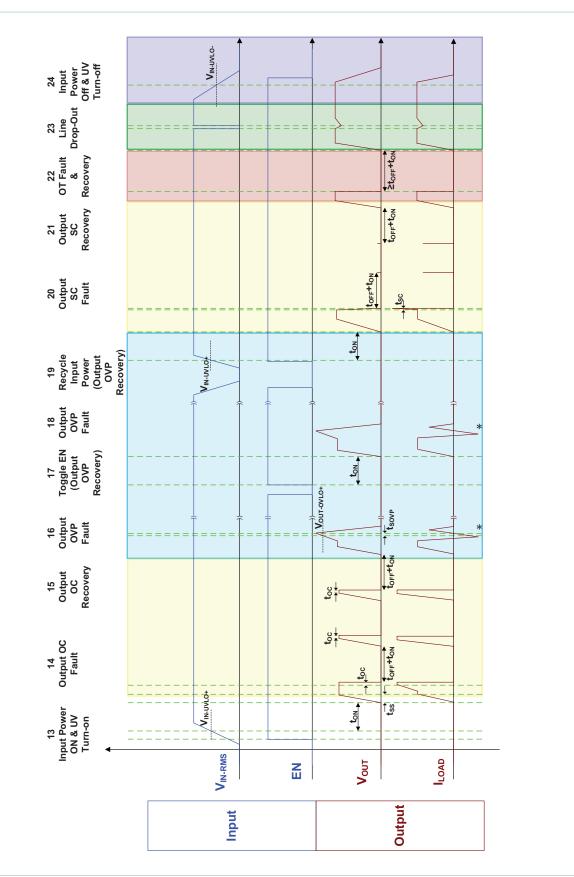

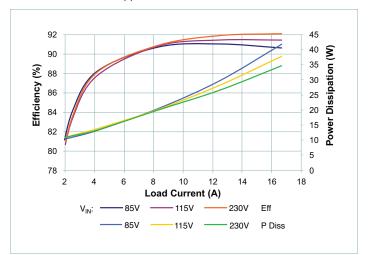

| · · · · · · · · · · · · · · · · · · ·                       |                         | V <sub>IN</sub> = 230V, full load, exclusive of input rectifier losses                                                               | 90.5  | 92   |       | %                |

| Efficiency                                                  | η                       | 85V < V <sub>IN</sub> < 264V, full load, exclusive of input rectifier losses                                                         | 90    |      |       | %                |

|                                                             |                         | 85V < V <sub>IN</sub> < 264V, 75% load,<br>exclusive of input rectifier losses                                                       | 90    |      |       | %                |

| Output Voltage Ripple,<br>Switching Frequency               | V <sub>OUT-PP-HF</sub>  | Over all operating steady-state line and load conditions, 20MHz BW, measured at output, Figure 5                                     |       | 100  | 1000  | mV               |

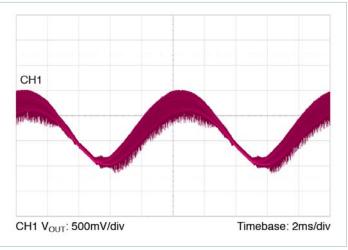

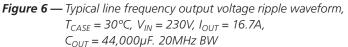

| Output Voltage Ripple<br>Line Frequency                     | V <sub>OUT-PP-LF</sub>  | Over all operating steady-state line and load conditions, 20MHz BW                                                                   |       | 1.5  | 3.5   | V                |

| Output Capacitance (External)                               | C <sub>OUT-EXT</sub>    | Allows for ±20% capacitor tolerance                                                                                                  | 27000 |      | 60000 | μF               |

| Output Turn-On Delay                                        | T <sub>ON</sub>         | From V <sub>IN</sub> applied                                                                                                         |       | 500  | 1000  | ms               |

| Start-Up Setpoint Aquisition Time                           | T <sub>SS</sub>         | Full load                                                                                                                            |       | 500  | 1000  | ms               |

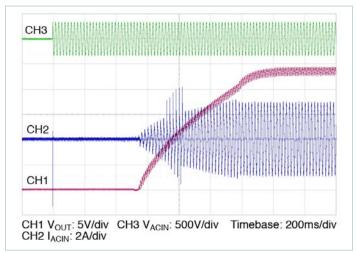

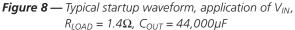

| Cell Reconfiguration Response Time                          | T <sub>CR</sub>         | Full load                                                                                                                            |       | 5.5  | 11    | ms               |

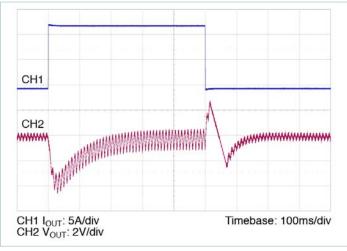

| Voltage Deviation (Transient)                               | %V <sub>OUT-TRANS</sub> |                                                                                                                                      | -37.5 |      | 20    | %                |

| Recovery Time                                               | T <sub>TRANS</sub>      |                                                                                                                                      |       | 300  | 600   | ms               |

| ine Regulation                                              | %V <sub>OUT-LINE</sub>  | Full load                                                                                                                            |       |      | 3     | %                |

| Load Regulation                                             | %V <sub>OUT-LOAD</sub>  | 10% to 100% load                                                                                                                     |       |      | 3     | %                |

| Output Current (Continuous)                                 | I <sub>OUT</sub>        | SOA                                                                                                                                  |       |      | 16.7  | А                |

| Output Current (Transient)                                  | I <sub>OUT-PK</sub>     | 20ms duration, average power ≤P <sub>OUT</sub> , max                                                                                 |       |      | 24.7  | А                |

#### **Electrical Specifications (Cont.)**

Specifications apply over all line and load conditions, 50Hz and 60Hz line frequencies,  $T_J = 25^{\circ}$ C, unless otherwise noted; **boldface** specifications apply over the temperature range of the specified product grade.  $C_{OUT}$  is 44,000µF ±20% unless otherwise specified.

| Attribute                                             | Symbol                 | Conditions / Notes                | Min | Тур  | Мах | Unit             |

|-------------------------------------------------------|------------------------|-----------------------------------|-----|------|-----|------------------|

|                                                       |                        | Powertrain Protections            |     |      |     |                  |

| Input Undervoltage Turn-On                            | V <sub>IN-UVLO+</sub>  | See Timing Diagram                |     | 74   | 83  | V <sub>RMS</sub> |

| Input Undervoltage Turn-Off                           | V <sub>IN-UVLO-</sub>  |                                   | 65  | 71   |     | V <sub>RMS</sub> |

| Input Overvoltage Turn-On                             | V <sub>IN-OVLO-</sub>  | See Timing Diagram                | 265 | 270  |     | V <sub>RMS</sub> |

| Input Overvoltage Turn-Off                            | V <sub>IN-OVLO+</sub>  |                                   |     | 273  | 287 | V <sub>RMS</sub> |

| Output Overvoltage Threshold                          | V <sub>OUT-OVLO+</sub> | Instantaneous, latched shutdown   | 29  | 30.5 | 32  | V                |

| Upper Start / Restart<br>Temperature Threshold (Case) | T <sub>CASE-OTP-</sub> |                                   | 100 |      |     | °C               |

| Overtemperature Shutdown<br>Threshold (Junction)      | T <sub>J-OTP+</sub>    |                                   |     | 125  |     | °C               |

| Overtemperature Shutdown<br>Threshold (Case)          | T <sub>CASE-OTP+</sub> |                                   |     | 110  |     | °C               |

| Overcurrent Blanking Time                             | T <sub>OC</sub>        | Based on line frequency           | 400 | 460  | 550 | ms               |

| Input Overvoltage Response Time                       | T <sub>POVP</sub>      |                                   |     | 40   |     | ms               |

| Input Undervoltage Response Time                      | T <sub>UVLO</sub>      | Based on line frequency           |     | 200  |     | ms               |

| Output Overvoltage Response Time                      | T <sub>SOVP</sub>      | Powertrain on                     |     | 30   |     | ms               |

| Short Circuit Response Time                           | T <sub>SC</sub>        | Powertrain on, operational state  |     | 270  |     | μs               |

| Fault Retry Delay Time                                | T <sub>OFF</sub>       | See Timing Diagram                |     | 10   |     | S                |

| Output Power Limit                                    | P <sub>PROT</sub>      | 50% overload for 20ms typ allowed | 400 |      |     | W                |

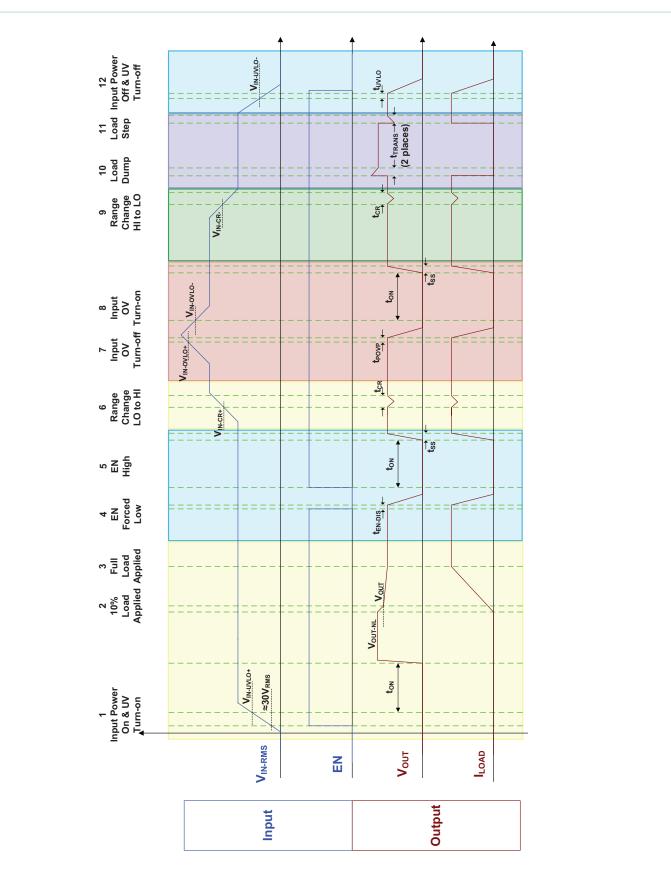

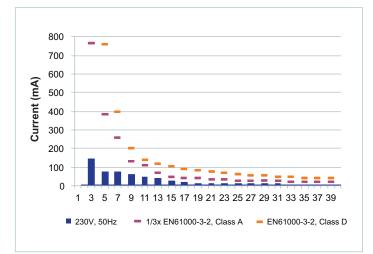

#### **Timing Diagram**

Rev 1.4 08/2017

#### Timing Diagram (Cont.)

Rev 1.4 08/2017

#### **Application Characteristics**

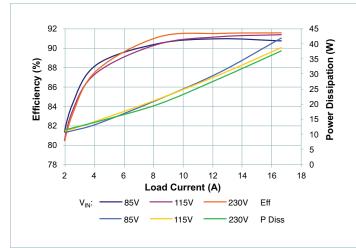

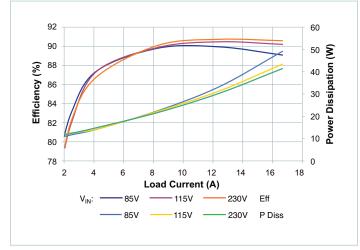

Figure 1 — Full load efficiency vs. line voltage

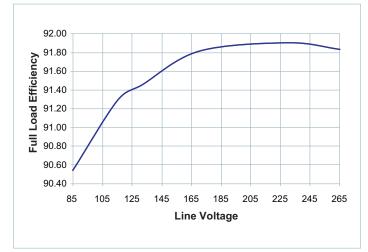

**Figure 3** — Typical input current harmonics, full load vs. V<sub>IN</sub> using typical applications circuit on pages 2 & 3

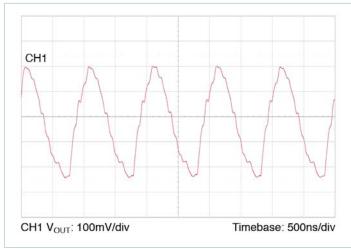

**Figure 5** — Typical switching frequency output voltage ripple waveform,  $T_{CASE} = 30^{\circ}$ C,  $V_{IN} = 230$ V,  $I_{OUT} = 16.7$ A, no external ceramic capacitance, 20MHz BW

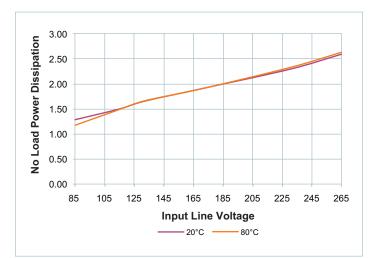

Figure 2 — Typical no load power dissipation vs. V<sub>IN</sub>, module enabled

**Figure 4** — Typical power factor vs. V<sub>IN</sub> and I<sub>OUT</sub> using typical applications circuit on pages 2 & 3

#### **Application Characteristics (Cont.)**

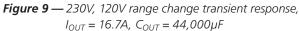

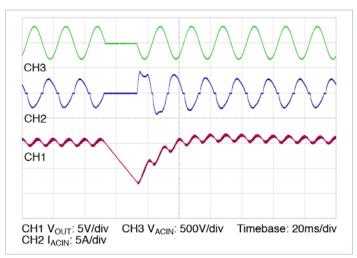

**Figure 11** — Line drop out, 90° phase,  $V_{IN} = 230V$ ,  $I_{OUT} = 16.7A$ ,  $C_{OUT} = 44,000 \mu F$

**Figure 10** — Line drop out, 230V 50Hz, 0° phase,  $I_{OUT} = 16.7A$ ,  $C_{OUT} = 44,000\mu F$

#### **Application Characteristics (Cont.)**

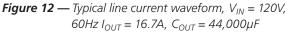

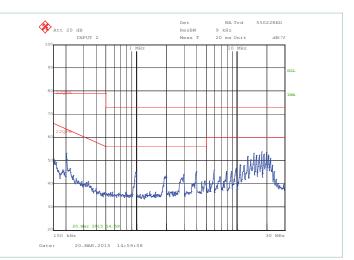

Figure 13 — Typical EMI Spectrum, Peak Scan, 90% load,  $115V_{IN}$ ,  $C_{OUT} = 44,000\mu$ F, No Inlet Filter, C4

Figure 15 — Typical EMI Spectrum, Peak Scan, 90% load, 230V<sub>IN</sub>,  $C_{OUT} = 44,000\mu$ F, No Inlet Filter, C4

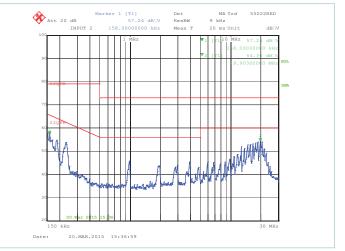

**Figure 14** — Typical EMI Spectrum, Peak Scan, 90% load,  $115V_{IN}$ ,  $C_{OUT} = 44,000 \mu F$  using Typical Chassis Mount Application Circuit

**Figure 16** — Typical EMI Spectrum, Peak Scan, 90% load, 230V<sub>IN</sub>,  $C_{OUT} = 44,000\mu$ F using Typical Chassis Mount Application Circuit

#### **Application Characteristics (Cont.)**

**Figure 19** —  $V_{IN}$  to  $V_{OUT}$  efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT}$ ,  $T_{CASE} = 80^{\circ}C$

#### **General Characteristics**

Specifications apply over all line and load conditions, 50Hz and 60Hz line frequencies,  $T_c = 25$ °C, unless otherwise noted; **boldface** specifications apply over the temperature range of the specified Product Grade.

| Attribute                                                       | Symbol              | Conditions / Notes                                                              | Min   | Тур            | Max | Unit                               |  |  |  |

|-----------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------|-------|----------------|-----|------------------------------------|--|--|--|

|                                                                 |                     |                                                                                 |       |                |     |                                    |  |  |  |

|                                                                 |                     | Mechanical                                                                      |       |                |     |                                    |  |  |  |

| Length                                                          | L                   |                                                                                 |       | 124.8 / [4.91] |     | mm / [in]                          |  |  |  |

| Width                                                           | W                   |                                                                                 |       | 35.5 / [1.40]  |     | mm / [in                           |  |  |  |

| Height                                                          | Н                   |                                                                                 |       | 9.3 / [0.37]   |     | mm / [in]                          |  |  |  |

| Volume                                                          | Vol                 | Without heatsink                                                                |       | 42.0/[2.56]    |     | cm <sup>3</sup> / [in <sup>3</sup> |  |  |  |

| Weight                                                          | W                   |                                                                                 |       | 156 / [5.5]    |     | g / [oz]                           |  |  |  |

| Pin Material                                                    |                     | C145 copper, half hard                                                          |       |                |     |                                    |  |  |  |

| Underplate                                                      |                     | Low stress ductile nickel                                                       | 50    |                | 100 | μin                                |  |  |  |

|                                                                 |                     | Palladium                                                                       | 0.8   |                | 6   | µin                                |  |  |  |

| Pin Finish                                                      |                     | Soft Gold                                                                       | 0.12  |                | 2   | μin                                |  |  |  |

|                                                                 |                     |                                                                                 |       |                |     |                                    |  |  |  |

|                                                                 |                     | Thermal                                                                         |       |                |     |                                    |  |  |  |

|                                                                 | - <b>T</b>          | C-Grade, see derating curve in SOA                                              | -20   |                | 100 | °C                                 |  |  |  |

| Operating Case Temperature                                      | T <sub>C</sub>      | T-Grade, see derating curve in SOA                                              | -40   |                | 100 | °C                                 |  |  |  |

| Thermal Resistance,<br>Junction to Case, Top                    | R <sub>JC_TOP</sub> |                                                                                 |       | 1.43           |     | °C/W                               |  |  |  |

| Thermal Resistance,<br>Junction to Case, Bottom                 | R <sub>JC_BOT</sub> |                                                                                 |       | 1.85           |     | °C/W                               |  |  |  |

| Coupling Thermal Resistance,<br>Top to Bottom of Case, Internal | R <sub>HOU</sub>    |                                                                                 |       | 0.36           |     | °C/W                               |  |  |  |

| Shell Thermal Capacity                                          |                     |                                                                                 |       | 32             |     | J/K                                |  |  |  |

| Thermal Design                                                  |                     | See Thermal Considerations on Page 18                                           |       |                |     |                                    |  |  |  |

|                                                                 |                     | Assembly                                                                        |       |                |     |                                    |  |  |  |

|                                                                 | ESD <sub>HBM</sub>  | Human Body Model,<br>JEDEC JESD 22-A114C.01                                     | 1,000 |                |     |                                    |  |  |  |

| ESD Rating                                                      | ESD <sub>MM</sub>   | Machine Model,<br>JEDEC JESD 22-A115B                                           | N/A   |                |     | V                                  |  |  |  |

|                                                                 | ESD <sub>CDM</sub>  | Charged Device Model,<br>JEDEC JESD 22-C101D                                    | 200   |                |     |                                    |  |  |  |

|                                                                 |                     |                                                                                 |       |                |     |                                    |  |  |  |

|                                                                 |                     | Safety                                                                          |       |                |     |                                    |  |  |  |

|                                                                 | cTÜVus; E           | N 60950-1                                                                       |       |                |     |                                    |  |  |  |

|                                                                 | cURus; UL           | 60950-1                                                                         |       |                |     |                                    |  |  |  |

| Agency Approvals / Standards                                    | CE Markee           | CE Marked for Low Voltage Directive and RoHS Recast Directive, as applicable    |       |                |     |                                    |  |  |  |

|                                                                 |                     | rent measured in accordance with IEC<br>ng measuring network Figure 3 (PFM in a |       | 0.5            |     | mA                                 |  |  |  |

#### **General Characteristics (Cont.)**

Specifications apply over all line and load conditions, 50Hz and 60Hz line frequencies,  $T_c = 25$ °C, unless otherwise noted; **boldface** specifications apply over the temperature range of the specified Product Grade.

| Attribute                                                                          | Symbol | Conditions / Notes                                                                       | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                                                                                    |        |                                                                                          |     |     |     |      |

|                                                                                    |        | EMI/EMC Compliance (pending)                                                             |     |     |     |      |

| FCC Part 15, EN55022, CISPR22: 2006 + A1: 2007, Conducted Emissions                |        | Class B Limits - with –OUT<br>connected to GND                                           |     |     |     |      |

| EN61000-3-2: 2009,<br>Harmonic Current Emissions                                   |        | Class A                                                                                  |     |     |     |      |

| EN61000-3-3: 2005,<br>Voltage Changes & Flicker                                    |        | P <sub>ST</sub> <1.0; P <sub>LT</sub> <0.65; dc <3.3%<br>dmax <6%                        |     |     |     |      |

| EN61000-4-4: 2004,<br>Electrical Fast Transients                                   |        | Level 2, Performance Criteria A                                                          |     |     |     |      |

| EN61000-4-5: 2006,<br>Surge Immunity                                               |        | Level 3, Immunity Criteria A,<br>external TMOV and fuse shown on page<br>2 or 3 required |     |     |     |      |

| EN61000-4-6: 2009,<br>Conducted RF Immunity                                        |        | Level 2, 130dBµV (3.0V <sub>RMS</sub> )                                                  |     |     |     |      |

| EN61000-4-8: 1993 + A1 2001,<br>Power Frequency H-Field 10A/m,<br>continuous field |        | Level 3, Performance Criteria A                                                          |     |     |     |      |

| EN61000-4-11: 2004,<br>Voltage Dips & Interrupts                                   |        | Class 2, Performance Criteria A Dips,<br>Performance Criteria B Interrupts               |     |     |     |      |

| Case | Reliability Assurance Relex Modeling, Studio 2007, v2]                              | Temp (°C) | Duty Cycle | Condition | MTBF (MHrs) | FIT  |  |  |  |

|------|-------------------------------------------------------------------------------------|-----------|------------|-----------|-------------|------|--|--|--|

|      |                                                                                     |           |            |           |             |      |  |  |  |

|      | Reliability                                                                         |           |            |           |             |      |  |  |  |

| 1    | Telcordia Issue 2, Method I Case 1                                                  | 25        | 100%       | GB,GC     | 0.702       | 1424 |  |  |  |

| 2    | MIL-HDBK-217FN2 Parts Count - 25°C Ground Benign, Stationary,<br>Indoors / Computer | 25        | 100%       | GB,GC     | 0.322       | 3102 |  |  |  |

| 3    | Telcordia Issue 2, Method I Case 3                                                  | 25        | 100%       | GB,GC     | 2.43        | 412  |  |  |  |

#### **Product Details and Design Guidelines**

#### **Building Blocks and System Designs**

Figure 20 — 400W Universal AC-DC Supply

The PFM in a VIA package is a high efficiency AC-DC converter, operating from a universal AC input to generate an isolated SELV  $24V_{DC}$  output bus with power factor correction. It is the key component of an AC-DC power supply system such as the one shown in Figure 20 above.

The input to the PFM in a VIA package is a rectified sinusoidal AC source with a power factor maintained by the module with harmonics conforming to IEC 61000-3-2. Internal filtering enables compliance with the standards relevant to the application (Surge, EMI, etc.). See EMI/EMC Compliance standards on Page 15.

The module uses secondary-side energy storage (at the SELV 24V bus) to maintain output hold up through line dropouts and brownouts. Downstream regulators also provide tighter voltage regulation, if required.

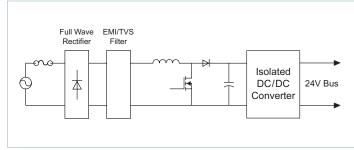

#### Traditional PFC Topology

Figure 21 — Traditional PFC AC-DC supply

To cope with input voltages across worldwide AC mains  $(85 - 264V_{AC})$ , traditional AC-DC power supplies (Figure 21) use two power conversion stages: 1) a PFC boost stage to step up from a rectified input as low as  $85V_{AC}$  to  $\sim 380V_{DC}$ ; and 2) a DC-DC down converter from  $380V_{DC}$  to a 24V bus.

The efficiency of the boost stage and of traditional power supplies is significantly compromised operating from worldwide AC lines as low as  $85V_{AC}$ .

#### Adaptive Cell™ Topology

With its single stage Adaptive Cell<sup>™</sup> topology, the PFM in a VIA package enables consistently high efficiency conversion from worldwide AC mains to a 24V bus and efficient secondary-side power distribution.

#### Input Fuse Selection

PFM in a VIA package products are not internally fused in order to provide flexibility in configuring power systems. Input line fusing is recommended at system level, in order to provide thermal protection in case of catastrophic failure. The fuse shall be selected by closely matching system requirements with the following characteristics:

- Recommended fuse: 216 Series Littelfuse 8A or lower current rating (usually greater than the PFM maximum current at lowest input voltage)

- Maximum voltage rating (usually greater than the maximum possible input voltage)

- Ambient temperature

- Breaking capacity per application requirements

- Nominal melting I<sup>2</sup>t

#### **Source Inductance Considerations**

The PFM Powertrain uses a unique Adaptive Cell Topology that dynamically matches the powertrain architecture to the AC line voltage. In addition the PFM in a VIA package uses a unique control algorithm to reduce the AC line harmonics yet still achieve rapid response to dynamic load conditions presented to it at the DC output terminals. Given these unique power processing features, the PFM in a VIA package can expose deficiencies in the AC line source impedance that may result in unstable operation if ignored.

It is recommended that for a single PFM, the line source inductance should be no greater than 1mH for a universal AC input of 100 – 240V. If the PFM in a VIA package will be operated at 240V nominal only, the source impedance may be increased to 2mH. For either of the preceding operating conditions it is best to be conservative and stay below the maximum source inductance values. When multiple PFM in a VIA package's are used on a single AC line, the inductance should be no greater than 1mH/N, where N is the number of PFM in a VIA package's on the AC branch circuit, or 2mH/N for 240V $_{AC}$  operation. It is important to consider all potential sources of series inductance including and not limited to, AC power distribution transformers, structure wiring inductance, AC line reactors, and additional line filters. Non-linear behavior of power distribution devices ahead of the PFM in a VIA package may further reduce the maximum inductance and require testing to ensure optimal performance.

If the PFM in a VIA package is to be utilized in large arrays, the PFM in a VIA packages should be spread across multiple phases or sources thereby minimizing the source inductance requirements, or be operated at a line voltage close to  $240V_{AC}$ . Vicor Applications should be contacted to assist in the review of the application when multiple devices are to be used in arrays.

#### **Fault Handling**

#### Input Undervoltage (UV) Fault Protection

The input voltage is monitored by the micro-controller to detect an input under voltage condition. When the input voltage is less than the V<sub>IN-UVLO</sub>-, a fault is detected, the fault latch and reset logicdisables the modulator, the modulator stops powertrain switching, and the output voltage of the unit falls. After a time t<sub>UVLO</sub>, the unit shuts down. Faults lasting less than t<sub>UVLO</sub> may not be detected. Such a fault does not go through an auto-restart cycle. Once the input voltage rises above V<sub>IN-UVLO+</sub>, the unit recovers from the input UV fault, the powertrain resumes normal switching after a time t<sub>ON</sub> and the output voltage of the unit reaches the set-point voltage within a time t<sub>SS</sub>.

#### Overcurrent (OC) Fault Protection

The unit's output current, determined by V<sub>EAO</sub>, V<sub>IN\_B</sub> and the primary-side sensed output voltage is monitored by the microcontroller to detect an output OC condition. If the output current exceeds its current limit, a fault is detected, the reset logic disables the modulator, the modulator stops powertrain switching, and the output voltage of the module falls after a time t<sub>OC</sub>. As long as the fault persists, the module goes through an auto-restart cycle with off time equal to t<sub>OFF</sub> + t<sub>ON</sub> and on time equal to t<sub>OC</sub>. Faults shorter than a time t<sub>OC</sub> may not be detected. Once the fault is cleared, the module follows its normal start up sequence after a time t<sub>OFF</sub>.

#### Short Circuit (SC) Fault Protection

The microcontroller determines a short circuit on the output of the unit by measuring its primary sensed output voltage and EAO. Most commonly, a drop in the primary-sensed output voltage triggers a short circuit event. The module responds to a short circuit event within a time  $t_{SC}$ . The module then goes through an auto restart cycle, with an off time equal to  $t_{OFF} + t_{ON}$  and an on time equal to  $t_{SC}$ , for as long as the short circuit fault condition persists. Once the fault is cleared, the unit follows its normal start up sequence after a time  $t_{OFF}$ . Faults shorter than a time  $t_{SC}$  may not be detected.

#### Temperature Fault Protection

The microcontroller monitors the temperature within the PFM in a VIA package. If this temperature exceeds  $T_{J-OTP+}$ , an overtemperature fault is detected, the reset logic block disables the modulator, the modulator stops the powertrain switching and the output voltage of the PFM in a VIA package falls. Once the case temperature falls below  $T_{CASE-OTP-}$ , after a time greater than or equal to  $t_{OFF}$ , the converter recovers and undergoes a normal restart. For the C-grade version of the converter, this temperature is 75°C. Faults shorter than a time  $t_{OTP}$  may not be detected. If the temperature falls below  $T_{CASE-UTP-}$ , an undertemperature fault is detected, the reset logic disables the modulator, the modulator stops powertrain switching and the output voltage of the unit falls. Once the case temperature rises above  $T_{CASE-UTP}$ , after a time greater than or equal to  $t_{OFF}$ , the unit recovers and undergoes a normal restart.

#### Output Overvoltage Protection (OVP)

The microcontroller monitors the primary sensed output voltage to detect output OVP. If the primary sensed output voltage exceeds  $V_{OUT-OVLO+}$ , a fault is latched, the logic disables the modulator, the modulator stops powertrain switching, and the output voltage of the module falls after a time  $t_{SOVP}$ . Faults shorter than a time  $t_{SOVP}$  may not be detected. This type of fault is a latched fault and requires that the input power be recycled to recover from the fault.

#### Hold-up Capacitance

The PFM in a VIA package uses secondary-side energy storage (at the SELV 24V bus) and downstream regulators to maintain output hold up through line dropouts and brownouts. The module's output bulk capacitance can be sized to achieve the required hold up functionality.

Hold-up time depends upon the output power drawn from the The PFM in a VIA package based AC-DC front end and the input voltage range of downstream DC-DC converters.

The following formula can be used to calculate hold-up capacitance for a system comprised of PFM in a VIA package and a downstream regulator:

$$C = 2 \bullet P_{OUT} \bullet (0.005 + t_d) / (V_2^2 - V_1^2)$$

Where:

- C VIA PFM's output bulk capacitance in Farads

- t<sub>d</sub> Hold-up time in seconds

- **Pout** VIA PFM's output power in Watts

- V<sub>2</sub> Output voltage of VIA PFM's converter in Volts

- V<sub>1</sub> Downstream regulator undervoltage turn off (Volts) -OR-

$P_{OUT} / I_{OUT-PK}$ , whichever is greater.

#### **Output Filtering**

The The PFM in a VIA package requires an output bulk capacitor in the range of 27,000µF to 60,000µF for proper operation of the PFC front-end. A minimum 40,000µF is recommended for full rated output. Capacitance can be reduced proportionally for lower maximum loads.

- **1.** Line frequency voltage ripple: 2 f<sub>LINE</sub> Hz component

- **2.** Switching frequency voltage ripple: 1MHz module switching frequency component (see Figure 5).

#### Line Frequency Filtering

Output line frequency ripple depends upon output bulk capacitance. Output bulk capacitor values should be calculated based on line frequency voltage ripple. High-grade electrolytic capacitors with adequate ripple current ratings, low ESR and a minimum voltage rating of 35V are recommended.

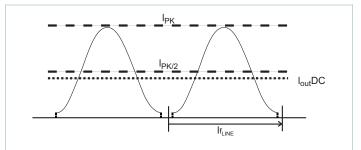

Figure 22 — Output current waveform

Based on the output current waveform, as seen in Figure 22, the following formula can be used to determine peak-to-peak line frequency output voltage ripple:

$$V_{ppl} \approx 0.2 \bullet P_{OUT} / (V_{OUT} \bullet f_{LINE} \bullet C)$$

Where:

- **V**<sub>ppl</sub> Output voltage ripple peak-to-peak line frequency

- **P**<sub>OUT</sub> Average output power

- Vout Output voltage set point, nominally 24V

- **f**<sub>line</sub> Frequency of line voltage

- **C** Output bulk capacitance

- **I**<sub>DC</sub> Maximum average output current

- IPK Peak-to-peak line frequency output current ripple

In certain applications, the choice of bulk capacitance may be determined by hold-up requirements and low frequency output voltage filtering requirements. Such applications may use the greater capacitance value determined from these requirements. The ripple current rating for the bulk capacitors can be determined from the following equation:

$$I_{ripple} \approx 0.8 \bullet P_{OUT} / V_{OUT}$$

#### Switching Frequency Filtering

This is included within the PFM in a VIA. No external filtering is necessary for most applications. For the most noise sensitive applications, a common mode choke followed by two caps to PE GND will reduce switching noise further.

#### EMI Filtering and Transient Voltage Suppression

#### EMI Filtering

The PFM in a VIA package with PFC is designed such that it will comply with EN55022 Class B for Conducted Emissions with a commercially available off-the-shelf EM filter. The emissions spectrum is shown in Figures 13 – 16. If one of the outputs is connected to earth ground, a small output common mode choke is also recommended.

EMI performance is subject to a wide variety of external influences such as PCB construction, circuit layout etc. As such, external components in addition to those listed herein may be required in specific instances to gain full compliance to the standards specified. Radiated emissions require certification at the system level. For best results, enclose the product in a steel enclosure. Filtering must be considered for every conductor leaving the enclosure, which can present itself as a potential transmission antenna.

#### Transient Voltage Suppression

The PFM in a VIA package contains line transient suppression circuitry to meet specifications for surge (i.e. EN61000-4-5) and fast transient conditions (i.e. EN61000-4-4 fast transient/"burst") when coupled with an external TMOV as shown on pages 2 and 3.

When more than one PFM is used in a system, each PFM should have its own fuse, TMOV and bridge rectifier.

#### **Thermal Considerations**

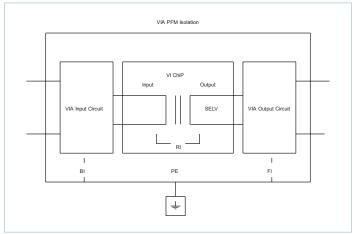

The VIA<sup>™</sup> package provides effective conduction cooling from either of the two module surfaces. Heat may be removed from the

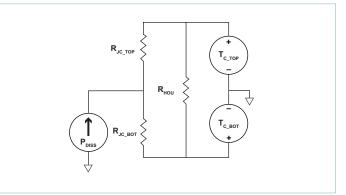

top surface, the bottom surface or both. The extent to which these two surfaces are cooled is a key component for determining the maximum power that can be processed by a VIA, as can be seen from specified thermal operating area on Page 5. Since the VIA has a maximum internal temperature rating, it is necessary to estimate this internal temperature based on a system-level thermal solution. To this purpose, it is helpful to simplify the thermal solution into a roughly equivalent circuit where power dissipation is modeled as a current source, isothermal surface temperatures are represented as voltage sources and the thermal resistances are represented as resistors. Figure 23 shows the "thermal circuit" for the VIA module.

Figure 23 — Double sided cooling VIA thermal model

In this case, the internal power dissipation is  $P_{DISS},\,R_{JC\_TOP}$  and  $R_{JC\_BOT}$  are thermal resistance characteristics of the VIA module and the top and bottom surface temperatures are represented as  $T_{C\_TOP}$ , and  $T_{C\_BOT}$ . It interesting to notice that the package itself provides a high degree of thermal coupling between the top and bottom case surfaces (represented in the model by the resistor  $R_{HOU}$ ). This feature enables two main options regarding thermal designs:

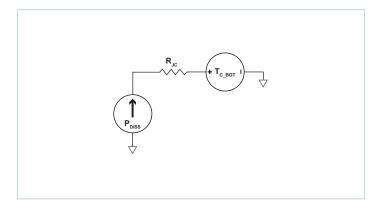

Single side cooling: the model of Figure 23 can be simplified by calculating the parallel resistor network and using one simple thermal resistance number and the internal power dissipation curves; an example for bottom side cooling only is shown in Figure 24.

In this case,  $R_{JC}$  can be derived as following:

$$R_{JC} = \frac{(R_{_{JC\_TOP}} + R_{_{HOU}}) \bullet R_{_{JC\_BOT}}}{R_{_{JC\_TOP}} + R_{_{HOU}} + R_{_{JC\_BOT}}}$$

## PFM4914xB6M24D0yzz

## PFM4914xB6M24D0yzz

Double side cooling: while this option might bring limited advantage to the module internal components (given the surface-to-surface coupling provided), it might be appealing in cases where the external thermal system requires allocating power to two different elements, like for example heatsinks with independent airflows or a combination of chassis/air cooling.

#### **Powering a Constant Power Load**

When the output voltage of the PFM in a VIA package module is applied to the input of the downstream regulator, the regulator turns on and acts as a constant-power load. When the module's output voltage reaches the input undervoltage turn on of the regulator, the regulator will attempt to start. However, the current demand of the downstream regulator at the undervoltage turn-on point and the hold-up capacitor charging current may force the PFM in a VIA package into current limit. In this case, the unit may shut down and restart repeatedly. In order to prevent this multiple restart scenario, it is necessary to delay enabling a constant-power load when powered up by the upstream PFM in a VIA package until after the output set point of the PFM in a VIA package is reached.

This can be achieved by:

**1.** Keeping the downstream constant-power load off during power up sequence,

and

**2.** Turning the downstream constant-power load on after the output voltage of the module reaches 24V steady state.

After the initial startup, the output of the PFM in a VIA package can be allowed to fall to 15V during a line dropout at full load. In this case, the circuit should not disable the downstream regulator if the input voltage falls after it is turned on; therefore, some form of hysteresis or latching is needed on the enable signal for the constant power load. The output capacitance of the PFM in a VIA package should also be sized appropriately for a constant power load to prevent collapse of the output voltage of the module during line dropout (see Hold up Capacitance on Page 17). A constant-power load can be turned off after completion of the required hold up time during the power-down sequence or can be allowed to turn off when it reaches its own undervoltage shutdown point.

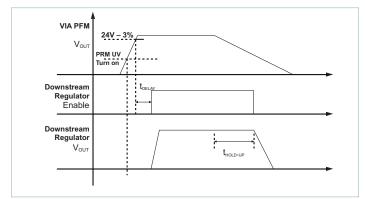

The timing diagram in Figure 25 shows the output voltage of the PFM in a VIA package and the downstream regulator's enable pin voltage and output voltage of the PRM regulator for the power up and power down sequence. It is recommended to keep the time delay approximately 10 to 20ms.

Special care should be taken when enabling the constant-power load near the auto-ranger threshold, especially with an inductive source upstream of the PFM in a VIA package. A load current spike may cause a large input voltage transient, resulting in a range change which could temporarily reduce the available power (see Adaptive Cell™ Topology below).

#### Adaptive Cell<sup>™</sup> Topology

The Adaptive Cell topology utilizes magnetically coupled "top" and "bottom" primary cells that are adaptively configured in series or parallel by a configuration controller comprised of an array of switches. A microcontroller monitors operating conditions and defines the configuration of the top and bottom cells through a range control signal.

A comparator inside the microcontroller monitors the line voltage and compares it to an internal voltage reference.

If the input voltage of the PFM crosses above the positive going cell reconfiguration threshold voltage, the top cell and bottom cell configure in series and the unit operates in "high" range.

If the peak of input voltage of the unit falls below the negative-going range threshold voltage for two line cycles, the cell configuration controller configures the top cell and bottom cell in parallel, the unit operates in "low" range.

Power processing is held off while transitioning between ranges and the output voltage of the unit may temporarily droop. External output hold up capacitance should be sized to support power delivery to the load during cell reconfiguration. The minimum specified external output capacitance is sufficient to provide adequate ride-through during cell reconfiguration for typical applications. Waveforms showing active cell reconfiguration can be seen in Figure 9.

#### **Dielectric Withstand**

The chassis of the PFM is required to be connected to Protective Earth when installed in the end application and must satisfy the requirements of IEC 60950-1 for Class I products. Both sides of the housing are required to be connected to Protective Earth to satisfy safety and EMI requirements. Protective earthing can be accomplished through dedicated wiring harness (example: ring terminal clamped by mounting screw) or surface contact (example: pressure contact on bare conductive chassis or PCB copper layer with no solder mask).

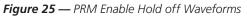

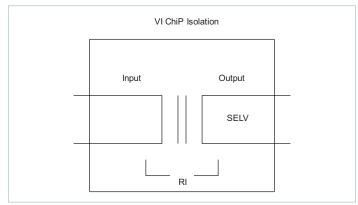

The PFM contains an internal safety approved isolating component (VI ChiP) that provides the Reinforced Insulation from Input to Output. The isolating component is individually tested for Reinforced Insulation from Input to Output at  $3000V_{AC}$  or  $4242V_{DC}$  prior to the final assembly of the VIA.

When the VIA assembly is complete the Reinforced Insulation can only be tested at Basic Insulation values as specified in the electric strength Test Procedure noted in clause 5.2.2 of IEC 60950-1.

#### Test Procedure Note from IEC 60950-1

"For equipment incorporating both REINFORCED INSULATION and lower grades of insulation, care is taken that the voltage applied to the REINFORCED INSULATION does not overstress BASIC INSULATION or SUPPLEMENTARY INSULATION."

#### Summary

The final VIA assembly contains basic insulation from input to case, reinforced insulation from input to output, and functional insulation from output to case.

The output of the VIA complies with the requirements of SELV circuits so only functional insulation is required from the output (SELV) to case (PE) because the case is required to be connected to protective earth in the final installation. The construction of the VIA can be summarized by describing it as a "Class II" component installed in a "Class I" subassembly. The reinforced insulation from input to output can only be tested at a basic insulation value of  $2121V_{DC}$  on the completely assembled VIA product.

Figure 26 — VI Chip before final assembly in the VIA

Figure 27 — PFM in a VIA package after final assembly

## PFM4914xB6M24D0yzz

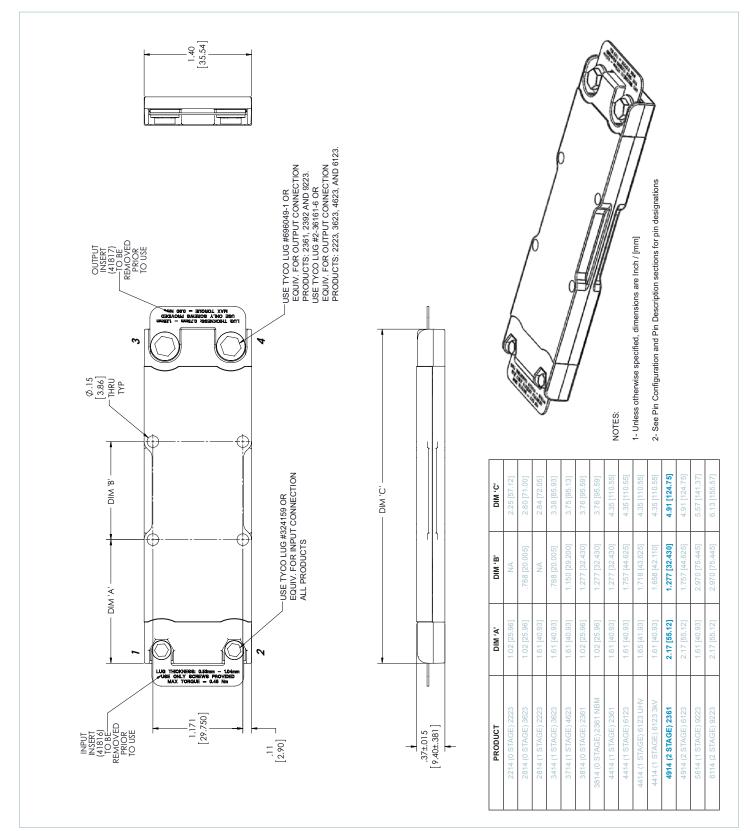

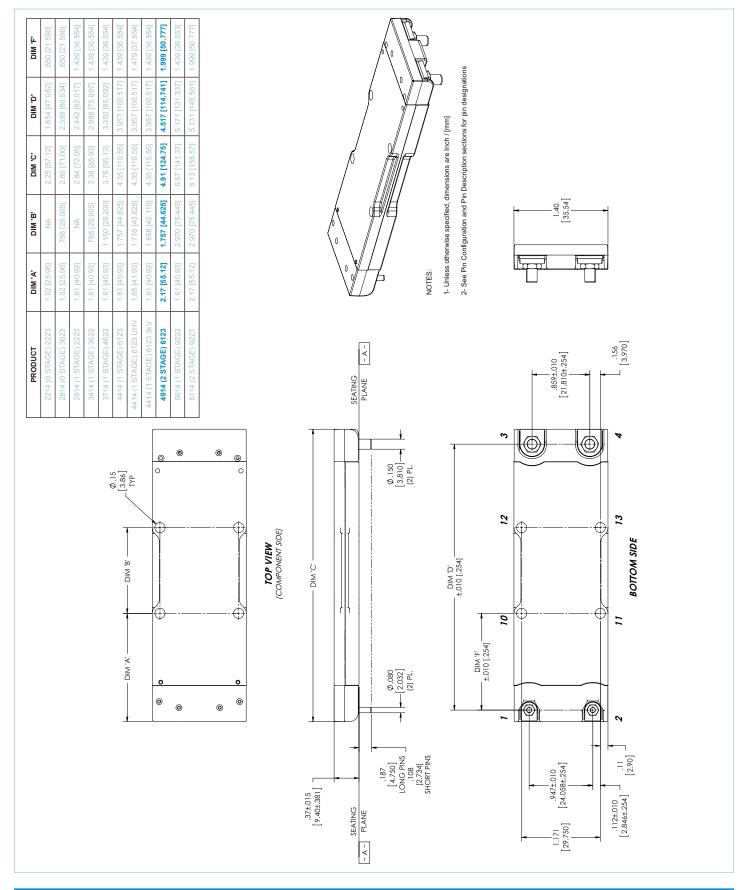

#### PFM in a VIA Package Chassis Mount Package Mechanical Drawing

Product outline drawing; product outline drawings are available in .pdf and .dxf formats. 3D mechanical models are available in .pdf and .step formats.

Rev 1.4 08/2017

## PFM4914xB6M24D0yzz

VIC

Rev 1.4 08/2017

## PFM<sup>™</sup> in a VIA Package

# 4.517 [114.741] 4.91 [124.75]

1.999 [50.777]

1.757 [44.625]

2.17 [55.12] 1.61 [40.93]

4914 (2 STAGE) 6123

5614 (1 STAGE)

.439 [36

.1. MIQ

.q. WIQ

DIM 'C'

.8. WIQ

.V. MID

PRODUCT

¥

80

¥

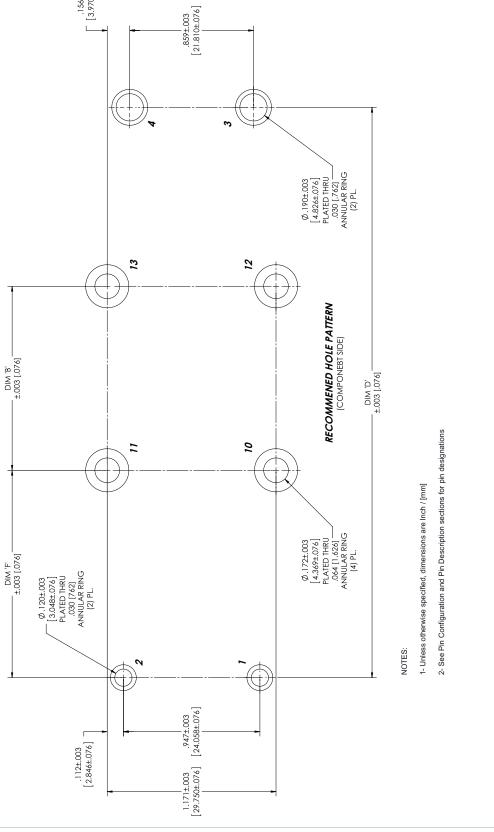

PFM in a VIA Package PCB Mount Package Recommended Land Pattern

.156±.003 [3.970±.076]

∟

Rev 1.4

08/2017

VIC

$\cap R$

#### **Revision History**

| Revision | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page Number(s)                                              |

|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1.0      | 05/15/15 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n/a                                                         |

| 1.1      | 05/15    | Mechanical drawing change                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                          |

| 1.2      | 06/10/15 | Revised typical application part numbers<br>Grounding note added<br>Pin name change                                                                                                                                                                                                                                                                                                                                                                                          | 2, 3<br>18<br>20                                            |

| 1.3      | 07/16/15 | Added Pin Configuration and Description page<br>Added Source Inductor Consideration note<br>Added Safety Approvals<br>Added Source Inductor Consideration section<br>Updated Mechanical drawing                                                                                                                                                                                                                                                                              | 4<br>6<br>14<br>16<br>21                                    |

| 1.4      | 08/02/17 | PFM in a VIA package nomenclature and Product ratings table added<br>Corrected ULVO labels to UVLO<br>Updated thermal model parameters<br>Added "fuse" to list of external components required to meet surge level 3<br>Updated typical application information<br>Updated pin configuration<br>Updated storage temperature, input-output isolation test voltage<br>Clarified power output specifications<br>Clarified EMI filtering information<br>Updated package drawings | 1<br>7<br>14<br>15<br>2-3<br>4<br>5<br>6<br>15, 18<br>21-23 |

## Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication. Vicor reserves the right to make changes to any products, specifications, and product descriptions at any time without notice. Information published by Vicor has been checked and is believed to be accurate at the time it was printed; however, Vicor assumes no responsibility for inaccuracies. Testing and other quality controls are used to the extent Vicor deems necessary to support Vicor's product warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

#### Specifications are subject to change without notice.

Visit <u>http://www.vicorpower.com/ac-dc/converters/isolated-ac-dc-converter-pfc</u> for the latest product information.

#### Vicor's Standard Terms and Conditions and Product Warranty

All sales are subject to Vicor's Standard Terms and Conditions of Sale, and Product Warranty which are available on Vicor's webpage (<u>http://www.vicorpower.com/termsconditionswarranty</u>) or upon request.

#### **Life Support Policy**

VICOR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF VICOR CORPORATION. As used herein, life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness. Per Vicor Terms and Conditions of Sale, the user of Vicor products and components in life support applications assumes all risks of such use and indemnifies Vicor against all liability and damages.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. No license, whether express, implied, or arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by the following U.S. Patents Numbers: Patents Pending.

Contact Us: http://www.vicorpower.com/contact-us

#### **Vicor Corporation**

25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715 www.vicorpower.com

email

Customer Service: <u>custserv@vicorpower.com</u> Technical Support: <u>apps@vicorpower.com</u>

©2017 Vicor Corporation. All rights reserved. The Vicor name is a registered trademark of Vicor Corporation. All other trademarks, product names, logos and brands are property of their respective owners.