# **NORA-W30** series

## Stand-alone dual-band Wi-Fi and Bluetooth® modules

Data sheet

### **Abstract**

Aimed towards developers and other technical staff, this document provides important information necessary for the design of customer applications based on NORA-W30 dual-band Wi-Fi and Bluetooth modules. It includes an overview and comprehensive functional description of each module variant – together with a detailed pin list, block diagram, mechanical and electrical specification, application development information, and more.

## **Document information**

| Title                  | NORA-W30 series                                    |             |

|------------------------|----------------------------------------------------|-------------|

| Subtitle               | Stand-alone dual-band Wi-Fi and Bluetooth® modules |             |

| Document type          | Data sheet                                         |             |

| Document number        | UBX-22021117                                       |             |

| Revision and date      | R06                                                | 21-Mar-2025 |

| Disclosure restriction | C1-Public                                          |             |

| Product status                   | Corresponding content status |                                                                                       |  |

|----------------------------------|------------------------------|---------------------------------------------------------------------------------------|--|

| Functional sample                | Draft                        | For functional testing. Revised and supplementary data will be published later.       |  |

| In development /<br>Prototype    | Objective specification      | Target values. Revised and supplementary data will be published later.                |  |

| Engineering sample               | Advance information          | Data based on early testing. Revised and supplementary data will be published later.  |  |

| Initial production               | Early production information | Data from product verification. Revised and supplementary data may be published later |  |

| Mass production /<br>End of life | Production information       | Document contains the final product specification.                                    |  |

### This document applies to the following products:

| Product name | Type number      | IN/PCN reference | Product status     |

|--------------|------------------|------------------|--------------------|

| NORA-W301    | NORA-W301-00B-00 | N/A              | Initial production |

| NORA-W306    | NORA-W306-00B-00 | N/A              | Initial production |

u-blox or third parties may hold intellectual property rights in the products, names, logos, and designs included in this document. Copying, reproduction, or modification of this document or any part thereof is only permitted with the express written permission of u-blox. Disclosure to third parties is permitted for clearly public documents only.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability, and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents and statuses, visit www.u-blox.com.

Copyright © u-blox AG.

## **Contents**

| D | ocu  | men  | t information                 | . 2 |

|---|------|------|-------------------------------|-----|

| C | onte | ents |                               | . 3 |

| 1 | F    | unct | ional description             | . 6 |

|   | 1.1  | Ove  | rview                         | . 6 |

|   | 1.2  | App  | lications                     | . 6 |

|   | 1.3  | Bloc | k diagram                     | . 7 |

|   | 1.4  | Prod | duct variants                 | . 7 |

|   | 1.   | 4.1  | NORA-W301                     | . 7 |

|   | 1.   | 4.2  | NORA-W306                     | . 7 |

|   | 1.5  | Rad  | io performance                | .8  |

|   | 1.6  | CPL  | J                             | . 8 |

|   |      |      | Open CPU software             |     |

|   | 1.   | 6.2  | Software upgrade              | . 9 |

|   | 1.7  | MA   | C addresses                   | . 9 |

|   |      |      | er modes                      |     |

| 2 | In   | terf | aces                          | I C |

|   | 2.1  | Pow  | er supply                     | 1 C |

|   | 2.2  | Low  | power clock                   | 1 C |

|   | 2.3  | Mod  | lule reset                    | 1 C |

|   | 2.4  | Boo  | tstrap pins                   | 1 C |

|   | 2.5  | RF a | antenna interface             | 1 C |

|   |      | 5.1  | Internal antenna              |     |

|   |      |      | External RF antenna interface |     |

|   |      |      | ignals                        |     |

|   |      |      | PWM timer                     |     |

|   | 2.7  | Data | a interfaces                  | 11  |

|   | 2.   | 7.1  | USI                           | 11  |

|   | 2.   | 7.2  | I2C                           | 11  |

|   | 2.   | 7.3  | 125                           | 12  |

|   | 2.   |      | IR                            |     |

|   | 2.   | 7.5  | Key-scan                      | 12  |

|   | 2.   | 7.6  | Q-decoder                     | 12  |

|   | 2.   |      | RTC                           |     |

|   |      |      | SDIO                          |     |

|   |      |      | SPI                           |     |

|   | 2.   | 7.10 | SPI Flash                     | 13  |

|   |      |      | UART                          |     |

|   |      |      | USB                           |     |

|   | 2.   | 7.13 | Wake sources                  | 13  |

|   | 2.8  | Ana  | log interfaces                | 14  |

|   | 2.8.1   | ADC                                 | 14 |

|---|---------|-------------------------------------|----|

|   | 2.9 Del | oug interface                       | 14 |

|   | 2.9.1   | SWD                                 | 14 |

| 3 | Pin d   | efinition                           | 15 |

|   | 3.1 NO  | RA-W3 pin definition                | 15 |

|   | 3.1.1   | NORA-W30 open CPU pin assignments   | 15 |

| 4 | Elect   | rical specifications                | 20 |

|   | 4.1 Ab  | solute maximum ratings              | 20 |

|   | 4.1.1   | ESD characteristics                 | 20 |

|   | 4.2 Red | commended operating conditions      | 20 |

|   | 4.2.1   | Operating temperature               | 20 |

|   | 4.2.2   | Supply / power pins                 | 20 |

|   | 4.2.3   | I2C pull-up resistor values         | 21 |

|   | 4.2.4   | nRESET pin                          |    |

|   | 4.2.5   | Low frequency clock                 | 21 |

|   | 4.2.6   | Digital pins                        | 21 |

|   | 4.2.7   | Current consumption                 |    |

|   | 4.2.8   | Wi-Fi radio characteristics         | 22 |

|   | 4.2.9   | Bluetooth LE characteristics        |    |

|   | 4.2.10  | ) Antenna radiation patterns        | 24 |

| 5 | Mech    | nanical specifications              | 26 |

|   |         | RA-W30 footprint dimensions         |    |

|   | 5.2 NO  | RA-W30 mechanical specifications    |    |

|   | 5.2.1   | NORA-W301 mechanical specifications |    |

|   | 5.2.2   | NORA-W306 mechanical specifications |    |

| 6 | Quali   | fications and approvals             | 28 |

|   | 6.1 Co  | untry approvals                     | 28 |

|   |         | etooth qualification                |    |

|   | 6.3 Env | vironmental                         |    |

|   | 6.3.1   | RoHS                                |    |

|   | 6.3.2   | REACH                               |    |

|   |         | tennas                              |    |

| 7 |         | uct handling                        |    |

|   | 7.1 Pag | ckaging                             |    |

|   | 7.1.1   | Reels                               |    |

|   | 7.1.2   | Tapes                               |    |

|   |         | isture sensitivity levels           |    |

|   |         | flow soldering                      |    |

|   |         | D precautions                       |    |

| 8 | Labe    | ling and ordering information       | 33 |

|   |         | oduct labeling                      |    |

|   | 8.2 Ord | dering information                  | 33 |

| Αp       | pendix               | 34 |

|----------|----------------------|----|

| Α        | Glossary             | 34 |

|          | elated documentation |    |

| Re       | evision history      | 35 |

| <u>_</u> | ntoct                | 25 |

## 1 Functional description

### 1.1 Overview

The NORA-W3 series comprises small, stand-alone, dual-band Wi-Fi™ and Bluetooth® Low Energy modules that are perfect for integrating wireless connectivity into end products.

With Wi-Fi 4 (IEEE 802.11a/b/g/n) in the 2.4 and 5 GHz bands it can be a Wi-Fi station connecting to a remote access point or act as an access point. It can assume peripheral or central roles, or both simultaneously. It can be a GATT client or server.

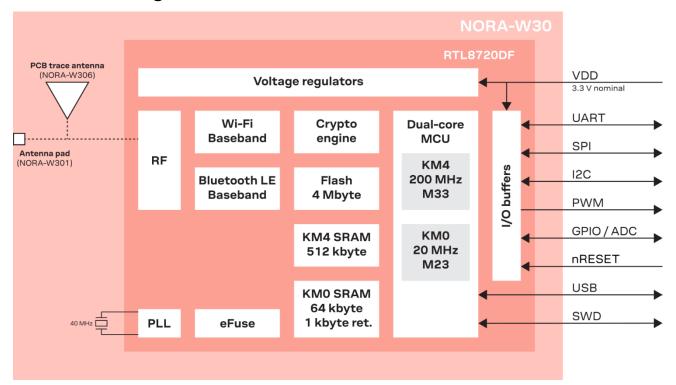

The module embeds a dual-core MCU, with a powerful Arm® Cortex®-M33 compatible processor for the main application and an Arm Cortex-M23 compatible processor for low power operation.

The NORA-W30 series includes hardware security features like secure boot, trusted execution environment with Arm TrustZone®, encrypted flash, protection of debug port, and a crypto acceleration engine. The wireless communication can be secured with WPA2/WPA3 authentication, TLS 1.2/1.3 encryption, Bluetooth LE secure connection pairing, and HTTPS.

The modules are suitable for a wide range of applications, including industrial automation, smart cities, smart buildings and homes, metering and utilities, healthcare, and Electrical Vehicle (EV) charging.

NORA-W306 comes with an internal PCB antenna while NORA-W301 has a module pin to connect to an external antenna of choice. The internal PCB antenna provides a robust low-profile solution with high performance and an extensive range. The NORA-W30 series is globally certified for use with the internal antenna or a range of external antennas, which reduces time, cost and effort for customers integrating Wi-Fi and Bluetooth low energy in their designs.

NORA-W30 modules have the same physical dimensions as other NORA modules and have critical pins and interfaces at the same positions. This offers maximum flexibility for the development of similar end-devices with different radio technologies. The modules support operation in an extended temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C and are qualified for professional grade applications. NORA-W30 is verified against Bluetooth Core 5.3.

Approval for NORA-W30 is currently pending in some countries. See also Country approvals.

## 1.2 Applications

NORA-W30 series are suitable for a wide range of applications, including:

- Wi-Fi networks

- Internet of Things (IoT)

- · Bluetooth Low Energy applications

- Metering and utilities

- Point-of-sales

- Healthcare

- Access to laptops, mobile phones, and similar consumer devices

- · Smart buildings and homes

- EV charging

## 1.3 Block diagram

Figure 1: NORA-W30 series block diagram

### 1.4 Product variants

NORA-W30 modules have an open CPU architecture that is tailored towards OEMs that want to embed Wi-Fi 802.11a/b/g/n and Bluetooth Low Energy 5.3 in the 2.4 GHz ISM band into their own application. NORA-W30 product variants share the same pin-out, footprint, and size of 14.3 mm  $\times$  10.4 mm  $\times$  1.9 mm.

### 1.4.1 NORA-W301

NORA-W301 has no internal antenna. The RF signal for routing to an external antenna or antenna connector signal is exposed through a dedicated module pin.

### 1.4.2 NORA-W306

NORA-W306 is equipped with an internal PCB trace antenna, using antenna technology licensed from Abracon. The RF signal is not connected to any module pin.

## 1.5 Radio performance

The radio provides support for Wi-Fi 4, IEEE 802.11a/b/g/n in the 2.4 GHz and 5 GHz ISM bands and Bluetooth LE communication in the 2.4 GHz ISM band, as shown in Table 1.

| Wi-Fi                                                                                                                                                                                                | Bluetooth Low Energy                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| IEEE 802.11a/b/g/n                                                                                                                                                                                   | Bluetooth LE 5.3                                                           |

| Band support Station mode: 2.4 GHz, channels 1-13*, (14 Japan only)** 5 GHz, channels 36-165*                                                                                                        | Band support<br>2.4 GHz, 40 channels                                       |

| Access Point mode:<br>2.4 GHz, channels 1-13*, (14 Japan only)*<br>5 GHz, channels 36-48, 149-165*                                                                                                   |                                                                            |

| Typical conducted output power:<br>2.4 GHz, 20 dBm<br>5 GHz, 18 dBm                                                                                                                                  | Typical conducted output power<br>8 dBm (NORA-W306)<br>6.5 dBm (NORA-W301) |

| Typical radiated output power:<br>2.4 GHz, 25.3 dBm EIRP**<br>5 GHz, 23.3 dBm EIRP**                                                                                                                 | Typical radiated output power 11.8 dBm EIRP**                              |

| Conducted sensitivity 802.11b, -98 dBm (1 Mbps) 802.11g, -95 dBm (6 Mbps) 802.11a, -93 dBm (6 Mbps) 802.11n, -95 dBm (2.4GHz, MCS 0) 802.11n, -93 dBm (5GHz, MCS 0)                                  | Conducted sensitivity<br>LE1M, –101 dBm<br>LE2M, –97 dBm                   |

| Data rates:<br>IEEE 802.11a:<br>6/9/12/18/24/36/48/54 Mbps<br>IEEE 802.11b:<br>1/2/5.5/11 Mbps<br>IEEE 802.11g:<br>6/9/12/18/24/36/48/54 Mbps<br>IEEE 802.11n:<br>MCS 0-7, HT20 (6.5-150 Mbps), HT40 | Data rates:<br>1 / 2 Mbps                                                  |

<sup>\*</sup> Maximum support depends on the region.

#### Table 1: NORA-W30 series Wi-Fi and Bluetooth characteristics

### 1.6 CPU

NORA-W30 embeds a dual-core MCU, with a powerful Arm Cortex-M33 compatible processor running at 200 MHz for the main application and an Arm Cortex-M23 compatible processor running at 20 MHz for low power operation.

The main features of the internal NORA-W30 memory include:

- 4 Mbyte flash for applications

- 512 kbyte RAM for the main core

- 64 kbyte RAM for the low power core

- Arm TrustZone hardware encryption to protect programs

<sup>\*\*</sup> RF power including maximum antenna gain (2.4 GHz – 5.3 dBi, 5 GHz – 5.3 dBi).

### 1.6.1 Open CPU software

NORA-W30 series modules are not supplied with any application software but include an open-CPU architecture that allows customers to develop advanced applications running on the dual core 32-bit MCU.

NORA-W30 series modules can be used to design solutions with top-grade security. Including integrated cryptographic hardware accelerators, the modules feature secure boot functionality that ensures that the module can only be restarted with authenticated software.

### 1.6.2 Software upgrade

A bootloader is included in ROM. When upgrading the module firmware, see also the NORA-W30 system integration manual [1].

### 1.7 MAC addresses

NORA-W30 series modules are assigned a block of four MAC addresses. The lowest number is encoded in the 2D data matrix printed on the label. The remaining are intended to be calculated by the application according to Table 2.

| MAC address      | Assignment                  | Remarks                                             |

|------------------|-----------------------------|-----------------------------------------------------|

| Base address     | Wi-Fi station               | Printed on label data matrix. See Product labeling. |

| Base address + 1 | Wi-Fi access point          | Calculated by application                           |

| Base address + 2 | Bluetooth LE device address | Calculated by application                           |

| Base address + 3 | Unused                      |                                                     |

Table 2: MAC addresses

### 1.8 Power modes

NORA-W30 series modules are power efficient devices capable of operating in different power saving modes and configurations. Different sections of the module can be powered off when they are not needed, and complex wake up events can be generated from different external and internal inputs.

NORA-W30 series modules have three power modes: active, sleep, and deep-sleep as noted in the Realtek UM0401 RTL872xD data sheet [2].

| Power mode | Description               | Conditions            |  |

|------------|---------------------------|-----------------------|--|

| Active     | Normal operation          |                       |  |

| Sleep      | Processor clock idle      | All SRAM retained     |  |

|            | System clock running      | Interrupts on         |  |

|            |                           | All I/O retained      |  |

| Deep-sleep | System clock halted       | 1 kbyte SRAM retained |  |

|            | PLL switched off          | Interrupts off        |  |

|            | Flash memory switched off | 7 GPIO retained       |  |

Table 3: Power modes

For more information about power modes, see the Realtek RTL872xD data sheet [2] and Ameba-D application note [3].

## 2 Interfaces

## 2.1 Power supply

The power for NORA-W30 series modules is supplied through **VDD** pins with a nominal voltage of 3.3 VDC. The input voltage is also the input / output (I/O) reference voltage for interfacing external circuitry.

⚠

The system power supply circuit must be able to support peak power. As the current drawn from **VDD** can vary significantly based on Wi-Fi and Bluetooth LE power consumption profiles.

NORA-W30 series modules use an integrated voltage converter to transform and stabilize the supply voltage applied to the **VDD** pin. The voltage converter operates in linear low drop-out mode (LDO) or switching power supply (SPS) mode. SPS is the default mode.

### 2.2 Low power clock

NORA-W36 series modules have an internal low frequency clock which is derived from the main clock. If low power modes are required, an external 32.768 kHz LPO signal, **EXT\_32K**, can be supplied externally.

### 2.3 Module reset

NORA-W30 series modules can be reset (rebooted) with a low-level input on the **nRESET** pin. See also the NORA-W30 series system integration manual [1].

## 2.4 Bootstrap pins

Pins B1 (**PA30**), H2 (**SWD\_DATA**), and A5 (**PA7**) are used to configure the boot mode. Default is pulled high for best power efficiency, booting normally from internal flash. See also the NORA-W30 series system integration manual [1].

### 2.5 RF antenna interface

The RF antenna interface of NORA-W30 modules supports Wi-Fi and Bluetooth LE on the same antenna. The different communication protocols are time divided on the antenna to switch between the Bluetooth and Wi-Fi data. Although communication using these different protocols is (more or less) transparent in the application, these protocols are never active at the same time in the module antenna.

NORA-W30 series modules support either an internal antenna (NORA-W306) or external antennas connected through a dedicated antenna pin (NORA-W301).

### 2.5.1 Internal antenna

NORA-W306 modules have internal antennas that are specifically designed and optimized for NORA modules. NORA-W306 is equipped with a dual-band PCB trace antenna tuned for the 2.4 GHz and 5 GHz ISM bands.

For more information about antenna-related design, see also the NORA-W30 series system integration manual [1].

⚠

The ANT signal solder pin is not available on the NORA-W306 module.

### 2.5.2 External RF antenna interface

The NORA-W301 module has an antenna signal (**ANT**) pin with a characteristic impedance of 50  $\Omega$  for using an external antenna. The antenna signal supports both Tx and Rx.

The external antenna, for example, can be an SMD antenna (or PCB integrated antenna) on the host board. An antenna connector for use with an external antenna through a coaxial cable could also be implemented. A cable antenna might be necessary if the module is mounted in a shielded enclosure such as a metal box or cabinet.

An external antenna connector (U.FL connector) reference design is available and must be followed to comply with the NORA-W30 FCC/ISED modular approvals. See the NORA-W30 series system integration manual [1] for the U.FL reference design and the list of approved antennas.

### 2.6 IO signals

NORA-W30 series modules have 20 pins available for general purpose input / output (GPIO). Specific functions are available on selected pins. A limited combination of data interfaces may be used at one time. For available assignments, see Pin definition and the system integrations manual [1].

### 2.6.1 PWM timer

The Pulse Width Modulation (PWM) timer consists of a 16-bit auto-reload up-counter driver by an 8-bit prescaler. It can be used for a variety of purposes, including measuring input pulse lengths (input capture) and generating output waveforms (PWM) that can be used to drive RGB LED devices.

The PWM controller is available on 12 high speed GPIO channels and 6 low power GPIO channels.

### 2.7 Data interfaces

Data interfaces are described in detail in the Realtek RTL8720DF data sheet [2] and user manual [3].

#### 2.7.1 USI

The Universal Serial Interface (USI) is a high-speed peripheral that can be assigned as a universal asynchronous receiver transmitter (UART), a main or sub node interintegrated circuit (I2C), or a main or sub node serial peripheral interface (SPI). Use of the USI is in addition to other available UART, I2C or SPI instances, depending on GPIO pin availability.

One USI instance is available. It is a high-speed peripheral that powers down in sleep and deep sleep modes.

### 2.7.2 I2C

The Inter-Integrated Circuit (I2C) bus is a two-wire serial interface consisting of serial data (SDA) and serial clock (SCL) signals. These signals carry information between devices connected to the bus. Each device is recognized by a unique address and can operate as either a transmitter or receiver, depending on the function of the device. Devices can also be considered as main or sub nodes when performing data transfers. A main node device initiates a data transfer on the bus and generates the clock signal to permit the transfer. At that time, any device addressed is considered a sub node.

Each I2C interface can only be programmed to operate in either a main or sub node. Operating main or sub nodes simultaneously is not supported.

Three I2C instances are available. One high-speed and one associated with the USI power off in sleep and deep sleep modes. The low power instance powers off in sleep mode. When used as a sub node, the low-power instance can be used to wake NORA-W30 from sleep mode upon a decoded address match.

### 2.7.3 I2S

Inter-IC Sound (I2S) is a serial bus standard used for communication with digital audio devices. It communicates audio data between integrated circuits in an electronic device. The I2S bus separates clock and serial data signals, resulting in a lower jitter than typical communication systems that recover the clock from the data stream.

The I2S interface can operate as main or sub nodes, as a receiver, or a transmitter. It can address three different audio standards including the I2S Philips standard, the left-justified standard, and the right-justified standard.

One I2S instance is available. It is a high-speed peripheral and powers off sleep and deep sleep modes.

### 2.7.4 IR

The Infrared Radiation (IR) interface is designed to process IR signals with carrier frequencies of under 500 kHz. The hardware interface supports modulation with can be used on the IR transmission. It can also detect the period of continuous high- or low-level signal and record it in the RX FIFO. Application code then processes the serial signal.

One IR interface is available. It is a high-speed peripheral and powers off in sleep and deep sleep modes.

### 2.7.5 Key-scan

The key-scan interface automatically scans a keypad matrix and generates interrupts on activity. This frees the CPU from scanning a keypad from within an application. Key arrangements of up to  $5 \times 2$  or  $4 \times 3$  are supported.

One key-scan instance is available. It is a low-power peripheral that remains powered in sleep and deep sleep modes and can be used as a wake source.

### 2.7.6 Q-decoder

The Quadrature Decoder (Q-decoder or QDEC) interface is used to determine the position and speed of rotary devices, such as servomotors, volume control wheels, and PC mice. The decoded signals are used as sensory input to a system to determine the absolute or relative position of a rotary device, which can be used in a control loop.

One Q-decoder instance is available. It is a low power peripheral that is powered off in deep sleep.

#### 2.7.7 RTC

The Real-Time Clock (RTC) is an independent Binary Coded Decimal (BCD) timer/counter. One 32-bit register contains seconds, minutes, hours (12- or 24-hour format) expressed in BCD format. A second 32-bit register contains the days expressed in binary format. RTC clock sources are derived from the system clock or low power clock, or **EXT\_32K**, logic-level low frequency (32.768 kHz) clock input. **RTC\_OUT** can be used as an alarm output.

One RTC instance is available. It is a low power peripheral that runs in all states – active, sleep, and deep sleep – and can be used as a wake source.

### 2.7.8 SDIO

Secure Digital Input / Output (SDIO) is a fast, 4-bit interface and may operate as a host or device with a clock rate of up to 50 MHz. SDIO 2.0 SDR25 (25 Mbytes / sec) is supported. SDIO can operate as a SD card host. INIC mode is supported for SDIO to Wi-Fi transformation.

One SDIO instance is available. It is a high-speed peripheral that is powered off in deep sleep mode.

#### 2.7.9 SPI

The serial peripheral interface (SPI) is a synchronous serial communication consisting of four signals: clock (CLK), chip select (CS), main-in-sub-out (MISO) data, and main-out-sub-in (MOSI) data.

Three SPI instances are available, each operating as a main or sub mode. SPI0 can be configured with a maximum rate of 50 Mbps. SPI1 has a maximum rate of 25 Mbps. The third SPI port is associated with the USI peripheral, with a maximum rate of 50 Mbps. All SPI ports are powered off in sleep and deep sleep modes.

#### 2.7.10 SPI Flash

The SPI Flash interface is a 4-bit memory interface that manages CPU instruction and data code access to external flash memory. It implements erase and program memory operations and read/write protection mechanisms. It accelerates code execution with a system of instruction and prefetch cache lines.

One SPI Flash instance is available. It is powered off in deep sleep mode.

#### 2.7.11 UART

The Universal Asynchronous Receiver Transmitter (UART) is an asynchronous serial interface consisting of up to four signals – transmit data (TXD), receive data (RXD), request-to-send (RTS) handshake, and clear-to-send (CTS) handshake. The handshake signals are optional, though recommended at higher speeds.

Four UART instances are available. One is a high-speed peripheral. One is associated with the USI. Two are low-power peripherals. All UARTs are powered off in deep sleep.

### 2.7.12 USB

The Universal Serial Bus (USB v2.0) utilizes two data signals as a bidirectional, differential pair to connect host computers and peripheral devices. The USB interface is provided through the **HSDM** and **HSDP** signals. **RREF** is an analog reference for the USB interface, connected to a 12.0 k $\Omega$  resistor to ground.

One USB peripheral interface is available to operate in either host or device mode. High-speed (HS, up to 480 Mbps), full-speed (FS, up to 12 Mbps), and low-speed (LS, up to 1.5 Mbps) modes are supported. The USB peripheral is powered off in sleep and deep sleep modes.

### 2.7.13 Wake sources

NORA-W30 can wake from sleep by the sources described in Table 4.

| Peripheral Source Remarks |                                                | Remarks |

|---------------------------|------------------------------------------------|---------|

| HS_UART                   | JART Receive activity                          |         |

| LP_UART                   | Receive activity                               |         |

| COMP or ADC               | Analog input level interrupt                   |         |

| I2C                       | Wake on address match I2C target mode only     |         |

| BOD                       | Brown-out event                                |         |

| WLAN                      | Wake on beacon interval Default 102.4 ms       |         |

| GPIO                      | PA[12], PA[13], PA[14], PA[15], PA[25], PA[26] |         |

| TIMER                     | Wake on timer event                            |         |

| AON                       | After deep sleep wake event See Table 5        |         |

|                           |                                                |         |

Table 4: Wake sources

NORA-W30 can wake from deep sleep by the sources described in Table 5.

| Peripheral | Source Remarks                                 |  |  |

|------------|------------------------------------------------|--|--|

| PDB        | Power down event                               |  |  |

| KEYSCAN    | Key press on configured GPIOs                  |  |  |

| TSF        | WLAN Time sync                                 |  |  |

| RTC        | Real time clock event                          |  |  |

| AON_TIMER  | Wake after a predetermined interval            |  |  |

| AON_GPIO   | PA[12], PA[13], PA[14], PA[15], PA[25], PA[26] |  |  |

Table 5: Deep sleep wake sources

## 2.8 Analog interfaces

### 2.8.1 ADC

A 12- bit Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) is available on three GPIO pins. The input range is 0 V to 3.3 V. The maximum conversion rate is 1 M samples / second. The ADC remains on in sleep and deep sleep modes and can be used as a wake source.

The ADC inputs are available on pins PB[1] (ADC4), PA[2] (ADC5), and PB[3] (ADC6).

## 2.9 Debug interface

### 2.9.1 SWD

NORA-W30 series uses the Arm® Serial Wire Debug (SWD) interface (**SWD\_DATA** and **SWD\_CLK**) for programming and debugging both cores of the Realtek RTL8720DF within the module.

## 3 Pin definition

## 3.1 NORA-W3 pin definition

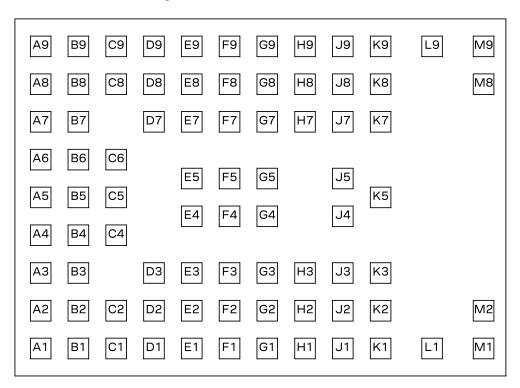

**TOP VIEW**

Figure 2: Pin layout

## 3.1.1 NORA-W30 open CPU pin assignments

Table 6 describes the NORA-W30 open CPU module pin assignments.

| No | Name   | I/O¹    | Boot strap | Alternate functions                                             |

|----|--------|---------|------------|-----------------------------------------------------------------|

| A1 | VSS    | Power   |            |                                                                 |

| A2 | n/c    | -       |            |                                                                 |

| А3 | n/c    | -       |            |                                                                 |

| A4 | n/c    | -       |            |                                                                 |

| A5 | PA[7]  | I/O, PU | UART_DL    | UART_LOG_TXD                                                    |

| A6 | PA[8]  | I/O, PU |            | UART_LOG_RXD                                                    |

| Α7 | VDD    | Power   |            | 3.0 VDC to 3.6 VDC power supply input and I/O reference voltage |

| A8 | VDD    | Power   |            | 3.0 VDC to 3.6 VDC power supply input and I/O reference voltage |

| A9 | VSS    | Power   |            |                                                                 |

| B1 | PA[30] | I/O, PU | SPS_SEL    | HS_USI_SPI_CLK, HS_PWM7, LP_PWM1                                |

| B2 | VSS    | Power   |            |                                                                 |

| В3 | PA[28] | I/O     |            | LP_UART_CTS, HS_USI_SPI_CS, HS_PWM6, LP_PWM0, RREF              |

| В4 | n/c    | -       |            |                                                                 |

<sup>&</sup>lt;sup>1</sup> I/O notations: I=Input only, I/O=Input or Output, PU=Pull Up, AI=Analog Input, n/c=Not Connected

| No | Name   | I/O <sup>1</sup> | Boot strap | Alternate functions                                                                                          |

|----|--------|------------------|------------|--------------------------------------------------------------------------------------------------------------|

| B5 | n/c    | -                |            |                                                                                                              |

| В6 | n/c    | -                |            |                                                                                                              |

| В7 | VDD    | Power            |            |                                                                                                              |

| B8 | VSS    | Power            |            |                                                                                                              |

| В9 | n/c    | -                |            |                                                                                                              |

| C1 | PA[26] | I/O              |            | LP_UART_TXD, HS_USI_SPI_MISO, IR_RX, LP_I2C_SDA, HS_PWM5, LP_PWM5, HSDP                                      |

| C2 | PA[25] | I/O              |            | LP_UART_RXD, HS_USI_SPI_MOSI, IR_TX, LP_I2C_SCL, HS_PWM4, LP_PWM4, HSDM                                      |

| C4 | n/c    | -                |            |                                                                                                              |

| C5 | n/c    | -                |            |                                                                                                              |

| C6 | n/c    | -                |            |                                                                                                              |

| C8 | PB[23] | I/O              |            | LP_TIM5_TRIG, SPI_DATA2, SD_D1, HS_PWM15, LP_PWM3, I2S_MCLK, QDEC_PHA, EXT_32K                               |

| C9 | n/c    | -                |            |                                                                                                              |

| D1 | n/c    | -                |            |                                                                                                              |

| D2 | n/c    | -                |            |                                                                                                              |

| D3 | n/c    | -                |            |                                                                                                              |

| D7 | n/c    | -                |            |                                                                                                              |

| D8 | PB[1]  | I/O, AI          |            | LP_UART_TXD, HS_TIM4_TRIG                                                                                    |

| D9 | n/c    | -                |            |                                                                                                              |

| E1 | n/c    | -                |            |                                                                                                              |

| E2 | n/c    | -                |            |                                                                                                              |

| E3 | n/c    | -                |            |                                                                                                              |

| E4 | VSS    | Power            |            |                                                                                                              |

| E5 | VSS    | Power            |            |                                                                                                              |

| E7 | n/c    | -                |            |                                                                                                              |

| E8 | PB[2]  | I/O, AI          |            | LP_UART_RXD, HS_TIM5_TRIG                                                                                    |

| E9 | PB[22] | I/O              |            | LP_TIM4_TRIG, SPI_DATA3, SD_D0, HS_PWM14, LP_PWM2, I2S_SD_RX, QDEC_PHB                                       |

| F1 | n/c    | -                |            |                                                                                                              |

| F2 | n/c    | -                |            |                                                                                                              |

| F3 | n/c    | -                |            |                                                                                                              |

| F4 | VSS    | Power            |            |                                                                                                              |

| F5 | VSS    | Power            |            |                                                                                                              |

| F7 | n/c    | -                |            |                                                                                                              |

| F8 | PB[21] | I/O              |            | HS_USI_UART_RXD, HS_UARTO_RTS, SPIO_CS, SPI_CLK, HS_USI_I2C_SDA, SD_CLK, HS_PWM13, LP_PWM1, I2S_WS, QDEC_IDX |

| F9 | PB[20] | I/O              |            | HS_USI_UART_TXD, HS_UARTO_CTS, SPIO_CLK, SPI_DATA0, HS_USI_I2C_SCL, SD_CMD, HS_PWM12, LP_PWM0, I2S_CLK       |

| G1 | n/c    | -                |            |                                                                                                              |

| G2 | n/c    | -                |            |                                                                                                              |

| G3 | n/c    | -                |            |                                                                                                              |

| G4 | n/c    | -                |            |                                                                                                              |

| G5 | n/c    | -                |            |                                                                                                              |

| G7 | n/c    | -                |            |                                                                                                              |

| G8 | PB[19] | I/O              |            | HS_UARTO_TXD, HS_USI_UART_CTS, SPI0_MISO, SPI_DATA1, SD_D3, HS_PWM11, LP_PWM5, SWD_DATA, I2S_SD_TX0          |

| No | Name   | I/O <sup>1</sup> | Boot strap | Alternate functions                                                                 |

|----|--------|------------------|------------|-------------------------------------------------------------------------------------|

| G9 | PB[18] | I/O              |            | HS_UARTO_RXD, HS_USI_UART_RTS, SPIO_MOSI, SPI_CS, SD_D2, HS_PWM10, LP_PWM4, SWD_CLK |

| H1 | n/c    | -                |            |                                                                                     |

| H2 | PA[27] | I/O, PU          | BL_EN      | SWD_DATA (Default), LP_UART_RTS                                                     |

| НЗ | n/c    | -                |            |                                                                                     |

| H7 | n/c    | -                |            |                                                                                     |

| Н8 | PA[15] | I/O              |            | LP_UART_CTS, SPI1_CS, KEY_ROW2, KEY_COL6                                            |

| Н9 | PA[14] | I/O              |            | LP_UART_RTS, SPI1_CLK, I2S_SD_TX2, KEY_ROW2, RTC_OUT                                |

| J1 | n/c    | -                |            |                                                                                     |

| J2 | PB[3]  | I/O, AI          |            | SWD_CLK (Default)                                                                   |

| J3 | nRESET | I, PU            |            |                                                                                     |

| J4 | n/c    | -                |            |                                                                                     |

| J5 | n/c    | -                |            |                                                                                     |

| J7 | n/c    | -                |            |                                                                                     |

| J8 | PA[13] | I/O              |            | LP_UART_RXD, SPI1_MISO, HS_PWM1, LP_PWM1, I2S_SD_TX1, KEY_ROW1                      |

| J9 | PA[12] | I/O              |            | LP_UART_TXD, SPI1_MOSI, HS_PWM0, LP_PWM0, I2S_MCLK, KEY_ROW0                        |

| K1 | n/c    | -                |            |                                                                                     |

| K2 | VSS    | Power            |            |                                                                                     |

| К3 | VSS    | Power            |            |                                                                                     |

| K5 | VSS    | Power            |            |                                                                                     |

| K7 | VSS    | Power            |            |                                                                                     |

| K8 | VSS    | Power            |            |                                                                                     |

| K9 | ANT    | I/O              |            | $50\Omega$ Single-ended antenna connection, only connected on NORA-W301             |

| L1 | VSS    | Power            |            |                                                                                     |

| L9 | VSS    | Power            |            |                                                                                     |

| M1 | VSS    | Power            |            |                                                                                     |

| M2 | VSS    | Power            |            |                                                                                     |

| M8 | VSS    | Power            |            |                                                                                     |

| M9 | VSS    | Power            |            |                                                                                     |

|    |        |                  |            |                                                                                     |

### Table 6: NORA-W30 open CPU pinout table

The alternate pin functions are described in Table 7.

Only certain functions may be enabled at one time. For more information about pin multiplexing, see also the system integration guide [1].

| Signal   | 1/0 | Description                       |  |

|----------|-----|-----------------------------------|--|

| EXT_32K  | 0   | 32.768 kHz clock output           |  |

| HSDM     | I/O | USB data signal minus             |  |

| HSDP     | I/O | USB data signal plus              |  |

| HS_PWM0  | 0   | High speed PWM output, channel 0  |  |

| HS_PWM1  | 0   | High speed PWM output, channel 1  |  |

| HS_PWM4  | 0   | High speed PWM output, channel 4  |  |

| HS_PWM5  | 0   | High speed PWM output, channel 5  |  |

| HS_PWM6  | 0   | High speed PWM output, channel 6  |  |

| HS_PWM7  | 0   | High speed PWM output, channel 7  |  |

| HS_PWM10 | 0   | High speed PWM output, channel 10 |  |

| HS_PWM11 | 0   | High speed PWM output, channel 11 |  |

| Signal          | I/O | Description                                               |

|-----------------|-----|-----------------------------------------------------------|

| HS_PWM12        | 0   | High speed PWM output, channel 12                         |

| HS_PWM13        | 0   | High speed PWM output, channel 13                         |

| HS_PWM14        | 0   | High speed PWM output, channel 14                         |

| HS_PWM15        | 0   | High speed PWM output, channel 15                         |

| HS_TIM4_TRIG    | I   | High speed timer capture, channel 4                       |

| HS TIM5 TRIG    |     | High speed timer capture, channel 5                       |

| HS_UARTO_CTS    |     | High speed UARTO, clear to send                           |

| HS UARTO RTS    | 0   | High speed UARTO, ready to send                           |

| HS_UARTO_RXD    |     | High speed UARTO, receive data                            |

| HS_UARTO_TXD    | 0   | High speed UARTO, transmit data                           |

| HS_USI_I2C_SCL  | 0   | High speed universal serial interface, I2C clock          |

| HS_USI_I2C_SDA  | I/O | High speed universal serial interface, I2C data           |

| HS_USI_SPI_CLK  | 0   | High speed universal serial interface, SPI clock          |

| HS_USI_SPI_CS   | 0   | High speed universal serial interface, chip select        |

| HS_USI_SPI_MISO |     | High speed universal serial interface, main in sub out    |

| HS_USI_SPI_MOSI | 0   | High speed universal serial interface, main out sub in    |

| HS_USI_UART_CTS |     | High speed universal serial interface, UART clear to send |

| HS_USI_UART_RTS | 0   | High speed universal serial interface, UART ready to send |

| HS_USI_UART_RXD |     | High speed universal serial interface, UART receive data  |

| HS_USI_UART_TXD | 0   | High speed universal serial interface, UART transmit data |

| I2S_MCLK        | 0   | I2S main clock output                                     |

| I2S_SD_RX       |     | I2S data input                                            |

| I2S_SD_TX0      | 0   | I2S data output 0                                         |

| I2S_SD_TX1      | 0   | I2S data output 1                                         |

| I2S_SD_TX2      | 0   | I2S data output 2                                         |

| I2S_CLK         | I/O | I2S data clock                                            |

| I2S_WS          | I/O | I2S word select                                           |

| IR_RX           | I   | Infrared receive                                          |

| IR_TX           | 0   | Infrared transmit                                         |

| KEY_COL0        | 0   | Keypad column 0                                           |

| KEY_COL1        | 0   | Keypad column 1                                           |

| KEY_COL5        | 0   | Keypad column 5                                           |

| KEY_COL6        | 0   | Keypad column 6                                           |

| KEY_ROW0        | 1   | Keypad row 0                                              |

| KEY_ROW1        | 1   | Keypad row 1                                              |

| KEY_ROW2        | ı   | Keypad row 2                                              |

| KEY_ROW3        | 1   | Keypad row 3                                              |

| KEY_ROW4        | I   | Keypad row 4                                              |

| LP_I2C_SCL      | 0   | Low power I2C clock                                       |

| LP_I2C_SDA      | I/O | Low power I2C data                                        |

| LP_PWM0         | 0   | Low power PWM output, channel 0                           |

| LP_PWM1         | 0   | Low power PWM output, channel 1                           |

| LP_PWM2         | 0   | Low power PWM output, channel 2                           |

| LP_PWM3         | 0   | Low power PWM output, channel 3                           |

| LP_PWM4         | 0   | Low power PWM output, channel 4                           |

| LP_PWM5         | 0   | Low power PWM output, channel 5                           |

|                 |     |                                                           |

| Signal       | I/O | Description                                      |

|--------------|-----|--------------------------------------------------|

| LP_TIM4_TRIG | I   | Low power timer capture, channel 5               |

| LP_TIM5_TRIG | I   | Low power timer capture, channel 5               |

| LP_UART_CTS  | I   | Low power UART clear to send                     |

| LP_UART_RTS  | 0   | Low power UART request to send                   |

| LP_UART_RXD  | I   | Low power UART receive data                      |

| LP_UART_TXD  | 0   | Low power UART transmit data                     |

| QDEC_IDX     | I   | Quadrature decoded index pulse                   |

| QDEC_PHA     | I   | Quadrature decoded index phase A                 |

| QDEC_PHB     | I   | Quadrature decoded index phase B                 |

| RREF         | Al  | USB reference resistor, use 1% (value undefined) |

| SD_CLK       | 0   | SDIO clock                                       |

| SD_CMD       | 0   | SDIO command                                     |

| SD_D0        | I/O | SDIO data 0                                      |

| SD_D1        | I/O | SDIO data 1                                      |

| SD_D2        | I/O | SDIO data 2                                      |

| SD_D3        | I/O | SDIO data 3                                      |

| SPI0_CLK     | 0   | High speed SPI0, SPI clock                       |

| SPIO_CS      | 0   | High speed SPI0, chip select                     |

| SPI0_MISO    | I   | High speed SPI0, main in sub out                 |

| SPI0_MOSI    | 0   | High speed SPI0, main out sub in                 |

| SPI1_CLK     | 0   | High speed SPI1, SPI clock                       |

| SPI1_CS      | 0   | High speed SPI1, chip select                     |

| SPI1_MISO    | I   | High speed SPI1, main in sub out                 |

| SPI1_MOSI    | 0   | High speed SPI1, main out sub in                 |

| SPI_CLK      | 0   | Quad SPI clock                                   |

| SPI_CS       | 0   | Quad SPI chip select                             |

| SPI_DATA0    | I/O | Quad SPI data 0                                  |

| SPI_DATA1    | I/O | Quad SPI data 1                                  |

| SPI_DATA2    | I/O | Quad SPI data 2                                  |

| SPI_DATA3    | I/O | Quad SPI data 3                                  |

| SWD_CLK      | 0   | Serial wire debug clock                          |

| SWD_DATA     | I/O | Serial wire debug data                           |

| UART_LOG_RXD | I   | Debug UART receive data                          |

| UART_LOG_TXD | 0   | Debug UART transmit data                         |

|              |     |                                                  |

Table 7: Alternate function signal descriptions

## 4 Electrical specifications

Stressing the device above one or more of the ratings listed in the Absolute maximum ratings section may cause permanent damage. These are stress ratings only.

Operating the module at these or at any conditions other than those specified in the Recommended operating conditions should be avoided. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

**T**

All given application information is only advisory and does not form part of the specification.

## 4.1 Absolute maximum ratings

| Symbol               | Description                                     | Condition                    | Min  | Max  | Unit |

|----------------------|-------------------------------------------------|------------------------------|------|------|------|

| VDD                  | Module supply voltage                           | Input DC voltage at VDD pins | -0.3 | 3.63 | V    |

| I <sub>VDD MAX</sub> | Absolute maximum power consumption <sup>2</sup> | 3.3 VDC power supply         | У    | 800  | mA   |

| T <sub>STR</sub>     | Storage temperature                             |                              | -40  | +105 | °C   |

Table 8: Absolute maximum ratings

The product is not protected against overvoltage or reversed voltages. If necessary, voltage spikes exceeding the power supply voltage specification shown in Table 8 must be limited to values within the specified boundaries by using appropriate protection devices.

### 4.1.1 ESD characteristics

| Parameter                 | Min. | Typical Max. | Unit | Remarks               |

|---------------------------|------|--------------|------|-----------------------|

| Human body model (HBM)    |      | ±2000        | V    | JEDEC EIA/JESD22-A114 |

| Charge device model (CDM) |      | ±500         | V    | JEDED EIA/JESD22-C101 |

Table 9: ESD characteristics

## 4.2 Recommended operating conditions

### 4.2.1 Operating temperature

| Parameter             | Min. | Max. | Unit |

|-----------------------|------|------|------|

| Operating temperature | -40  | +105 | °C   |

Table 10: Temperature range

## 4.2.2 Supply / power pins

The input supply can operate at a nominal input voltage of 3.3 VDC.

| Symbol            | Parameter                  | Condition                                | Min  | Тур  | Max  | Unit |

|-------------------|----------------------------|------------------------------------------|------|------|------|------|

| VDD               | Input supply voltage       | Ambient temperature -40 °C to<br>+105 °C | 3.00 | 3.30 | 3.60 | V    |

| t <sub>PRDY</sub> | VDD ramp up to<br>1.76 VDC |                                          | 0.1  | 0.6  | 4.6  | ms   |

| t <sub>CORE</sub> | MCU HS core power ready    |                                          |      | 15   |      | ms   |

| t <sub>BOOT</sub> | MCU HS core boot time      |                                          | 200  | 200  |      | ms   |

Table 11: Input characteristics of voltage supply pins

$<sup>^2\,800</sup>$  mA @ 40 µsec during WLAN channel enable and change.

### 4.2.3 I2C pull-up resistor values

NORA-W30 series has configurable, internal pull-up and pull-down resistors. A minimum value of 4.7 k $\Omega$  may be selected on pins assigned to I2C functionality.

### 4.2.4 nRESET pin

| Pin name           | Parameter                   | Min | Тур | Max     | Unit |

|--------------------|-----------------------------|-----|-----|---------|------|

| nRESET             | Low-level input             | 0   |     | 0.2*VDD | V    |

|                    | Internal pull-up resistance |     | 10  |         | kΩ   |

| t <sub>RESET</sub> | Minimum nRESET low pulse    | 1   | 1   |         | ms   |

Table 12: nRESET pin characteristics

### 4.2.5 Low frequency clock

NORA-W36 series modules have an internal low frequency clock which is derived from the main clock. If low power modes are required, an external 32.768 kHz LPO signal – **EXT\_32K** – can be supplied externally. Voltage levels are defined at Digital pins.

| Symbol  | Parameter             | Min | Тур    | Max | Unit |

|---------|-----------------------|-----|--------|-----|------|

| EXT_32K | Input clock frequency |     | 32.768 |     | kHz  |

Table 13: External LPO clock characteristics

### 4.2.6 Digital pins

Digital pin specifications depend on the power supply voltage, VDD.

| Pin name        | Parameter                                   | Min | Тур | Max  | Unit | Remarks                             |

|-----------------|---------------------------------------------|-----|-----|------|------|-------------------------------------|

| Any digital pin | Input characteristic:<br>Low-level input    | 0   |     | 0.8  | V    |                                     |

|                 | Input characteristic:<br>high-level input   | 2.0 |     | VDD  | V    |                                     |

|                 | Output characteristic:<br>Low-level output  | 0   |     | 0.4  | V    |                                     |

|                 | Output characteristic:<br>High-level output | 2.4 |     | VDD  | V    |                                     |

|                 | Drive capability                            | 3.6 |     | 23.3 | mA   | For drive settings, see [2] and [3] |

|                 | Loading capacitance                         |     | 15  |      | pF   |                                     |

|                 | Pull-up/pull-down resistance                | 4.7 |     | 50   | kΩ   | For pull settings, see [2] and [3]  |

Table 14: Digital pin characteristics at VDD=3.3 VDC

### 4.2.7 Current consumption

The typical current consumption of a NORA-W30 module is shown in Table 15. The current consumption is highly dependent on the application implementation. All measurements taken with  $3.3 \, \text{V}$  supply at  $25 \, ^{\circ}\text{C}$  except as noted.

### The current consumption figures are inherited from the Realtek RTL 8720DF data sheet [2].

| Power mode | Activity                                                                | Min. | Тур. | Unit Remarks |

|------------|-------------------------------------------------------------------------|------|------|--------------|

| Wi-Fi      | Wi-Fi Tx packet P <sub>OUT</sub> 17 dBm,<br>Ch7/MCS0/Bandwidth 20 MHz   |      | 252  | mA           |

|            | Wi-Fi Tx packet P <sub>OUT</sub> 15 dBm,<br>Ch100/MCS0/Bandwidth 20 MHz |      | 300  | mA           |

|            | Wi-Fi Rx and listening                                                  |      | 63   | mA           |

| Power mode   | Activity                   | Min. | Тур. | Unit Remarks |

|--------------|----------------------------|------|------|--------------|

| Bluetooth LE | Bluetooth Tx Pout 8 dBm    |      | 100  | mA           |

|              | Bluetooth Rx and listening |      | 60   | mA           |

| Active       | CPU 200 MHz                |      | 20   | mA           |

|              | RF off                     |      |      |              |

| Sleep mode   | CPU idle                   |      | 75   | μΑ           |

|              | RF off                     |      |      |              |

|              | Interrupts on              |      |      |              |

|              | SRAM: all retained         |      |      |              |

|              | LP wake sources enabled    |      |      |              |

| Deep sleep   | CPU off                    |      | 10   | μΑ           |

| mode         | RF off                     |      |      |              |

|              | Interrupts off             |      |      |              |

|              | SRAM: 1Kbyte retained      |      |      |              |

|              | LP wake sources disabled   |      |      |              |

Table 15: Current consumption during typical use cases

### 4.2.8 Wi-Fi radio characteristics

$V_{DD}$  = 3.3 V,  $T_{amb}$  = 25 °C

| Parameter                          | Operation mode      |              | Specification                | Unit             |

|------------------------------------|---------------------|--------------|------------------------------|------------------|

| RF frequency range                 | 802.11a/n           |              | 5.180 – 5.825                | GHz              |

|                                    | 802.11b/g/n         |              | 2.412 – 2.472                | GHz              |

|                                    | 802.11b/g/n         | (Japan only) | 2.412 – 2.484                | GHz              |

| Modulation                         | 802.11b             |              | CCK and DSSS                 |                  |

|                                    | 802.11a/g/n         |              | OFDM                         |                  |

| Supported Data Rates               | 802.11a             |              | 6, 9, 12, 18, 24, 36, 48, 54 | Mbit/s           |

|                                    | 802.11b             |              | 1, 2, 5.5, 11                | Mbit/s           |

|                                    | 802.11g             |              | 6, 9, 12, 18, 24, 36, 48, 54 | Mbit/s           |

|                                    | 802.11n             |              | MCS0-MCS7                    |                  |

| Supported Bandwidth                | 802.11n             |              | 20, 40                       | MHz              |

| Supported Guard Interval           | 802.11n             |              | 400, 800                     | ns               |

| Conducted Transmit Power (typical) | 2.4 GHz CCK         | 1 Mbit/s     | 20                           | dBm <sup>*</sup> |

|                                    |                     | 11 Mbit/s    | 18                           | dBm <sup>*</sup> |

|                                    | 2.4 GHz OFDM        | 6 Mbit/s     | 19                           | dBm <sup>*</sup> |

|                                    |                     | 54 Mbit/s    | 17                           | dBm <sup>*</sup> |

|                                    | 2.4 GHz HT20 / HT40 | MCS0         | 18                           | dBm <sup>*</sup> |

|                                    |                     | MCS7         | 16                           | dBm <sup>*</sup> |

|                                    | 5 GHz OFDM          | 6 Mbit/s     | 18                           | dBm <sup>*</sup> |

|                                    |                     | 54 Mbit/s    | 14                           | dBm <sup>*</sup> |

|                                    | 5 GHz HT20 / HT40   | MCS0         | 16                           | dBm <sup>*</sup> |

|                                    |                     | MCS7         | 13                           | dBm <sup>*</sup> |

| Receiver Sensitivity (typical)     | 2.4 GHz CCK         | 1 Mbit/s     | -98                          | dBm              |

|                                    |                     | 11 Mbit/s    | -91                          | dBm              |

|                                    | 2.4 GHz OFDM        | 6 Mbit/s     | -95                          | dBm              |

|                                    |                     | 54 Mbit/s    | -77                          | dBm              |

|                                    | 2.4 GHz HT20        | MCS0         | -95                          | dBm              |

|                                    |                     | MCS7         | -75                          | dBm              |

|                                    | 2.4 GHz HT40        | MCS0         | <b>-93</b>                   | dBm              |

| Parameter | Operation mode |           | Specification | Unit |

|-----------|----------------|-----------|---------------|------|

|           |                | MCS7      | -72           | dBm  |

|           | 5 GHz OFDM     | 6 Mbit/s  | -93           | dBm  |

|           |                | 54 Mbit/s | -76           | dBm  |

|           | 5 GHz HT20     | MCS0      | -93           | dBm  |

|           |                | MCS7      | -74           | dBm  |

|           | 5 GHz HT40     | MCS0      | -91           | dBm  |

|           |                | MCS7      | -71           | dBm  |

<sup>\*</sup> There is lower output power on band edge channels and certain regulatory domains.

Table 16: Wi-Fi radio characteristics

### 4.2.9 Bluetooth LE characteristics

$V_{DD}$  = 3.3 V,  $T_{amb}$  = 25 °C

| Parameter                      | Specification                            | Unit |

|--------------------------------|------------------------------------------|------|

| RF Frequency Range             | 2.400 – 2.4835                           | GHz  |

| Supported Modes                | Bluetooth LE 5.3                         |      |

| Number of channels 40          |                                          |      |

| Modulation                     | GFSK                                     |      |

| Transmit Power (typical)       | 8 ± 1 (NORA-W306),<br>6.5 ± 1(NORA-W301) | dBm  |

| Receiver Sensitivity (typical) | -101 ± 2                                 | dBm  |

<sup>\*</sup> Conducted output power.

Table 17: Bluetooth LE characteristics

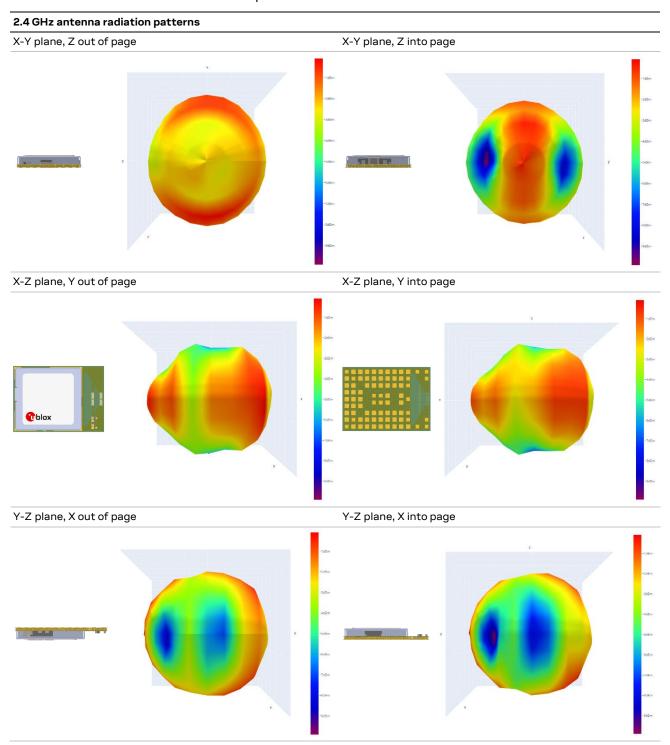

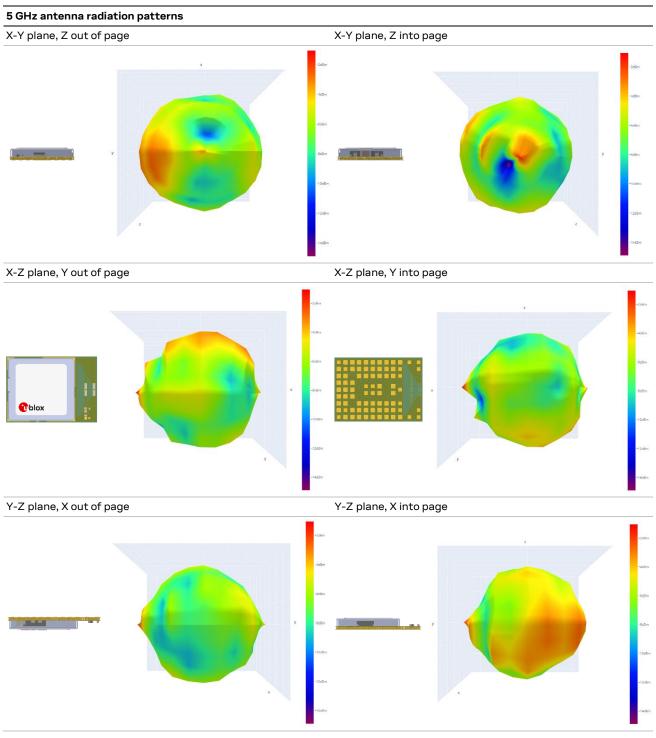

### 4.2.10 Antenna radiation patterns

Antenna patterns for approved antennas associated with NORA-W301 can be found in the respective antenna data sheet. See the NORA-W30 system integration manual [1] for the list of approved antennas.

Table 18 and Table 19 show radiation patterns for NORA-W306.

Table 18: NORA-W306 Wi-Fi and Bluetooth antenna characteristics in the 2.4 GHz band

Table 19: NORA-W306 Wi-Fi antenna characteristics in the 5 GHz band

## 5 Mechanical specifications

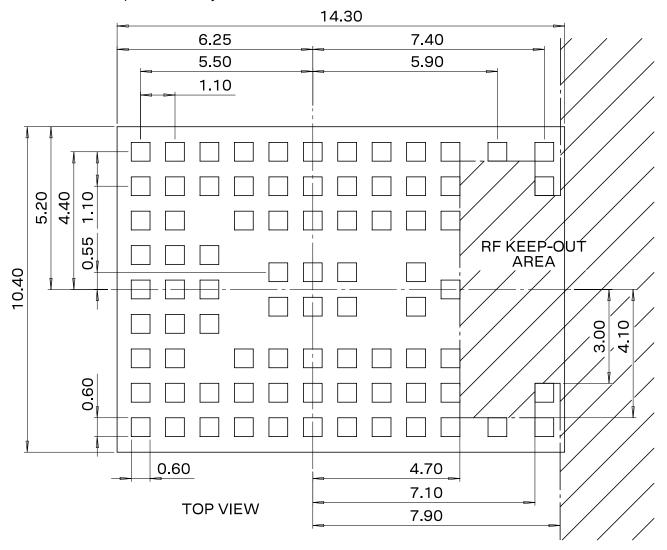

## 5.1 NORA-W30 footprint dimensions

Figure 3 shows the common footprint and dimensions of NORA-W30 series modules that are shared across the whole product family.

All dimensions in mm.

Figure 3: NORA-W30 footprint dimensions

The RF keep-out area is only required for NORA-W306 modules.

## 5.2 NORA-W30 mechanical specifications

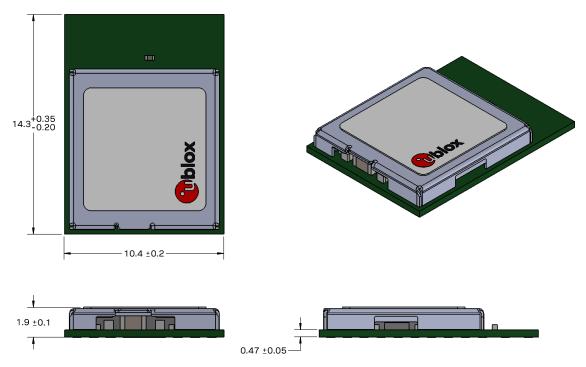

## 5.2.1 NORA-W301 mechanical specifications

Dimensions in mm

Figure 4: NORA-W301 mechanical specification

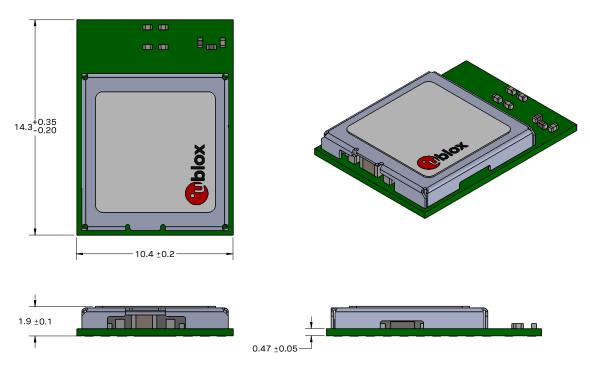

## 5.2.2 NORA-W306 mechanical specifications

Dimensions in mm

Figure 5: NORA-W306 mechanical specification

## 6 Qualifications and approvals

### 6.1 Country approvals

The NORA-W30 module series is certified for use in the countries/regions shown in

| Country                   | Agency | Approval |  |

|---------------------------|--------|----------|--|

| Europe                    | RED    | Approved |  |

| Great Britain             | UKCA   | Approved |  |

| USA                       | FCC    | Approved |  |

| Canada                    | ISED   | Approved |  |

| South Africa              | ICASA  | Approved |  |

| Japan                     | MIC    | Approved |  |

| Taiwan                    | NCC    | Approved |  |

| South Korea               | KCC    | Approved |  |

| Australia and New Zealand | ACMA   | Approved |  |

| Brazil                    | ANATEL | Approved |  |

|                           |        |          |  |

Table 20: Country approvals

For detailed information about the regulatory requirements that must be met when using NORA-W30 modules in an end-product, see the NORA-W30 series SIM [1].

### 6.2 Bluetooth qualification

NORA-W30 series is a Bluetooth qualified design, listed in accordance with the Bluetooth Core 5.3 specification.

All products that use Bluetooth technology must be qualified with the Bluetooth Special Interest Group (SIG) to obtain its own Design Number (DN). This is also applicable for products that already use qualified Bluetooth modules.

The Bluetooth Qualification Process is initiated at the Bluetooth SIG Qualification Workspace (login required). At the "Specify the Design" tab, include the existing design QDID listed in Table 21.

| Product type | Declaration ID | Referenced QDID |

|--------------|----------------|-----------------|

| End product  | D065864        | 194774          |

Table 21: Bluetooth qualified design ID for NORA-W30 series

### 6.3 Environmental

#### 6.3.1 RoHS

NORA-W30 series modules are in compliance with Directive 2011/65/EU (EU RoHS 2) and its amendment, Directive 2015/863 (EU RoHS3) of the European Parliament and the Council on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

### **6.3.2 REACH**

NORA-W30 series modules do not contain the SVHC (Substance of Very High Concern), as defined by Directive EC/1907/2006 Article according to REACH Annex XVII.

### 6.4 Antennas

NORA-W306 includes an internal PCB antenna, whereas NORA-W301 is equipped with an antenna pin for connecting an external antenna. For information about the approved antennas for use with NORA-W30 modules, see the system integration manual [1].

## 7 Product handling

## 7.1 Packaging

### 7.1.1 Reels

NORA-W30 series modules are delivered as hermetically sealed, reeled tapes to enable efficient production, production lot set-up and tear-down. For more information about packaging, see the Product packaging reference guide [5].

NORA-W30 modules are delivered in quantities of 500 pieces on a reel.

The reel types for NORA-W30 modules are shown in Table 22, with more detailed information included in the Product packaging reference guide [5].

| Model     | Reel type |

|-----------|-----------|

| NORA-W301 | A3        |

| NORA-W306 | A3        |

Table 22: Reel types for different NORA-W30 series modules

### **7.1.2 Tapes**

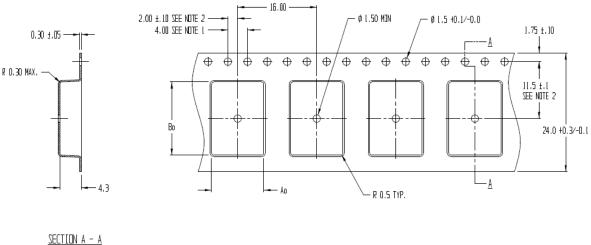

Figure 6 and Figure 7 show the position and orientation of NORA-W30 modules as they are delivered on tape. The dimensions of the tapes are specified in Figure 8.

Figure 6: NORA-W301 module on tape orientation

Figure 7: NORA-W306 module on tape orientation

Ao = 10.6Bo = 14.8 Ko = 4.3

- 1. 10 SPRODKET HOLE PITCH CUMILATIVE TOLERANCE ±0.2

- 2. POCKET POSITION RELATIVE TO SPROCKET HOLE MEASURED AS TRUE POSITION OF POCKET, NOT POCKET HOLE

- 3. AD AND BO ARE CALCULATED ON A PLANE AT A DISTANCE "R" ABOVE THE BOTTOM OF THE POCKET.

Figure 8: NORA-W301/NORA-W306 tape dimensions

## Moisture sensitivity levels

⚠ The NORA-W30 series modules are Moisture Sensitive Devices (MSD) in accordance with the IPC/JEDEC specification.

The Moisture Sensitivity Level (MSL) relates to the required packaging and handling precautions. The NORA-W30 series modules are rated at MSL level 4. For more information regarding moisture sensitivity levels, labeling, and storage, see the Product packaging reference guide [5].

For MSL standards, see IPC/JEDEC J-STD-020, which can be downloaded from www.jedec.org.

#### **Reflow soldering** 7.3

Reflow profiles are to be selected according to u-blox recommendations. See NORA-W30 series system integration manual [1] for more information.

Failure to observe these recommendations can result in severe damage to the device.

### 7.4 ESD precautions

⚠

NORA-W30 series modules contain highly sensitive electronic circuitry and are Electrostatic Sensitive Devices (ESD). Handling the NORA-W30 series modules without proper ESD protection may destroy or damage them permanently.

NORA-W30 series modules are electrostatic sensitive devices (ESD) and require special ESD precautions typically applied to ESD sensitive components. See also Maximum ESD ratings.

Proper ESD handling and packaging procedures must be applied throughout the processing, handling and operation of any application that incorporates the NORA-W30 series module. The ESD precautions should be implemented on the application board where the module is mounted as described in the NORA-W30 series system integration manual [1].

⚠ Failure to observe these recommendations can result in severe damage to the device.

## 8 Labeling and ordering information

## 8.1 Product labeling

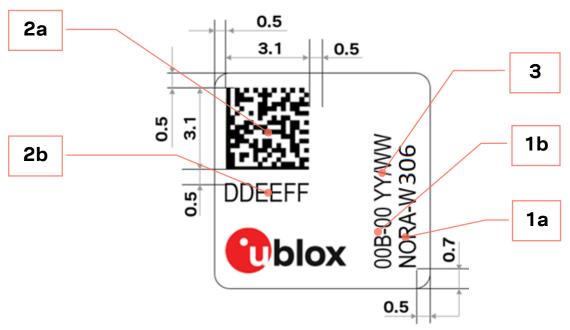

The labels (8 x 8 mm) of the NORA-W30 series modules described in the section include important product information.

Figure 9 shows the label of all the NORA-W30 series modules, which includes product type number and revision, production date, and data matrix that bears a unique serial number and the u-blox logo.

All units in mm unless specified stated otherwise.

Figure 9: Location of product type number on the NORA-W30 series module label

| Reference | Description  Product Name (Applicable model names: NORA-W301, NORA-W306).                                                                                                    |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1a        |                                                                                                                                                                              |  |  |

| 1b        | Product type number suffix.                                                                                                                                                  |  |  |

| 2a        | Data Matrix with unique serial number comprising 19 alphanumeric symbols:                                                                                                    |  |  |

|           | <ul> <li>The first 3 symbols are used for production tracking and are an abbreviated representation of the<br/>Type number that is unique to each module variant.</li> </ul> |  |  |

|           | <ul> <li>The following 12 symbols represent the unique hexadecimal Bluetooth address of the module<br/>AABBCCDDEEFF, and</li> </ul>                                          |  |  |

|           | The last 4 symbols represent the hardware and firmware version encoded HHFF.                                                                                                 |  |  |

| 2b        | The six last hex symbols of the MAC address (AABBCC <b>DDEEFF</b> ).                                                                                                         |  |  |

| 3         | Date of production encoded YY/WW (year/week).                                                                                                                                |  |  |

Table 23: NORA-W30 series label description

## 8.2 Ordering information

| Ordering code | Product                                                                    |

|---------------|----------------------------------------------------------------------------|

| NORA-W301-00B | Module with antenna pin. Open CPU version. Using RTL8720DF.                |

| NORA-W306-00B | Module with internal PCB trace antenna. Open CPU version. Using RTL8720DF. |

Table 24: Product ordering codes

# Appendix

# A Glossary

| Abbrovictic: | Definition                                        |  |  |

|--------------|---------------------------------------------------|--|--|

| Abbreviation | Definition                                        |  |  |

| ADC          | Analog to Digital Converter                       |  |  |

| AON          | Always ON                                         |  |  |

| ARM          | Arm (Advanced RISC Machines) Holdings             |  |  |

| BOD          | Brown-Out Detect                                  |  |  |

| CDM          | Charge Device Model                               |  |  |

| COMP         | Comparator                                        |  |  |

| CPU          | Central Processing Unit                           |  |  |

| DN           | Design Number                                     |  |  |