# Automotive high end front door module with 2 LIN and CAN FD

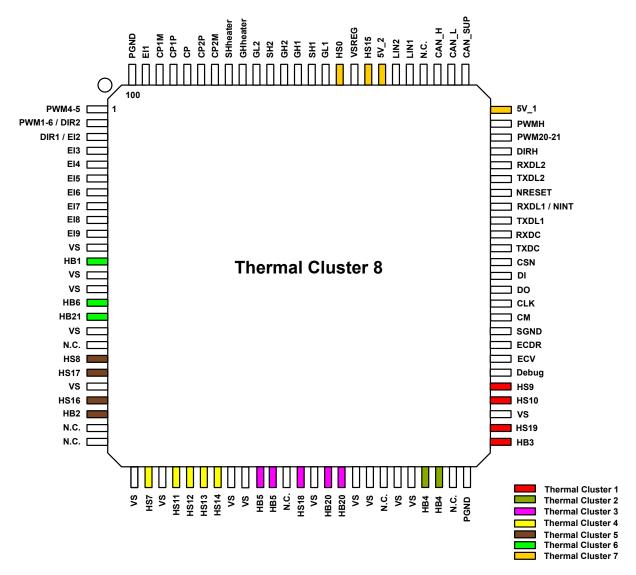

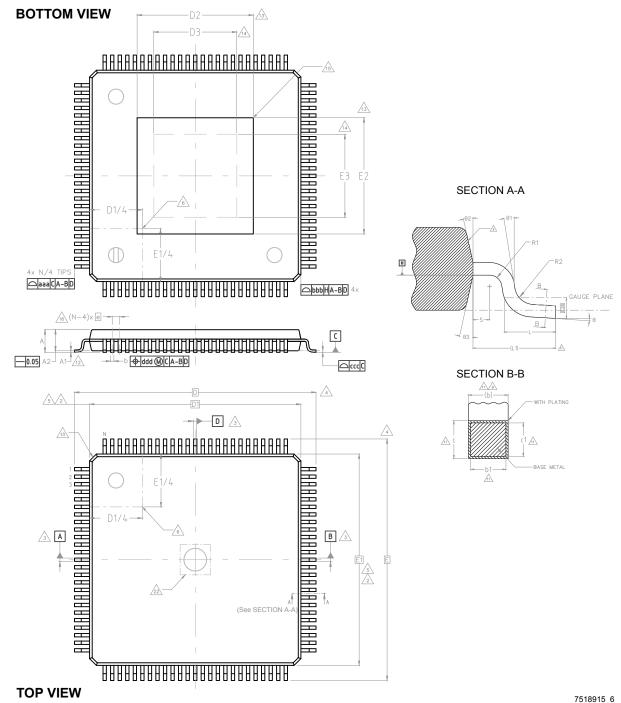

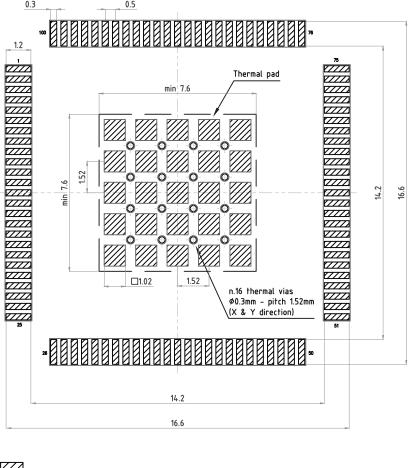

LQFP100 14x14 mm (exposed pad down)

#### **Features**

| Channel                                      | R <sub>ON</sub> | I <sub>LIMH</sub> |

|----------------------------------------------|-----------------|-------------------|

| 2 half bridge                                | 100 mΩ          | 7.5 A             |

| 1 half bridge                                | 150 mΩ          | 6 A               |

| 2 half bridges                               | 1600 mΩ         | 0.5 A             |

| 3 half bridges                               | 300 mΩ          | 3 A               |

| 1 configurable high-side driver              | 300 mΩ          | 1.5 A             |

| i configurable nigh-side driver              | 1600 mΩ         | 0.35 A            |

| 2 high-side drivers                          | 1.4 Ω           | 0.5 A             |

| 1 high-side driver to supply EC Glass MOSFET | 1.4 Ω           | 0.5 A             |

| 10 high-side drivers                         | 7 Ω             | 0.15 A            |

- CAN FD transceiver supporting communication up to 5 Mbit/s (ISO 11898-2/2016 and SAE J2284 compliant) with local failure and bus failure diagnosis

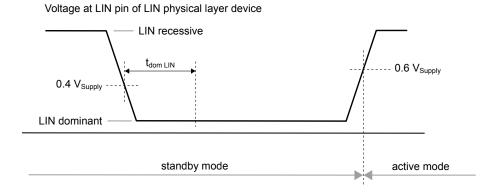

- 2 LIN transceivers ISO 17987-4/2016 compliant

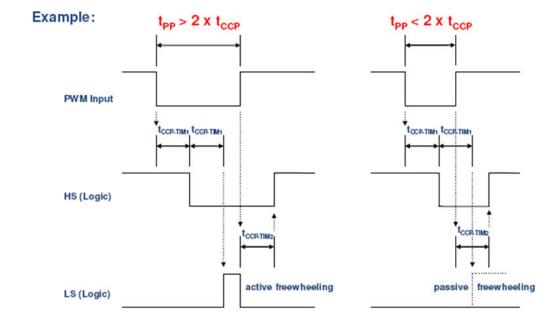

- Advanced lock and fold closing by means of PWM control on HB1-HB6, HB4-HB5, HB20 and HB21

- Advanced short-circuit detection on all the half bridges

- All HS drivers with constant current mode at start-up to drive capacitive loads

- Internal 10-bit PWM timer for each stand-alone high-side driver

- Buffered supply for voltage regulators and 2 high-side drivers (HS15 and HS0/ both P-channel) to supply, for example, external contacts

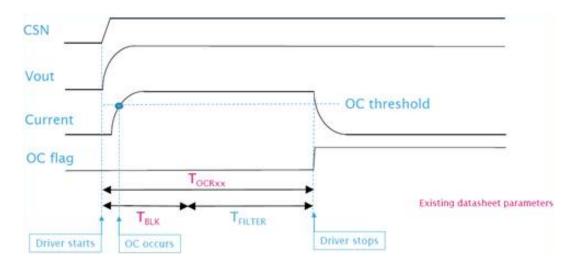

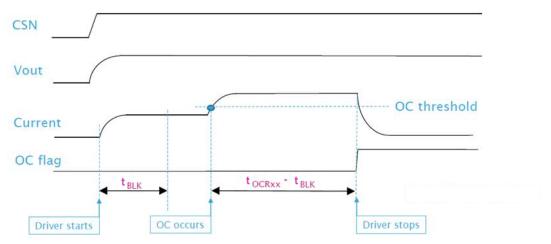

- Programmable overcurrent recovery function, to drive loads with higher inrush currents as current limitation value (for HB1-HB6, HS7-HS10)

- Flexible HS drivers (HS7-HS19 and HS0), suitable to drive external LED modules with high input capacitance value

- Programmable periodic system wake-up feature

- Complete 9-channel contact monitoring interface, with programmable cyclic sense functionality, one of them also with DIR functionality

- Dedicated debug input pin

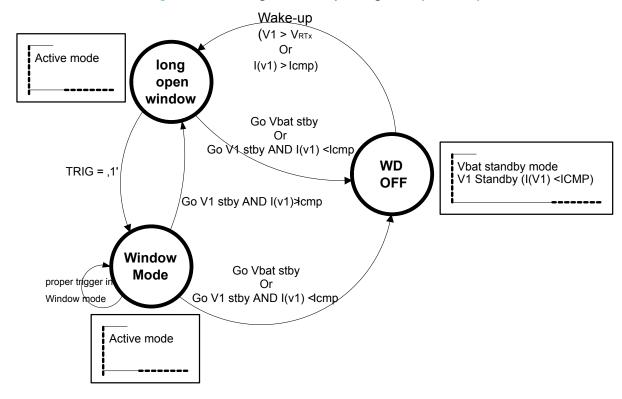

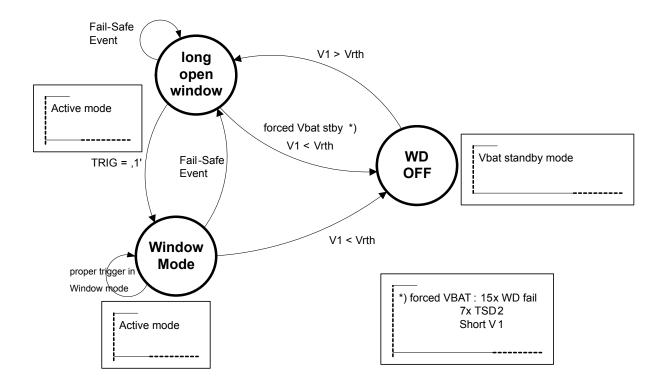

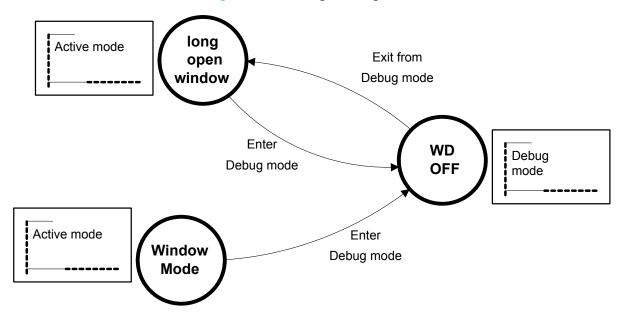

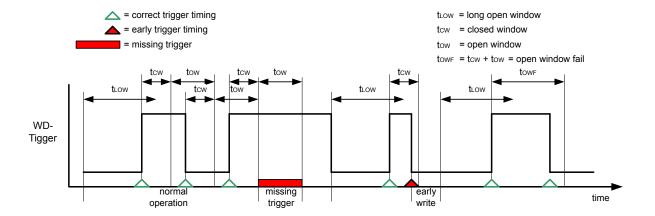

- Configurable window watchdog

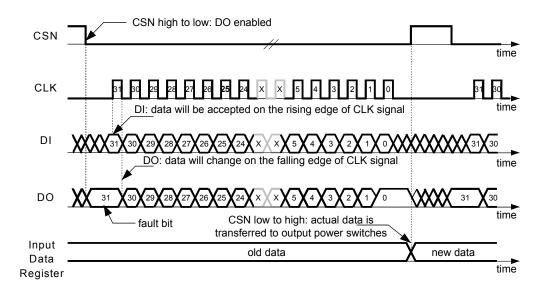

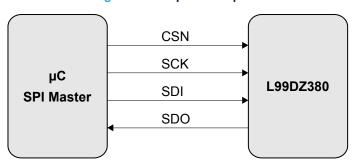

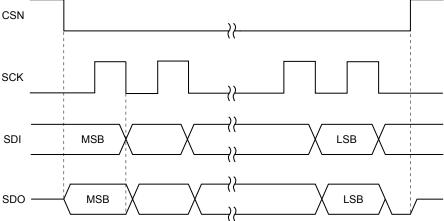

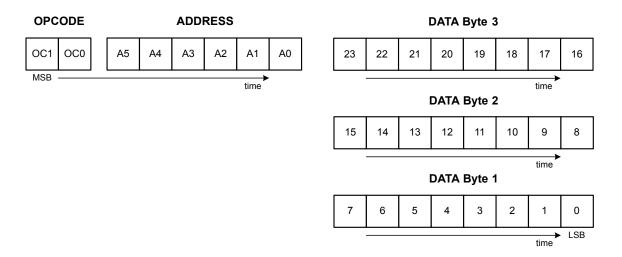

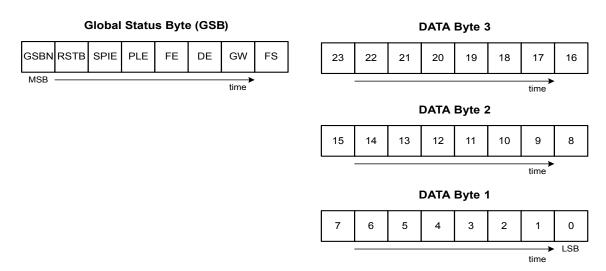

- STM standard serial peripheral interface (32-bit/ST-SPI 4.0)

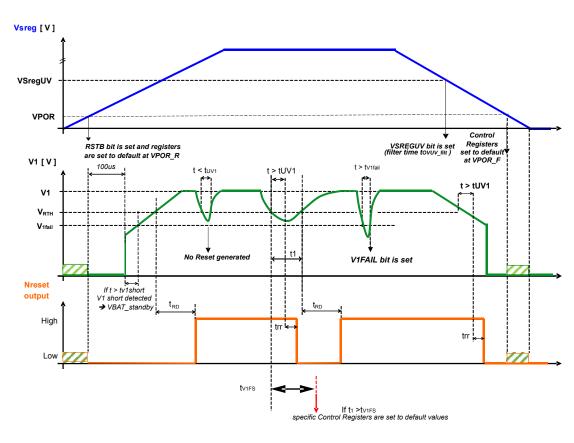

- Programmable reset generator for power-on and undervoltage

- Ultra low quiescent current in standby modes

- No electrolytic capacitor required on regulator outputs

- Two 5 V voltage regulators for microcontroller and peripheral supply

- Central two-stage charge pump

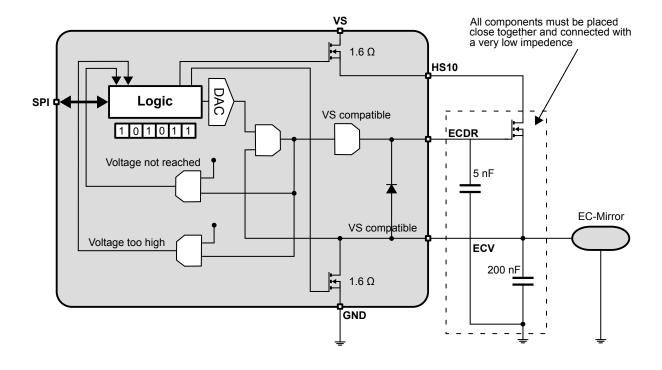

- Control block for electrochromic element

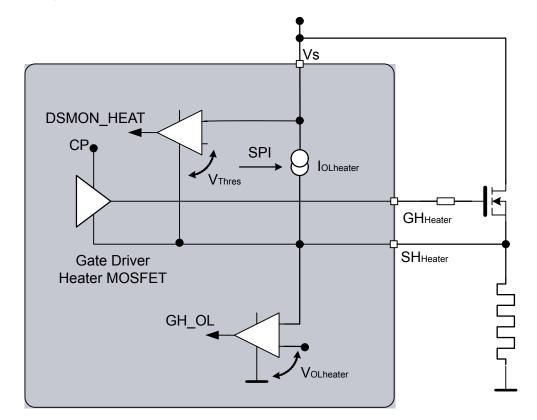

- Driver for external MOSFET in high-side configuration with SC protection/ diagnosis and open-load diagnosis

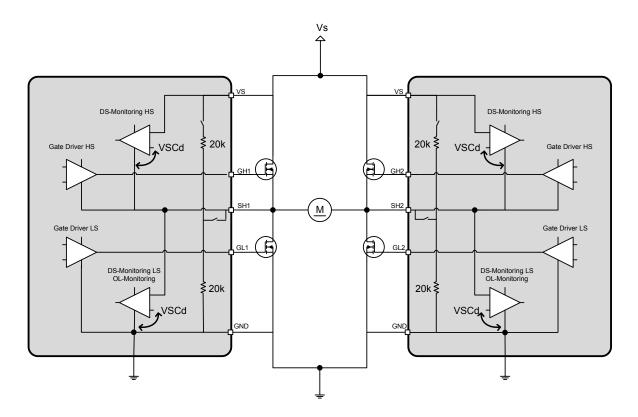

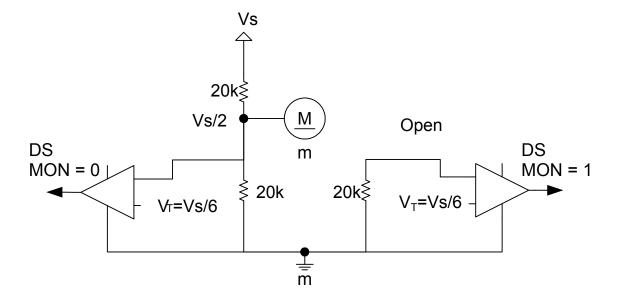

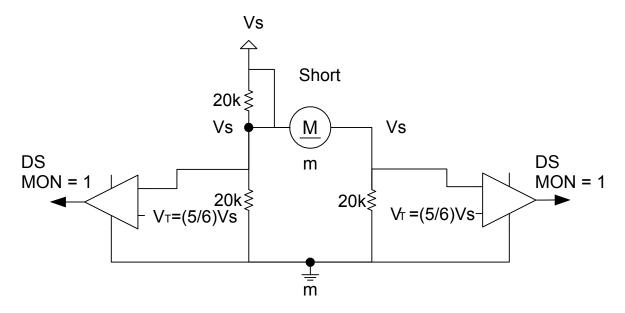

- Motor bridge driver for 4 external MOSFETs, in H-bridge configuration with short-circuit protection/diagnosis and open-load diagnosis

- · Diagnostic functions

- Current monitor output for all internal high-side drivers

- · Digital thermal clusters

- Device contains temperature warning and protection

- Open-load diagnosis for all the outputs

- · Overcurrent protection for all the outputs

# **Description**

The L99DZ380 is a door zone system IC providing electronic control modules with enhanced power management power supply functionality, including various standby modes, as well as CAN FD and 2 identical LIN physical communication layers. The device has two low drop voltage regulators to supply the system microcontroller and external peripheral loads such as sensors and provides enhanced system standby functionality with programmable local and remote wake-up capability. Moreover, the 14 high-side drivers (13 to supply LEDs and 1 to supply bulbs) increase the system integration level; all the high-side drivers support the constant current mode for LED module with high input capacitance. Up to 7 DC motors and 4 external MOS transistors in H-bridge configuration can be driven in PWM mode up to 25 kHz. An additional gate drive can control an external MOSFET in high-side configuration to supply a resistive load connected to GND (for example mirror heater). An electrochromic mirror glass can be controlled using the integrated SPI-driven module in conjunction with an external MOS transistor. All the outputs are SC protected and implement an open-load diagnosis. The ST standard SPI interface (4.0) allows control and diagnosis of the device and enables generic software development.

DS14014 - Rev 5 page 2/172

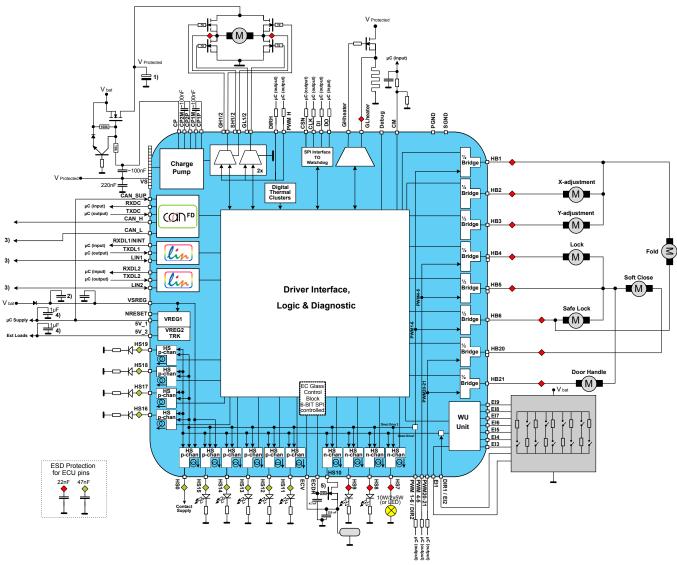

# Block diagram and pin description

DIRH PWM H Debug CM PGND CP2P CP2P CP1M CP1P CP2M CSN CLK DI DI SPI Interface TO Watchdog Charge HB1 (300m Ω, 3A) VS Pump Digital Thermal Clusters h-bridge **H**B2 (1600mΩ, 0.5A) CAN\_SUP RXDC TXDC ½ Bridge CAN\_H HB3 (1600mΩ, 0.5A) CAN\_L RXDL1/NINT ½ Bridge lin TXDL1 HB4 (150m Ω, 6A) RXDL2 ½ Bridge lin TXDL2 HB5 (100m Ω, 7.5A) **Driver Interface,** LIN2 VSREG Logic & Diagnostic ½ Bridge NRESET VREG1 -**\(\beta\)** HB6 (300 m Ω, 3 A) 5V\_1 PWM1-6 VREG2 TRK 5V\_2 HS19 (7 Ω,190 mA) HB20 (100m Ω, 7.5A) HS18 (7 Ω,190 mA) 🗖 Bridge - HB21 (300m Ω, 3A) EC Glass Control Block HS17 (7 Ω,190 mA) 🗖 E19 E18 E17 E16 E16 E15 E14 E13 6-BIT SPI controlled HS16 (7 Ω,190 mA) WU Unit HS HS HS HS P-chan P-chan P-chan P-chan HS n-chan n-chan DIR1 / EI2

DEI1

PWM20-21

PWM 4-5

PWM 1-6 / DIR2 ECDR HS10 (1.4Ω, 500mA) HS15 (7 Ω,190 mA) HS0 (7 Ω,190 mA) HS14 (7 Ω,190 mA) HS13 (7 Ω,190 mA) HS12 (7 Ω,190 mA) HS11 (7 Ω,190 mA) HS9 (1.4Ω, HS8 (1.4Ω, 500mA) 7 300m Ω, 1.5A resp 1.6Ω, 0.35A , 500mA)

Figure 1. Block diagram

DS14014 - Rev 5 page 3/172

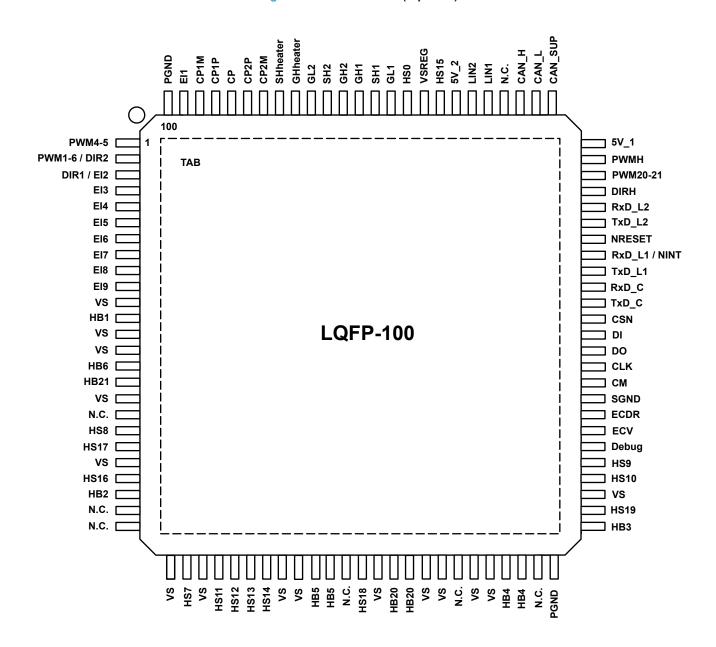

Figure 2. Pin connection (top view)

**Table 1. Pin function**

| Pin | Name        | Function                                                                                        |  |  |  |

|-----|-------------|-------------------------------------------------------------------------------------------------|--|--|--|

| 1   | PWM4-5      | PWM input: this input signal can be used to control the HB4 or HB5                              |  |  |  |

| 2   | PWM1-6/DIR2 | PWM1-6 input: this input signal can be used to control the HB1 or HB6; DIR2: direct HS drive 2; |  |  |  |

| 3   | DIR1/EI2    | DIR1: direct HS drive 1; EI2: input pin for static or cyclic monitoring of external contacts    |  |  |  |

| 4   | EI3         | Input pin for static or cyclic monitoring of external contacts                                  |  |  |  |

| 5   | El4         | Input pin for static or cyclic monitoring of external contacts                                  |  |  |  |

| 6   | EI5         | Input pin for static or cyclic monitoring of external contacts                                  |  |  |  |

DS14014 - Rev 5 page 4/172

| Pin | Name                    | Function                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | El6                     | Input pin for static or cyclic monitoring of external contacts                                                                                                                                                                                                                                                                                                                 |

| 8   | EI7                     | Input pin for static or cyclic monitoring of external contacts                                                                                                                                                                                                                                                                                                                 |

| 9   | EI8                     | Input pin for static or cyclic monitoring of external contacts                                                                                                                                                                                                                                                                                                                 |

| 10  | EI9                     | Input pin for static or cyclic monitoring of external contacts                                                                                                                                                                                                                                                                                                                 |

| 11  | VS                      | Power supply voltage for power stage outputs (external reverse battery protection required), for this input a ceramic capacitor as close as possible to GND is recommended. Important: For the capability of driving the full current at the outputs, all pins of VS must be connected externally!                                                                             |

| 12  | HB1                     | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 13  | VS; 2 <sup>nd</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 14  | VS; 3 <sup>rd</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 15  | HB6                     | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 16  | HB21                    | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 17  | VS; 4 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 18  | NC                      | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 19  | HS8                     | High-side driver output to drive LEDs. The channel is protected by auto-recovery feature.                                                                                                                                                                                                                                                                                      |

| 20  | HS17                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 21  | VS; 5 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 22  | HS16                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 23  | HB2                     | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 24  | NC                      | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 25  | NC                      | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 26  | VS; 6 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 27  | HS7                     | High-side driver output to drive LEDs or a 10 W bulb (programmable Rdson). The channel is protected by autorecovery feature.                                                                                                                                                                                                                                                   |

| 28  | VS; 7 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 29  | HS11                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 30  | HS12                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 31  | HS13                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 32  | HS14                    | High-side driver output to drive LEDs                                                                                                                                                                                                                                                                                                                                          |

| 33  | VS; 8 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 34  | VS; 9 <sup>th</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 35  | HB5                     | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to Vs, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

DS14014 - Rev 5 page 5/172

| Pin | Name                      | Function                                                                                                                                                                                                                                                                                                                                                                       |

|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36  | HB5; 2 <sup>nd</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 37  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 38  | HS18                      | High-side driver output to drive LEDs.                                                                                                                                                                                                                                                                                                                                         |

| 39  | VS; 10 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 40  | HB20                      | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 41  | HB20; 2 <sup>nd</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 42  | VS; 11 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 43  | VS; 12 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 44  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 45  | VS; 13 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 46  | VS; 14 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 47  | HB4                       | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 48  | HB4; 2 <sup>nd</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 49  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                                                                  |

| 50  | PGND                      | Power ground                                                                                                                                                                                                                                                                                                                                                                   |

| 51  | HB3                       | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output). The channel is protected by auto-recovery feature. |

| 52  | HS19                      | High-side driver output to drive LEDs.                                                                                                                                                                                                                                                                                                                                         |

| 53  | VS; 15 <sup>th</sup> pin  | Current capability (pin description see above)                                                                                                                                                                                                                                                                                                                                 |

| 54  | HS10                      | High-side driver-output; Important: Beside the HS10-HS on/off bit this output can be switched on setting the ECON bit for electro-chrome control mode with higher priority. The channel is protected by auto-recovery feature.                                                                                                                                                 |

| 55  | HS9                       | High-side driver output to drive LEDs. The channel is protected by auto-recovery feature.                                                                                                                                                                                                                                                                                      |

| 56  | Debug                     | Debug input to deactivate the window watchdog (high active). Voltage capability linked to Vs.                                                                                                                                                                                                                                                                                  |

| 57  | ECV                       | ECV: using the device in EC control mode this pin is used as voltage monitor input. For fast discharge an additional low-side switch is implemented                                                                                                                                                                                                                            |

| 58  | ECDR                      | ECDR: using the device in EC control mode this pin is used to control the gate of an external N-channel Power MOSFET                                                                                                                                                                                                                                                           |

| 59  | SGND                      | Signal ground                                                                                                                                                                                                                                                                                                                                                                  |

| 60  | СМ                        | Current monitor output: depending on the selected multiplexer bits of the Control register this output sources an image of the instant current through the corresponding high-side driver with a fixed ratio                                                                                                                                                                   |

| 61  | CLK                       | SPI: serial clock input                                                                                                                                                                                                                                                                                                                                                        |

| 62  | DO                        | SPI: serial data output (push pull output stage)                                                                                                                                                                                                                                                                                                                               |

| 63  | DI                        | SPI: serial data input                                                                                                                                                                                                                                                                                                                                                         |

| 64  | CSN                       | SPI: chip select not input                                                                                                                                                                                                                                                                                                                                                     |

| 65  | TXDC                      | CAN transmit data input                                                                                                                                                                                                                                                                                                                                                        |

| 66  | RXDC                      | CAN receive data output (push pull output stages)                                                                                                                                                                                                                                                                                                                              |

| 67  | TXDL1                     | LIN1 transmit data input                                                                                                                                                                                                                                                                                                                                                       |

DS14014 - Rev 5 page 6/172

| Pin | Name        | Function                                                                                                                                                                                                                                               |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | DVDI (AUNIT | RXDL: LIN1 receive data output;                                                                                                                                                                                                                        |

| 68  | RXDL1/NINT  | NINT: indicates local/remote wake-up events                                                                                                                                                                                                            |

| 69  | NRESET      | Power GND NReset output to micro controller; internal pull-up of typical 110 k $\Omega$ (reset state = LOW)(open drain output stage)                                                                                                                   |

| 70  | TXDL2       | LIN2 transmit data input                                                                                                                                                                                                                               |

| 71  | RXDL2       | RXDL2: LIN2 receive data output                                                                                                                                                                                                                        |

| 72  | DIRH        | Direction Input: this input controls the H-bridge drivers for the external Power MOSFETs                                                                                                                                                               |

| 73  | PWM20-21    | PWM input: this input signal can be used to control the HB20 or HB21                                                                                                                                                                                   |

| 74  | PWMH        | PWMH input: this input signal can be used to control the H-bridge gate driver                                                                                                                                                                          |

| 75  | 5V_1        | Voltage regulator output: 5 V supply for example micro controller, CAN transceiver                                                                                                                                                                     |

| 76  | CAN supply  | CAN supply input; to allow external CAN supply from V1                                                                                                                                                                                                 |

| 77  | CAN_L       | CAN low level voltage I/O                                                                                                                                                                                                                              |

| 78  | CAN_H       | CAN high level voltage I/O                                                                                                                                                                                                                             |

| 79  | NC          | Not connected                                                                                                                                                                                                                                          |

| 80  | LIN1        | LIN bus line 1                                                                                                                                                                                                                                         |

| 81  | LIN2        | LIN bus line 2                                                                                                                                                                                                                                         |

| 82  | 5V_2        | Voltage tracker output: 5 V supply for external loads (potentiometer, sensors). V2 is protected against reverse supply                                                                                                                                 |

| 83  | HS15        | High-side driver output to drive LEDs                                                                                                                                                                                                                  |

| 84  | VSREG       | Power supply voltage to supply the internal voltage regulators and the HS0 (external reverse battery protection required / Diode) for this input a ceramic capacitor as close as possible to GND and an electrolytic back up capacitor is recommended. |

| 85  | HS0         | High-side driver output to drive LEDs or to supply contacts                                                                                                                                                                                            |

| 86  | GL1         | Gate driver for Power MOSFET low-side switch in half-bridge 1                                                                                                                                                                                          |

| 87  | SH1         | Source of high-side switch in half-bridge 1                                                                                                                                                                                                            |

| 88  | GH1         | Gate driver for Power MOSFET high-side switch in half-bridge 1                                                                                                                                                                                         |

| 89  | GH2         | Gate driver for Power MOSFET high-side switch in half-bridge 2                                                                                                                                                                                         |

| 90  | SH2         | Source of high-side switch in half-bridge 2                                                                                                                                                                                                            |

| 91  | GL2         | Gate driver for Power MOSFET low-side switch in half-bridge 2                                                                                                                                                                                          |

| 92  | GHheater    | Gate driver for external N-channel Power MOSFET in high-side configuration to control the heater                                                                                                                                                       |

| 93  | SHheater    | Source of high-side Power MOSFET to control the heater                                                                                                                                                                                                 |

| 94  | CP2M        | Charge pump pin for capacitor 2, negative side                                                                                                                                                                                                         |

| 95  | CP2P        | Charge pump pin for capacitor 2, positive side                                                                                                                                                                                                         |

| 96  | СР          | Charge pump output                                                                                                                                                                                                                                     |

| 97  | CP1P        | Charge pump pin for capacitor 1, positive side                                                                                                                                                                                                         |

| 98  | CP1M        | Charge pump pin for capacitor 1, negative side                                                                                                                                                                                                         |

| 99  | EI1         | Input pin for static or cyclic monitoring of external contacts                                                                                                                                                                                         |

| 100 | PGND        | Power GND                                                                                                                                                                                                                                              |

| -   | TAB         | Ground connection                                                                                                                                                                                                                                      |

DS14014 - Rev 5 page 7/172

# 2 Electrical specifications

# 2.1 Absolute maximum ratings

Stressing the device above the rating listed in the Table 2. Absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings

| Symbol                                                                                                                                                                                                                                                                                                     | Parameter                                                              | Condition                 | Min.                  | Тур. | Max.                 | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------|-----------------------|------|----------------------|------|

| V <sub>S</sub> , V <sub>Sreg</sub>                                                                                                                                                                                                                                                                         | DC supply voltage/jump start                                           |                           | -0.3                  |      | 28                   |      |

| V <sub>S</sub> , V <sub>Sreg</sub>                                                                                                                                                                                                                                                                         | DC supply voltage/load dump                                            |                           | -0.3                  |      | 40                   | V    |

| 5V1                                                                                                                                                                                                                                                                                                        | Stabilized supply voltage, logic supply                                | V1 <<br>V <sub>SREG</sub> | -0.3                  |      | 6.5                  | V    |

| 5V2                                                                                                                                                                                                                                                                                                        | Stabilized supply voltage (1)                                          |                           | -0.3                  |      | 28                   | V    |

| V <sub>DI</sub> ,V <sub>CLK</sub> , V <sub>CSN</sub> ,<br>V <sub>DO</sub> , V <sub>RXDL</sub> /NINT,<br>V <sub>RXDC</sub> , V <sub>NRESET</sub> ,<br>V <sub>CM</sub> , V <sub>PWMH</sub> ,<br>V <sub>DIRH</sub> , V <sub>PWM1-6</sub> ,<br>V <sub>PWM4-5</sub> , V <sub>PW20</sub> ,<br>V <sub>PWM21</sub> | Logic input/output voltage range                                       |                           | -0.3                  |      | V1+0.3               | V    |

| $V_{TXDC}$ , $V_{TXDL}$                                                                                                                                                                                                                                                                                    | Logic input/output voltage range                                       |                           | -0.3                  |      | V1+0.3               | V    |

| V <sub>Debug</sub>                                                                                                                                                                                                                                                                                         | Debug input pin voltage range                                          |                           | -0.3                  |      | V <sub>S</sub> +0.3  | V    |

| V <sub>EI1,3,9</sub>                                                                                                                                                                                                                                                                                       | DC external input voltage/"jump start"                                 |                           | -0.3                  |      | 28                   | V    |

| V <sub>DIR1/EI2</sub>                                                                                                                                                                                                                                                                                      | DC external input voltage/"jump start"                                 |                           | -0.3                  |      | 28                   | V    |

| V <sub>LIN</sub>                                                                                                                                                                                                                                                                                           | LIN bus I/O voltage range                                              |                           | -27                   |      | 40                   | V    |

| I <sub>Input</sub>                                                                                                                                                                                                                                                                                         | Current injection into V <sub>S</sub> related input pins               |                           |                       | 20   |                      | mA   |

| I <sub>out_inj</sub>                                                                                                                                                                                                                                                                                       | Current injection into V <sub>S</sub> related outputs                  |                           |                       | 20   |                      | mA   |

| V <sub>CANSUP</sub>                                                                                                                                                                                                                                                                                        | CAN supply                                                             |                           | -0.3                  |      | 5.25                 | V    |

| V <sub>CANH</sub> , V <sub>CANL</sub>                                                                                                                                                                                                                                                                      | CAN bus I/O voltage range                                              |                           | -27                   |      | 40                   | V    |

| V <sub>CANH</sub> - V <sub>CANL</sub>                                                                                                                                                                                                                                                                      | Differential CAN-bus voltage                                           |                           | -5                    |      | 10                   | V    |

| V <sub>HBn</sub> , V <sub>HSm</sub> ,<br>V <sub>ECDR</sub> , V <sub>ECV</sub> ,<br>V <sub>HS0</sub>                                                                                                                                                                                                        | Output voltage:  • for HB (n = 1 to 6, 20, 21)  • for HS (m = 7 to 19) |                           | -0.3                  |      | V <sub>S</sub> +0.3  | V    |

| V <sub>GH1</sub> , V <sub>GH2</sub> ,<br>(V <sub>Gxy</sub> )                                                                                                                                                                                                                                               | High voltage signal pins                                               | V <sub>CP</sub> +0.3      | V <sub>Sxy</sub> -0.3 |      | V <sub>Sxy</sub> +13 | V    |

| V <sub>GL1</sub> , V <sub>GL2</sub>                                                                                                                                                                                                                                                                        | High voltage signal pins                                               | V <sub>CP</sub> +0.3      | -0.3                  |      | 12                   | V    |

|                                                                                                                                                                                                                                                                                                            | High voltage signal pins                                               |                           | -1                    |      | 40                   | V    |

| V <sub>SH1</sub> , V <sub>SH2</sub> (V <sub>Sxy</sub> )                                                                                                                                                                                                                                                    | High voltage signal pins; single pulse with t <sub>max.</sub> = 200 ns |                           | -5                    |      | 40                   | V    |

| V <sub>CP1P</sub>                                                                                                                                                                                                                                                                                          | High voltage signal pins                                               |                           | V <sub>S</sub> -0.3   |      | V <sub>S</sub> +10   | V    |

| V <sub>CP2P</sub>                                                                                                                                                                                                                                                                                          | High voltage signal pins                                               |                           | V <sub>S</sub> -0.6   |      | V <sub>S</sub> +10   | V    |

| V <sub>CP1M</sub> , V <sub>CP2M</sub>                                                                                                                                                                                                                                                                      | High voltage signal pins                                               |                           | -0.3                  |      | V <sub>S</sub> +0.3  | V    |

DS14014 - Rev 5 page 8/172

| Symbol                                                                                                        | Parame                                                                            | eter                              | Condition                                                               | Min.                | Тур. | Max.               | Unit |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------|---------------------|------|--------------------|------|

| V                                                                                                             | Library alternational air                                                         | V <sub>S</sub> ≤ 26 V             |                                                                         | V <sub>S</sub> -0.3 |      | V <sub>S</sub> +14 |      |

| $V_{CP}$                                                                                                      | High voltage signal pin                                                           | V <sub>S</sub> > 26 V             |                                                                         | V <sub>S</sub> -0.3 |      | 40                 | V    |

| V <sub>GH_heater</sub>                                                                                        |                                                                                   |                                   | V <sub>CP</sub> +0.3 V <sub>Sheater</sub> -0.3 V <sub>Sheater</sub> +13 |                     | V    |                    |      |

| V <sub>SH_heater</sub>                                                                                        |                                                                                   |                                   |                                                                         | -0.3                |      | 40                 | V    |

| I <sub>ECV</sub> , HB2, HB3, HS9,<br>HS10, HS11, HS12,<br>HS13, HS14, HS15,<br>HS16, HS17, HS18,<br>HS19, HS0 | Output current (2)                                                                |                                   |                                                                         | -1.25               |      | 1.25               | Α    |

| I <sub>HS8</sub>                                                                                              | Output current <sup>(2)</sup>                                                     |                                   |                                                                         | -2.5                |      | 2.5                | Α    |

| I <sub>HS7</sub>                                                                                              | Output current <sup>(2)</sup>                                                     |                                   |                                                                         | -5                  |      | 5                  | Α    |

| I <sub>HB1,6,21</sub>                                                                                         | Output current <sup>(2)</sup>                                                     |                                   |                                                                         | -5                  |      | 5                  | Α    |

| I <sub>HB4,5,20</sub>                                                                                         | Output current <sup>(2)</sup>                                                     |                                   |                                                                         | -10                 |      | 10                 | Α    |

|                                                                                                               | Maximum cumulated current at $\mathrm{V}_{S}$ drawn by HB1 & $\mathrm{HB2}^{(2)}$ |                                   |                                                                         | -7.5                |      | 7.5                |      |

|                                                                                                               | Maximum cumulated current at $V_S$ drawn by HB3, HS8 & HS10 $^{(2)}$              |                                   |                                                                         | -2.5                |      | 2.5                |      |

| lue                                                                                                           | Maximum cumulated current at V <sub>S</sub> drawn by HB4 <sup>(2)</sup>           |                                   |                                                                         | -10                 |      | 10                 | A    |

| I <sub>VScum</sub>                                                                                            | Maximum cumulated current at V <sub>S</sub> drawn by HB5 <sup>(2)</sup>           |                                   |                                                                         | -10                 |      | 10                 | A    |

|                                                                                                               | Maximum cumulated current at $V_S$ drawn by HB6 & ${\rm HS7}^{(2)}$               |                                   |                                                                         | -7.5                |      | 7.5                |      |

|                                                                                                               | Maximum cumulated current<br>HS11, HS12, HS13, HS14, H                            |                                   |                                                                         | -2.5                |      | 2.5                |      |

| I <sub>VSREG</sub>                                                                                            | Maximum current at V <sub>SREG</sub> p                                            | in <sup>(2)</sup> (5V_1. 5V_2 and |                                                                         | -2.5                |      | 2.5                | Α    |

|                                                                                                               | Maximum cumulated current & HB6 <sup>(2)</sup>                                    | at PGND drawn by HB1              |                                                                         | -7.5                |      | 7.5                |      |

| I <sub>PGNDcum</sub>                                                                                          | Maximum cumulated current at PGND drawn by HB2 & HB5 <sup>(2)</sup>               |                                   |                                                                         | -12.5               |      | 12.5               | Α    |

|                                                                                                               | Maximum cumulated current HB4 & ECV <sup>(2)</sup>                                | at PGND drawn by HB3,             |                                                                         | -12.5               |      | 12.5               |      |

| I <sub>SGND</sub>                                                                                             | Maximum current at SGND(2)                                                        |                                   |                                                                         | -1.25               |      | 1.25               | А    |

| GND pins                                                                                                      | PGND vs SGND                                                                      |                                   |                                                                         | -0.3                |      | 0.3                | V    |

- 1. L99DZ380 is protected against 5V2 shorted to  $V_S$  and 5V2 reverse biasing when  $V_{SREG}$  is higher than 3.5 V.

- 2. Values for the absolute maximum DC current through the bond wires. This value does not consider maximum power dissipation or other limits.

Note:

- 1. All maximum ratings are absolute ratings. Leaving the limitation of any of these values may cause an irreversible damage of the integrated circuit.

- 2. Loss of ground or ground shift with externally grounded loads: ESD structures are configured for nominal currents only. If external loads are connected to different grounds, the current load must be limited to this nominal current.

DS14014 - Rev 5 page 9/172

#### 2.2 ESD protection

Table 3. ESD protection

| Parameter                                                                        | Value             | Unit |

|----------------------------------------------------------------------------------|-------------------|------|

| All pins <sup>(1)</sup>                                                          | ±2                | kV   |

| All power output pins <sup>(2)</sup> : HB1–HB6, HB20, HB21, HS7 - HS19, HS0, ECV | ±4                | kV   |

|                                                                                  | ±8 <sup>(2)</sup> |      |

| LIN                                                                              | ±8 <sup>(3)</sup> | kV   |

|                                                                                  | ±6 <sup>(4)</sup> |      |

| CAN LI CAN I                                                                     | ±8 <sup>(2)</sup> | kV   |

| CAN_H, CAN_L                                                                     |                   | KV   |

| All pins <sup>(5)</sup>                                                          | ±500              | V    |

| Corner pins <sup>(5)</sup>                                                       | ±750              | V    |

- 1. HBM (human body model, 100 pF, 1.5 k $\Omega$ ) according to AEC-Q100-002.

- 2. HBM with all none zapped pins grounded. HBx (x = 1, ..., 6, 20, 21) and HSy (y = 7, ..., 15, 0, 16, ..., 19).

- Indirect ESD Test according to IEC 61000-4-2 (150 pF, 330 Ω) and 'Hardware requirements for LIN, CAN and flexray interfaces in automotive applications' (version 1.3, May 2012).

- 4. Direct ESD test according to IEC 61000-4-2 (150 pF, 330 Ω) and 'Hardware Requirements for LIN, CAN and Flexray interfaces in automotive applications' (version 1.3, May 2012).

- 5. Charged device model according to AEC-Q100-011.

#### 2.3 Thermal data

Table 4. Operation junction temperature

| Symbol         | Parameter                      | Typ. value | Unit |  |

|----------------|--------------------------------|------------|------|--|

| T <sub>J</sub> | Operating junction temperature | -40 to 175 | °C   |  |

All parameters are guaranteed in the temperature range -40 to 150°C (unless otherwise specified); the device is still operative and functional at higher temperatures (up to 175°C).

Note:

- 1. Parameters limits at higher temperatures than 150°C may change with respect to what is specified as per the standard temperature range.

- 2. Device functionality at high temperature is guaranteed by characterization.

Table 5. Temperature warning and thermal shutdown

| Symbol               | Parameter                                 | Test condition                | Min. | Тур. | Max. | Unit | Item  |

|----------------------|-------------------------------------------|-------------------------------|------|------|------|------|-------|

| T <sub>W</sub>       | Thermal overtemperature warning threshold | T <sub>J</sub> <sup>(1)</sup> | 140  | 150  | 160  | °C   | F.025 |

| T <sub>SD1</sub>     | Thermal shutdown junction temperature 1   | T <sub>J</sub> <sup>(1)</sup> | 165  | 175  | 185  | °C   | F.026 |

| T <sub>SD2</sub>     | Thermal shutdown junction temperature 2   | T <sub>J</sub> <sup>(1)</sup> | 175  | 185  | 195  | °C   | F.028 |

| T <sub>SD12hys</sub> |                                           | Hysteresis                    |      | 5    |      | °C   | F.029 |

| t <sub>fTjTW</sub>   | Thermal warning/shutdown filter time      | Tested by scan                |      | 32   |      | μs   | F.030 |

1. Non overlapping.

DS14014 - Rev 5 page 10/172

#### 2.3.1 L99DZ380 thermal profiles

#### **Profile 1**

Battery voltage: 16 V, ambient temperature start: 85 °C.

#### DC activation:

- V1 charged with 70 mA (68 Ω DC activation)

- V2 charged with 30 mA (120 Ω DC activation)

- HS7: 1 x 10 W bulb (DC activation)

- HS11: 300 Ω resistor (DC activation)

- HS12: 300 Ω resistor (DC activation)

- HS13: 300 Ω resistor (DC activation)

- HS14: 300 Ω resistor (DC activation)

#### Cyclic activation:

- **HB4–HB5**: 3.3 Ω resistor placed across those outputs

- 10 activations of lock/unlock (250 ms ON lock; 500 ms wait; 250 ms ON unlock; 500 ms wait).

- **HB5–HB6**: 10 Ω resistor placed across those outputs

- 10 activations of safe lock/unlock (250 ms ON lock; 500 ms wait; 250 ms ON unlock; 500 ms wait).

#### Test execution:

Once thermal equilibrium is reached with all DC load active, the "Cyclic activation" sequence is applied.

The device operates always without triggering the thermal warning threshold.

#### Profile 2

Battery voltage: 16 V, ambient temperature start: 85 °C.

#### DC activation:

- V1 charged with 70 mA (68 Ω DC activation)

- V2 charged with 30 mA (120 Ω DC activation)

- HS7: 1 x 10 W bulb (DC activation)

- HS11: 300 Ω resistor (DC activation)

- HS12: 300 Ω resistor (DC activation)

- HS13: 300 Ω resistor (DC activation)

- HS14: 300 Ω resistor (DC activation)

- HS16: 300 Ω resistor (DC activation)

- HS17: 300 Ω resistor (DC activation)

- HS18: 300 Ω resistor (DC activation)

- HS19: 300 Ω resistor (DC activation)

#### Cyclic activation:

- HB1–HB6: 10 Ω resistor placed across those outputs

- 2 activations of fold/unfold. (3 s fold; 1 s wait; 3 s unfold; 1 s wait)

- HB20–HB5: 10 Ω resistor placed across those outputs

- 2 activations of soft door in/out. (1 s ON; 3 s wait; 1 s ON; 3 s wait)

#### Test execution:

Once thermal equilibrium is reached with all DC load active, the "Cyclic activation" sequence is applied.

The device operates always without triggering the thermal warning threshold.

DS14014 - Rev 5 page 11/172

#### **Profile 3**

Battery voltage: 16 V, ambient temperature start: 85°C.

#### DC activation:

- V1 charged with 70 mA (68  $\Omega$  DC activation)

- V2 charged with 30 mA (120 Ω DC activation)

- HS7: 1 x10 W bulb (DC activation)

- HS8: 100 Ω resistor (DC activation)

- HS11: 300 Ω resistor (DC activation)

- HS12: 300 Ω resistor (DC activation)

- HS13: 300 Ω resistor (DC activation)

- HS14: 300 Ω resistor (DC activation)

#### Cyclic activation:

- **HB5–HB21**: 10 Ω resistor placed across those outputs

- 5 activations of door handle in/out. (1 s ON; 5 s wait; 1 s OFF; 5 s wait)

- T<sub>ON</sub> PWM: 20 kHz

#### Test execution:

Once thermal equilibrium is reached with all DC load active, the "Cyclic activation" sequence is applied. The device operates always without triggering the thermal warning threshold.

#### 2.4 Electrical characteristics

For an efficient and easy tracking, numbering has been added to each electrical parameter.

Device features are split into categories (see Table 3. ESD protection, Table 4. Operation junction temperature and Table 5. Temperature warning and thermal shutdown) and each of them is represented by a letter (such as A, B, C); all parameters are completely identified by a letter and a three-digit number (for example B.125, C.096) for their whole lifetime.

New inserted parameters continue with the numbering of the related category, no matter of where they are placed.

To facilitate insertion, the last number inserted for each category is also reported in the second column of the table.

Table 6. Electrical parameters numbering

| Category           | Parameters numbering | Last Inserted |

|--------------------|----------------------|---------------|

| Analog I/O         | A.xxx                | A.195         |

| Digital I/O        | B.xxx                | B.034         |

| Voltage regulators | C.xxx                | C.057         |

| Outputs            | D.xxx                | D.137         |

| Transceivers       | E.xxx                | E.124         |

| Others             | F.xxx                | F.030         |

Due to these rules and taking into account that deleted parameter numbers are no more reassigned, numbering inside each category may not be sequential.

Note:

For all the parameters described as "Tested by scan", the related timings are specified by design and have been measured in lab.

DS14014 - Rev 5 page 12/172

## 2.4.1 Supply, supply monitoring and current consumption

All SPI communication, logic and oscillator parameters are working down to  $V_{SREG}$  = 3.5 V and parameters are as specified in the respective chapters.

- SPI thresholds

- Oscillator frequency (delay times correctly elapsed)

- Internal register status correctly kept (reset at default values for V<sub>S</sub>< V<sub>POR</sub>)

- Reset threshold correctly detected

The voltages are referred to ground, and currents are assumed positive, when the current flows into the pin.  $6 \text{ V} < \text{V}_S < 28 \text{ V}, 6 \text{ V} < \text{V}_{SREG} < 28 \text{ V}, T_J = -40 ^{\circ}\text{C}$  to  $150 ^{\circ}\text{C}$ , unless otherwise specified.

Table 7. Supply monitoring and current consumption

| Symbol                   | Parameter                                                                         | Test condition                                                                                                                                                         | Min.  | Тур. | Max. | Unit | Item  |

|--------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|-------|

| V <sub>SUV</sub>         | V <sub>S</sub> undervoltage threshold                                             | V <sub>S</sub> increasing / decreasing                                                                                                                                 | 4.7   |      | 5.4  | ٧    | A.001 |

| V <sub>hyst_UV</sub>     | V <sub>S</sub> undervoltage hysteresis                                            |                                                                                                                                                                        | 0.025 | 0.1  | 0.2  | ٧    | A.002 |

| V <sub>SOV</sub>         | V <sub>S</sub> overvoltage threshold                                              | V <sub>S</sub> increasing                                                                                                                                              | 19    |      | 22.5 | ٧    | A.003 |

| V <sub>SOV</sub>         | V <sub>S</sub> overvoltage threshold                                              | V <sub>S</sub> decreasing                                                                                                                                              | 18.5  |      | 22.5 | ٧    | A.004 |

| V <sub>hyst_OV</sub>     | V <sub>S</sub> overvoltage hysteresis                                             |                                                                                                                                                                        | 0.5   | 1.3  | 1.7  | V    | A.005 |

| V <sub>SREGUV</sub>      | V <sub>SREG</sub> undervoltage threshold                                          | V <sub>SREG</sub> increasing/decreasing                                                                                                                                | 4.2   |      | 4.9  | V    | A.006 |

| V <sub>hyst_UV</sub>     | V <sub>SREG</sub> undervoltage hysteresis                                         |                                                                                                                                                                        | 0.025 | 0.1  | 0.2  | V    | A.007 |

| V <sub>SREGOV</sub>      | V <sub>SREG</sub> overvoltage threshold                                           | V <sub>SREG</sub> increasing                                                                                                                                           | 19    |      | 22.5 | V    | A.008 |

| V <sub>SREGOV</sub>      | V <sub>SREG</sub> overvoltage threshold                                           | V <sub>SREG</sub> decreasing                                                                                                                                           | 18.5  |      | 22.5 | V    | A.009 |

| V <sub>hyst_OV</sub>     | V <sub>SREG</sub> overvoltage hysteresis                                          |                                                                                                                                                                        | 0.5   | 1.3  | 1.7  | V    | A.010 |

| t <sub>ovuv_filt</sub>   | V <sub>S</sub> / V <sub>SREG</sub> overvoltage/<br>undervoltage filter time       | Tested by scan                                                                                                                                                         |       | 64   |      | μs   | A.011 |

| I <sub>V(act)</sub>      | Current consumption in active mode                                                | $V_S$ =12 V, TXD CAN = high,<br>TXD LIN = high, V1 = on, V2 = on,<br>HS/LS driver OFF                                                                                  |       | 6.2  | 12   | mA   | A.012 |

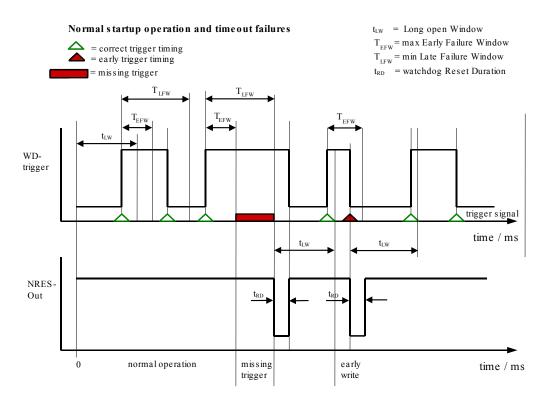

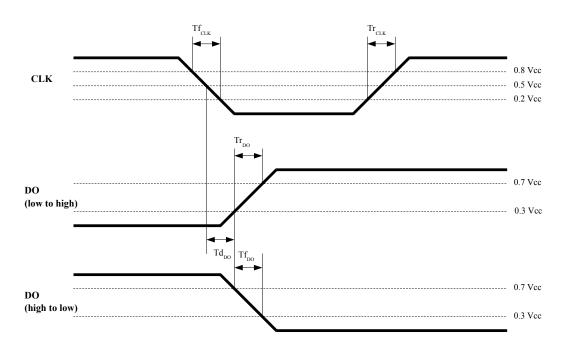

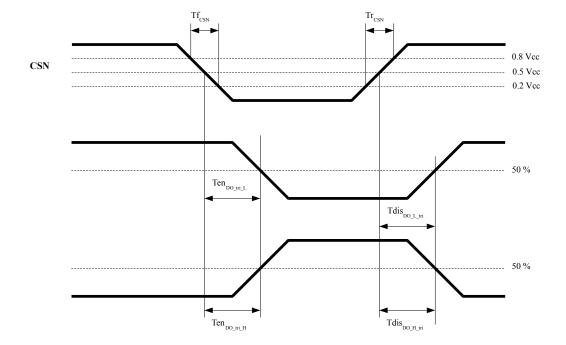

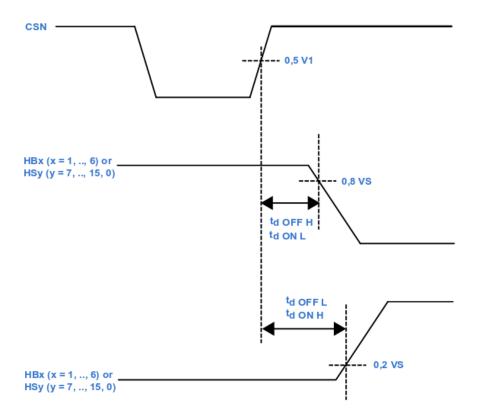

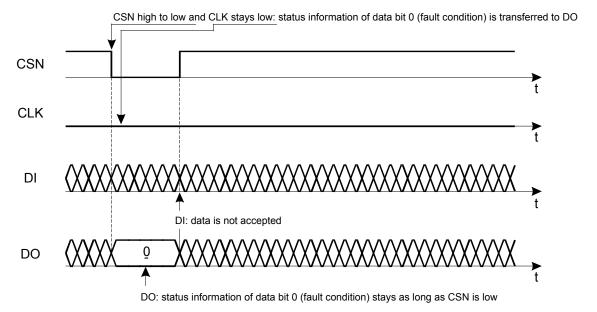

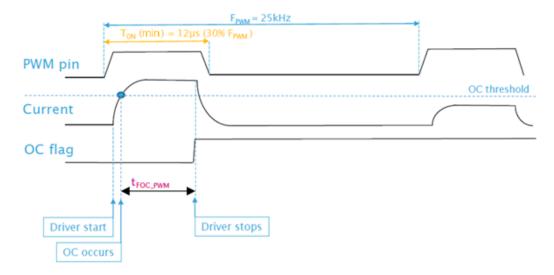

| I <sub>V(BAT)</sub>      | Current consumption in VBAT_Standby mode (1)                                      | V <sub>S</sub> = 12 V, T <sub>J</sub> = 85°C,<br>HS/LS driver OFF,<br>CAN WU disabled                                                                                  | 8     | 20   | 35   | μА   | A.013 |