# Half-bridge pre-driver for automotive applications

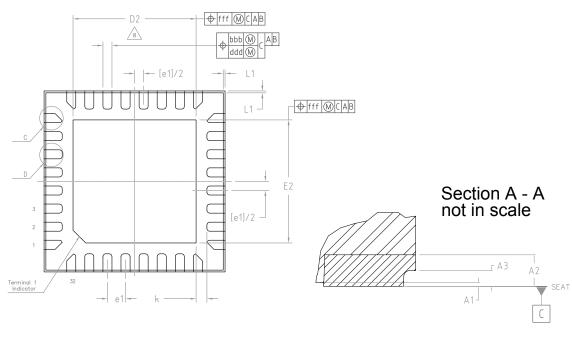

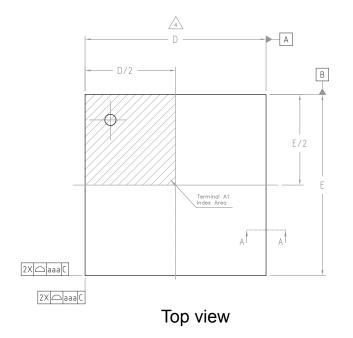

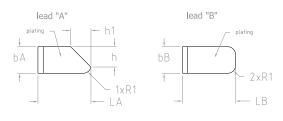

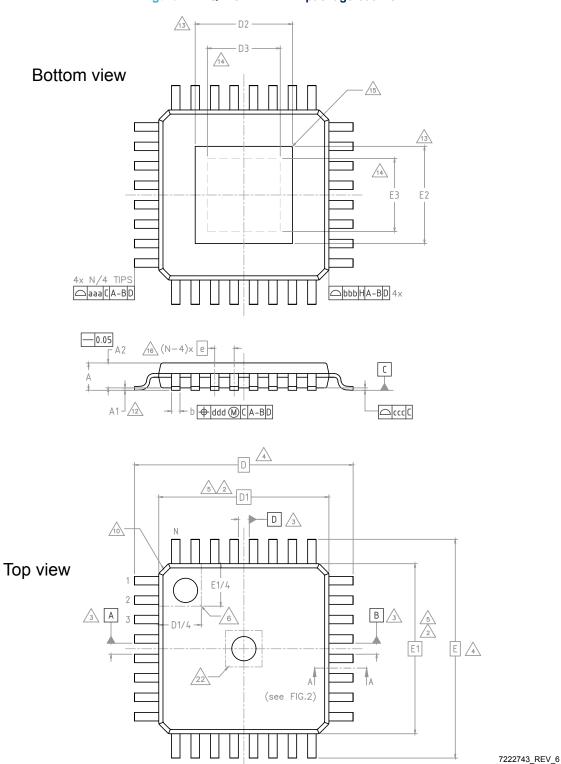

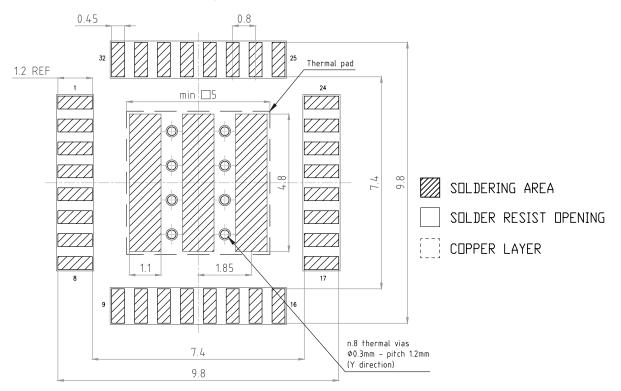

# QFN32 5x5 exposed pad

#### Product status link

L99H92

| Product summary |               |  |  |  |  |  |

|-----------------|---------------|--|--|--|--|--|

| Order code      | L99H92Q5-TR   |  |  |  |  |  |

| Package         | QFN32         |  |  |  |  |  |

| Packing         | Tape and reel |  |  |  |  |  |

| Order code      | L99H92QF-TR   |  |  |  |  |  |

| Package         | TQFP32        |  |  |  |  |  |

| Packing         | Tape and reel |  |  |  |  |  |

#### **Features**

- AEC-Q100 qualified

- · RoHs compliant device

- Power supply operating range from 4.51 V to 28 V (gate drivers operative from 5.41 V)

- 3.3 V/5 V compatible I/Os

- All pins linked to the microcontroller, fail-safe input and VDD are made tolerant to battery exposure

- · Dual half-bridge driver compatible with standard level threshold NMOSFETs

- · Configurable full-bridge or dual independent half-bridges control

- Programmable recirculation path in case of full-bridge control

- Dual stage charge pump supporting 100% PWM duty cycle down to 5.41 V battery voltage

- High and low side minimum  $V_{GS}$ =6.2 V @ VDH=5.5 V and charge pump load current ( $I_{CPLOAD}$ ) equal to 5 mA

- High and low side minimum V<sub>GS</sub>=8.2 V @ VDH≥8 V and charge pump load current (I<sub>CPLOAD</sub>) equal to 10 mA

- Charge pump output available for driving an external reverse battery NMOSFET protection

- Programmable gate driving current (up to 170 mA) for output voltage slew rate control

- Programmable drain-source monitoring for overcurrent protection and programmable cross-current protection time (dead-time)

- · Open load and output short circuit detection in off-state diagnostic mode

- SPI for control and diagnosis (ST SPI 4.1)

- Programmable diagnostic output

- Two independent current sense amplifiers

- Low offset with extremely low thermal drift

- Suitable for high-side, in-line and low-side current sensing

- Independently programmable gain (10x, 20x, 50x, 100x)

- Analog output centered at V<sub>DD</sub>/2 or VDD/22

- Overtemperature prewarning and shutdown

- Analog and digital power supply inputs over/undervoltage protections

- Asynchronous and logic independent fail-safe input to switch off all the MOSFETs

- · Low quiescent current

#### **Applications**

- Sun-roof

- Power trunk lift gate

- Sliding doors

- · Window lift, seat-belt pre-tensioners, etc.

- · Electric park brake system

## **Description**

The L99H92 is designed to drive 4 external N-channel MOSFET transistors in single H-bridge or dual independent half bridge configuration for DC-motor control in automotive applications. Two free configurable current sense amplifiers are integrated.

The device has a low power mode (standby mode) where the current consumption is less than 5 µA.

Programmable gate driving current allow minimizing EMI. Each gate driver monitors independently its external MOSFET drain-source voltage for fault conditions.

Programmable cross current protection time avoids concurrency of high side and low side activation for each half bridge.

Two off-state diagnostic comparators detect potential short to ground, short to battery or open load conditions.

The integrated standard serial peripheral interface (SPI) controls the device and provides diagnostic information. An additional DIAGN output pin alert the microcontrollers of a fault occurred into the device faster of SPI communication.

The L99H92 device implements diagnostic and protection features such as supply voltage monitoring, charge pump voltage monitoring, overcurrent protection, temperature warning and overtemperature shutdown.

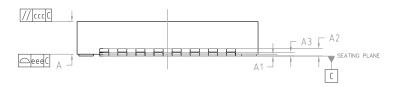

The device is hosted in a TQFP32 and QFN32 package both with exposed pad. QFN32 has wettable flanks for easy visual inspection of the solder joint.

DS14069 - Rev 1 page 2/75

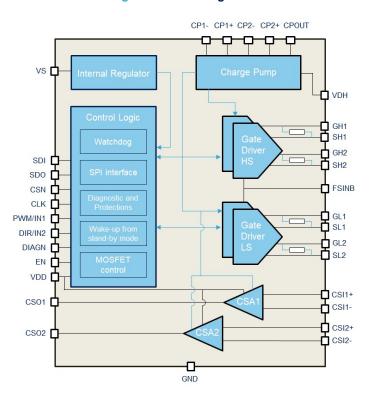

# 1 Block diagram and pins description

## 1.1 Block diagram

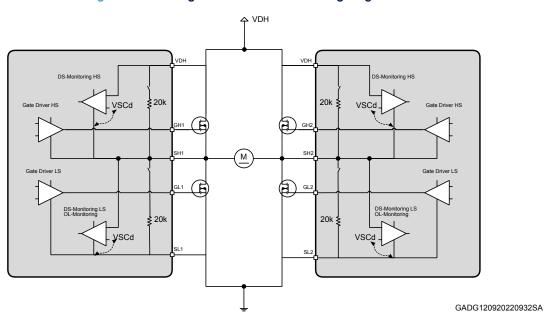

Figure 1. Block diagram

GADG120920220920SA

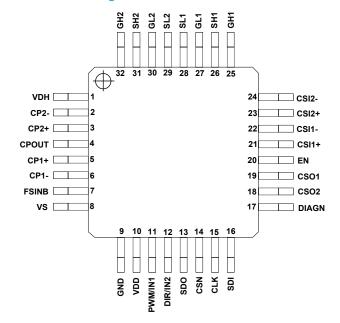

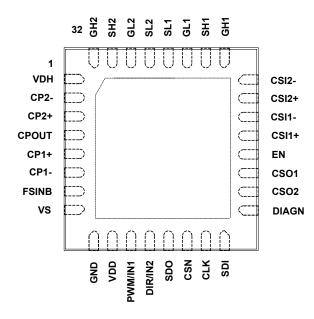

## 1.2 Pinout

Figure 2. Pinout - TQFP32

GADG120920221234SA

DS14069 - Rev 1

Figure 3. Pinout - QFN 32

GADG120920221236SA

# 1.3 Pins description

Table 1. Pin definitions and functions

| Pin | Name    | Description                                                         |

|-----|---------|---------------------------------------------------------------------|

| 1   | VDH     | High-side drain connection                                          |

| 2   | CP2-    | Charge pump stage 2 negative connection                             |

| 3   | CP2+    | Charge pump stage 2 positive connection                             |

| 4   | CPOUT   | Charge pump output                                                  |

| 5   | CP1+    | Charge pump stage 1 positive connection                             |

| 6   | CP1-    | Charge pump stage 1 negative connection                             |

| 7   | FSINB   | Fail-safe input not                                                 |

| 8   | VS      | Power supply input                                                  |

| 9   | GND     | Ground connection                                                   |

| 10  | VDD     | 3.3 V/5 V supply for I/Os and current sense amplifiers output stage |

| 11  | PWM/IN1 | PWM input or leg 1 input                                            |

| 12  | DIR/IN2 | Direction input or leg 2 input                                      |

| 13  | SDO     | SPI serial data output                                              |

| 14  | CSN     | SPI chip select not                                                 |

| 15  | CLK     | SPI serial clock                                                    |

| 16  | SDI     | SPI serial data input                                               |

| 17  | DIAGN   | Diagnostic output not                                               |

| 18  | CSO2    | Current sense amplifier 2 output                                    |

| 19  | CSO1    | Current sense amplifier 1 output                                    |

| 20  | EN      | Enable input                                                        |

| 21  | CSI1+   | Current sense amplifier 1 positive input                            |

| 22  | CSI1-   | Current sense amplifier 1 negative input                            |

DS14069 - Rev 1 page 4/75

| Pin  | Name    | Description                                           |

|------|---------|-------------------------------------------------------|

| 23   | CSI2+   | Current sense amplifier 2 positive input              |

| 24   | CSI2-   | Current sense amplifier 2 negative input              |

| 25   | GH1     | High-side gate of leg 1                               |

| 26   | SH1     | High-side source of leg 1 and Low-side drain of leg 1 |

| 27   | GL1     | Low-side gate of leg 1                                |

| 28   | SL1     | Low-side source of leg 1                              |

| 29   | SL2     | Low-side source of leg 2                              |

| 30   | GL2     | Low-side gate of leg 2                                |

| 31   | SH2     | High-side source of leg 2 and Low-side drain of leg 2 |

| 32   | GH2     | High-side gate of leg 2                               |

| Expo | sed pad | Connection to GND is recommended                      |

DS14069 - Rev 1 page 5/75

## 2 Device description

## 2.1 Supply pins

The device has three supply input pins:

- VS is the supply input of the internal regulator that supplies the logic.

- VDH is the supply input of the charge pump that supplies the gate drivers and the current sense amplifiers input stage.

- VDD is the supply input of the I/Os and the current sense amplifiers output stage. This voltage has to be the same as the application microcontroller supply (for example, 3.3 V or 5 V).

None of the supply input pins are internally protected against negative voltage. The VDD supply input can withstand a short to battery up to VDD absolute maximum rating Table 17.

#### 2.1.1 VS overvoltage warning (VSOVW)

When the VS supply input voltage rises above the programmable overvoltage warning threshold (VSOVWT1 for OVTS=0 or VSOVWT2 for OVTS=1) for a time longer than t<sub>ovuv\_filt</sub>, then the corresponding overvoltage warning flag (VSOVW) is set, and no action is taken.

The overvoltage warning flag VSOVW can be cleared by an SPI "Read & Clear" command only if the VS overvoltage condition is no longer present, namely if VS<VSOVWT1 or VS<VSOVWT2, depending on the OVTS control bit value, for a time longer than the corresponding filtering time t<sub>ovuv</sub> filt.

#### 2.1.2 VDH overvoltage (VDHOV)

When the VDH supply input voltage rises above the programmable overvoltage protection threshold (VDHOVT1 for OVTS=0 or VDHOVT2 for OVTS=1) for a time longer than  $t_{\text{OVUV\_filt}}$ , then the corresponding overvoltage flag (VDHOV) is set, and to protect the application the charge pump is disabled and the external MOSFETs are switched off. In particular, the LS MOSFETs gate drivers are forced in sink switch mode to switch off actively the LS MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits), whereas the HS MOSFETs gate drivers are forced in sink switch mode for 32 µs (up to 64 µs) and as long as VCP>VDH+3 V to switch off actively the HS MOSFETs with the maximum available current, regardless of the programmed gate discharge current. Once the 32 µs (up to 64 µs) are over or VCP<VDH+3 V the HS MOSFETs gate drivers are disabled leaving just an internal resistive connection (RGSHx) between gate and source of the MOSFETs. The charge pump is automatically enabled once the VDH falls back below the overvoltage protection threshold (VDHOVT1 for OVTS=0 or VDHOVT2 for OVTS=1) for a time longer than the corresponding filtering time  $t_{\text{OVUV\_filt}}$ , while the LS MOSFETs gate drivers remain in sink switch mode and the HS MOSFETs gate drivers remain disabled until the VDHOV flag is cleared.

The overvoltage protection flag VDHOV can be cleared by an SPI "Read & Clear" command only if the VDH overvoltage condition is no longer present, namely if the foresaid condition that automatically enables the charge pump is fulfilled.

#### 2.1.3 VDH undervoltage (VDHUV)

When the VDH supply input voltage falls below the undervoltage protection threshold (VDHUV) for a time longer than  $t_{\text{OVUV\_filt}}$ , then the corresponding undervoltage flag (VDHUV) is set, and to protect the external power stage the external MOSFETs are switched off. In particular, the LS MOSFETs gate drivers are forced in sink switch mode to switch off actively the LS MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). The HS MOSFETs gate drivers are forced in sink switch mode, as long as VCP>VDH+3 V, otherwise the HS MOSFETs gate drivers are disabled and the HS MOSFETs are passively switched off through the internal resistive connection between gate and source (RGSHx). The gate drivers come out of forced sink switch mode/disabled mode once the undervoltage flag VDHUV is cleared. The under-voltage flag VDHUV can be cleared by an SPI "Read & Clear" command only if the VDH undervoltage condition is no longer present, namely if VDH>VDHUV for a time longer than the corresponding filtering time  $t_{\text{Ovuv}\_filt}$ .

DS14069 - Rev 1 page 6/75

#### 2.1.4 VDD overvoltage (VDDOV)

When the VDD exceeds the  $V_{DDOV}$  threshold for a time longer than  $t_{ovuv\_filt}$ , then the corresponding overvoltage flag (VDDOV) is set, and to protect the application all the gate drivers are forced in sink switch mode to switch off actively all the MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). The gate drivers come out of forced sink switch mode once the overvoltage flag VDDOV is cleared. The overvoltage flag VDDOV can be cleared by an SPI "Read & Clear" command only if the VDD overvoltage condition is no longer present, namely if VDD<VDDOV for a time longer than the corresponding filtering time  $t_{ovuv\_filt}$ . The VDD overvoltage protection aims to make the application robust against VDD short to battery.

## 2.1.5 Digital input/output overvoltage (DIOOV)

When the voltage at any of the digital input/output pins listed below exceeds the  $V_{DIOOV}$  threshold for a time longer than  $t_{ovuv\_filt}$ , then the corresponding overvoltage flag (DIOOV) is set, and to protect the application all the gate drivers are forced in sink switch mode to switch off actively all the MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). The gate drivers come out of forced sink switch mode once the overvoltage flag DIOOV is cleared. The overvoltage flag DIOOV can be cleared by an SPI "Read & Clear" command only if the digital input/output overvoltage condition is no longer present namely if VDIO<VDIOOV for a time longer than the corresponding filtering time  $t_{ovuv\_filt}$ . The digital input/output overvoltage protection aims to make the application robust against digital input/output pins short to battery. The digital input/output pins monitored for overvoltage events are: PWM/IN1, DIR/IN2, DIAGN, CSO1, CSO2, CSN, SDI, SDO, CLK. Any overvoltage detection affecting the device digital output pins DIAGN and SDO will not affect/propagate internally to VDD. Anyhow, all the digital input/output pins, FSINB pin and EN pin included, can withstand a short to battery up to the related absolute maximum rating Table 17.

#### 2.1.6 Power-on reset (POR)

The device gets out of standby mode to get into active mode as soon as the EN pin is high, the VDD is above  $V_{DDPOR\ OFF}$  and the VS is above  $V_{SPOR\ OFF}$ .

If either the VDD falls below  $V_{DDPOR\_ON}$  or the VS falls below  $V_{SPOR\_ON}$  with the EN pin still high, the device experiences a power-on reset and enter in standby mode. In standby mode the gate drivers and the charge pump are switched off, leaving just the internal resistive link between gate and source at each MOSFET (RGSHx and RGSLx). Besides, the content of all the registers is reset to default value. Once out of standby mode the global status byte RSTB bit will be set indicating that all the device registers have been reset to default value. This bit is automatically cleared by any valid SPI communication frame.

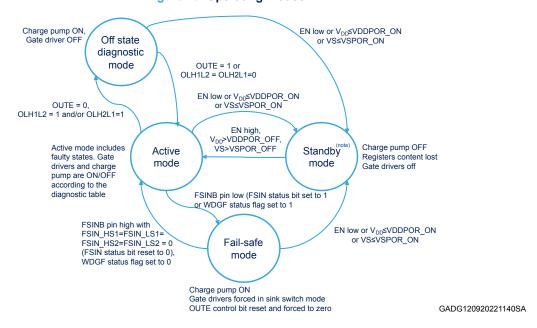

## 2.2 Standby mode (EN)

The L99H92 is enabled/disabled by pulling the EN input pin high/low. If VDD >  $V_{DDPOR\_OFF}$ , VS> $V_{SPOR\_OFF}$  and EN input pin is high, the device enters in active mode. If any of the above conditions is not met, the device will remain in standby mode. When the EN input pin is left floating, because of the internal pull-down current (IIN), the device enters (if not already) in standby mode minimizing its current consumption. In standby mode the minimum current drawn by VS, less than 5  $\mu$ A ( $I_{Sq}$ ) for CSN = high (SDO in tristate), can be achieved by pulling the EN input pin low. Besides, in standby mode, the gate drivers together with the charge pump are switched off. All the MOSFETs are passively switched off by the internal resistive link between gate and source present at each MOSFET (regardless of the control input pins PWM/IN1, DIR/IN2 and FSINB logic levels), and all the registers are reset to default values. Out of standby mode the device diagnostic is available and all the operations on the device registers are available as well.

## 2.3 Active mode (OUTE)

As soon as the EN pin is high, the VDD is above V<sub>DDPOR\_OFF</sub> and the VS is above V<sub>SPOR\_OFF</sub> the device comes out of standby mode to go in active mode. In active mode the device diagnostic is available.

In active mode with no faults, the charge pump is enabled, and the gate drivers are enabled as long as the OUTE control bit is set. Instead, if the OUTE control bit is reset, then all the gate drivers are disabled and all the MOSFETs are switched off passively through the internal resistive connection between gate and source present at each MOSFET. In active mode with no fault and with OUTE set, the MOSFETs to be turned on are controlled through the combination of the input signals PWM/IN1, DIR/IN2 and the control bits INPMODE, AFWE and FWS.

DS14069 - Rev 1 page 7/75

## 2.4 Thermal warning and thermal shutdown (TW/TSD)

When the device junction temperature rises above the  $T_{jTW\_ON}$  threshold for a time longer than  $t_{fTjTW/TSD}$ , then the temperature warning flag TW is set and no action is taken. The TW flag can be cleared by an SPI "Read & Clear" command only if the thermal warning condition is no longer present, namely if  $T_j < T_{jTW\_OFF}$  for a time longer than the corresponding filtering time  $t_{fTjTW/TSD}$ .

When the junction temperature rises above the  $T_{\rm jSD\_ON}$  threshold for a time longer than  $t_{\rm fTjTW/TSD}$ , then the thermal shutdown flag TSD is set and the external MOSFETs, together with the charge pump are switched-off to protect the device. In particular, the LS MOSFETs gate drivers are forced in sink switch mode to switch off actively the LS MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). The HS MOSFETs gate drivers are forced in sink switch mode for 32 $\mu$ s (up to 64  $\mu$ s) and as long as VCP>VDH+3 V to switch off actively the HS MOSFETs with the maximum available current, regardless of the programmed gate discharge current. Once the 32  $\mu$ s (up to 64  $\mu$ s) are over or VCP<VDH+3 V the HS MOSFETs gate drivers are disabled leaving just an internal resistive connection between gate and source of the HS MOSFETs.

The LS gate drivers remain in sink switch mode and the HS gate drivers remain disabled together with the charge pump until the TSD flag is cleared.

The TSD flag can be cleared by an SPI "Read & Clear" command only if the thermal shutdown condition is no longer present, namely if  $T_i < T_{iSD\ OFF}$  for a time longer than the corresponding filtering time  $t_{fTiTW/TSD}$ .

## 2.5 Charge pump (CPOUT)

The dual stage charge pump uses two external flying capacitors, which are switched at the frequency  $f_{CP}$ , and one output capacitor connected between the CPOUT pin and the VDH pin. The output of the charge pump has a current limitation (ICP\_lim). The NRDY status bit indicates that the charge pump is still not ready to provide enough driving voltage to the gate drivers. This status bit is set during any charge pump startup event because of the device transition from standby mode to active mode or because of the charge pump being enabled once the fault condition/flag that disabled the charge pump is no longer present/set. While the NRDY status bit is set the gate drivers are disabled. The NRDY status bit is automatically cleared once the charge pump output voltage is no longer below the low voltage threshold ( $V_{CP\_low}$ ) for a time longer than the  $t_{CP}$  filtering time. Out of standby mode and without any fault the charge pump is enabled. In standby mode, after a thermal shutdown event detection, or in VDH overvoltage condition the charge pump is disabled. To enable the charge pump disabled by a thermal shut down event detection, the TSD flag has to be cleared. To enable the charge pump disabled by VDH overvoltage condition, it is enough that the VDH falls back below the overvoltage threshold (VDHOVT1 or VDHOVT2) for a time longer than the  $t_{OVUV}$  filt filtering time.

After the charge pump startup, once the NRDY status bit is cleared, if the charge pump output voltage falls below the charge pump output voltage low threshold  $V_{CP\_low}$  for a time longer than  $t_{CP}$ , then the CPLOW flag is set and the external MOSFETs are switched off. In particular, the LS MOSFETs gate drivers are forced in sink switch mode to switch off actively the LS MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). The HS MOSFETs gate drivers are forced in sink switch mode as long as VCP>VDH+3 V, otherwise the HS MOSFETs gate drivers will be disabled and the HS MOSFETs will be switched off passively through the internal resistive connection between gate and source (RGSHx). If the CP\_LOW\_CONFIG control bit is set to one, the CPLOW status flag becomes a status bit (set and reset automatically) and the gate drivers come out of forced sink switch mode automatically upon recovery from the charge pump low voltage condition. In this case, the status bit is automatically cleared as soon as the charge pump output voltage is no longer below the low voltage threshold for a time longer than  $t_{CP}$ . If the CP\_LOW\_CONFIG control bit is set to zero, the gate drivers come out of forced sink switch mode only once the charge pump low voltage flag CPLOW is cleared via SPI. The charge pump low voltage flag CPLOW can be cleared by an SPI "Read & Clear" command only if the charge pump low voltage condition is no longer present, namely if VCP>V<sub>CP\_LOW</sub> for a time longer than  $t_{CP}$ .

To reduce electromagnetic emissions, the charge pump frequency dithering is enabled by default. However, the dithering can be disabled through the control bit CPFDD.

DS14069 - Rev 1 page 8/75

Internal CP enable signal

CP Voltage

Charge pump low filter time

NRDY bit

CPLOW flag

NRDY auto clear

CPLOW Read & Clear via SPI

Figure 4. NRDY status bit and CPLOW flag

GADG120920220925SA

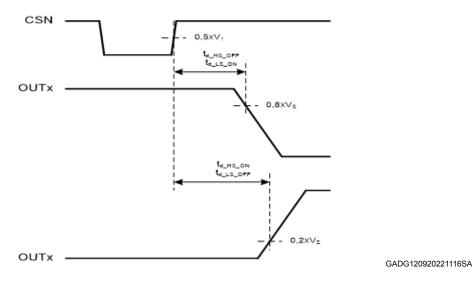

#### 2.6 Gate drivers

## 2.6.1 Outputs driving signals (PWM/IN1 and DIR/IN2)

When the OUTE control bit is reset with the FSINB pin high, all the gate drivers are disabled and the turned on MOSFETs are passively shut off through the internal resistance connected between gate and source of each MOSFET (RGSHx and RGSLx). Regardless of the OUTE control bit value, when the FSINB pin is pulled low all the MOSFETs are actively shut off by the gate drivers forced in sink switch mode.

Once the OUTE control bit is set and the FSINB pin is high, the external MOSFETs are driven by the input pins PWM/IN1 and DIR/IN2. Both input pins, PWM/IN1 and DIR/IN2, have an internal pull-down current (IPWM\_in and IDIR\_in) to put the outputs in a well-known condition in case any of the pins will no longer be driven by the microcontroller. Depending on the value of the INPMODE control bit, the device can work as full-bridge driver or dual half-bridge driver:

If INPMODE = 0 (default value), the device works in full-bridge mode. In this case the active full-bridge diagonal, fixing the rotational direction of the motor is selected by DIR/IN2 input while the driving PWM signal has to be applied to PWM/IN1 input.

Depending on the active free-wheeling enable control bit value (AFWE) and the freewheeling selection control bit value (FWS), four different freewheeling strategies are available: active or passive and freewheeling on either high-side or low-side MOSFETs. The *DIR input pin sets the active diagonal. The AFWE control bit enables or disables active free-wheeling and the FWS control bit sets the free-wheeling path (HS or LS).*

Table 2. Truth table

|      | Device in active mode with INPMODE=0 (FULL-BRIDGE MODE) |     |                  |     |     |                    |                    |                    |                    |  |

|------|---------------------------------------------------------|-----|------------------|-----|-----|--------------------|--------------------|--------------------|--------------------|--|

|      | Inputs                                                  |     |                  |     |     |                    | utputs (in ca      | se of no faul      | ts)                |  |

| OUTE | AFWE bit                                                | FWS | FSINB            | DIR | PWM | HS1                | LS1                | HS2                | LS2                |  |

| bit  | 711 112 211                                             | bit | pin              | pin | pin |                    |                    |                    |                    |  |

| х    | x                                                       | x   | 0 <sup>(1)</sup> | х   | x   | OFF                | OFF                | OFF                | OFF                |  |

| 0    | x                                                       | x   | 1                | х   | x   | OFF <sup>(2)</sup> | OFF <sup>(2)</sup> | OFF <sup>(2)</sup> | OFF <sup>(2)</sup> |  |

| 1    | 0                                                       | 0   | 1                | 0   | 0   | OFF                | OFF                | OFF                | ON                 |  |

| 1    | x                                                       | x   | 1                | 0   | 1   | ON                 | OFF                | OFF                | ON                 |  |

| 1    | 0                                                       | 1   | 1                | 0   | 0   | ON                 | OFF                | OFF                | OFF                |  |

DS14069 - Rev 1 page 9/75

|      | Device in active mode with INPMODE=0 (FULL-BRIDGE MODE) |     |       |     |     |     |               |               |     |  |

|------|---------------------------------------------------------|-----|-------|-----|-----|-----|---------------|---------------|-----|--|

|      | Inputs                                                  |     |       |     |     |     | utputs (in ca | se of no faul | ts) |  |

| OUTE | AFWE bit                                                | FWS | FSINB | DIR | PWM | HS1 | LS1           | HS2           | LS2 |  |

| bit  | AI WE BIL                                               | bit | pin   | pin | pin | пот | LSI           | 1102          | E02 |  |

| 1    | 1                                                       | 0   | 1     | х   | 0   | OFF | ON            | OFF           | ON  |  |

| 1    | 1                                                       | 1   | 1     | х   | 0   | ON  | OFF           | ON            | OFF |  |

| 1    | 0                                                       | 0   | 1     | 1   | 0   | OFF | ON            | OFF           | OFF |  |

| 1    | х                                                       | х   | 1     | 1   | 1   | OFF | ON            | ON            | OFF |  |

| 1    | 0                                                       | 1   | 1     | 1   | 0   | OFF | OFF           | ON            | OFF |  |

- 1. In this case, when the FSINB input pin goes from high to low, the device moves from active mode to fail-safe mode. In fail-safe mode the OUTE control bit is automatically reset and all the gate drivers are forced in sink switch mode so that all the MOSFETs are actively switched off with the maximum available discharge current.

- In this case, the MOSFET is passively switched off through the internal resistive connection between gate and related source. In all the other cases where the MOSFET is off, it is actively switched off and forced off by the gate driver working in sink switch mode.

- If INPMODE = 1, the device works in dual half-bridge mode. The two half-bridges can be driven separately

by IN1 and IN2 input pins and can be individually disabled through DIS1 and DIS2 control bits.

| Device in active mode with INPMODE=1 (DUAL HALF-BRIDGE MODE) |                     |          |                    |                    |  |  |  |

|--------------------------------------------------------------|---------------------|----------|--------------------|--------------------|--|--|--|

| Inputs Outputs (in case of no faults); x=1,2                 |                     |          |                    |                    |  |  |  |

| FSINB                                                        | OUTE bit            | DISx bit | HSx                | LSx                |  |  |  |

| 1                                                            | 1                   | 0        | Inx                | Īnx                |  |  |  |

| 1                                                            | 0                   | x        | OFF <sup>(1)</sup> | OFF <sup>(1)</sup> |  |  |  |

|                                                              | All the other cases |          | OFF                | OFF                |  |  |  |

Table 3. Dual half-bridge mode

"Inx" means ON if logic level on Inx pin input is high and vice versa."  $\overline{\text{Inx}}$ " means OFF if logic level on Inx pin input is high and vice versa (x=1,2).

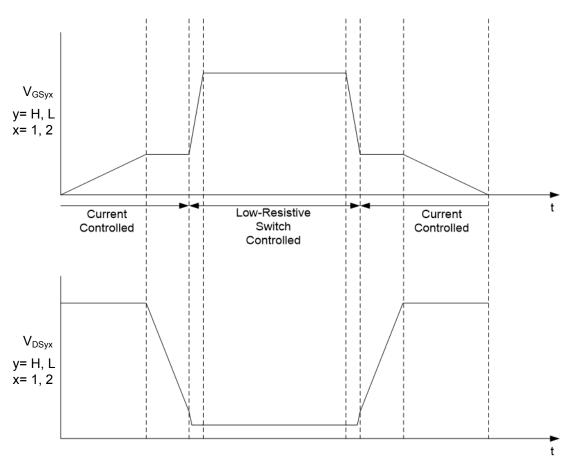

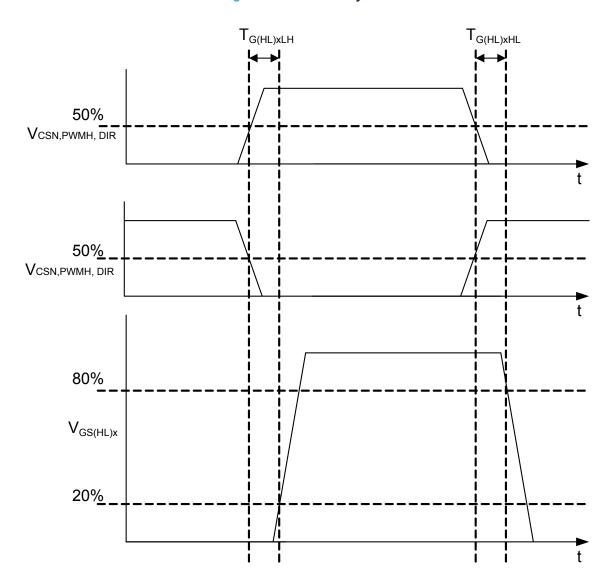

#### 2.6.2 Slew rate control (SLEW)

The rising and falling voltage slopes at the outputs can be controlled through slew rate control bits. When the SLEWzx control bits are all set to zero the gate drivers will work in switch mode providing the maximum available current to charge/discharge the MOSFETs input capacitance. The maximum available source/sink current in switch mode is internally limited (IGHx(Ch) and IGLx(Ch)). If any value different from zero is programmed, then the gate drivers will work as current source, instead of low impedance switch, as long as during the MOSFET turning on/off the drain-source voltage over the MOSFETs is above/below the switch threshold (VDSHxfSW and VDSHxrSW). Once the switch threshold is reached, the drivers will work in switch mode. The gate drivers source (charge) and sink (discharge) currents can be independently programmed through dedicated control bits in order to have different output voltage slopes during the turning on and the turning off of the MOSFETs. The MOSFETs gate charging current is programmed using the control bits SLEWCx[4:0], while the MOSFETs gate discharging current is programmed using the control bits SLEWDx[4:0]. The gate current is set depending on the SLEWzx control bits value according to the formula:

$$I_{GATE} = \frac{SLEWzx[4:0]}{31} * I_{GATEMAX}$$

(1)

SLEWzx can be either SLEWDx or SLEWCx, while  $I_{GATEMAX}$  can be either  $I_{GLxymax}$  or  $I_{GHxymax}$  (y=r for source current; y=f for sink current).

Programming SLEWzx[4:0] to 0 disables the slew rate control and enables gate driving through the low-impedance switch during the entire turning on/off process.

DS14069 - Rev 1 page 10/75

In this case, the MOSFET is passively switched off through the internal resistive connection between gate and related source. In all the other cases where the MOSFET is off, it is actively switched off and forced off by the gate driver working in sink switch mode.

GADG190920221238SA

#### 2.6.3 Short circuit detection / drain-source monitoring (DSHS/DSLS)

The voltage-drop over each MOSFET is sensed and compared to a programmable threshold to detect an overcurrent condition. This monitoring is active only on the MOSFETs driven to be turned on. In dual half-bridge mode, each half-bridge has its own programmable threshold (DSMONx[2:0]), blanking time (DSBTx[2:0]) and filtering time (FTx[1:0]). As soon as the gate driver starts to turn on a MOSFET, the corresponding drain source monitoring comparator output is masked for the programmed blanking time to give time to the MOSFET to turn on. Besides the blanking time, a filtering time is also present to filter noise. Both values have to be chosen depending on the application.

If the voltage-drop over the driven MOSFET exceeds the programmed threshold voltage  $V_{SCdx}$  (DSMON1[2:0] control bits for full-bridge or leg 1 and DSMON2[2:0] control bits for leg 2 in dual half-bridge mode) for a time longer than the programmed filtering time (and the programmed blanking time, where applicable), then:

- with DSMON\_CONFIG control bit set to zero the gate drivers belonging to the faulty leg are forced in sink switch mode to switch off actively the half-bridge MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits)

- for INPMODE set to zero and DSMON\_CONFIG control bit set to one all the gate drivers are forced in sink switch mode to switch off actively all the full-bridge MOSFETs.

In any case, the drain source monitoring flag DSHSx or DSLSx of the MOSFET detecting the fault is set. The drain-source monitoring flags have to be cleared through SPI to reactivate the affected half-bridge/full-bridge gate drivers that are forced in sink switch mode. The drain-source monitoring flag DSHSx/DSLSx can be cleared by an SPI "Read & Clear" command only if the fault condition is no longer present.

DS14069 - Rev 1 page 11/75

Figure 6. Full-bridge drain-source monitoring diagnosis

#### 2.6.4 Programmable cross current protection time (DT)

In any input mode (dual half-bridge mode or full-bridge mode), the device automatically adds a dead-time between the turn-off of a MOSFET and the turn-on of the complementary one (that is, the other MOSFET of the same leg) to avoid cross-conduction in any of the half-bridges.

In dual half-bridge mode, each half-bridge dead-time  $t_{DT}$  (from  $t_{DT0000}$  to  $t_{DT1111}$ ) is independently configurable by control bits DT1[3:0] and DT2[3:0]. Instead, in full-bridge mode, the dead time of both half-bridges is set by control bits DT1[3:0].

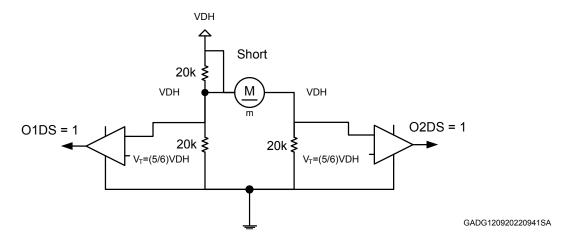

## 2.7 Diagnostic in off-mode (O1DS/O2DS)

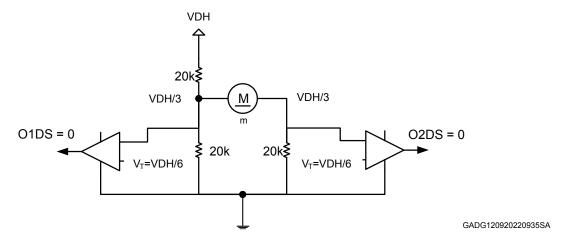

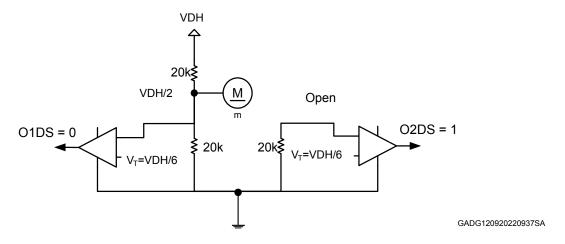

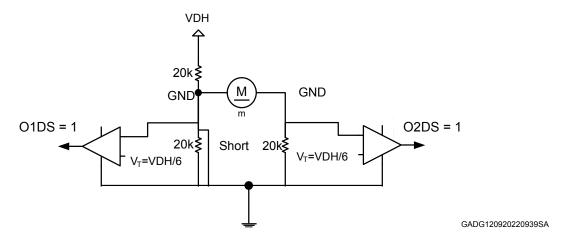

Two off-state diagnostic comparators compare the drop between each half-bridge output (SHx pin) and related LS MOSFET source (SLx) to a programmable threshold , while all the transistors are switched off. Possible system faulty conditions such as open-load, output shorted to ground or to battery, before even turning on any of the MOSFETs can be so detected.

The outputs of the off-state diagnostic comparators are always available (except in standby mode) and can be read through O1DS and O2DS status bits of the status register DSR2.

When the OUTE control bit set, the O1DS and the O2DS status bits provide the not filtered SH1 and SH2 output logic levels respect to the threshold, selected by the DSMONxy control bits, respectively. In all the other cases (except in standby mode, where everything is disabled) the O1DS and the O2DS status bits provide the not filtered SH1 and SH2 output logic levels respect to the threshold, selected by the OLTHH control bit, respectively. To run off-state diagnostic the device has to be in off-state diagnostic mode.

To enter in off–state diagnostic mode at least the OLH1L2 control bit or the OLH2L1 control bit has to be, set to one with the device OUTE control bit set to zero and CSA must be disabled. To exit from off–state diagnostic mode either the OUTE control bit is set to one or both the OLH1L2 and the OLH2L1 are set to zero. In off–state diagnostic mode a pull-up resistor is connected to one of the half-bridge outputs or to both and two pull-down resistors are connected to the two half-bridge outputs.

Considering that the pull-up resistance is the same as the pull-down resistances, the VDS of the two low side transistors (that is, the two half-bridge outputs) is expected to be equal to 1/3 VDH if a low resistive load is connected between the two legs.

On the contrary if the VDS of any of the two low sides is lower than 1/6 VDH (OLTHH=0) or higher than 5/6 VDH (OLTHH=1), then a faulty condition must be present.

Below figures and table summarize the possible faulty conditions and related OxDS status bits values.

DS14069 - Rev 1 page 12/75

Figure 7. Full-bridge open-load detection (no open-load detected)

Figure 8. Full-bridge open-load-detection (open-load detected)

Figure 9. Full-bridge open-load-detection (short to ground detected)

DS14069 - Rev 1 page 13/75

Figure 10. Full-bridge open-load-detection (short to VDH detected)

In case of short to VDH detection, achieved for OLTHH=1, the outputs of the two off-state diagnostic comparators are inverted to be compliant to Table 4.

Table 4. Full-bridge monitoring in off-mode

| Control bits |        | Failure bits |      | Comments |                               |

|--------------|--------|--------------|------|----------|-------------------------------|

| OLH1L2       | OLH2L1 | OLTHH        | O1DS | O2DS     |                               |

| 0            | 0      | 0            | 0    | 0        | Off-state diagnostic disabled |

| 1            | 0      | х            | 0    | 0        | No open-load detected         |

| 1            | 0      | 0            | 0    | 1        | Open-load SH2                 |

| 1            | 0      | 0            | 1    | 1        | Short to GND                  |

| 1            | 0      | 1            | 1    | 1        | Short to VDH                  |

| 0            | 1      | х            | 0    | 0        | No open-load detected         |

| 0            | 1      | 0            | 1    | 0        | Open-load SH1                 |

| 0            | 1      | 0            | 1    | 1        | Short to GND                  |

| 0            | 1      | 1            | 1    | 1        | Short to VDH                  |

What reported in this chapter applies only to single motor full-bridge configuration; that is, the case where one full-bridge drives only one motor.

In dual half-bridge mode (INPMODE = 1), the device can still detect an open-load condition.

In off-state diagnostic mode, it is recommended to wait at least 2.5 ms, starting from any change of OLH2L1, OLH1L2 or OLTHH control bits, before reading stable O1DS and O2DS status bits values.

DS14069 - Rev 1 page 14/75

## 2.8 Fail-safe output switch-off input not pin (FSINB)

The L99H92 features an asynchronous, logic independent fail-safe input pin working as a redundant switch-off path for all MOSFETs. The fail-safe input not pin (FSINB), active low, has an internal pull-down resistance RFSINB. As soon as the FSINB pin falls below the VFSINBLTH threshold for a time longer then t<sub>FSINB</sub> filt, the FSINLL status bit together with the FSIN status bit are set and the device is put in fail-safe mode. In fail-safe mode the OUTE control bit is reset and the gate drivers are forced in sink switch mode to switch off actively all the MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). As long as the FSINB input pin is low, the gate drivers are forced in sink switch mode and the OUTE control bit is forced to zero. For functional safety reasons, the FSINHS1,2 and the FSINLS1,2, status bits indicate whether the HS1,2 and the LS1,2, gate drivers have been put successfully in sink switch mode or not, because of the FSINB pin pulled low. Once the FSINB pin has been pulled low, in order to reactivate again the gate drivers that are forced in sink switch mode, the FSINB pin has to rise above the VFSINHTH threshold for a time longer than the filtering time. All the FSINHSx and the FSINLSx status bits have to go back to zero (indicating that all the gate drivers came out of forced sink switch mode and making the device come out of fail-safe mode) and then the OUTE control bit has to be set back to one via SPI. In case where at least one of the status bits FSINHSx or FSINLSx will remain set, indicating that at least one gate driver did not come out of forced sink switch mode. the device remains in fail-safe mode. With the FSINB pin high and the OUTE control bit reset, the gate drivers are disabled, leaving just a resistive link between gate and source of each MOSFET.

The FSINB input pin status can be read, but not cleared, through FSINLL status bit. The FSIN status bit, linked to the global status byte fail-safe bit (FS), is the logical OR of the following status bits: FSINLL, FSINHS1, FSINHS1, FSINHS2, and FSINLS2. The fail-safe input pin acts just on the gate drivers and on the OUTE control bit.

## 2.9 Diagnostic not output (DIAGN)

The microcontroller can use the DIAGnostic not (DIAGN) output pin, active low, to detect a device fault, including a device power-on-reset event. The purpose of the DIAGN output pin is to warn immediately the microcontroller that a new fault has been detected by the device, without the need of periodic SPI transfers. The DIAGN output pin has an internal weak pull-up resistance (RDIAGN). The logic level signal at the pin is the logical NOR combination of all the status flags and status bits linked to the pin through the DIAGCR control register, together with the global status byte RSTB bit. Once the device comes out of standby mode, the DIAGN pin is pulled low because of the global status byte RSTB bit. If just the global status byte RSTB bit is set, any valid SPI communication frame clears the RSTB bit pulling up the DIAGN pin. Any read access to the DSR1 register resets this signal to high level, until an error coming from a new source occurs pulling again the pin low. If a fault coming from a new error source occurs during the read access to the DSR1 register, the DIAGN output pin remains low (this avoids any loss of information since the new error source status flag/bit will not be reported by the concomitant read access, but a new read access would be required). Even if a read operation of the status register should always come before a Read & Clear operation, any Read & Clear operation of status register DSR1 will pull the DIAGN pin high. If a new source of fault triggers an error during the Read & Clear access to the DSR1 register, the Read & clear operation will not pull the DIAGN pin high at the CSN rising edge of the DSR1 register Read & Clear operation (this will avoid any loss of information since the new error source status flag/bit will not be reported by the concomitant Read & Clear access, but a new read or Read & Clear access would be required).

## 2.10 Current monitors

The current sense amplifiers (CSA1 and CSA2) are designed for current sensing in automotive applications. They are independent, bidirectional, single-supply differential amplifiers with a wide input common mode voltage range (VICM). They support high-side current sensing, low side-current sensing and in-line current sensing through two sensing resistors.

A gain of 100, 50, 20 or 10 is independently SPI programmable for each CSA. Since the CSAs have a transconductance input stage, input series resistors (for filtering etc.) should not exceed 50  $\Omega$  to keep the additional gain error below 1%.

The CSO outputs are compliant to the VDD power supply rail and have a programmable offset set by CSA100 and CSA200 control bits. If these bits are reset, the output offset is set to VO0, otherwise it is set to VO1. The current sense amplifiers input stage is supplied by the charge pump. When the charge pump is disabled, the CSAs is disabled as well.

By default, both current sense amplifiers are enabled. To reduce current consumption both of them can be disabled independently through control bits DCSA1 and DCSA2.

DS14069 - Rev 1 page 15/75

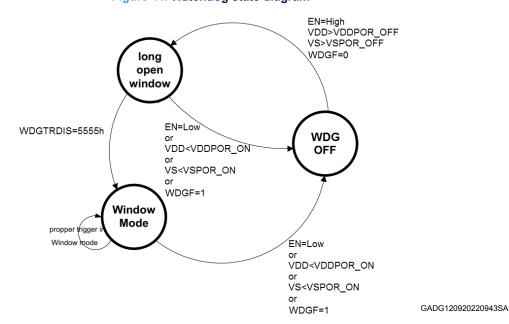

## 2.11 Window watchdog (WDG)

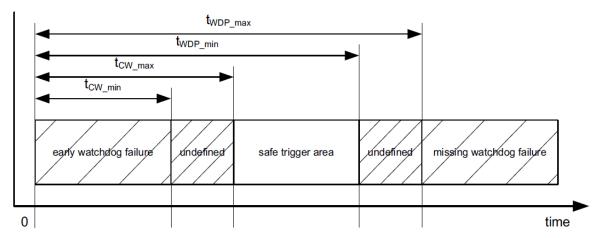

Out of standby mode, the L99H92 watchdog monitors the microcontroller status within a periodic window.

By default, as soon as the device enters in active mode, the watchdog is enabled and start running with a long open window ( $t_{LOW}$ ). The long open window provides more time to the microcontroller for the L99H92 initialization and allows the watchdog disabling procedure to be run, when no watchdog is required by the application. To trigger the watchdog for the first time during a Long Open Window (LOW), the microcontroller has to write 5555h to the watchdog trigger/disable register (WDGTRDIS) before the end of the long open window. After the first valid watchdog trigger, the watchdog will enter in window mode. In window mode the microcontroller has to serve the watchdog by alternating the watchdog trigger bits (that is, 2AAAh,5555h,...) of the watchdog trigger/disable register (WDGTRDIS) within the watchdog open window ( $t_{CW}$  and  $t_{WDP}$ ). Any correct watchdog trigger SPI frame will immediately start a new window.

In case of a watchdog failure (root cause can be any watchdog trigger outside the open window; invalid or unexpected watchdog trigger bits value; any watchdog timeout; any disabling procedure out of the LOW; any wrong disabling procedure during the LOW) will set the WDGF flag, stop the watchdog and put the device in fail-safe mode. In fail-safe mode the OUTE control bit is reset and the gate drivers are forced in sink switch mode to switch off actively all the MOSFETs with the maximum available current, regardless of the programmed gate discharge current (SLEWDx control bits). To reactivate the gate drivers that are forced in sink switch mode, the WDGF flag has to be cleared via SPI (clearing the WDGF flag makes the device come out of the fail-safe mode and makes the watchdog start again with a long open window) and then the OUTE control bit has to be set to one via SPI. As long as the device is in fail-safe mode (WDGF=1), the OUTE control bit is reset and cannot be set via SPI. Once the watchdog starts running again with a long open window after coming out of the fail-safe mode, to enter in window mode the microcontroller has to write 5555h to the watchdog trigger/disable register (WDGTRDIS). To disable the watchdog, the microcontroller has to write a specific key, consisting in two consecutive valid SPI frames to be sent in the right order, to control register WDGTRDIS before the end of any long open window. Just one attempt to disable the watchdog is allowed per LOW, if not successful, a watchdog fault is generated, and it will no longer be possible to disable the watchdog until the next LOW. Any other SPI transfer between the two SPI frames carrying the key including an invalid SPI transfer generating an SPIE aborts the disable process and generate a watchdog fault (WDGF). Besides, the keys sent in the wrong order will not disable the watchdog and generate a watchdog fault as well. Once in window mode, it will no longer be possible to disable the watchdog until the next LOW. Any attempt to disable the watchdog outside the LOW will generate a watchdog fault (WDGF).

Any read access to the WDGTRDIS register provides information concerning the watchdog disabling procedure result together with the three least significant bits of the latest write operation performed on the same register.

Figure 11. Watchdog state diagram

DS14069 - Rev 1 page 16/75

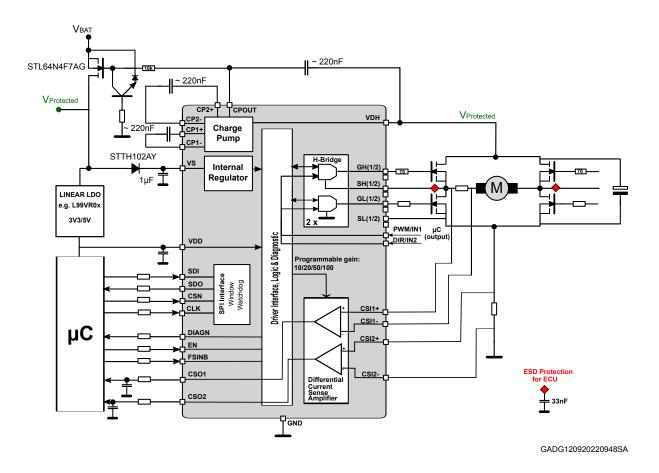

# 3 Application

Figure 12. Application schematic

DS14069 - Rev 1 page 17/75

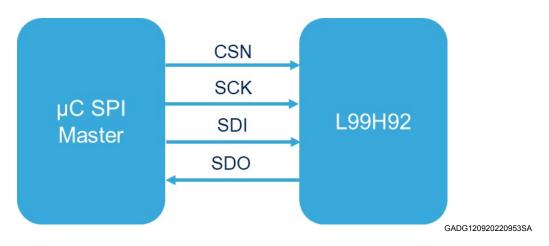

# 4 Serial peripheral interface (SPI)

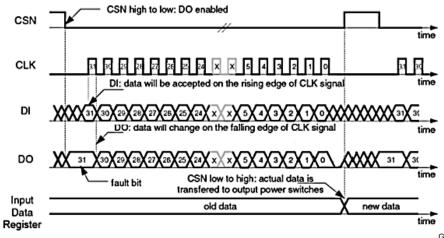

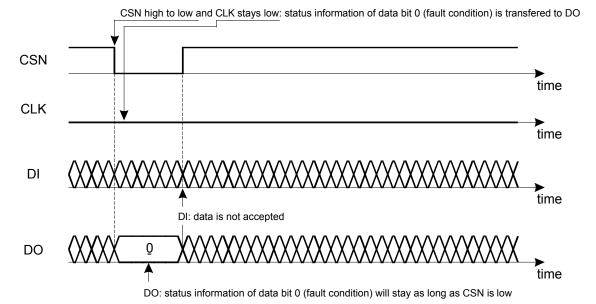

A 24-bit SPI is used for bidirectional communication with the microcontroller.

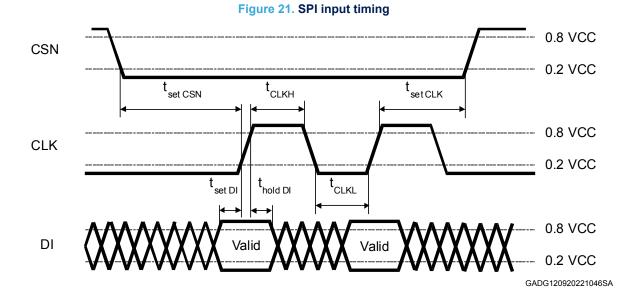

The microcontroller SPI peripheral must run in the following configuration:

CPOL = 0 and CPHA = 0.

In this configuration the input data is sampled by the low to high transition of the serial clock CLK, and the output data is changed by the high to low transition of the serial clock CLK.

Any fault condition can be detected without even providing any serial clock CLK by setting CSN low. In fact, if CSN = 0, the serial data output SDO pin will reflect the global error flag (GSBN bit of the global status byte) of the device.

Chip select not (CSN)

The CSN input pin is used to address the SPI communication with the device. When CSN is high, the output pin (SDO) is in high impedance. When CSN is low, the output pin (SDO) driver is enabled and a serial communication can start. The information transferred during CSN = 0 is called a communication frame.

If CSN = low for  $t > t_{CSNfail}$  the SDO output will be switched into high impedance to allow SPI communications with other SPI nodes.

Serial data in (SDI)

The SDI input pin is used to transfer data into the device. The data applied to the SDI will be sampled at the rising edge of the serial CLK signal and shifted into an internal 24 bit shift register. At the rising edge of the CSN signal the content of the shift register will be transferred to Data Input Register. The writing to the selected Data Input Register is enabled only if exactly 24 bits are transmitted within one communication frame (that is, CSN low). If more or less than 24 clock pulses are counted within one frame the complete frame will be ignored. This safety function is implemented to avoid an activation of the output stages by any wrong communication frame.

Note: Due to this safety functionality, daisy chaining is not possible. Instead, a parallel operation of the SPI bus by controlling the CSN signal of the connected IC's is recommended.

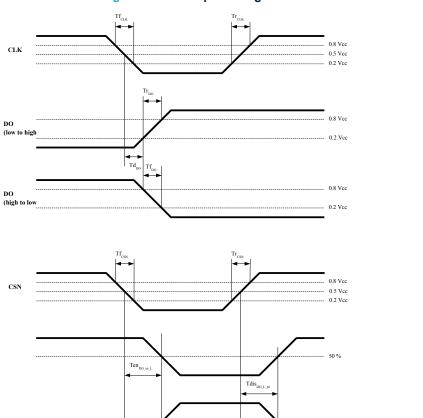

Serial data out (SDO)

The SDO output driver is activated by a logical low level at the CSN input and will go from high impedance to low or high level depending on the global error flag value (GSBN bit). The first falling edge of the CLK input after a high to low transition of the CSN pin transfers the next global status byte bit out. Each subsequent falling edge of the CLK shifts the following bits out.

Serial clock (CLK)

The CLK input pin is used to synchronize the input and output serial bit streams. The data input (SDI) is sampled at the rising edge of the CLK and the data output (SDO) will change with the falling edge of the CLK. The SPI can work with a CLK frequency up to 4 MHz (1/t<sub>CLK</sub>).

#### 4.1 ST SPI 4.1

The ST-SPI is a standard used in ST automotive ASSP devices.

This chapter describes the SPI protocol standardization. It defines a common structure of the communication frames and defines specific addresses for product and status information.

The ST-SPI allows usage of generic software to operate the devices while maintaining the required flexibility to adapt it to the individual functionality of a particular product. In addition, fail-safe mechanisms are implemented to protect the communication from external influences and wrong or unwanted usage.

The device serial peripheral interface is compliant to the ST SPI standard rev. 4.1.

DS14069 - Rev 1 page 18/75

## 4.1.1 Physical layer

Figure 13. SPI pins description

#### 4.1.2 Clock and data characteristics

The ST-SPI can be driven by a microcontroller with its SPI peripheral running in the configuration:

- CPOL = 0

- CPHA = 0

SCK

SDI MSB LSB

GADG120920220954SA

Figure 14. SPI signal description

Any communication frame starts with the falling edge of the CSN (Communication Start). CLK has to be low.

The SDI data is then latched at the following rising CLK edges into the internal shift registers.

After *Communication Start* the SDO leaves 3-state mode and present the MSB of the data shifted out to SDO. At all following falling CLK edges, data is shifted out through the internal shift registers to SDO.

The communication frame is finished with the rising edge of CSN. If a valid communication took place (for example, correct number of CLK cycles, access to a valid address, no parity error), the requested operation according to the operating code will be performed (write or clear operation).

## 4.1.3 Communication protocol

#### **SDI frame**

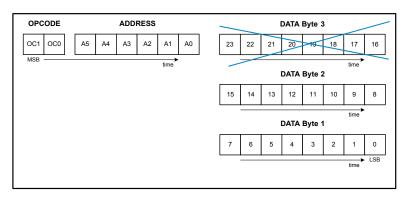

The device data-in frame consists of 24 bits (OpCode (2 bits) + Address (6 bits) + Data Byte 2 (8 bits) + Data Byte 1 (8 bits)).

DS14069 - Rev 1 page 19/75

Note:

The first two transmitted bits (MSB, MSB-1) contain the operation code, which represents the command/instruction that will be performed. The following 6 bits (MSB-2 to MSB-7) represent the address on which the command/operation will be performed.

The subsequent two bytes contain the payload.

Figure 15. SDI frame

GADG120920221006SA

#### Operating code

The operating code is used to distinguish between different commands/operations on registers of the slave device.

Table 5. Operation codes

| OC1 | OC0 | Description                     |  |  |  |  |

|-----|-----|---------------------------------|--|--|--|--|

| 0   | 0   | Write command                   |  |  |  |  |

| 0   | 1   | Read command                    |  |  |  |  |

| 1   | 0   | Read & Clear command            |  |  |  |  |

| 1   | 1   | Read device information command |  |  |  |  |

Any **Write command** (with no parity error, no wrong address and no CLK count error) will modify the content of the addressed control register with the payload. Besides this, a shift out of the content (data present at *Communication Start*) of the addressed register is performed.

A **Read command** shifts out the data present in the addressed register at **Communication Start**. The payload data is ignored, and the data of the addressed register will not be modified. Moreover, a **Burst Read** can be performed.

A **Read & Clear command** (with no parity error, no wrong address and no CLK count error) will lead to a clear of addressed status bits. The bits to be cleared are defined first by address, second by payload bits set to '1'. Besides this, a shift out of the content (data present at **Communication Start**) of the register is performed.

avoid any loss of any reported status that it is recommended to clear just the status register bits, which are

already reported in the previous communication frame (Selective Bitwise Clear).

#### Advanced operation codes

Two Advanced Operation Codes can be used to set all control registers to the default value and to clear all status registers by one single SPI frame respectively.

A 'set all control registers to default' command is launched when an SPI frame with OpCode '11' and address '111111' is sent to the device.

A 'clear all status registers' command is launched when an SPI frame with OpCode '10' and address'111111' is sent to the device.

#### Data-in payload

The *Payload* (Data Byte 1 to Data Byte 2) is the data transferred to the device with every SPI communication. The *Payload* always follows the OpCode and the Address bits.

DS14069 - Rev 1 page 20/75

For write access the *Payload* represents the new data written to the addressed register. For *Read & Clear* commands the *Payload* defines which bits of the addressed Status Register will be cleared. In case of a '1' at the corresponding bit position the status flag will be cleared.

For a Read Operation, the *Payload* is not used. For functional safety reasons it is recommended to set unused *Payload* to '0'.

#### **SDO frame**

The data-out frame consist of 24 bits (GSB (8 bits) + Data Byte 2 (8 bits) + Data Byte 1 (8 bits)).

The first eight transmitted bits contain device related status information and are latched into the shift register at the time of the *Communication Start*. These 8 bits are transmitted at every SPI transaction.

The subsequent bytes contain the payload data and are latched into the shift register with the eighth positive CLK edge.

This could lead to an inconsistency of data between the GSB and *Payload* due to different shift register load times. Anyhow, no unwanted status register clear should appear, as status information should just be cleared with a dedicated bit clear after.

Global Status Byte (GSB) DATA Byte 3 GSBN RSTB SPIE PLE FE 23 22 20 17 DATA Byte 2 15 13 12 11 DATA Byte 1 6 5 3 0

Figure 16. SDO frame

GADG120920221019SA

#### Global status byte (GSB)

The global status byte bits, from Bit16 to Bit19, represent a logical OR combination of status flags and status bits located in the status register DSR1. Therefore, no direct Read & Clear command can be performed on these GSB bits.

Table 6. Global status byte

| Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| GSBN   | RSTB   | SPIE   | -      | FE     | DE     | GW     | FS     |

#### Global status bit not (GSBN)

The GSBN is a logically NOR combination of global status byte bits from bit 16 to bit 22. This bit can also be used as *Global Error Flag* without starting a complete communication frame as it is directly present on SDO after pulling CSN low.

GSBN = 1 (No error)

GSBN = 0 (Error)

#### ReSeT bit (RSTB)

The RSTB bit indicates that all the device registers have been reset to default. By default, it is set to one coming out from standby mode. It is reset automatically after any valid SPI communication frame.

#### SPI error bit (SPIE)

The SPIE bit is a logical OR combination of all the errors related to a wrong SPI communication.

Besides, the CLK count, the CSN low timeout and the SDI stuck at errors, the parity error and the read/write from/to wrong address are reported here as well.

The SPIE bit is automatically cleared by any valid SPI communication frame.

DS14069 - Rev 1 page 21/75

#### Functional error bit (FE)

The FE bit is a logical OR combination of errors coming from application specific functional items:

#### Overcurrent status flags (DSHSx, DSLSx)

Device error bit (DE)

The DE bit is a logical OR combination of errors related to device specific blocks:

- VDH overvoltage status flag (VDHOV)

- VDH undervoltage status flag (VDHUV)

- VDD overvoltage status flag (VDDOV)

- Thermal shutdown status flag (TSD)

- Charge pump not ready status bit (NRDY)

- Charge pump low status flag/bit (CPLOW)

- Digital input/output overvoltage status flag (DIOOV)

Global warning bit (GW). The GW bit is a logical OR combination of all warning flags:

- Thermal warning status flag (TW)

- VS overvoltage warning status flag (VSOVW)

Fail-safe bit (FS). The FS bit indicates that the device was forced into fail-safe mode due to watchdog failure or due to FSINB input pin pulled low.

- Watchdog fault status flag (WDGF)

- Fail-safe input not status bit (FSIN)

#### **Data-out payload**

The Payload (data Byte1 and 2) is the data transferred from the slave device with every SPI communication to the master device (in-frame-response). The Payload always follows the global status byte.

#### 4.1.4 **Address definition**

Table 7. Address definition - device application access

| Device application access |     |  |  |  |  |

|---------------------------|-----|--|--|--|--|

| Operating code            |     |  |  |  |  |

| OC1                       | OC0 |  |  |  |  |

| 0                         | 0   |  |  |  |  |

| 0                         | 1   |  |  |  |  |

| 1                         | 0   |  |  |  |  |

Table 8. Address definition - device information read access

| Device information read access |     |  |  |

|--------------------------------|-----|--|--|

| Operating code                 |     |  |  |

| OC1                            | OC0 |  |  |

| 1                              | 1   |  |  |

Table 9. Address definition - RAM access

| RAM address | Description  | Access |

|-------------|--------------|--------|

| 3FH         | Advanced Op. | С      |

| 3EH         | Reserved     | None   |

|             |              |        |

|             |              |        |

|             |              |        |

DS14069 - Rev 1 page 22/75

| RAM address | Description                | Access |

|-------------|----------------------------|--------|

| 0DH         | Reserved                   | None   |

| 0CH         | Reserved (RESVDI)          | R      |

| 0BH         | Reserved (RESVDO)          | R/W    |

| 0AH         | Contro register (WDGTRDIS) | R/W    |

|             |                            |        |

| 02H         | Status register (DSR2)     | R      |

| 01H         | Status register (DSR1)     | R/C    |

| 00H         | Reserved                   | None   |

Table 10. Address definition - ROM access

| ROM Address | Description                   | Access |

|-------------|-------------------------------|--------|

| 3FH         | <advanced op.=""></advanced>  | W      |

| 3EH         | <gsb options=""></gsb>        | R      |

|             |                               |        |

| 20H         | <spi cpha="" test=""></spi>   | R      |

| 16H         | <wd 4="" bit="" pos.=""></wd> | R      |

| 15H         | <wd 3="" bit="" pos.=""></wd> | R      |

| 14H         | <wd 2="" bit="" pos.=""></wd> | R      |

| 13H         | <wd 1="" bit="" pos.=""></wd> | R      |

| 12H         | <wd 2="" type=""></wd>        | R      |

| 11H         | <wd 1="" type=""></wd>        | R      |

| 10H         | <spi mode=""></spi>           | R      |

|             |                               |        |

| 0AH         | <silicon ver.=""></silicon>   | R      |

|             |                               |        |

| 05H         | <device n.4=""></device>      | R      |

| 04H         | <device n.3=""></device>      | R      |

| 03H         | <device n.2=""></device>      | R      |

| 02H         | <device n.1=""></device>      | R      |

| 01H         | <device family=""></device>   | R      |

| 00Н         | <company code=""></company>   | R      |

#### Information registers

The device information registers can be read by using OpCode '11'. After shifting out the GSB the 8-bit wide payload will be transmitted. By reading device information registers a communication width which is minimum 16 bits plus a multiple by 8 can be used. After shifting out the GSB followed by the 8bit wide payload a series of '0' is shifted out at the SDO.

Table 11. L99H92 information registers map

| ROM Address | Description                  | Access |               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|------------------------------|--------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 3FH         | <advanced op.=""></advanced> |        |               |       |       |       |       |       |       |       |       |

| 3EH         | <gsb options=""></gsb>       | R      | $\rightarrow$ | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

DS14069 - Rev 1 page 23/75

| ROM Address | Description                   | Access |               | Bit 7 | Bit 6   | Bit 5   | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0 |

|-------------|-------------------------------|--------|---------------|-------|---------|---------|-------|-------|---------|---------|-------|

| •••         |                               |        |               |       |         |         |       |       |         |         |       |

| 20H         | <spi cpha="" test=""></spi>   | R      | $\rightarrow$ | 0     | 1       | 0       | 1     | 0     | 1       | 0       | 1     |

| 16H         | <wd 4="" bit="" pos.=""></wd> | R      | $\rightarrow$ |       |         |         | 00    | ЭH    |         |         |       |

| 15H         | <wd 3="" bit="" pos.=""></wd> | R      | $\rightarrow$ |       |         |         | 00    | ЭH    |         |         |       |

| 14H         | <wd 2="" bit="" pos.=""></wd> | R      | $\rightarrow$ |       |         |         | 00    | ΡΗ    |         |         |       |

| 13H         | <wd 1="" bit="" pos.=""></wd> | R      | $\rightarrow$ |       |         |         | 49    | ЭН    |         |         |       |

| 12H         | <wd 2="" type=""></wd>        | R      | $\rightarrow$ |       |         |         | A     | 4H    |         |         |       |

| 11H         | <wd 1="" type=""></wd>        | R      | $\rightarrow$ |       |         |         | 4/    | λH    |         |         |       |

| 10H         | <spi mode=""></spi>           | R      | $\rightarrow$ |       |         |         | A     | 1H    |         |         |       |

|             |                               |        | $\rightarrow$ |       |         |         |       |       |         |         |       |

| 0AH         | <silicon ver.=""></silicon>   | R      | $\rightarrow$ |       | major ı | evision |       |       | minor r | evision |       |

|             |                               |        | $\rightarrow$ |       |         |         |       |       |         |         |       |

| 05H         | <device no.4=""></device>     | R      | $\rightarrow$ |       |         |         | 40    | СН    |         |         |       |

| 04H         | <device no.3=""></device>     | R      | $\rightarrow$ |       |         |         | 36    | 6H    |         |         |       |

| 03H         | <device no.2=""></device>     | R      | <b>→</b>      | 52H   |         |         |       |       |         |         |       |

| 02H         | <device no.1=""></device>     | R      | <b>→</b>      | 55H   |         |         |       |       |         |         |       |

| 01H         | <device family=""></device>   | R      | <b>→</b>      | 01H   |         |         |       |       |         |         |       |

| 00H         | <company code=""></company>   | R      | $\rightarrow$ | 00Н   |         |         |       |       |         |         |       |

## **Device identification registers**

These registers represent a unique signature to identify the device and silicon version.

- <Company Code>: 00H (STMicroelectronics)

- <Device Family>: 01H (BCD Power Management)

- <Device No. 1>: 55H (ASCII code for U)

- <Device No. 2>: 52H (ASCII code for R)

- <Device No. 3>: 36H (ASCII code for 6)

- <Device No. 4>: 4CH (ASCII code for L)

## **SPI** modes

By reading out the <SPI Mode> register, general information of the device SPI can be read.

Table 12. SPI mode registers

| Bit7 | Bit6 | Bit5 | Bit 4 | Bit 3 | Bit 2 | Bit1 | Bit0 |

|------|------|------|-------|-------|-------|------|------|

| BR   | DL2  | DL1  | DL0   | 0     | 0     | S1   | S0   |

| 1    | 0    | 1    | 0     | 0     | 0     | 0    | 1    |

<SPI Mode>: A1H (Burst Mode read available, 24 bit SPI frame, parity error check)

## SPI burst read

Table 13. Burst read bit

| Bit 7 | Description      |

|-------|------------------|

| 0     | BR not available |

| 1     | BR available     |

DS14069 - Rev 1 page 24/75

The SPI Burst Read bit indicates whether the burst read mode is available or not. The Burst Read can be used to perform a device internal memory dump to the SPI Master.

The start of the *Burst Read* is like a normal *Read Operation*. The difference is that after the *SPI Data Length* the CSN is not pulled high and the CLK will be continuously clocked. When the normal CLK max count is reached (SPI data length) the consecutive addressed data is latched into the shift register. This procedure is performed every time the CLK payload length is reached.

In case the automatically incremented address is not used by the device, undefined data is shifted out. An automatic address overflow is implemented when address 3FH is reached.

The SPI Burst Read is limited by the CSN low timeout.

#### SPI data length

The SPI Data Length value indicates the length of the CLK count monitor which is running for all accesses to the Device Registers. Any communication frame with a CLK count not equal to the reported one will trigger an SPI error and the corresponding command/operation will be ignored.

Bit 5 Bit 4 Bit 6 Description DL2 DL1 DL0 0 0 0 invalid 0 16-bit SPI 1 0 24-bit SPI 1 0 0 32-bit SPI 1 1 1 1 1 64-bit SPI

Table 14. SPI data length

#### Data consistency check (parity/CRC)

Table 15. Data consistency check

| Bit 1       | Bit 0 Description |             |  |  |

|-------------|-------------------|-------------|--|--|

| <b>\$</b> 1 | S0                |             |  |  |

| 0           | 0                 | not used    |  |  |

| 0           | 1                 | Parity used |  |  |

| 1           | 0                 | CRC used    |  |  |

| 1           | 1                 | Invalid     |  |  |

## Watchdog identification registers

The <WD Type 1> and <WD Type 2> ROM registers are defined as follows:

Table 16. WD type ROM registers

|                        | Bit 7 | Bit 6 | Bit 5                     | Bit 4                                            | Bit 3 | Bit 2      | Bit 1       | Bit 0 |  |

|------------------------|-------|-------|---------------------------|--------------------------------------------------|-------|------------|-------------|-------|--|

|                        | WD1   | WD0   |                           |                                                  |       |            |             |       |  |

| <wd 1="" type=""></wd> | 0     | 1     | WT5                       | WT4                                              | WT3   | WT2        | WT1         | WT0   |  |

|                        |       |       | Wa                        | Watchdog timeout/long open window WT[5:0] * 5 ms |       |            |             |       |  |

| <wd 2="" type=""></wd> | 1     | 0     | OW1                       | OW0                                              | CW3   | CW2        | CW1         | CW0   |  |

|                        |       |       | Open window OW[1:0] *5 ms |                                                  | Clos  | sed window | CW[3:0] * 5 | 5 ms  |  |

DS14069 - Rev 1 page 25/75

The binary value of WT[5:0] times 5 ms indicates the maximal safe long open window time. CW[3:0] times 5 ms defines the maximum closed window time and WW[1:0] times 5 ms defines the minimum safe open window time.

The watchdog trigger register address is defined by the <WD bit pos. 1> ROM register.

#### Device application registers (RAM)

The Device Application Registers are all registers accessible using OpCode '00', '01' and '10'. The functions of these registers are defined in the device specification.

#### Protocol failure detection

To achieve a communication protocol that covers certain fail-safe requirements a basic set of SPI communication failure detection mechanisms are implemented.

#### **Clock monitor**

During communication (CSN low) a clock monitor counts the valid CLK clock edges. If the CLK edges do not correlate with the *SPI Data Length* an SPIE is reported with the next command and the actual command is rejected.

By accessing the *Device Information Registers* (OpCode = '11') the *Clock Monitor* is set to a minimum of 24 CLK edges plus a multiple by 16 (for example, 16, 32, , ...).

Providing no CLK edge during the CSN low phase is not recognized as an SPIE. For an *SPI Burst Read* also the *SPI Data Length* plus multiple numbers of *Payloads* CLK edges are assumed as a valid communication.

#### CLK polarity (CPOL) check

To detect the wrong polarity access via CLK the internal clock monitor is used. Providing first a negative edge on CLK during communication (CSN low) or a positive edge at last will lead to an *SPI Error* reported in the next communication and the actual command is rejected.

#### CLK phase (CPHA) check

To verify that the *CLK Phase* of the SPI master is set correctly a special *Device Information Register* is implemented. By reading this register the data must be 55H. In case AAH is read, the CPHA setting of the SPI master is wrong and a proper communication cannot be guaranteed.

#### **CSN** timeout

By pulling CSN low the SDO is set active and leaves its tristate condition. To ensure communication between other SPI devices within the same bus even in case of CSN stuck @ low a CSN timeout is implemented. By pulling CSN low an internal timer is started. When the timer reaches its end, the ongoing command is rejected, the SPIE is set (and it will be visible at the next communication) and the SDO is set in tristate condition.

## SDI stuck at LOW

As a communication with data all-'0' and OpCode '00' on address b'000000 cannot be distinguished between a valid command and a SDI stuck @ LOW, this communication is not allowed. Nevertheless, in case a stuck @ LOW is detected the command will be rejected and the SPIE will be set and it will be visible at the next communication.

#### SDI stuck at HIGH

As a communication with data all-'1' and OpCode '11' on address b'111111 cannot be distinguished between a valid command and a SDI stuck @ HIGH, this communication is not allowed. In case a stuck @ HIGH is detected the command will be rejected and the SPIE will be set and it will be visible at the next communication.

## SDO stuck @

The SDO stuck @ GND and stuck @ HIGH has to be detected by the SPI master. As the definition of the GSB quarantees at least one toggle, a GSB with all '0' or all '1' reports a stuck at error.

DS14069 - Rev 1 page 26/75

## 5 Electrical characteristics

## 5.1 Absolute max rating

Stressing the device above the rating listed in Table 17 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 17. Absolute maximum ratings

| Symbol                                                    | Paran                                              | Value                         | Unit                          |   |

|-----------------------------------------------------------|----------------------------------------------------|-------------------------------|-------------------------------|---|

| V V                                                       | Power supply voltage                               | - 0.3 to 28                   |                               |   |

| $V_{DH}, V_{S}$                                           | Single pulse t <sub>max</sub> < 400 n              | าร                            | 40                            | V |

| VDD                                                       | I/O supply voltage                                 |                               | -0.3 to 18                    | V |

| SDI, SDO, CLK, CSN,<br>EN, DIR/IN2, PWM/IN1, DIAGN, FSINB | Digital input/ output voltage                      | -0.3 to V <sub>DD</sub> + 0.3 | V                             |   |

| CSO1, CSO2                                                | Analog output voltage                              |                               | -0.3 to V <sub>DD</sub> + 0.3 | V |

| CSI1+, CSI1-, CSI2+, CSI2-                                | HV signal pins                                     |                               | -6 to 40                      | V |

| CSI1+, CSI1-, CSI2+, CSI2-                                | Differential input voltage range HV signal pins -1 |                               | -19 to +19                    | V |

| GL2, GH2, GL1,<br>GH1 (Gxy)                               | HV signal pins                                     | HV signal pins                |                               |   |

| SL2, SH2, SL1, SH1                                        | HV signal pins                                     |                               | VCPOUT + 0.3<br>-6 to 40      | V |

| CP2-, CP1-                                                | HV signal pins                                     |                               | -0.3 to 42                    | V |

| CP1+                                                      | LIV signal pip                                     | VDH ≤ 26 V                    | VDH-0.3 to VDH+14             | V |

| CP1+                                                      | HV signal pin                                      | VDH > 26 V                    | VDH-0.3 to +42                | V |

| CD2.                                                      | IN/ simplinin                                      | VDH ≤ 26 V                    | VDH-0.6 to VDH+14             |   |

| CP2+                                                      | HV signal pin                                      | VDH > 26 V                    | VDH-0.6 to +42                | V |

| CPOUT                                                     | VDH ≤ 26 V                                         |                               | VDH-0.3 to VDH+14             | V |

| CPOUT                                                     | HV signal pin                                      | VDH > 26 V                    | VDH-0.3 to +42                | v |

## 5.2 ESD protection

Table 18. ESD protection

| Parameter                                                                                                 | Value | Unit |

|-----------------------------------------------------------------------------------------------------------|-------|------|

| Electrostatic discharge test (AECQ100-002-E) all pins                                                     | ±2    | kV   |

| Electrostatic discharge test (AECQ100-002-E) output pins SHx (X = 1,2), CSI1x (X = +,-) , CSI2x (X = +,-) | ±4    | kV   |

| Charge device model (CDM-AEC-Q100-011) all pins                                                           | ±500  | V    |

| Charge device model (CDM-AEC-Q100-011) corner pins                                                        | ±750  | V    |

DS14069 - Rev 1 page 27/75

## 5.3 Thermal data

Table 19. Thermal operating range

| Item  | Symbol           | Parameter                      | Value      | Unit |

|-------|------------------|--------------------------------|------------|------|

| 5.3.1 | TJ               | Operating junction temperature | -40 to 150 | °C   |

| 5.3.2 | T <sub>stg</sub> | Storage temperature            | -55 to 150 | °C   |

Table 20. Temperature warning and thermal shutdown