# Low Capacitance TransClamp® Surge Protection for xDSL Interfaces

### PROTECTION PRODUCTS

### **Description**

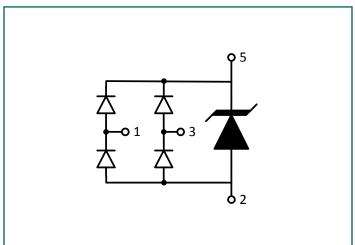

TClamp®2472S is specifically designed to provide secondary surge and ESD protection for Class-H VDSL2 line drivers. TClamp2472S integrates low capacitance, surge-rated steering diodes with a high power transient voltage suppressor (TVS). The TVS utilizes snap-back or "crow-bar" technology to minimize device clamping voltage and features high surge current capability of 20A (tp=8/20us).

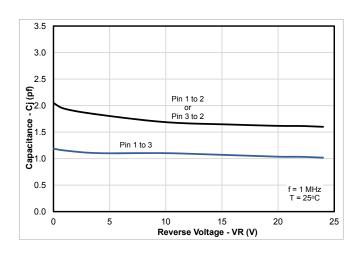

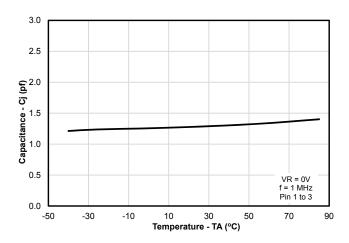

TClamp2472S capacitance is limited to 3.5pF maximum with a typical capacitance variation of 0.10pF over the operating voltage range. This ensures correct signal transmission on VDSL lines. The biased bridge structure allows the device to be used in VDSL2 applications that utilize asymetrical Class-H line drivers with operating voltages up to 24Vp-p.

TClamp2472S is in a 6-pin SOT-23 package. The leads are finished with lead-free matte tin. The flow-through package design simplifies PCB layout.

### **Features**

- · Transient Protection to

- IEC 61000-4-2 (ESD) Level 4

- IEC 61000-4-4 (EFT) 2kV (5/50ns)

- IEC 61000-4-5 (Lightning) 20A (8/20µs)

- Bias diodes prevent charging of TVS capacitance

- Working Voltage: 24V

- Low Capacitance: 3.5pF Maximum

- Capacitance variation <1.5pF (1V to 24V)

- Solid-State Silicon-Avalanche Technology

### **Mechanical Characteristics**

- JEDEC SOT-23 6L package

- · Pb-Free, Halogen Free, RoHS/WEEE Compliant

- Lead Finish: matte Tin

- Molding Compound Flammability Rating: UL 94V-0

- Marking: Marking Code + Date Code

- Packaging: Tape and Reel

### **Applications**

- ADSLx / VDSLx Secondary Protection

- VDSL2 Class-H Line Driver Secondary Protection

- Modems

- Access Equipment

- Central Office Equipment

- Customer Premise Equipment

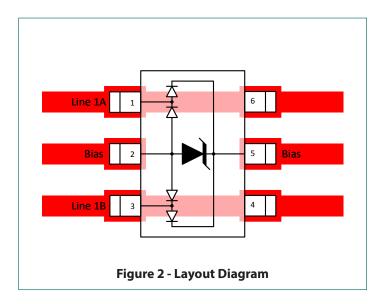

# **Circuit Diagram**

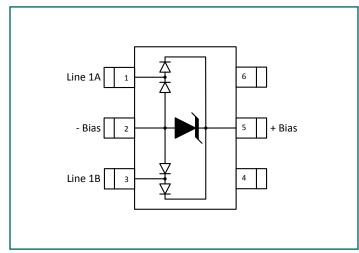

# **Pin Configuration**

# **Absolute Maximum Ratings**

| Rating                                              | Symbol           | Value       | Units |

|-----------------------------------------------------|------------------|-------------|-------|

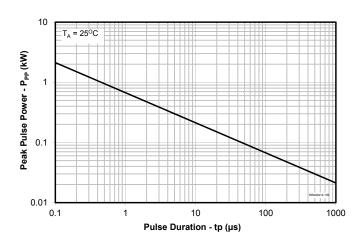

| Peak Pulse Power (tp = 1.2/50μs)                    | P <sub>PK</sub>  | 150         | W     |

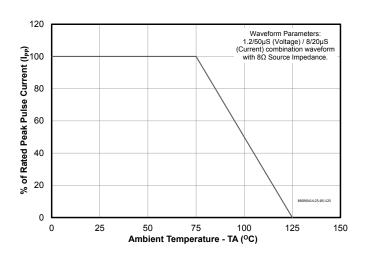

| Peak Pulse Current (tp = 1.2/50µs)                  | I <sub>PP</sub>  | 20          | A     |

| ESD per IEC 61000-4-2 (Contact) <sup>(1), (3)</sup> | V <sub>ESD</sub> | ±8          | kV    |

| Operating Temperature                               | T <sub>J</sub>   | -40 to +85  | °C    |

| Storage Temperature                                 | T <sub>STG</sub> | -55 to +150 | оС    |

# **Electrical Characteristics (T=25°C unless otherwise specified)**

| Parameter                                        | Symbol                                                                                  | Conditions                                                                             |          | Min. | Тур. | Max.  | Units |

|--------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------|------|------|-------|-------|

| Reverse Stand-Off Voltage                        | V <sub>RWM</sub>                                                                        | -40°C to 85°C<br>Pin 1 to Pin 2, Pin 3 to Pin 2, Pin 1 to Pin 3                        |          |      |      | 24    | V     |

| Reverse Breakdown Voltage                        | V <sub>BR</sub>                                                                         | I <sub>BR</sub> = 10mA, T = -40°C to 85°C<br>Pin 1 to Pin 3                            |          | 27   | 31   | 35    | V     |

| Reverse Leakage Current                          |                                                                                         | V = 24V                                                                                | T = 25°C |      | 0.01 | 0.100 | μΑ    |

|                                                  | I <sub>R</sub>                                                                          |                                                                                        | T = 85°C |      | 0.02 | 0.100 | μΑ    |

| Holding Current <sup>(3)</sup>                   | I <sub>H</sub>                                                                          |                                                                                        |          | 50   | 200  |       | mA    |

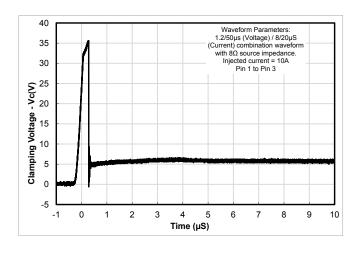

| Clarening Valtage (2) (3)                        | $I_{pp}=10$ A, $tp=1.2/50\mu s$ , $8/20\mu s$<br>Combination Waveform<br>Pin 1 to Pin 3 |                                                                                        |          | 6    |      | V     |       |

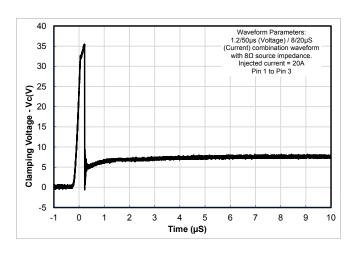

| Clamping Voltage <sup>(2), (3)</sup>             | V <sub>c</sub>                                                                          | I <sub>pp</sub> = 20A, tp = 1.2/50μs, 8/20μs<br>Combination Waveform<br>Pin 1 to Pin 3 |          |      | 7.5  |       | V     |

| Breakover Voltage(3)                             | V <sub>BO</sub>                                                                         | I <sub>BO</sub> = 50mA<br>Pin 1 to Pin 3                                               |          |      | 35   |       | V     |

| Junction Capacitance                             | C <sub>J</sub>                                                                          | $V_R = 0V$ , $f = 1MHz$<br>Pin 1 to 2 or Pin 3 to Pin 2                                | T = 25°C |      | 2    | 3.5   | pF    |

|                                                  |                                                                                         | $V_R = 0V, f = 1MHz$<br>Pin 1 to Pin 3                                                 |          |      | 1.2  | 2     | рF    |

| Variation in Junction Capacitance <sup>(3)</sup> | $\Delta C_{_{\mathrm{J}}}$                                                              | V <sub>R</sub> = 1V - 24V, f = 1MHz<br>Pin 1 to Pin 3                                  |          |      | 0.1  | 1.5   | pF    |

### Notes:

<sup>(1):</sup> ESD Gun return path to Ground Reference Plane (GRP)

<sup>(2):</sup> Measured using a 1.2/50us voltage, 8/20us current combination waveform, RS = 8 Ohms. Clamping is defined as the peak voltage across the device after the device snaps back to a conducting state.

<sup>(3):</sup> Guaranteed by design. Not production tested

# **Typical Characteristics**

### Non-Repetitive Peak Pulse Power vs. Pulse Time

### **Power Derating Curve**

### Clamping Characteristic (10A, Combination Waveform)

Clamping Characteristic (20A, Combination Waveform)

Capacitance vs. Reverse Voltage

**Capacitance vs. Temperature**

# **Typical Characteristics**

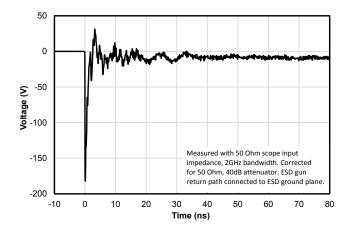

ESD Clamping (+8kV Contact per IEC 61000-4-2), Pin 1 to 3

# Measured with 50 Ohm scope input impedance, 2GHz bandwidth. Corrected for 50 Ohm, 40dB attenuator. ESD gun return path connected to ESD ground plane.

### ESD Clamping (-8kV Contact per IEC 61000-4-2), Pin 1 to 3

# **Device Operation**

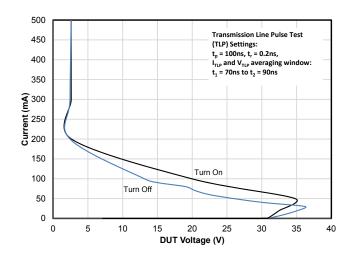

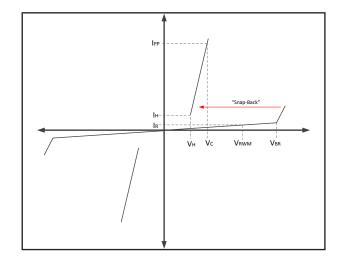

This device utilizes a multi-junction structure that is designed to switch to a low voltage state when triggered by ESD, EOS, or other transient events. During normal operation, the device will present a high-impedance to the circuit for voltage up to the working voltage ( $V_{\rm RWM}$ ) of the device. When the voltage across the device terminals exceeds the breakdown voltage ( $V_{\rm BR}$ ), avalanche breakdown occurs in the blocking junction causing the device to "snap-back" or switch to a low impedance on-state. This has the advantage of lowering the overall clamping voltage ( $V_{\rm C}$ ) as ESD peak pulse current ( $I_{\rm PP}$ ) flows through the device. Once the current decreases below the holding current ( $I_{\rm H}$ ), the device will return to a high-impedance off-state.

| Table 1 - Parameter Definition |                         |  |

|--------------------------------|-------------------------|--|

| Symbol                         | Parameter               |  |

| $V_{_{\mathrm{RWM}}}$          | Maximum Working Voltage |  |

| $V_{_{\mathrm{BR}}}$           | Breakdown Voltage       |  |

| V <sub>C</sub>                 | Clamping Voltage        |  |

| I <sub>H</sub>                 | Holding Current         |  |

| I <sub>R</sub>                 | Reverse Leakage Current |  |

| I <sub>PP</sub>                | Peak Pulse Current      |  |

### **Typical Low Current IV Characteristic**

### **Characteristic Curve**

# **Applications Information**

### **VDSL Protection Design**

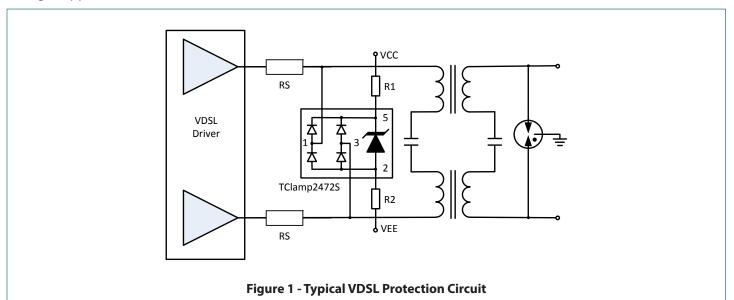

TClamp2472S is designed to protect VDSL interfaces from transient over-voltages which result from lightning and ESD. An example of how to implement the TClamp2472S for secondary (line driver side) protection is shown in Figure 1 below. When connected as shown, it will limit the differential voltage across the driver inputs during ESD and high current surge events. Pins 1 and 3 of the device are connected directly to the transmit and receive lines. Steering diodes at these pins route the surge current through the internal transient voltage suppressor (TVS). Pins 2 and 5 are connected

to the voltage supply lines via resistors R1 and R2. This connection serves to limit capacitance fluctuation of the TVS. The resistors should be large enough value as to minimize leakage current (typically 1 Meg Ohm). For single supply applications, only one resitor (R1) would be needed. Depending on immunity requirements, A primary protection device, such as a gas discharge tube (GDT), may be required to limit the voltage (and thus current) delivered to the line side of the transformer. Series resistors (RS) with a value of 1 - 2 Ohms may be needed to reduce current flow into the driver IC.

### **Device Connection and PCB Routing**

The flow-through design of TClamp2472S simplifies board layout and PCB trace routing. Figure 2 shows an example of how to connect the differential lines and bias voltages to the device. Line 1A is connected at pin1 and its trace can continue under the part and connect to pin 6, which is not connected internally to the part. A similar connection can be made for Line 1B. This layout makes it easy to keep the differential signal traces symmetrical. Bias voltage should be applied at pins 5 (positive polarity voltage) and 2 (negative polarity voltage). For single supply applications, Pin 2 can be connected to ground.

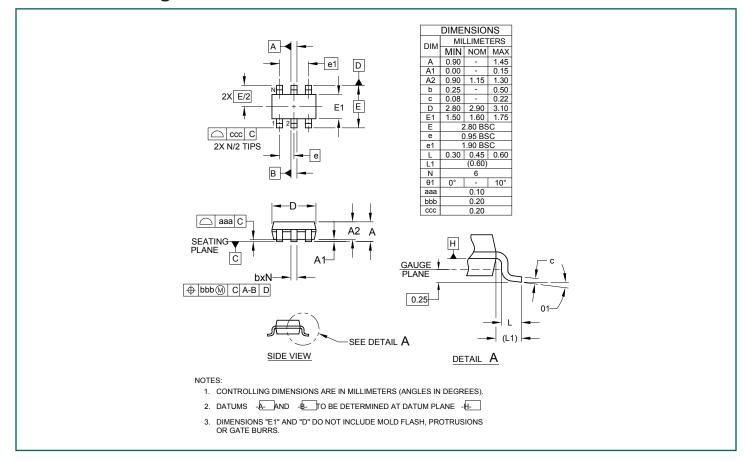

# **Outline Drawing - SOT-23 6L**

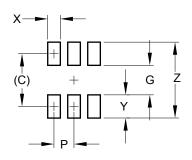

# **Land Pattern - SOT-23 6L**

| DIMENSIONS |             |  |

|------------|-------------|--|

| DIM        | MILLIMETERS |  |

| С          | (2.50)      |  |

| G          | 1.40        |  |

| Р          | 0.95        |  |

| Х          | 0.60        |  |

| Υ          | 1.10        |  |

| Ζ          | 3.60        |  |

### NOTES:

Rev 2.1

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

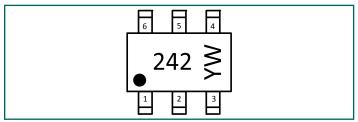

# **Marking Code**

Notes: YW = Alphanumeric character Date Code

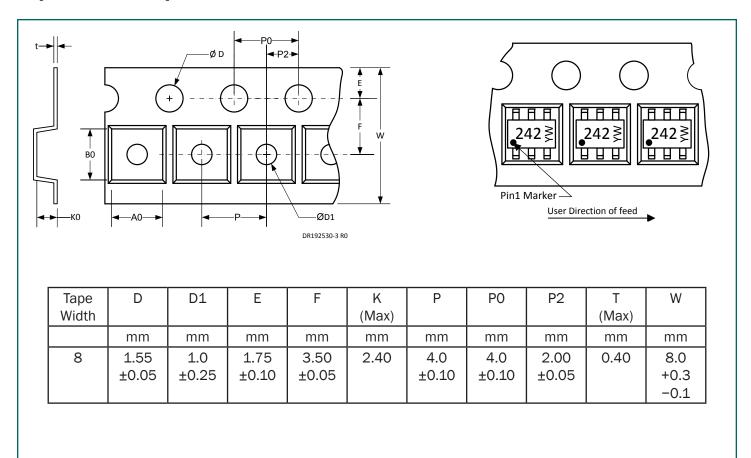

# **Tape and Reel Specification**

# **Ordering Information**

| Part Number                                                             | <b>Qty per Reel</b> | Reel Size |  |  |

|-------------------------------------------------------------------------|---------------------|-----------|--|--|

| TClamp2472S.TCT                                                         | 3000                | 7 Inch    |  |  |

| TransClamp and TClamp are registered trademarks of Semtech Corporation. |                     |           |  |  |

### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2015

### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com