# M8751H-8

Rochester Electronics<sup>®</sup>

## Single-Component 8-Bit Microcomputer

The M8751H-8 is a pin compatible EPROM version of M8051AH. Intel's advanced +5V, depletion load, N-channel, HMOS technology allows the M8751H-8 to remain fully compatible with its M8751H-8 predecessor in addition to incorporating two new features: A program memory security bit that can be used to protect the EPROM against unauthorized readout, and a programmable baud rate modification bit, which doubles the range of baud rates available to the serial port.

Specifically, the M8751H-8 features: 4K byte program memory space; 32 I/O lines; two 16-bit timer/event counters; a 5-source, 2-level interrupt structure; a full duplex serial channel; a Boolean processor; and on-chip oscillator and clock circuitry. Standard TTL and most byte-oriented MCS-80 and MCS-85 peripherals can be used for I/O and memory expansion.

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing. n 🖬 4826175 0081770 8 1

PRELIMINARY

### M8751H-8 T-49-19-59 SINGLE-COMPONENT 8-BIT MICROCOMPUTER

302

- 8 MHz Operation

- Program Memory Security

- 4K x 8 EPROM

- 🔳 128 x 8 RAM

- 32 I/O Lines (Four 8-Bit Ports)

- Two 16-Bit Timer/Counters

- Boolean Processor

- Military

- Programmable Full-Duplex Serial Channel

- 128K Accessible External Memory

- Multiply and Divide

- 256 User Bit-Addressable Locations

- Military Temperature Range: -55°C to + 125°C (T<sub>C</sub>)

The M8751H-8 is a pin compatible EPROM version of M8051AH. Intel's advanced +5V, depletion load, N-channel, HMOS\* technology allows the M8751H-8 to remain fully compatible with its M8751-8 predecessor in addition to incorporating two new features: A program memory security bit that can be used to protect the EPROM against unauthorized readout, and a programmable baud rate modification bit, which doubles the range of baud rates available to the serial port.

Specifically, the M8751H-8 features: 4K byte program memory space; 32 I/O lines; two 16-bit timer/event counters; a 5-source, 2-level interrupt structure; a full duplex serial channel; a Boolean processor; and on-chip oscillator and clock circuitry. Standard TTL and most byte-oriented MCS®-80 and MCS-85 peripherals can be used for I/O and memory expansion.

The M8751H-8 is available in a hermetically sealed, ceramic, 40-lead dual in-line package which includes a window that allows for EPROM erasure when exposed to ultraviolet light (see Erasure Characteristics). During normal operation, ambient light may adversely affect the functionality of the chip. Therefore, applications which expose the M8751H-8 to ambient light may require an opaque label over the window.

\*HMOS is a patented process of Intel Corporation.

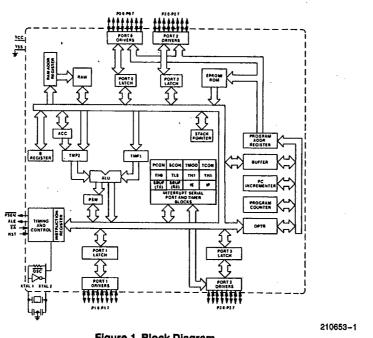

Figure 1. Block Diagram

10-15

December 1989 Order Number: 210653-004

302

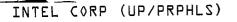

**Figure 2. Pin Configurations**

#### **M8751H PIN DESCRIPTIONS**

Vss Circuit ground potential.

Vcc Supply voltage during programming, verification, and normal operation.

#### Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. It is also the multiplexed low-order address and data bus during accesses to external memory. It also receives the instruction bytes during EPROM programming, and outputs instruction bytes during program verification. (External pullups are required during program verification.) Port 0 can sink (and in bus operations can source) eight LS TTL inputs.

#### Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pullups. It receives the low-order address byte during EPROM programming and program verification. Port 1 can sink/source four LS TTL inputs. Port 2 Port 2 is an 8-bit bidirectional I/O port with internal

pullups. It emits the high-order address byte during accesses to external memory. It also receives the high-order address bits during EPROM programming and program verification. Port 2 can sink/source four LS TTL inputs.

4826175 0081771 T

#### Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pullups. It also serves the functions of various special features of the MCS-51 Family, as listed below:

| Port Pin | Alternate Function                     |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INTO (external interrupt)              |

| P3.3     | INT1 (external interrupt)              |

| P3.4     | T0 (Timer/counter 0 external input)    |

| P3.5     | T1 (Timer/counter 1 external input)    |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

Port 3 can sink/source four LS TTL inputs.

20E D 🗰 4826175 0081772 1 1

M8751H-8

Preliminary

19-19.59

RST

intal

A high on this pin for two machine cycles while the oscillator is running resets the device. A small external pulldown resistor ( $\approx$ 8.2 K $\Omega$ ) from RST to V<sub>SS</sub> permits power-on reset when a capacitor ( $\approx$ 10  $\mu$ f) is also connected from this pin to V<sub>CC</sub>.

### ALE/PROG

Address Latch Enable output for latching the low byte of the address during accesses to external memory. ALE is activated at a constant rate of ½ the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. This pin is also the program pulse input (PROG) during EPROM programming.

### PSEN

Program Store Enable output is the read strobe to external Program Memory. PSEN is activated twice each machine cycle during fetches from external Program Memory. (However, even when executing out of external Program Memory two activations of PSEN are skipped during each access to external data memory.)

#### EA/VPP

External Access enable.  $\overline{EA}$  must be externally held low in order to enable the device to fetch code from external Program Memory locations 0000H to 0FFFH. Note, however, that if the Security Bit is programmed, the device will not fetch code from any location in external Program Memory.

This pin also receives the 21V programming supplyvoltage (V<sub>PP</sub>) during EPROM programming.

#### XTAL1

Input to the inverting oscillator amplifier.

#### XTAL2

Output from the inverting oscillator amplifier.

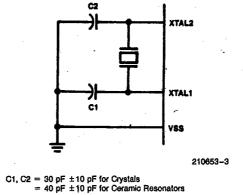

### **OSCILLATOR CHARACTERISTICS**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 3. Either a quartz crystal or ceramic resonator may be used. More detailed information concerning the use of the on-chip oscillator is available in Application Note AP-155, "Oscillators for Microcontrollers", published in the Embedded Controller Handbook.

#### Figure 3. Oscillator Connections

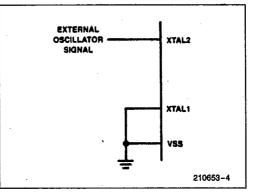

as shown in Figure 4. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the Data Sheet must be observed.

Figure 4. External Drive Configuration

| Datum      | Emitting<br>Port <del>s</del> | Degraded<br>I/O Lines | V <sub>OL</sub><br>(Peak)<br>(Max) |

|------------|-------------------------------|-----------------------|------------------------------------|

| Address    | P2, P0                        | P1, P3                | V8.0                               |

| Write Data | P0                            | P1, P3, ALE           | V8.0                               |

m

### <sup>20E</sup> D M8751H-8

**ABSOLUTE MAXIMUM RATINGS\***

| Case Temperature<br>Under Bias55°C to +125°C                                  |

|-------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                             |

| Voltage on Any Pin to V <sub>SS</sub><br>(Except V <sub>PP</sub> )0.5V to +7V |

| Voltage from V <sub>PP</sub> to V <sub>SS</sub> 21.5V                         |

| Power Dissipation2W                                                           |

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

4826175 0081773 3 🛲

PRELIMINARY

T.49-19-59

NOTICE: Specifications contained within the following tables are subject to change.

### **Operating Conditions**

| Symbol | Description                   | Min  | Max  | Units<br>°C |  |

|--------|-------------------------------|------|------|-------------|--|

| То     | Case Temperature (Instant On) | - 55 | +125 |             |  |

| Vcc    | Digital Supply Voltage        | 4.50 | 5.50 | V           |  |

### D.C. CHARACTERISTICS (Over Specified Operating Conditions)

| Symbol           | Parameter                                                       | Min  | Max                | Unit   | Comments                                               |

|------------------|-----------------------------------------------------------------|------|--------------------|--------|--------------------------------------------------------|

| VIL              | Input Low Voltage                                               | -0.5 | 0.7                | V      |                                                        |

| VIL1             | Input Low Voitage to EA                                         | 0    | 0.7                | V      |                                                        |

| V <sub>IH</sub>  | Input High Voltage (Except XTAL2, RST)                          | 2.2  | $V_{\rm CC}$ + 0.5 | v      |                                                        |

| V <sub>IH1</sub> | Input High Voltage to XTAL2, RST                                | 2.5  | $V_{CC}$ + 0.5     | V      | $XTAL1 = V_{SS}$                                       |

| VOL              | Output Low Voltage Ports 1, 2, 3 (Note 1)                       |      | 0.45               | ۷      | l <sub>OL</sub> = 1.2 mA                               |

| V <sub>OL1</sub> | Output Low Voltage Port 0, ALE, PSEN<br>(Note 1)                |      | 0.60<br>0.45       | V<br>V | $I_{OL} = 2.8 \text{ mA}$<br>$I_{OL} = 2.4 \text{ mA}$ |

| VOH              | Output High Voltage Ports 1, 2, 3                               | 2.4  |                    | V      | l <sub>OH</sub> = −60 μA                               |

| V <sub>OH1</sub> | Output High Voltage Port 0 (in External<br>Bus Mode), ALE, PSEN | 2.4  |                    | V      | l <sub>OH</sub> = −300 μA                              |

| Ι <u>Ι</u> .     | Logical 0 Input Current P1, P2, P3                              |      | -500               | μA     | V <sub>IN</sub> = 0.45V                                |

| IIL1             | Logical 0 Input Current to EA/VPP                               |      | -15                | mA     | V <sub>IN</sub> = 0.45V                                |

| I <sub>IL2</sub> | Logical 0 Input Current to XTAL2                                |      | -4.5               | mA     | $XTAL1 = V_{SS}, V_{IN} = 0.45V$                       |

| l <sub>Li</sub>  | Input Leakage Current to Port 0                                 |      | ±125               | μΑ     | $0.45V < V_{IN} < V_{CC}$                              |

| Iн               | Logical Input Current to EA/VPP                                 |      | 500                | μA     | $V_{IN} = 2.4V$                                        |

| liH1             | Input Current to RST/VPD to Activate Reset                      |      | 500                | μA     | V <sub>IN</sub> < (V <sub>CC</sub> - 1.5V)             |

| lcc              | Power Supply Current                                            |      | 275                | mA     | All Outputs Disconnected, $\overline{EA} = V_{CC}$     |

| CIO              | Capacitance of I/O Buffers                                      |      | 10 ´               | рF     | f <sub>c</sub> = 1 MHz, T <sub>A</sub> = 25°C          |

#### NOTES:

1. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE line may exceed 0.8V. In such cases it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

intel

20E D = 4826175 0081774 5 = PRELIMINARY

M8751H-8

T.99.19.59

A.C. CHARACTERISTICS (Over Specified Operating Conditions), Load Capacitance for Port 0, ALE, T and  $\overline{PSEN} = 100 \text{ pF}$ ; Load Capacitance for all other outputs = 80 pF

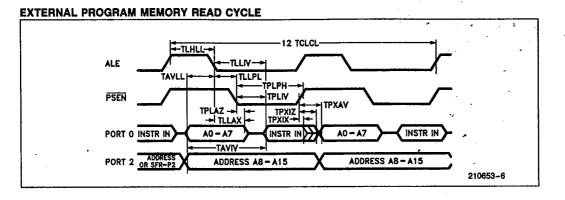

**EXTERNAL PROGRAM MEMORY CHARACTERISTICS**

| Symbol  | Parameter                        | 8 MHz Osc |     | Variable  | Units      |      |

|---------|----------------------------------|-----------|-----|-----------|------------|------|

|         | raiailietei                      | Min       | Max | Min       | Max        |      |

| 1/TCLCL | Oscillator Frequency             |           | -   | 3.5       | 8          | MHz  |

| TLHLL   | ALE Pulse Width                  | 195       |     | 2TCLCL-55 |            | ns   |

| TAVLL   | Address Valid to ALE             | 70        |     | TCLCL-55  | ~          | ns   |

| TLLAX   | Address Hold after ALE           | 75        |     | TCLCL-50  | ı,         | ns   |

| TLLIV   | ALE to Valid Instr In            |           | 335 |           | 4TCLCL-165 | ns   |

| TLLPL   | ALE to PSEN                      | 85        | ÷   | TCLCL-40  |            | ns   |

| TPLPH   | PSEN Pulse Width                 | 300       |     | 3TCLCL-75 |            | ns   |

| TPLIV   | PSEN to Valid Instr In           |           | 210 |           | 3TCLCL-165 | ns   |

| TPXIX   | Input Instr Hold after PSEN      | 0         |     | 0         |            | ns   |

| TPXIZ   | Input Instr Float after PSEN     |           | 90  |           | TCLCL-35   | ns   |

| TPXAV   | PSEN to Address Valid            | 100       |     | TCLCL-25  |            | ns   |

| TAVIV   | Address to Valid Instr In        |           | 460 |           | 5TCLCL-165 | , ns |

| TPLAZ   | <b>PSEN</b> Low to Address Float |           | 20  |           | 20         | ns   |

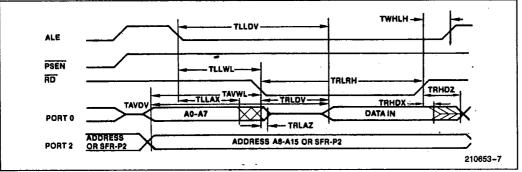

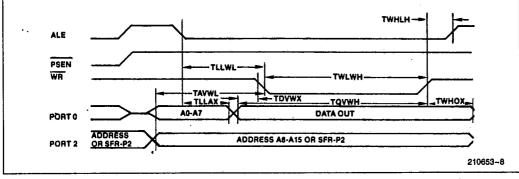

### **EXTERNAL DATA MEMORY CHARACTERISTICS**

| Symbol  | Parameter                   | 8 MH | z Osc | Variable   | Units      |       |

|---------|-----------------------------|------|-------|------------|------------|-------|

| oynibol |                             | Min  | Max   | Min        | Max        | Unita |

| TRLRH   | RD Pulse Width              | 650  |       | 6TCLCL-100 |            | ns    |

| TWLWH   | WR Pulse Width              | 650  |       | 6TCLCL-100 |            | ns    |

| TLLAX   | Address Hold after ALE      | 75   |       | TCLCL-50   |            | ns    |

| TRLDV   | RD to Valid Data In         |      | 440   |            | 5TCLCL-185 | ns    |

| TRHDX   | Data Hold after RD          | 0    |       | 0          |            | ns    |

| TRHDZ   | Data Float after RD         |      | 165   |            | 2TCLCL-85  | ns    |

| TLLDV   | ALE to Valid Data In        |      | 830   |            | 8TCLCL-170 | ns    |

| TAVDV   | Address to Valid Data In    |      | 940   |            | 9TCLCL-185 | ns    |

| TLLWL   | ALE to WR or RD             | 310  | 440   | 3TCLCL-65  | 3TCLCL+65  | ns    |

| TAVWL   | Address to WR or RD         | 355  |       | 4TCLCL-145 |            | ns    |

| TQVWX   | Data Valid to WR Transition | 40   |       | TCLCL-85   |            | ns    |

| TQVWH   | Data Setup to WR High       | 800  |       | 7TCLCL-75  |            | ns    |

| TWHQX   | Data Held after WR          | 60   |       | TCLCL-65   |            | ns    |

| TRLAZ   | RD Low to Address Float     |      | 20    |            | 20         | ns    |

| TWHLH   | RD or WR High to ALE High   | 60   | 190   | TCLCL-65   | TCLCL+65   | ns    |

me

4826175 0081775 7 🔳 -PRELIMINARY

<sup>-,</sup>49.19.59

M8751H-8

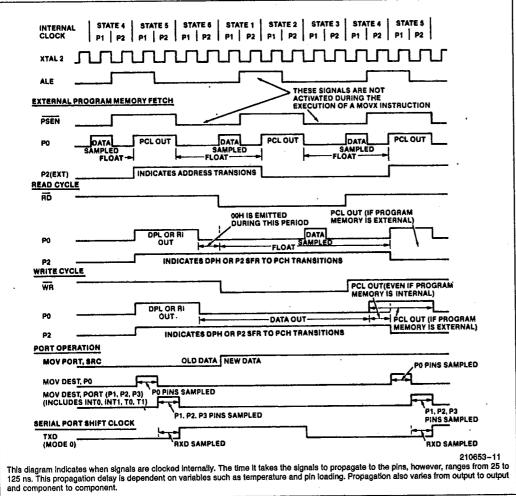

### A.C. TIMING DIAGRAMS

### EXTERNAL DATA MEMORY READ CYCLE

### EXTERNAL DATA MEMORY WRITE CYCLE

intel

) <u>sõe</u> **D**

M8751H-8

■ 4826175 0081776 9 ■ PRELIMINARY

T.49-19.59

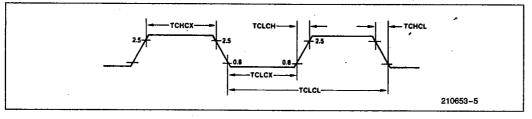

### **EXTERNAL CLOCK DRIVE CHARACTERISTICS (XTAL2)**

| Symbol  | Parameter                   | Min                             | Max   | Units |  |

|---------|-----------------------------|---------------------------------|-------|-------|--|

| 1/TCLCL | CL Oscillator Frequency 3.5 |                                 | 8     | MHz   |  |

| TCHCX   | High Time                   | 20                              |       | ns    |  |

| TCLCX   | Low Time                    | 20                              | · · · | ns    |  |

| TCLCH   | Rise Time                   |                                 | 20    | ns    |  |

| TCHCL   | Fall Time                   | · · · · · · · · · · · · · · · · | 20    | ns    |  |

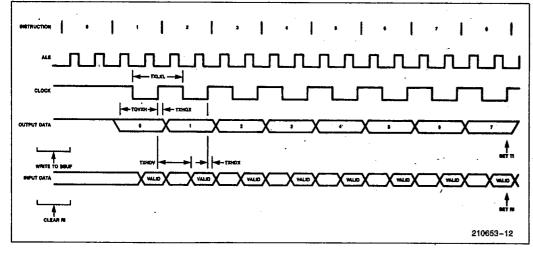

### SERIAL PORT TIMING-SHIFT REGISTER MODE Load Capacitance = 80 pF

| Symbol | Parameter                                | 8 MHz Osc |      | Variable    | Units       |        |

|--------|------------------------------------------|-----------|------|-------------|-------------|--------|

|        |                                          | Min       | Max  | Min         | Max         | Quinta |

| TXLXL  | Serial Port Clock Cycle Time             | 1.0       | · ·  | 12TCLCL     |             | μs     |

| TQVXH  | Output Data Setup to Clock Rising Edge   | 1117      |      | 10TCLCL-133 |             | ns     |

| TXHQX  | Output Data Hold after Clock Rising Edge | 133       |      | 2TCLCL-117  |             | ns     |

| TXHDX  | Input Data Hold after Clock Rising Edge  | 0         |      | 0           |             | ns     |

| TXHDV  | Clock Rising Edge to Input Data Valid    |           | 1117 |             | 10TCLCL-133 | ns     |

### SHIFT REGISTER TIMING WAVEFORMS

intel

## 20E D 💻

M8751H-8

4826175 0081777 0 ■ **PRELIMINARY**

49-19.59

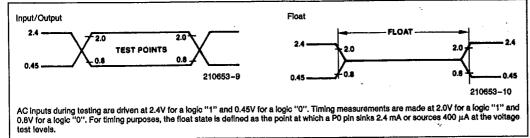

### A.C. TESTING INPUT/OUTPUT, FLOAT WAVEFORMS

### **CLOCK WAVEFORMS**

4826175 0081778 2 🖬 ´ PRELIMINARY

T·49-19.59

### EPROM CHARACTERISTICS

| Mode         | RST | PSEN | ALE | ĒĀ              | P2.7 | P2.6 | P2.5 | P2.4  |

|--------------|-----|------|-----|-----------------|------|------|------|-------|

| Program      | 1   | 0    | 0*  | VPP             | 1    | 0 :  | · X. | • ° X |

| Inhibit      | 1   | 0    | 1   | Х               | 1    | 0    | X    | Х     |

| Verify       | 1   | 0    | 1   | 1               | 0    | 0    | X    | X     |

| Security Set | 1   | 0    | 0*  | V <sub>PP</sub> | 1    | 1    | X    | x     |

NOTES:

"1" = logic high for that pin

"0" = logic low for that pin "X" = "don't care"

"Vpp" =  $+21V \pm 0.5V$

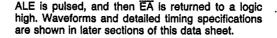

\*ALE is pulsed low for 50 ms.

### **Programming the EPROM**

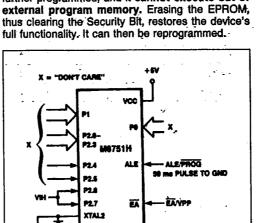

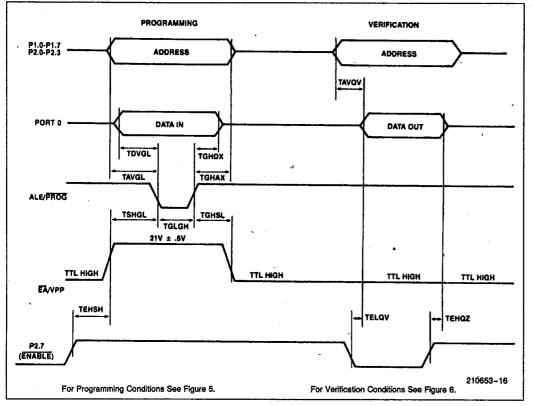

To be programmed, the part must be running with a 4 to 6 MHz oscillator. (The reason the oscillator needs to be running is that the internal bus is being used to transfer address and program data to appropriate internal registers.) The address of an EPROM location to be programmed is applied to Port 1 and pins P2.0–P2.3 of Port 2, while the code byte to be programmed into that location is applied to Port 0. The other Port 2 pins, and RST, PSEN, and EA should be held at the "Program" levels indicated in Table 1. ALE is pulsed low for 50 ms to program the code byte into the addressed EPROM location. The setup is shown in Figure 5.

Normally  $\overline{EA}$  is held at a logic high until just before ALE is to be pulsed. Then  $\overline{EA}$  is raised to +21V,

Note that the  $\overline{EA}/V_{PP}$  pin must not be allowed to go above the maximum specified V<sub>PP</sub> level of 21.5V for any amount of time. Even a narrow glitch above that voltage level can cause permanent damage to the device. The V<sub>PP</sub> source should be well regulated and free of glitches.

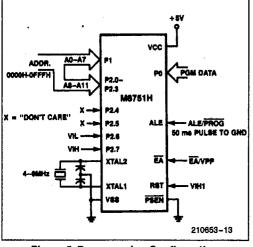

### **Program Verification**

If the Security Bit has not been programmed, the onchip Program Memory can be read out for verification purposes, if desired, either during or after the

Figure 5. Programming Configuration

Figure 6. Program Verification

20E D 4826175 0081779 4 M

M8751H-8

programming operation. The address of the Program Memory location to be read is applied to Port 1 and pins P2.0–P2.3. The other pins should be held at the "Verify" levels indicated in Table 1. The contents of the addressed location will come out on Port 0. External pullups are required on Port 0 for this operation.

The setup, which is shown in Figure 6, is the same as for programming the EPROM except that pin P2.7 is held at a logic low, or may be used as an active-low read strobe.

### **EPROM Security**

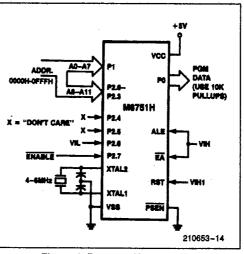

The security feature consists of a "locking" bit which when programmed denies electrical access by any external means to the on-chip Program Memory. The bit is programmed as shown in Figure 7. The setup and procedure are the same as for normal EPROM programming, except that P2.6 is held at a logic high. Port 0, Port 1, and pins P2.0–P2.3 may be in any state. The other pins should be held at the "Security" levels indicated in Table 1.

Once the Security Bit has been programmed, it can be cleared only by full erasure of the Program Mem-

ory. While it is programmed, the internal Program Memory cannot be read out, the device cannot be

further programmed, and it cannot execute out of

**1**9 · 19 · 59

Figure 7. Programming the Security Bit

### EPROM PROGRAMMING AND VERIFICATION CHARACTERISTICS

$T_A = 25^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V$

| Symbol  | Parameter                  | Min     | Max     | Units |

|---------|----------------------------|---------|---------|-------|

| Vpp     | Programming Supply Voltage | 20.5    | 21.5    | V     |

| lpp     | Programming Supply Current |         | 30      | mA    |

| 1/TCLCL | Oscillator Frequency       | 4       | 6       | MHz   |

| ·TAVGL  | Address Setup to PROG Low  | 48TCLCL |         |       |

| TGHAX   | Address Hold after PROG    | 48TCLCL |         |       |

| TDVGL   | Data Setup to PROG Low     | 48TCLCL |         |       |

| TGHDX   | Data Hold after PROG       | 48TCLCL |         |       |

| TEHSH   | P2.7 (ENABLE) High to VPP  | 48TCLCL |         |       |

| TSHGL   | VPP Setup to PROG Low      | 10      |         | μs    |

| TGHSL   | VPP Hold after PROG        | 10      |         | μs    |

| TGLGH   | PROG Width                 | 45      | 55      | ms    |

| TAVQV   | Address to Data Valid      |         | 48TCLCL |       |

| TELQV   | ENABLE Low to Data Valid   |         | 48TCLCL |       |

| TEHQZ   | Data Float after ENABLE    | 0       | 48TCLCL |       |

int

M8751H-8

30S

### **Erasure Characteristics**

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelengths shorter than approximately 4,000 Angstroms. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window. The recommended erasure procedure is exposure to ultraviolet light (at 2537 Angstroms) to an integrated dose of at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 20 to 30 minutes, at a distance of about 1 inch, should be sufficient.

4826175 0081780 0 📟

PRELIMINARY

49-*19-5*9

Erasure leaves the array in an all 1s state.

### EPROM PROGRAMMING AND VERIFICATION WAVEFORMS

me

20E D 🖬 4826122 0081281 2 🖬 / PRELIMINARY

### M8751H-8

# T :49-19-59

| ARITHMETIC OPE    | RATIONS                          |      | · 1                                          | LOGICAL OPERA      | TIONS (Continued)                       |                |     |

|-------------------|----------------------------------|------|----------------------------------------------|--------------------|-----------------------------------------|----------------|-----|

| Mnemonic          | Description                      | Byte | Cve                                          | Mnemonic ·         | Description                             | Byte           | Cy  |

| ADD A,Rn          | Add register to                  | byto | <b>,</b> ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ORL A,@RÌ          | OR indirect RAM to                      | -,             | -,  |

|                   | Accumulator                      | 1    | 1                                            | Onengon            | Accumulator                             | 1              | 1   |

|                   | Add direct byte to               | •    | '                                            | ORL A, #data       | OR immediate data to                    | •              | •   |

| ADD A, direct     | •                                | 2    | 1                                            | One A, * data      | Accumulator                             | 2              | -1  |

|                   | Accumulator                      | 2    |                                              | ORL direct,A       | OR Accumulator to                       |                | •   |

| ADD A,@RI         | Add indirect RAM to              | 1    | 1                                            | UNE UIIOULA        | direct byte                             | <sup>.</sup> 2 | 1   |

|                   | Accumulator                      | 1    | '                                            | OBI direct #date   |                                         | <u> </u>       |     |

| ADD A, #data      | Add immediate data to            | ~    | 1                                            | ORL direct, #data  |                                         | 3              | 2   |

|                   | Accumulator                      | 2    | 1                                            |                    | direct byte<br>Exclusive-OR register to |                | 2   |

| ADDC A,Rn         | Add register to                  |      |                                              | XRL A,Rn           | Accumulator                             | ſ              | 1   |

|                   | Accumulator with Carry           | 1    | 1                                            |                    |                                         |                | 1   |

| ADDC A, direct    | Add direct byte to A             | •    |                                              | XRL A, direct      | Exclusive-OR direct                     | ~              |     |

|                   | with Carry flag                  | 2    | 1                                            |                    | byte to Accumulator                     | 2              | • 1 |

| ADDC A,@Ri        | Add indirect RAM to A            |      | •                                            | XRL A,@Ri          | Exclusive-OR indirect                   |                |     |

|                   | with Carry flag                  | 1    | <b>1</b>                                     |                    | RAM to A                                | 1              | 1   |

| ADDC A, #data     | Add immediate data to            |      |                                              | XRL A, #data       | Exclusive-OR                            | _              |     |

|                   | A with Carry flag                | 2    | 1                                            |                    | immediate data to A                     | 2 .            | 1   |

| SUBB A,Rn         | Subtract register from A         |      |                                              | XRL direct,A       | Exclusive-OR Accumu-                    |                |     |

|                   | with Borrow                      | 1    | 1                                            |                    | lator to direct byte                    | 2              | 1   |

| SUBB A, direct    | Subtract direct byte             |      |                                              | XRL direct, # data | Exclusive-OR im-                        |                |     |

| •                 | from A with Borrow               | 2    | 1                                            |                    | mediate data to direct                  | 3              | 2   |

| SUBB A,@Ri        | Subtract Indirect RAM            |      |                                              | CLR A              | Clear Accumulator                       | 1              | 1   |

| · · · · ·         | from A with Borrow               | 1    | 1                                            | CPLA               | Complement                              |                |     |

| SUBB A, #data     | Subtract immed data              |      |                                              |                    | Accumulator                             | 1              | 1   |

|                   | from A with Borrow               | 2    | 1                                            | RLA                | Rotate Accumulator Left                 | ή              | 1   |

| INC A             | Increment Accumulator            | 1    | 1                                            | RLC A              | Rotate A Left through                   |                |     |

| INC Rn            | Increment register               | 1    | i                                            |                    | the Carry flag                          | 1              | 1   |

| INC direct        | Increment direct byte            | 2    | i                                            | RR A               | Rotate Accumulator                      | -              |     |

| INC @Ri           | Increment Indirect RAM           | 1    | i                                            | 1                  | Right                                   | 1              | 1   |

| INC OPTR          | increment Data Pointer           | i    | 2                                            | RRC A              | Rotate A Right through                  | •              | •   |

|                   | Decrement Accumulator            | 1    | 1                                            | 1                  | Carry flag                              | 1              | 1   |

| DEC A             |                                  | 1    | 1                                            | SWAP A             | Swap nibbles within the                 | •              | •   |

| DEC Rn            | Decrement register               | 2    | 1                                            | SWAFA              | Accumulator                             | 1              | 1   |

| DEC direct        | Decrement direct byte            | 2    |                                              | DATA TRANSFE       |                                         | •              |     |

| DEC @Ri           | Decrement indirect               |      |                                              |                    |                                         | Bide           | ~   |

|                   | RAM                              | 1    | 1                                            | Mnemonic           | Description                             | Byte           | Cy  |

| MUL AB            | Multiply A & B                   | 1    | 4                                            | - MOV A,Rn         | Move register to                        |                |     |

| DIV AB            | Divide A by B                    | 1    | 4                                            |                    | Accumulator                             | 1              | 1   |

| DAÁ               | Decimal Adjust                   |      |                                              | MOV A, direct      | Move direct byte to                     | -              |     |

| •                 | Accumulator                      | 1    | 1                                            |                    | Accumulator                             | 2              | 1   |

| LOGICAL OPERA     |                                  |      |                                              | MOV A,@Ri          | Move indirect RAM to                    |                |     |

| Mnemonic          | Destination                      | Byte | Cyc                                          |                    | Accumulator                             | 1              | 1   |

| ANL A,Rn          | AND register to                  |      |                                              | MOV A, #data       | Move immediate data                     |                |     |

|                   | Accumulator                      | 1    | 1                                            |                    | to Accumulator                          | 2              | 1   |

| ANL A, direct     | AND direct byte to               |      |                                              | MOV Rn,A           | Move Accumulator to                     |                |     |

|                   | Accumulator                      | 2    | 1                                            |                    | register                                | 1              | 1   |

| ANL A,@RI         | AND indirect RAM to              |      |                                              | MOV Rn, direct     | Move direct byte to                     |                |     |

|                   | Accumulator                      | • 1  | 1                                            |                    | register                                | 2              | 2   |

| ANL A, #data      | AND immediate data to            |      |                                              | MOV Rn, #data      | Move immediate data to                  |                |     |

|                   | Accumulator                      | 2    | 1                                            |                    | register                                | 2              | 1   |

| ANL direct,A      | AND Accumulator to               | -    |                                              | MOV direct,A       | Move Accumulator to                     |                |     |

|                   | direct byte                      | 2    | 1                                            |                    | direct byte                             | 2              | 1   |

| ANL direct, #data | •                                | 5    | •                                            | MOV direct,Rn      | Move register to direct                 | -              |     |

| ANL URBUL # UBLE  |                                  | 3    | 2                                            |                    | byte                                    | 2              | :   |

|                   | direct byte                      | 3    | 2                                            | MOV direct direct  |                                         | ~              | •   |

| ORL A,Rn          | OR register to                   | 4    | 4                                            | MOV direct, direct | direct                                  | 3              | . 2 |

|                   | Accumulator                      | 1    | 1                                            | MOV direct @Di     | Move indirect RAM to                    | 0              | 4   |

| ORL A, direct     | OR direct byte to<br>Accumulator | 2    | 1                                            | MOV direct,@Ri     | direct byte                             | 2              |     |

|                   |                                  |      |                                              |                    |                                         |                |     |

me

20E D 🔲 4826175 0081782 4 Boog Invinve

M8751H-8

Preliminary T · 19 - 19 - 59

|                        | Table 1. MCS®-5          | 1 Insi  | truct | lon   | Set Description (C   | T·49<br>ontinued)                                        | -19        | 7-5   |

|------------------------|--------------------------|---------|-------|-------|----------------------|----------------------------------------------------------|------------|-------|

| DATA TRANSFER (        |                          | · · · · |       | ]     | PROGRAM AND MA       |                                                          |            |       |

| Mnemonic               | Description              | Byte    | Cvc   |       | Mnemonic             | Description                                              | Byte       | Cve   |

| MOV direct, # data     | Move immediate data to   | -,      | -,-   |       | ACALL addr11         | Absolute Subroutine                                      | 0,10       | 0,0   |

|                        | direct byte              | 3       | 2     |       |                      | Call                                                     | 2          | 2     |

| MOV @RI,A              | Move Accumulator to      | •       | -     | ŀ     | LCALL addr16         | Long Subroutine Call                                     | 3          | 2     |

|                        | Indirect RAM             | 1       | 1     |       | RET                  | Return from subroutine                                   | 1          | 2     |

| MOV @Ri,direct         | Move direct byte to      | •       | •     |       | RETI                 | Return from interrupt                                    | 1          | 2     |

|                        | indirect RAM             | 2       | 2     |       | AJMP addr11          | Absoute Jump                                             | 2          | 2     |

| MOV @Ri,#data          | Move immediate data to   | _       | -     |       | LJMP addr16          | Long Jump                                                | 3          | 2     |

|                        | indirect RAM             | 2.      | 1     | 1     | SJMP rel             | Short Jump (relative                                     |            |       |

| MOV DPTR, #data16      | Load Data Pointer with   |         |       |       |                      | addr)                                                    | 2          | 2     |

|                        | a 16-bit constant        | 3       | 2     |       | JMP @A+DPTR          | Jump indirect relative to                                |            |       |

| MOVC A,@A+DPTR         | Move Code byte relative  |         |       |       |                      | the DPTR                                                 | 11         | 2     |

|                        | to DPTR to A             | 1       | 2     |       | JZ rel               | Jump if Accumulator is                                   |            |       |

| MOVC A,@A+PC           | Move Code byte relative  |         |       |       | 1                    | Zero                                                     | 2          | 2     |

|                        | to PC to A               | 1       | 2     |       | JNZ rel              | Jump if Accumulator is                                   |            |       |

| MOVX A,@Ri             | Move External RAM (8-    |         |       |       |                      | Not Zero                                                 | 2          | 2     |

|                        | bit addr) to A           | 1       | 2     |       | JC rel               | Jump if Carry flag is set                                | 2          | 2     |

| MOVX A,@DPTR           | Move External RAM (16-   |         |       |       | JNC rel              | Jump if No Carry flag                                    | 2          | 2     |

|                        | bit addr) to A           | 1       | 2     |       | JB bit,rel           | Jump if direct Bit set                                   | 3          | 2-    |

| MOVX @Ri,A             | Move A to External RAM   |         |       |       | JNB bit,rel          | Jump if direct Bit Not                                   | ~          | •     |

|                        | (8-bit addr)             | 1       | 2     |       | JBC bit,rel          | set<br>Iumn if direct Dit is not                         | 3          | 2     |

| MOVX @DPTR,A           | Move A to External RAM   |         |       |       | and pit'tel          | Jump if direct Bit is set<br>& Clear bit                 | •          | ~     |

|                        | (16-bit addr)            | 1       | 2     |       | CJNE A, direct, rel  | Compare direct to A &                                    | 3          | 2     |

| PUSH direct            | Push direct byte onto    |         |       |       |                      | Jump if Not Equal                                        | 3          | 2     |

|                        | stack                    | 2       | 2     |       | CJNE A, #data,rel    | Comp, immed, to A &                                      | 3          | 2     |

| POP direct             | Pop direct byte from     |         |       |       | Conte Ma Catalion    | Jump if Not Equal                                        | 3          | 2     |

|                        | stack                    | 2       | 2     |       | CJNE Rn, #data,rel   | Comp, immed, to reg &                                    | U          | 4     |

| XCH A,Rn               | Exchange register with   |         |       |       |                      | Jump if Not Equal                                        | 3          | 2     |

|                        | Accumulator              | 1       | 1     |       | CJNE @Ri. # data.rel | Comp, immed, to ind, &                                   | Ū          | -     |

| XCH A, direct          | Exchange direct byte     |         |       |       |                      | Jump if Not Equal                                        | 3          | 2     |

|                        | with Accumulator         | 2       | 1     |       | DJNZ Rn,rel          | Decrement register &                                     |            | -     |

| XCH A,@Ri              | Exchange indirect RAM    |         |       |       |                      | Jump if Not Zero                                         | 2          | 2     |

|                        | with A                   | 1       | 1     |       | DJNZ direct, rel     | Decrement direct &                                       |            |       |

| XCHD A,@Ri             | Exchange low-order       |         |       |       |                      | Jump if Not Zero                                         | 3          | 2     |

|                        | Digit ind RAM w A        | 1       | 1     |       | NOP                  | No operation                                             | 1          | 1     |

|                        |                          |         |       |       |                      | DDRESSING MODES                                          |            |       |

| <b>BOOLEAN VARIABL</b> | E MANIPULATION           |         |       |       |                      | ing register R0-R7                                       |            |       |

| Mnemonic               | Description              | Byte    | Cyc   |       | direct — 128 ir      | nternal RAM locations, any                               | 1/O pc     | ort,  |

| CLR C                  | Clear Carry Flag         | 1       | 1     |       |                      | ol or status register                                    |            |       |

| CLR bit                | Clear direct bit         | 2       | 1     |       |                      | ct Internal RAM location a                               | ddress     | ed    |

| SETB C                 | Set Carry flag           | 1       | 1     |       |                      | gister R0 or R1                                          |            |       |

| SETB bit               | Set direct bit           | 2       | 1     | i     |                      | constant included in instruc                             |            |       |

| CPL C                  | Complement Carry         | •       |       |       |                      | constant included as byte                                | s 2 & 3    | 5 of  |

|                        | flag                     | 1       | 1     |       | bit — 128 s          |                                                          |            |       |

| CPL bit                | Complement direct bit    | 2       | 1     |       | 1                    | oftware flags, any I/O pin,                              | contro     | lot   |

| ANL C,bit              | AND direct bit to Carry  |         |       |       | NOTES ON PROCE       | s Dit<br>AM ADDRESSING MODE                              | -          |       |

|                        | flag                     | 2       | 2     |       |                      |                                                          |            |       |

| ANL C,/bit             | AND complement of        |         |       |       |                      | nation address for LCALL a<br>be anywhere within the 64- |            |       |

|                        | direct bit to Carry      | 2       | 2     |       |                      | ory address space                                        | r prog     | ram   |

| ORL C/bit              | OR direct bit to Carry   |         |       |       | addr11 — Desti       | nation address for ACALL                                 | 2. A 13.41 | 0     |

| 001 0 // //            | flag                     | 2       | 2     |       |                      | e within the same 2-K page                               |            | r'    |

| ORL C,/bit             | OR complement of         |         |       |       |                      | am memory as the first by                                |            | A     |

|                        | direct bit to Carry      | 2       | 2     |       |                      | ving instruction                                         | e or up    | -     |

| MOV C,/bit             | Move direct bit to Carry |         |       |       |                      | and all conditional jumps                                | include    | an    |

|                        | flag                     | 2       | 1     |       | 8-bit                | offset byte, Range is + 12                               | 7-128      | - 411 |

| MOV bit,C              | Move Carry flag to       |         |       |       | bytes                | relative to first byte of the                            | followi    | na    |

|                        | direct bit               | 2       | 2     |       | instru               | ction                                                    |            |       |

|                        |                          |         |       |       |                      | ighted Corporation                                       | 1979       |       |

| ·····                  |                          |         |       | 10-27 |                      |                                                          |            |       |

intel

M8751H-8

20E D 4826175 0081783 6 M8751H-8 PRELIMINARY

T.49-19-59

|                 |                    | Table    | 2. Instruction Opco | aes in nexi | adecimal U         | ruer     |                   |

|-----------------|--------------------|----------|---------------------|-------------|--------------------|----------|-------------------|

| Hex<br>Code     | Number<br>of Bytes | Mnemonic | Operands            | Hex<br>Code | Number<br>of Bytes | Mnemonic | Operands          |

| 0               | 1                  | NOP      |                     | 33          | 1                  | RLC `    | A                 |

| 1               | 2                  | AJMP     | code addr           | 34          | 2                  | ADDC     | A,#data           |

| )2              | 3                  | LIMP     | code addr           | 35          | 2                  | ADDC     | A,data addr       |

| )3              | 1                  | RR       | A                   | 36          | 1                  | ADDC     | A,@R0             |

|                 | 1                  | INC      | Â                   | 37          | 1                  | ADDC     | A,@R1             |

| 04              |                    | INC      | data addr           | 38          | 1                  | ADDC     | A,R0              |

| 05              | 2                  |          | @R0                 | 39          | 1 1                | ADDC     | A,R1              |

| 06              | 1                  | INC      |                     | 38<br>3A    | 1                  |          | 4 00              |

| 07              | 1                  | INC      | @R1                 |             | 1                  | ADDC     | A,R2              |

| 08              | 1                  | INC      | RO                  | 3B          | 1                  | ADDC     | A,R4              |

| 09              | 1                  | INC      | R1                  | 30          |                    |          | A,R5              |

| 0A              | 1                  | INC      | R2                  | 3D          | 1                  | ADDC     |                   |

| 0B              | 1                  | INC      | R3                  | ЗE          | 1                  |          | < A,R6            |

| 0C              | 1                  | INC      | R4                  | 3F          | 1                  | ADDC     | A,R7              |

| 0D              | 1                  | INC      | R5                  | 40          | 2                  | JC       | code addr         |

| 0E              | 1                  | INC      | R6                  | 41          | 2                  | AJMP     | code addr         |

| 0F              | 1                  | INC      | R7                  | 42          | 2                  | ORL      | data addr,A       |

| 10              | 3                  | JBC      | bit addr.code addr  | 43          | 3                  | ORL      | data addr, # data |

| 11              | 2                  | ACALL    | code addr           | 44          | 2                  | ORL      | A,#data           |

|                 | 3                  | LCALL    | code addr           | 45          | 2                  | ORL      | A,data addr       |

| 12              |                    | RRC      | A                   | 46          | 1                  | ORL      | A,@R0             |

| 13              | 1                  |          | Â                   | 47          | 1                  | ORL      | A,@R1             |

| 14              | 1                  | DEC      |                     | 48          | 1                  | ORL      | A,R0              |

| 15              | 2                  | DEC      | data addr           | 40          | 1                  | ORL      | A,R1              |

| 16              | 1                  | DEC      | @R0                 | 1           | 1                  | ORL      | A,R2              |

| 17              | 1                  | DEC      | @R1                 | 4A          | -                  |          | •                 |

| 18              | 1                  | DEC .    | R0 .                | 48          | 1                  | ORL      | A,R3              |

| 19              | 1                  | DEC      | R1                  | 4C          | 1                  | ORL      | A,R4              |

| 1A <sup>`</sup> | 1                  | DEC      | R2                  | 4D          | 1                  | ORL      | A,R5              |

| 1B              | 1                  | DEC      | R3                  | 4E          | 1                  | ORL      | A,R6              |

| 10              | 1                  | DEC      | R4                  | 4F          | 1                  | ORL      | A,R7              |

| 1D              | 1                  | DEC      | R5                  | 50          | 2                  | JNC      | code addr         |

| 1E              | i                  | DEC      | R6                  | 51          | 2                  | ACALL    | code addr         |

| 1F              | 1                  | DEC      | B7                  | 52          | 2                  | ANL ·    | data addr,A       |

| 20              | 3                  | JB       | bit addr.code addr  | 53          | 3                  | ANL      | data addr, # dat  |

|                 | 2                  | AJMP     | code addr           | 54          | 2                  | ANL      | A.#data           |

| 21              |                    | RET      | COUB addr           | 55          | 2                  | ANL      | A,data addr       |

| 22              | 1                  |          |                     | 56          | ĩ                  | ANL      | A,@R0             |

| 23              | 1                  | RL       | A                   | 50          | 1                  | ANL      | A,@R1             |

| 24              | 2                  | ADD      | A,#data             |             | 1                  | ANL      | A,R0              |

| 25              | 2                  | ADD      | A,data addr         | 58          | 1                  |          |                   |

| 26              | 1                  | ADD      | A,@R0               | 59          | -                  | ANL      | A,R1              |

| 27              | 1                  | ADD      | A,@R1               | 5A          | 1                  | ANL      | A,R2              |

| 28              | 1                  | ADD      | A,R0                | 5B          | 1                  | ANL      | A,R3              |

| 29              | 1                  | ADD      | A,R1                | 5C          | 1                  | ANL      | A,R4              |

| 2Å              | 1                  | ADD      | A,R2                | 5D          | 1                  | ANL      | A,R5              |

| 2B              | 1                  | ADD      | A,R3                | 5E          | 1                  | ANL      | A,R6              |

| 20<br>20        | 1                  | ADD      | A,R4                | 5F          | 1                  | ANL      | A,R7              |

|                 | 1                  | ADD      | A,R5                | 60          | 2.                 | JZ       | code addr         |

| 2D              |                    | • •      |                     | 61          | 2                  | AJMP     | code addr         |

| 2E              | 1                  | ADD      | A,R6                | 62          | 2                  | XRL      | data addr,A       |

| 2F              | 1                  | ADD      | A,R7                | 63          | 3                  | XRL      | data addr, #da    |

| 30              | з                  | JNB      | bit addr,code addr  |             |                    | XRL      | A,#data           |

| 31              | 2                  | ACALL    | code addr           | 64          | 2                  |          | •                 |

| 32              | 1                  | RETI     |                     | 65          | 2                  | XRL      | A,data addr       |

intel

M8751H-8

.

202 🌔 🖿 4826175 0081784 8 🖿 Preliminary

| -                                                                           |                    |          |                      |  |             |                    |              | T-29-19-5             |  |

|-----------------------------------------------------------------------------|--------------------|----------|----------------------|--|-------------|--------------------|--------------|-----------------------|--|

| T·19-19.59<br>Table 2. Instruction Opcodes in Hexadecimal Order (Continued) |                    |          |                      |  |             |                    |              |                       |  |

|                                                                             | Number<br>of Bytes | Mnemonic | Operands             |  | Hex<br>Code | Number<br>of Bytes | Mnemonic     | Operands              |  |

|                                                                             | 1                  | XRL      | A,@R0                |  | 99          | 1                  | SUBB         | A,R1                  |  |

|                                                                             | 1                  | XRL      | A,@R1                |  | 9A          | 1                  | SUBB         | A,R2                  |  |

|                                                                             | 1                  | XRL      | A,R0                 |  | 9B          | 1                  | SUBB         | A,R3                  |  |

|                                                                             | 1                  | XRL      | A,R1                 |  | 9C          | 1                  | SUBB         | A,R4                  |  |

|                                                                             | 1                  | XRL      | A,R2                 |  | 9D          | 1                  | SUBB         | A,R5                  |  |

|                                                                             | 1 .                | XRL      | A,R3                 |  | 9E          | 1.                 | SUBB         | A,R6                  |  |

|                                                                             | 1                  | XRL      | A,R4                 |  | 9F          | 1                  | SUBB         | A,R7                  |  |

|                                                                             | 1                  | XRL      | A,R5                 |  | AO          | 2                  | ORL          | C,/bit addr           |  |

|                                                                             | <sup>1</sup> 1     | XRL      | A,R6                 |  | A1          | 2                  | AJMP         | code addr             |  |

|                                                                             | 1                  | XRL      | A,R7                 |  | A2          | 2                  | MOV          | C,bit addr            |  |

|                                                                             | 2                  | JNZ      | code addr            |  | A3          | 1                  | INC          | DPTR                  |  |

|                                                                             | 2                  | ACALL    | code addr            |  | A4          | 1.                 | MUL          | AB                    |  |

|                                                                             | 2                  | ORL      | C,bit addr           |  | A5          | •                  | reserved     |                       |  |

|                                                                             | 1                  | JMP      | @A+DPTR              |  | A6          | 2                  | MOV          | @R0,data addr         |  |

|                                                                             | 2                  | MOV      | A,#data              |  | A7          | 2                  | MOV          | @R1,data addr         |  |

|                                                                             | 3                  | MOV      | data addr. # data    |  | AB          | 2                  | MOV          | R0,data addr          |  |

|                                                                             | 2                  | MOV      | @R0.#data            |  | A9          | 2                  | MOV          | R1.data addr          |  |

|                                                                             | 2                  | MOV      | @R1,#data            |  | AA          | 2                  | MOV          | R2,data addr          |  |

|                                                                             | 2                  | MOV      | R0, #data            |  | AB          | 2                  | MOV          | R3.data addr          |  |

|                                                                             | 2                  | MOV      | R1,#data             |  | AC          | 2                  | MOV          | R4.data addr          |  |

|                                                                             | 2                  | MOV      | R2, #data            |  | AD          | 2                  | MOV          | R5,data addr          |  |

|                                                                             | 2                  | MOV      | R3,#data             |  | AE          | 2                  | MOV          | -                     |  |

|                                                                             | 2                  | MOV      | R4, #data            |  | AF          | . 2                | MOV          | R6,data addr          |  |

|                                                                             | . 2                | MOV      | R5, #data            |  | 80          | 2                  |              | R7,data addr          |  |

|                                                                             | 2                  | MOV      | R6, #data            |  | B1          | 2                  | ANL<br>ACALL | C,/bit addr           |  |

|                                                                             | 2                  | MOV      | R7, #data            |  | B2          | 2                  |              | code addr             |  |

|                                                                             | 2                  | SJMP     | code addr            |  | B2<br>B3    | 2                  | CPL          | bit addr              |  |

|                                                                             | 2                  | AJMP     | code addr            |  | 83<br>B4    | -                  |              | C .                   |  |

|                                                                             | 2                  |          |                      |  |             | 3                  | CJNE         | A,#data,code addr     |  |

|                                                                             | 2                  | MOVC     | C,bit addr           |  | 85          | 3                  | CJNE         | A,data addr,code addr |  |

|                                                                             |                    |          | A,@A+PC              |  | 86          | 3                  | CJNE         | @R0,#data,code addr   |  |

|                                                                             | 1                  | DIV .    | AB                   |  | B7          | 3                  | CJNE         | @R1,#data,code addr   |  |

|                                                                             | 3                  | MOV      | data addr, data addr |  | BB          | 3                  | CJNE         | R0, # data, code addr |  |

|                                                                             | 2                  | MOV .    | data addr,@R0        |  | B9          | 3                  | CJNE         | R1,#data,code addr    |  |

|                                                                             | 2                  | MOV      | data addr,@R1        |  | BA          | 3                  | CJNE         | R2, # data,code addr  |  |

|                                                                             | 2                  | MOV      | data addr,R0         |  | BB          | 3                  | CJNE         | R3, # data, code addr |  |

|                                                                             | 2                  | MOV      | data addr,R1         |  | BC          | 3                  | CJNE         | R4, #data,code addr   |  |

|                                                                             | 2                  | MOV      | data addr,R2         |  | 8D          | 3                  | CJNE         | R5,#data,code addr    |  |

| -                                                                           | 2                  | MOV      | data addr,R3         |  | BE          | 3                  | CJNE         | R6, #data,code addr   |  |

|                                                                             | 2                  | MOV      | data addr,R4         |  | BF          | 3                  | CJNE         | R7, #data,code addr   |  |

|                                                                             | 2                  | MOV      | data addr,R5         |  | CO          | 2                  | PUSH         | data addr             |  |

|                                                                             | 2                  | MOV      | data addr,R6         |  | C1          | 2                  | AJMP         | code addr             |  |

|                                                                             | 2                  | MOV      | data addr,R7         |  | C2          | 2                  | CLR          | bit addr              |  |

|                                                                             | 3                  | MOV      | DPTR,#data           |  | C3          | 1                  | CLR          | С                     |  |

|                                                                             | 2                  | ACALL    | code addr            |  | C4          | 1                  | SWAP         | Α ι                   |  |

|                                                                             | 2                  | MOV      | bit addr,C           |  | C5          | 2                  | XCH          | A,data addr           |  |

|                                                                             | 1                  | MOVC     | A,@A+DPTR            |  | C6          | 1                  | XCH          | A,@R0                 |  |

|                                                                             | 2                  | SUBB     | A, #data             |  | C7          | i                  | XCH          | A.@R1                 |  |

|                                                                             | 2                  | SUBB     | A,data addr          |  | C8          | 1                  | XCH          | A,R0                  |  |

|                                                                             | 1                  | SUBB     | A,@R0                |  | C9          | 1                  | XCH          | A,R1                  |  |

|                                                                             | 1                  | SUBB     | A,@R1                |  | ČĂ          | 1                  | XCH          | A,R2                  |  |

|                                                                             | 1                  | SUBB     | A,R0                 |  | CB          | 1                  | XCH          | A,R3                  |  |

R4,code addr

R6,code addr

R7,code addr

A,@DPTR

code addr

A,data addr

A,@R0

A,@R1

A

R5,code addr .

DJNZ

DJNZ

DJNZ

DJNZ

MOVX

AJMP

MOVX

MOVX

CLR

MOV

2

2

2

2

1

2

1

1

1

2

M8751H-8

20E D 📟 4826175 0081785 T 📖 PRELIMINARY

INTel

Hex

Code

cc CD CE CF D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 DA

DB

DC

DD

DE

DF

E0

E1

E2

E3

E4

E5

| Table 2. Instruction Opcodes in Hexadecimal Order (Continued) |          |                     |             |                    |          |              |  |  |  |  |

|---------------------------------------------------------------|----------|---------------------|-------------|--------------------|----------|--------------|--|--|--|--|

| Number<br>of Bytes                                            | Mnemonic | Operands            | Hex<br>Code | Number<br>of Bytes | Mnemonic | Operands     |  |  |  |  |

| 1                                                             | XCH      | A.R4                | E6          | 1                  | MOV      | A,@R0        |  |  |  |  |

| i                                                             | XCH      | A,R5                | E7          | 1                  | MOV      | A,@R1        |  |  |  |  |

| i                                                             | XCH      | A,R6                | E8          | 1                  | MOV      | A,RO         |  |  |  |  |

| 1                                                             | XCH      | A.R7                | E9          | 1                  | MOV      | A,R1         |  |  |  |  |

| 2                                                             | POP      | data addr           | EA          | 1                  | MOV      | A,R2         |  |  |  |  |

| 2                                                             | ACALL    | code addr           | EB          | 1                  | MOV      | A,R3         |  |  |  |  |

| 2                                                             | SETB     | bit addr            | É EC        | 1.4                | MOV      | A,R4         |  |  |  |  |

| 1                                                             | SETB     | C                   | ED          | - 1                | MOV      | A,R5         |  |  |  |  |

| i                                                             | DA       | A I                 | EE          | 1 1                | MOV "    | A,R6         |  |  |  |  |

| 3                                                             | DJNZ     | data addr.code addr | EF          | 1.                 | MOV ,    | , A,R7       |  |  |  |  |

| 1 .                                                           | XCHD     | A.@R0               | FO          | . 1                | MOVX     | @DPTR,A      |  |  |  |  |

| i.                                                            | XCHD     | A.@R1               | F1          | 2                  | AĆALL    | code addr    |  |  |  |  |

| 2                                                             | DJNZ     | R0.code addr        | F2          | 1                  | MOVX     | @R0,A        |  |  |  |  |

| 2                                                             | DJNZ     | R1.code addr        | F3          | . 1                | MOVX     | @R1,A        |  |  |  |  |

| 2                                                             | DJNZ     | R2,code addr        | F4          | 1                  | CPL      | Α            |  |  |  |  |

| 2                                                             | DJNZ     | R3.code addr        | F5          | 2                  | MOV      | data addr, A |  |  |  |  |

| 4                                                             | 00114    | 11010000 0000       |             |                    | MOV      | ADO A        |  |  |  |  |

F6

F7

F8

F9

FA

FB

FC

FD

FE

FF

T. 19-19.59

@R0,A

@R1,A

R0,A

R1,A

R2,A

R3,A

R4,A

R5,A

R6,A

R7,A

MOV

1

1

1

1

1

1

1

1

1

1