## 5 VOLT BULK ERASE FLASH MEMORY

28F010 and 28F020 (x8)

- Flash Electrical Chip-Erase

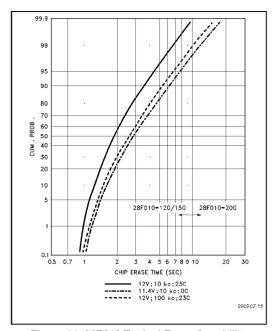

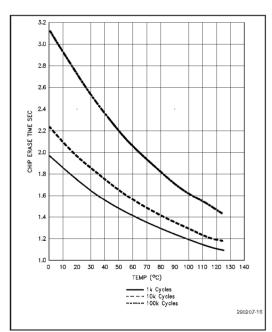

- 1-Mbit: 1 Second Typical Chip-Erase2-Mbit: 2 Second Typical Chip-Erase

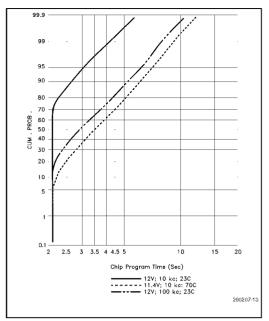

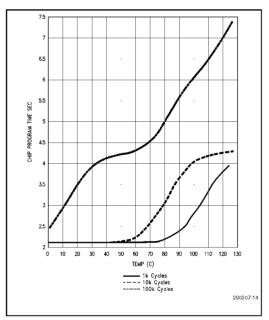

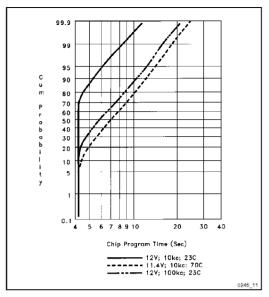

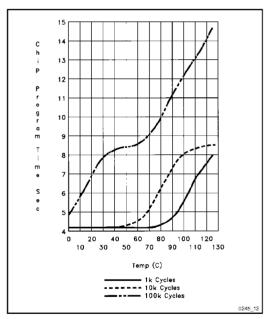

- Quick-Pulse Programming Algorithm

- 10 µs Typical Byte-Program

- 1-Mbit: 1 Second Chip-Program

- 2-Mbit: 2 Second Chip-Program

- 100,000 Erase/Program Cycles

- 12.0 V ±5% V<sub>PP</sub>

- High-Performance Read

- 90 ns Maximum Access Time

- CMOS Low Power Consumption

- 10 mA Typical Active Current

- 50 μA Typical Standby Current

- 0 Watts Data Retention Power

- Integrated Program/Erase Stop Timer

- Command Register Architecture for Microprocessor/Microcontroller Compatible Write Interface

- Noise Immunity Features

- ±10% V<sub>CC</sub> Tolerance

- Maximum Latch-Up Immunity through EPI Processing

- ETOX<sup>™</sup> Nonvolatile Flash Technology

- EPROM-Compatible Process Base

- High-Volume Manufacturing Experience

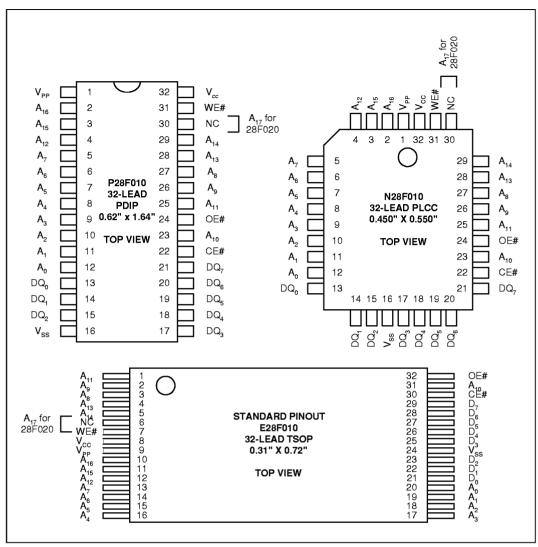

- JEDEC-Standard Pinouts

- 32-Pin Plastic Dip

- 32-Lead PLCC

- 32-Lead TSOP

(See Packaging Spec., Order #231369)

■ Extended Temperature Options

The Intel® 5 Volt Bulk Erase CMOS flash memory offers the most cost-effective and reliable alternative for read/write random access nonvolatile memory. The 28F010 and 28F020 add electrical chip-erasure and reprogramming to familiar EPROM technology. Memory contents can be rewritten: in a test socket; in a PROM-programmer socket; on-board during subassembly test; in-system during final test; and in-system after sale. The 28F010 and 28F020 increase memory flexibility, while contributing to time and cost savings.

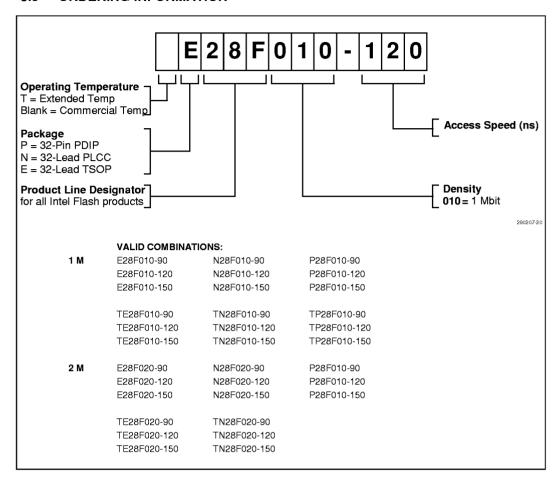

The 28F010 is a 1024 kilobit nonvolatile memory organized as 131,072 bytes of eight bits. Similarly, the 28F020 is a 2048 kilobit nonvolatile memory organized as 262,144 bytes of eight bits. Both devices are offered in 32-pin plastic dip or 32-lead PLCC and TSOP packages. Pin assignments conform to JEDEC standards for byte-wide EPROMs.

Extended erase and program cycling capability is designed into Intel<sup>®</sup> ETOX<sup>™</sup> (EPROM Tunnel Oxide) process technology. Advanced oxide processing, an optimized tunneling structure, and lower electric field combine to extend reliable cycling beyond that of traditional EEPROMs. With the 12.0 V V<sub>PP</sub> supply, the 28F010 and 28F020 perform 100,000 erase and program cycles—well within the time limits of the quick-pulse programming and quick-erase algorithms.

The Intel 28F010 and 28F020 employ advanced CMOS circuitry for systems requiring high-performance access speeds, low power consumption, and immunity to noise. Its 90 ns access time provides zero wait-state performance for a wide range of microprocessors and microcontrollers. Maximum standby current of 100  $\mu$ A translates into power savings when the device is deselected. Finally, the highest degree of latch-up protection is achieved through Intel's unique EPI processing. Prevention of latch-up is provided for stresses up to 100 mA on address and data pins, from -1 V to V<sub>CC</sub> + 1 V.

With Intel ETOX process technology base, the 28F010 and 28F020 build on years of EPROM experience to yield the highest levels of quality, reliability, and cost-effectiveness.

December 1998 Order Number: 290663-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F010 and 28F020 may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 8021-9808

or call 1-800-548-4725

or visit Intel's website at http://www.intel.com

Copyright @ Intel Corporation 1996, 1997, 1998.

<sup>\*</sup> Third-party brands and names are the property of their respective owners.

PAGE

## **CONTENTS**

PAGE

| 1.0 APPLICATIONS5                                                        | 4.5 DC Characteristics—28F020—TTL/NMOS Compatible—Commercial Products 22 |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 2.0 PRINCIPLES OF OPERATION9                                             | 4.6 DC Characteristics—28F010—CMOS                                       |

| 2.1 Integrated Stop Timer9                                               | Compatible—Commercial Products 24                                        |

| 2.2 Write Protection 10                                                  | 4.7 DC Characteristics—28F020—CMOS                                       |

| 2.2.1 Bus Operations 10                                                  | Compatible—Commercial Products 25                                        |

| 2.2.1.1 Read10                                                           | 4.8 DC Characteristics—28F010—TTL/NMO                                    |

| 2.2.1.2 Output Disable 10                                                | Compatible—Extended Temperature Products27                               |

| 2.2.1.3 Standby11                                                        | 4.9 DC Characteristics—28F020—TTL/NMO                                    |

| 2.2.1.4 Intelligent Identifier Operation 11                              | Compatible—Extended Temperature                                          |

| 2.2.1.5 Write11                                                          | Products29                                                               |

| 2.2.2 Command Definitions11                                              | 4.10 DC Characteristics—28F010—CMOS                                      |

| 2.2.2.1 Read Command                                                     | Compatible—Extended Temperature Products31                               |

| 2.2.2.2 Intelligent Identifier Command 12                                | 4.11 DC Characteristics—28F020—CMOS                                      |

| 2.2.2.3 Set-Up Erase/Erase Commands 13                                   | Compatible—Extended Temperature                                          |

| 2.2.2.4 Erase Verify Command 13                                          | Products32                                                               |

| 2.2.2.5 Set-Up Program/Program                                           | 4.12 AC Characteristics—28F010—Read-Only                                 |

| Commands13                                                               | Operation—Commercial and Extended Temperature Products                   |

| 2.2.2.6 Program Verify Command 13                                        | 4.13 AC Characteristics—28F020—Read Only                                 |

| 2.2.2.7 Reset Command 14                                                 | Operations—Commercial and Extended                                       |

| 2.2.3 Extended Erase/Program Cycling 14                                  | Temperature Products                                                     |

| 2.2.4 Quick-Pulse Programming Algorithm 14                               | 4.14 AC Characteristics—28F010—                                          |

| 2.2.5 Quick-Erase Algorithm14                                            | Write/Erase/Program Only Operation— Commercial and Extended Temperature  |

| 3.0 DESIGN CONSIDERATIONS 17                                             | Products38                                                               |

| 3.1 Two-Line Output Control                                              | 4.15 AC Characteristics—28F020—                                          |

| 3.2 Power Supply Decoupling                                              | Write/Erase/Program Only Operation—                                      |

| 3.3 V <sub>PP</sub> Trace on Printed Circuit Boards 17                   | Commercial and Extended Temperature Products                             |

| 3.4 Power-Up/Down Protection                                             | 4.16 AC Characteristics—28F010—Alternative                               |

| 3.5 5 Volt Bulk Erase Power Dissipation 17                               | CE#-Controlled Write—Commercial and                                      |

| 0.5 5 Volt Built Erase i Gwer Bissipation                                | Extended Temperature44                                                   |

| 4.0 ELECTRICAL SPECIFICATIONS 19                                         | 4.17 AC Characteristics—28F020—Alternate                                 |

| 4.1 Absolute Maximum Ratings 19                                          | CE# Controlled Writes—Commercial and<br>Extended Temperature Products    |

| 4.2 Operating Conditions                                                 | 4.18 Erase and Programming Performance 46                                |

| 4.3 Capacitance19                                                        | 5 Erass and Frogramming Fortomance 40                                    |

| 4.4 DC Characteristics—28F010—TTL/NMOS Compatible—Commercial Products 20 | 5.0 ORDERING INFORMATION47                                               |

| ·                                                                        | 6.0 ADDITIONAL INFORMATION47                                             |

## **REVISION HISTORY**

| Number | Description                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------|

| -001   | This document combines datasheets for the 28F010 (order 290207) and 28F020 (order 290245), bulk erase devices. |

### 1.0 APPLICATIONS

The Intel 28F010 and 28F020 flash memories provide nonvolatility along with the capability to perform over 100,000 electrical chip-erasure/reprogram cycles. These features make the 28F010 and 28F020 an innovative alternative to disk, EEPROM, and battery-backed static RAM. Where periodic updates of code and data tables are required, the 28F010 and 28F020 reprogrammability and nonvolatility make them the obvious and ideal replacements for EPROM.

Primary applications and operating systems stored in flash eliminate the slow disk-to-DRAM download process. This results in dramatic enhancement of performance and substantial reduction of power consumption—a consideration particularly important in portable equipment. Flash memory increases flexibility with electrical chip erasure and in-system update capability of operating systems and application code. With updatable code, system manufacturers can easily accommodate last-minute changes as revisions are made.

In diskless workstations and terminals, network traffic reduces to a minimum and systems are instant-on. Reliability exceeds that of electromechanical media. Often in these environments, power interruptions force extended re-boot periods for all networked terminals. This mishap is no longer an issue if boot code, operating systems, communication protocols and primary applications are flash resident in each terminal.

For embedded systems that rely on dynamic RAM/disk for main system memory or nonvolatile backup storage, the 28F010 and 28F020 flash memories offer a solid state alternative in a minimal form factor. The 28F010 and 28F020 provide higher performance, lower power consumption, instant-on capability, and allows an "eXecute in place" (XIP) memory hierarchy for code and data table reading. Additionally, the flash memory is more rugged and reliable in harsh environments where extreme temperatures and shock can cause disk-based systems to fail.

The need for code updates pervades all phases of a system's life—from prototyping to system manufacture to after sale service. The electrical chip-erasure and reprogramming ability of the 28F010 and 28F020 allow in-circuit alterability; this eliminates unnecessary handling and less reliable

socketed connections, while adding greater test, manufacture, and update flexibility.

Material and labor costs associated with code changes increases at higher levels of system integration—the most costly being code updates after sale. Code "bugs," or the desire to augment system functionality, prompt after sale code updates. Field revisions to EPROM-based code requires the removal of EPROM components or entire boards. With the 28F010 and 28F020, code updates are implemented locally via an edge connector, or remotely over a communication link.

For systems currently using a high-density static RAM/battery configuration for data accumulation, flash memory's inherent nonvolatility eliminates the need for battery backup. The concern for battery failure no longer exists, an important consideration for portable equipment and medical instruments, both requiring continuous performance. In addition, flash memory offers a considerable cost advantage over static RAM.

Flash memory's electrical chip erasure, byte programmability and complete nonvolatility fit well with data accumulation and recording needs. Electrical chip-erasure gives the designer a "blank slate" in which to log or record data. Data can be periodically off-loaded for analysis and the flash memory erased producing a new "blank slate."

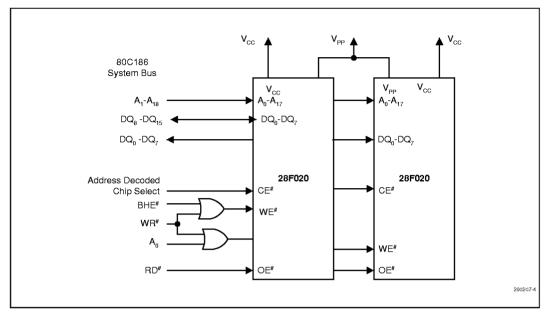

A high degree of on-chip feature integration simplifies memory-to-processor interfacing. Figure 3 depicts two 28F020s tied to the 80C186 system bus. The 228F010 and 28F020 architecture minimize interface circuitry needed for complete incircuit updates of memory contents.

The outstanding feature of the TSOP (Thin Small Outline Package) is the 1.2 mm thickness. TSOP is particularly suited for portable equipment and applications requiring large amounts of flash memory.

With cost-effective in-system reprogramming, extended cycling capability, and true nonvolatility, the 28F010 and 28F020 offer advantages to the alternatives: EPROMs, EEPROMs, battery backed static RAM, or disk. EPROM-compatible read specifications, straightforward interfacing, and incircuit alterability offers designers unlimited flexibility to meet the high standards of today's designs.

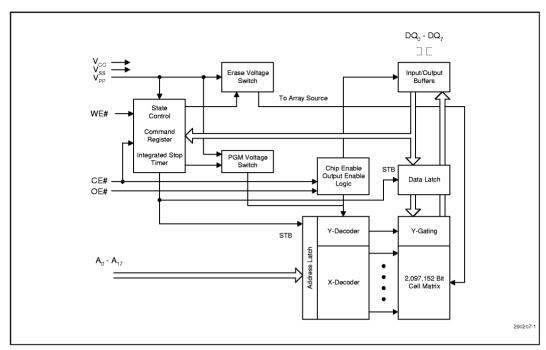

Figure 1. 28F020 Block Diagram

Table 1. Pin Description

| Symbol                           | Туре         | Name and Function                                                                                                                                                                                                                                                    |

|----------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>16</sub>  | INPUT        | ADDRESS INPUTS for memory addresses. Addresses are internally latched during a write cycle. 28F010: A[0–16], 28F020: A[0–17]                                                                                                                                         |

| DQ <sub>0</sub> –DQ <sub>7</sub> | INPUT/OUTPUT | DATA INPUT/OUTPUT: Inputs data during memory write cycles; outputs data during memory read cycles. The data pins are active high and float to tri-state off when the chip is deselected or the outputs are disabled. Data is internally latched during a write cycle |

| CE#                              | INPUT        | CHIP ENABLE: Activates the device's control logic, input buffers, decoders and sense amplifiers. CE# is active low; CE# high deselects the memory device and reduces power consumption to standby levels.                                                            |

| OE#                              | INPUT        | OUTPUT ENABLE: Gates the devices output through the data buffers during a read cycle. OE# is active low.                                                                                                                                                             |

| WE#                              | INPUT        | WRITE ENABLE: Controls writes to the control register and the array. Write enable is active low. Addresses are latched on the falling edge and data is latched on the rising edge of the WE# pulse.                                                                  |

|                                  |              | <b>Note:</b> With V <sub>PP</sub> ≤ 6.5 V, memory contents cannot be altered.                                                                                                                                                                                        |

| V <sub>PP</sub>                  |              | ERASE/PROGRAM POWER SUPPLY for writing the command register, erasing the entire array, or programming bytes in the array.                                                                                                                                            |

| Vcc                              |              | DEVICE POWER SUPPLY (5 V ±10%)                                                                                                                                                                                                                                       |

| V <sub>SS</sub>                  |              | GROUND                                                                                                                                                                                                                                                               |

| NC                               |              | NO INTERNAL CONNECTION to device. Pin may be driven or left floating.                                                                                                                                                                                                |

7

Figure 2. 28F010/28F020 Pin Configurations

Figure 3. 28F020 in a 80C186 System

### 2.0 PRINCIPLES OF OPERATION

Flash memory augments EPROM functionality with in-circuit electrical erasure and reprogramming. The 5 Volt Bulk Erase introduces a command register to manage this new functionality. The command register allows for: 100% TTL-level control inputs; fixed power supplies during erasure and programming; and maximum EPROM compatibility.

In the absence of high voltage on the  $V_{PP}$  pin, the 5 Volt Bulk Erase is a read-only memory. Manipulation of the external memory control pins yields the standard EPROM read, standby, output disable, and intelligent identifier operations.

The same EPROM read, standby, and output disable operations are available when high voltage is applied to the  $V_{\text{PP}}$  pin. In addition, high voltage on  $V_{\text{PP}}$  enables erasure and programming of the device. All functions associated with altering memory contents—intelligent identifier, erase, erase verify, program, and program verify—are accessed via the command register.

Commands are written to the register using standard microprocessor write timings. Register contents serve as input to an internal state machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for programming or erase operations. With the appropriate command written to the register, standard microprocessor read timings output array data, access the intelligent identifier codes, or output data for erase and program verification.

#### 2.1 Integrated Stop Timer

Successive command write cycles define the durations of program and erase operations; specifically, the program or erase time durations are normally terminated by associated Program or Erase Verify commands. An integrated stop timer provides simplified timing control over these operations; thus eliminating the need for maximum program/erase timing specifications. Programming and erase pulse durations are minimums only. When the stop timer terminates a program or erase operation, the device enters an inactive state and remains inactive until receiving the appropriate Verify or Reset command.

Table 2. 28F010/28F020 Bus Operations

| Mode       |                                    | V <sub>PP</sub> (1) | A <sub>0</sub>  | <b>A</b> 9                 | CE#             | OE#            | WE#             | DQ <sub>0</sub> –DQ <sub>7</sub> |

|------------|------------------------------------|---------------------|-----------------|----------------------------|-----------------|----------------|-----------------|----------------------------------|

|            | Read                               | V <sub>PPL</sub>    | <b>A</b> 0      | <b>A</b> 9                 | V <sub>IL</sub> | ۷⊔             | VIH             | Data Out                         |

|            | Output Disable                     | V <sub>PPL</sub>    | Х               | Х                          | V <sub>IL</sub> | $V_{IH}$       | V <sub>IH</sub> | Tri-State                        |

| READ-ONLY  | Standby                            | V <sub>PPL</sub>    | Х               | Х                          | V <sub>IH</sub> | Х              | Х               | Tri-State                        |

|            | Intelligent Identifier (Mfr)(2)    | V <sub>PPL</sub>    | V <sub>IL</sub> | <b>V</b> <sub>ID</sub> (3) | V <sub>IL</sub> | $V_{IL}$       | V <sub>IH</sub> | Data = 89H                       |

|            | Intelligent Identifier (Device)(2) | V <sub>PPL</sub>    | <b>∨</b> ⊒      | <b>V</b> <sub>ID</sub> (3) | V <sub>IL</sub> | ٧ <sub>L</sub> | VII             | Data = B4H                       |

|            | Read                               | V <sub>PPH</sub>    | <b>A</b> 0      | <b>A</b> 9                 | V <sub>IL</sub> | $V_{IL}$       | V <sub>IH</sub> | Data Out(4)                      |

| READ/WRITE | Output Disable                     | V <sub>PPH</sub>    | Х               | Х                          | V <sub>IL</sub> | $V_{IH}$       | V <sub>IH</sub> | Tri-State                        |

|            | Standby <sup>(5)</sup>             | V <sub>PPH</sub>    | Х               | Х                          | V <sub>IH</sub> | Х              | Х               | Tri-State                        |

|            | Write                              | V <sub>PPH</sub>    | <b>A</b> 0      | <b>A</b> 9                 | V <sub>IL</sub> | $V_{IH}$       | V <sub>IL</sub> | Data In(6)                       |

#### NOTES:

- 1. Refer to *DC Characteristics*. When  $V_{PP} = V_{PPL}$  memory contents can be read but not written or erased.

- Manufacturer and device codes may also be accessed via a command register write sequence. Refer to Table 3. All other addresses low.

- 3. V<sub>ID</sub> is the intelligent identifier high voltage. Refer to *DC Characteristics*.

- 4. Read operations with  $V_{PP} = V_{PPH}$  may access array data or the intelligent identifier codes.

- 5. With  $V_{PP}$  at high voltage, the standby current equals  $l_{CC} + l_{PP}$  (standby).

- 6. Refer to Table 3 for valid data-in during a write operation.

- 7. X can be V<sub>IL</sub> or V<sub>IH</sub>.

#### 2.2 Write Protection

The command register is only active when  $V_{PP}$  is at high voltage. Depending upon the application, the system designer may choose to make the  $V_{PP}$  power supply switchable—available only when memory updates are desired. When  $V_{PP} = V_{PPL}$ , the contents of the register default to the Read command, making the 28F010 and 28F020 read-only memories. In this mode, the memory contents cannot be altered.

Or, the system designer may choose to "hardwire"  $V_{PP}$ , making the high voltage supply constantly available. In this case, all command register functions are inhibited whenever  $V_{CC}$  is below the write lockout voltage  $V_{LKO}$ . (See Section 3.4,  $Power-Up/Down\ Protection$ .) The 28F010 and 28F020 are designed to accommodate either design practice, and to encourage optimization of the processor memory interface.

The two-step program/erase write sequence to the command register provides additional software write protections.

#### 2.2.1 BUS OPERATIONS

#### 2.2.1.1 Read

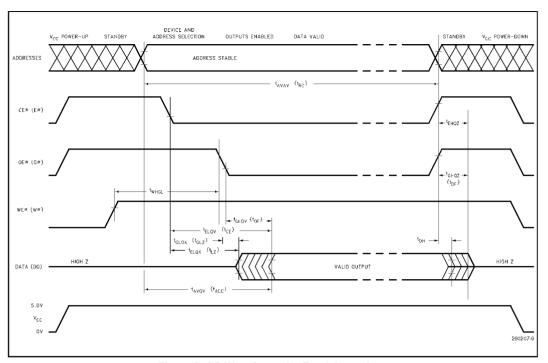

The 28F010 and 28F020 have two control functions, both of which must be logically active, to obtain data at the outputs. Chip Enable (CE#) is the power control and should be used for device selection. Output Enable (OE#) is the output control and should be used to gate data from the output pins, independent of device selection. Refer to the AC read timing waveforms.

When  $V_{PP}$  is high ( $V_{PPH}$ ), the read operation can be used to access array data, to output the intelligent identifier codes, and to access data for program/erase verification. When  $V_{PP}$  is low ( $V_{PPL}$ ), the read operation can **only** access the array data.

### 2.2.1.2 Output Disable

With OE# at a logic-high level ( $V_{\text{IH}}$ ), output from the device is disabled. Output pins are placed in a high-impedance state.

#### 2.2.1.3 Standby

With CE# at a logic-high level, the standby operation disables most of the 28F010 and 28F020's circuitry and substantially reduces device power consumption. The outputs are placed in a high-impedance state, independent of the OE# signal. If the 28F010 and 28F020 are deselected during erasure, programming, or program/erase verification, the device draws active current until the operation is terminated.

### 2.2.1.4 Intelligent Identifier Operation

The intelligent identifier operation outputs the manufacturer code (89H) and device code (B4H for 28F010, BDH for 28F020). Programming equipment automatically matches the device with its proper erase and programming algorithms.

With CE# and OE# at a logic low level, raising  $A_9$  to high voltage  $V_{\text{ID}}$  (see *DC Characteristics*) activates the operation. Data read from locations 0000H and 0001H represent the manufacturer's code and the device code, respectively.

The manufacturer and device codes can also be read via the command register, for instances where the 28F010 and 28F020 are erased and reprogrammed in the target system. Following a write of 90H to the command register, a read from address location 0000H outputs the manufacturer code (89H). A read from address 0001H outputs the device code (B4H for 28F010, BDH for 28F020).

#### 2.2.1.5 Write

Device erasure and programming are accomplished via the command register, when high voltage is applied to the  $V_{\text{PP}}$  pin. The contents of the register serve as input to the internal state machine. The state machine outputs dictate the function of the device.

The command register itself does not occupy an addressable memory location. The register is a latch used to store the command, along with address and data information needed to execute the command.

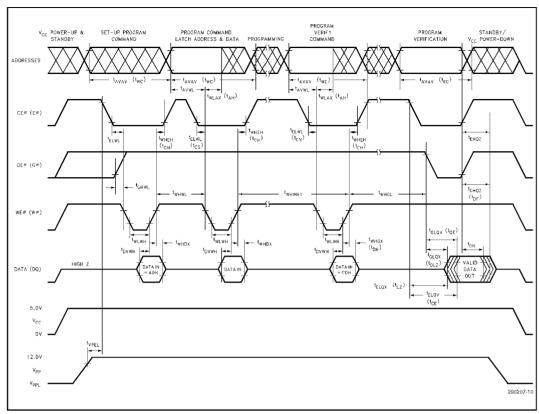

The command register is written by bringing WE# to a logic-low level  $(V_{IL})$ , while CE# is low. Addresses are latched on the falling edge of WE#, while data is latched on the rising edge of the WE# pulse. Standard microprocessor write timings are used.

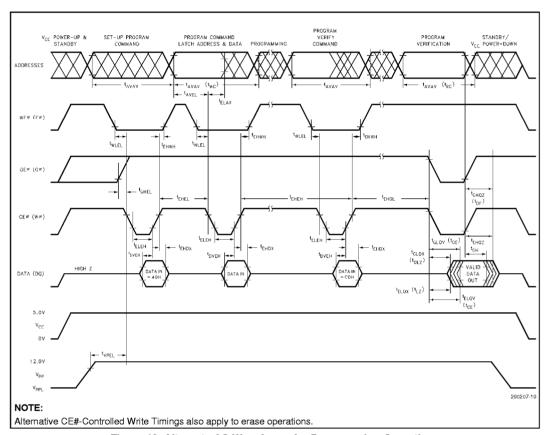

Refer to *AC Characteristics—Write/Erase/Program Only Operations* and the erase/programming waveforms for specific timing parameters.

#### 2.2.2 COMMAND DEFINITIONS

When low voltage is applied to the  $V_{PP}$  pin, the contents of the command register default to 00H, enabling read-only operations.

Placing high voltage on the V<sub>PP</sub> pin enables read/write operations. Device operations are selected by writing specific data patterns into the command register. Table 3 defines these 28F010/28F020 register commands.

**Table 3. Command Definitions**

|                                           |                        | Firs                     | t Bus Cycle            |                     | Second Bus Cycle         |                        |                     |  |  |  |

|-------------------------------------------|------------------------|--------------------------|------------------------|---------------------|--------------------------|------------------------|---------------------|--|--|--|

| Command                                   | Bus<br>Cycles<br>Req'd | Operation <sup>(1)</sup> | Address <sup>(2)</sup> | Data <sup>(3)</sup> | Operation <sup>(1)</sup> | Address <sup>(2)</sup> | Data <sup>(3)</sup> |  |  |  |

| Read Memory                               | 1                      | Write                    | Х                      | 00H                 |                          |                        |                     |  |  |  |

| Read Intelligent<br>Identifier Codes(4)   | 3                      | Write                    | IA                     | 90H                 | Read                     | IA                     | ID                  |  |  |  |

| Set-Up<br>Erase/Erase(5)                  | 2                      | Write                    | Х                      | 20H                 | Write                    | Х                      | 20H                 |  |  |  |

| Erase Verify(5)                           | 2                      | Write                    | EA                     | A0H                 | Read                     | Х                      | EVD                 |  |  |  |

| Set-Up Program/<br>Program <sup>(6)</sup> | 2                      | Write                    | Х                      | 40H                 | Write                    | PA                     | PD                  |  |  |  |

| Program Verify(6)                         | 2                      | Write                    | Х                      | C0H                 | Read                     | Х                      | PVD                 |  |  |  |

| Reset <sup>(7)</sup>                      | 2                      | Write                    | Х                      | FFH                 | Write                    | Х                      | FFH                 |  |  |  |

#### NOTES:

- 1. Bus operations are defined in Table 2.

- 2. IA = Identifier address: 00H for manufacturer code, 01H for device code.

- EA = Erase Address: Address of memory location to be read during erase verify.

- PA = Program Address: Address of memory location to be programmed.

- Addresses are latched on the falling edge of the WE# pulse.

- 3. ID = Identifier Data: Data read from location IA during device identification (Mfr = 89H, Device = (B4H for 28F010, BDH for 28F020).

- EVD = Érase Verify Data: Data read from location EA during erase verify.

- PD = Program Data: Data to be programmed at location PA. Data is latched on the rising edge of WE#.

- PVD = Program Verify Data: Data read from location PA during program verify. PA is latched on the Program command.

- 4. Following the Read Intelligent ID command, two read operations access manufacturer and device codes.

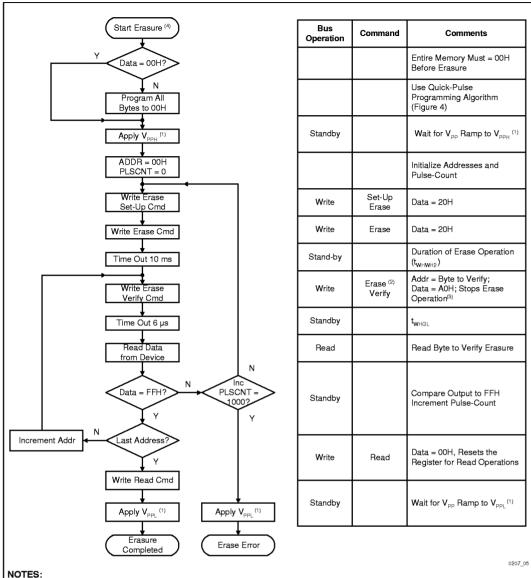

- 5. Figure 5 illustrates the 28F010/28F020 Quick-Erase Algorithm flowchart.

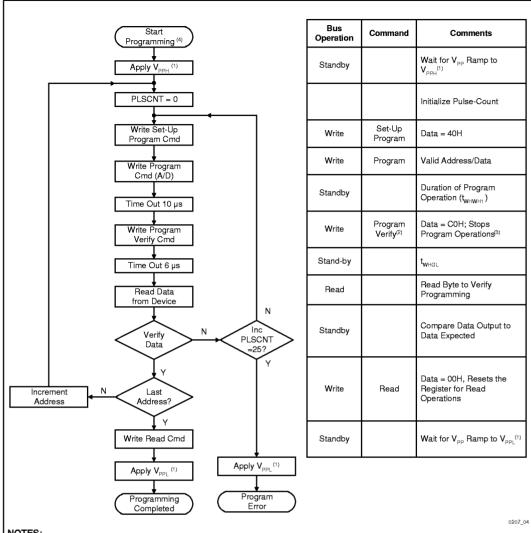

- 6. Figure 4 illustrates the 28F010/28F020 Quick-Pulse Programming Algorithm flowchart.

- 7. The second bus cycle must be followed by the desired command register write.

### 2.2.2.1 Read Command

While  $V_{PP}$  is high, for erasure and programming, memory contents can be accessed via the Read command. The read operation is initiated by writing 00H into the command register. Microprocessor read cycles retrieve array data. The device remains enabled for reads until the command register contents are altered.

The default contents of the register upon  $V_{PP}$  power-up is 00H. This default value ensures that no spurious alteration of memory contents occurs during the  $V_{PP}$  power transition. Where the  $V_{PP}$  supply is hardwired to the 28F010 or the 28F020, the device powers-up and remains enabled for reads until the command register contents are changed.

Refer to the *AC Characteristics—Read-Only Operations* and waveforms for specific timing parameters.

### 2.2.2.2 Intelligent Identifier Command

Flash memories are intended for use in applications where the local CPU alters memory contents. As such, manufacturer and device codes must be accessible while the device resides in the target system. PROM programmers typically access signature codes by raising  $A_{\rm 9}$  to a high voltage. However, multiplexing high voltage onto address lines is not a desired system design practice.

The 28F010 and 28F020 contain an intelligent identifier operation to supplement traditional PROMprogramming methodology. The operation is initiated by writing 90H into the command register. Following the command Write, a read cycle from address 0000H retrieves the manufacturer code of 89H. A read cycle from address 0001H returns the device code of (B4H for 28F010, BDH for 28F020). To terminate the operation, it is necessary to write another valid command into the register.

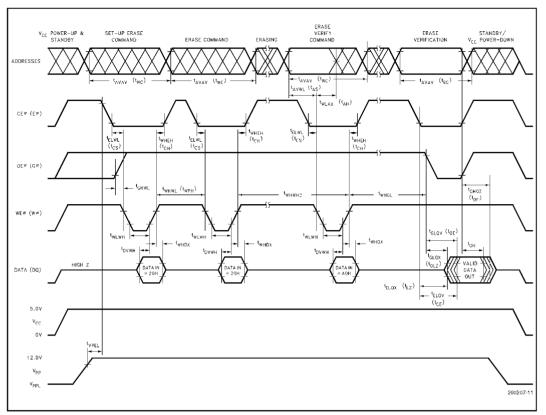

#### 2.2.2.3 Set-Up Erase/Erase Commands

Set-Up Erase is a command-only operation that stages the device for electrical erasure of all bytes in the array. The set-up erase operation is performed by writing 20H to the command register.

To commence chip-erasure, the Erase command (20H) must again be written to the register. The erase operation begins with the rising edge of the WE# pulse and terminates with the rising edge of the next WE# pulse (i.e., Erase Verify command).

This two-step sequence of set-up followed by execution ensures that memory contents are not accidentally erased. Also, chip-erasure can only occur when high voltage is applied to the pin. In the absence of this high voltage, memory contents are protected against erasure. Refer to AC Characteristics—Write/Erase/Program Only Operations and waveforms for specific timing parameters.

#### 2.2.2.4 Erase Verify Command

The Erase command erases all bytes of the array in parallel. After each erase operation, all bytes must be verified. The erase verify operation is initiated by writing A0H into the command register. The address for the byte to be verified must be supplied as it is latched on the falling edge of the WE# pulse. The register write terminates the erase operation with the rising edge of its WE# pulse.

The 5 Volt Bulk Erase applies an internallygenerated margin voltage to the addressed byte. Reading FFH from the addressed byte indicates that all bits in the byte are erased.

The Erase Verify command must be written to the command register prior to each byte verification to latch its address. The process continues for each byte in the array until a byte does not return FFH data, or the last address is accessed.

In the case where the data read is not FFH, another erase operation is performed. (Refer Section Set-Up Erase/Erase Commands.) Verification then resumes from the address of the last-verified byte. Once all bytes in the array have been verified, the erase step is complete. The device can be programmed. At this point, the verify operation is terminated by writing a valid command (e.g., Program Set-Up) to the command register. 28F010/28F020 Figure 5, the Quick-Erase Algorithm flowchart, illustrates how commands and bus operations are combined to perform electrical erasure of the 28F010 and 28F020. Refer to AC Characteristics-Write/Erase/Program Only Operations and waveforms for specific timing parameters.

## 2.2.2.5 Set-Up Program/Program Commands

Set-up program is a command-only operation that stages the device for byte programming. Writing 40H into the command register performs the set-up operation.

Once the program set-up operation is performed, the next WE# pulse causes a transition to an active programming operation. Addresses are internally latched on the falling edge of the WE# pulse. Data is internally latched on the rising edge of the WE# pulse. The rising edge of WE# also begins the programming operation. The programming operation terminates with the next rising edge of WE#, used to write the Program Verify command. Refer to AC Characteristics—Write/Erase/Program Only Operations and Waveforms for specific timing parameters.

#### 2.2.2.6 Program Verify Command

The 5 Volt Bulk Erase is programmed on a byte-bybyte basis. Byte programming may occur sequentially or at random. Following each programming operation, the byte just programmed must be verified.

The program verify operation is initiated by writing COH into the command register. The register write terminates the programming operation with the rising edge of its WE# pulse. The program verify operation stages the device for verification of the byte last programmed. No new address information is latched.

The 5 Volt Bulk Erase applies an internally-generated margin voltage to the byte. A microprocessor read cycle outputs the data. A successful comparison between the programmed byte and true data means that the byte is successfully programmed. Programming then proceeds to the next desired byte location. Figure 5, the 28F010/28F020 Quick-Pulse Programming Algorithm flowchart, illustrates how commands are combined with bus operations to perform byte programming. Refer to AC Characteristics—Write/Erase/Program Only Operations and waveforms for specific timing parameters.

### 2.2.2.7 Reset Command

A Reset command is provided as a means to safely abort the Erase or Program command sequences. Following either Set-Up command (Erase or Program) with two consecutive writes of FFH will safely abort the operation. Memory contents will not be altered. A valid command must then be written to place the device in the desired state.

## 2.2.3 EXTENDED ERASE/PROGRAM CYCLING

EEPROM cycling failures have always concerned users. The high electrical field required by thin oxide EEPROMs for tunneling can literally tear apart the oxide at defect regions. To combat this, some suppliers have implemented redundancy schemes, reducing cycling failures to insignificant levels. However, redundancy requires that cell size be doubled—an expensive solution.

Intel has designed extended cycling capability into its ETOX flash memory technology. Resulting improvements in cycling reliability come without increasing memory cell size or complexity. First, an advanced tunnel oxide increases the charge carrying ability ten-fold. Second, the oxide area per cell subjected to the tunneling electric field is one-tenth that of common EEPROMs, minimizing the probability of oxide defects in the region. Finally, the peak electric field during erasure is approximately 2 MV/cm lower than EEPROM. The lower electric field greatly reduces oxide stress and the probability of failure.

The 5 Volt Bulk Erase is capable or 100,000 program/erase cycles. The device is programmed and erased using Intel's quick-pulse programming

and quick- erase algorithms. Intel's algorithmic approach uses a series of operations (pulses), along with byte verification, to completely and reliably erase and program the device.

## 2.2.4 QUICK-PULSE PROGRAMMING ALGORITHM

The quick-pulse programming algorithm uses programming operations of 10 µs duration. Each operation is followed by a byte verification to determine when the addressed byte has been successfully programmed. The algorithm allows for up to 25 programming operations per byte, although most bytes verify on the first or second operation. The entire sequence of programming and byte verification is performed with V<sub>PP</sub> at high voltage. Figure 4 illustrates the *28F010/28F020 Quick-Pulse Programming Algorithm* flowchart.

#### 2.2.5 QUICK-ERASE ALGORITHM

Intel's quick-erase algorithm yields fast and reliable electrical erasure of memory contents. The algorithm employs a closed-loop flow, similar to the quick-pulse programming algorithm, to simultaneously remove charge from all bits in the array.

Erasure begins with a read of memory contents. The 5 Volt Bulk Erase is erased when shipped from the factory. Reading FFH data from the device would immediately be followed by device programming.

For devices being erased and reprogrammed, uniform and reliable erasure is ensured by first programming all bits in the device to their charged state (Data = 00H). This is accomplished, using the quick-pulse programming algorithm, in approximately two seconds.

Erase execution then continues with an initial erase operation. Erase verification (data = FFH) begins at address 0000H and continues through the array to the last address, or until data other than FFH is encountered. With each erase operation, an increasing number of bytes verify to the erased state. Erase efficiency may be improved by storing the address of the last byte verified in a register. Following the next erase operation, verification starts at that stored address location. Erasure typically occurs in one second. Figure 5 illustrates the 28F010/28F020 Quick-Erase Algorithm flowchart.

NOTES:

See DC Characteristics for the value of  $V_{\text{PPH}}$  and  $V_{\text{PPL}}$ . 1.

- 2. Program Verify is only performed after byte programming. A final read/compare may be performed (optional) after the register is written with the Read command.

- 3. Refer to Principles of Operation.

- **CAUTION:** The algorithm **must be followed** to ensure proper and reliable operation of the device. 4.

Figure 4. 28F010/28F020 Quick-Pulse Programming Algorithm

15

- 1. See *DC Characteristics* for the value of V<sub>PPH</sub> and V<sub>PPL</sub>.

- Erase Verify is performed only after chip-erasure. A final read/compare may be performed (optional) after the register is 2. written with the Read command.

- 3. Refer to Principles of Operation.

- **CAUTION:** The algorithm **must be followed** to ensure proper and reliable operation of the device.

Figure 5. 28F010/28F020 Quick-Erase Algorithm

#### 3.0 DESIGN CONSIDERATIONS

### 3.1 Two-Line Output Control

Flash memories are often used in larger memory arrays. Intel provides two read control inputs to accommodate multiple memory connections. Two-line control provides for:

- a. the lowest possible memory power dissipation

- complete assurance that output bus contention will not occur.

To efficiently use these two control inputs, an address decoder output should drive chip-enable, while the system's read signal controls all flash memories and other parallel memories. This assures that only enabled memory devices have active outputs, while deselected devices maintain the low power standby condition.

### 3.2 Power Supply Decoupling

Flash memory power-switching characteristics require careful device decoupling. System designers are interested in three supply current (I<sub>CC</sub>) issues—standby, active, and transient current peaks produced by falling and rising edges of chipenable. The capacitive and inductive loads on the device outputs determine the magnitudes of these peaks.

Two-line control and proper decoupling capacitor selection will suppress transient voltage peaks. Each device should have a 0.1  $\mu$ F ceramic capacitor connected between V<sub>CC</sub> and V<sub>SS</sub>, and between V<sub>PP</sub> and V<sub>SS</sub>.

Place the high-frequency, low-inherent inductance capacitors as close as possible to the devices. Also, for every eight devices, a 4.7  $\mu\text{F}$  electrolytic capacitor should be placed at the array's power supply connection, between  $V_{\text{CC}}$  and  $V_{\text{SS}}$ . The bulk capacitor will overcome voltage slumps caused by printed circuit board trace inductance, and will supply charge to the smaller capacitors as needed.

## 3.3 V<sub>PP</sub> Trace on Printed Circuit Boards

Programming flash memories, while they reside in the target system, requires that the printed circuit board designer pay attention to the  $V_{PP}$  power supply trace. The  $V_{PP}$  pin supplies the memory cell current for programming. Use similar trace widths and layout considerations given the  $V_{CC}$  power bus. Adequate  $V_{PP}$  supply traces and decoupling will decrease  $V_{PP}$  voltage spikes and overshoots.

### 3.4 Power-Up/Down Protection

The 5 Volt Bulk Erase is designed to offer protection against accidental erasure or programming during power transitions. Upon power-up, the 5 Volt Bulk Erase is indifferent as to which power supply,  $V_{\rm PP}$  or  $V_{\rm CC}$ , powers up first. Power supply sequencing is not required. Internal circuitry in the 5 Volt Bulk Erase ensures that the command register is reset to the read mode on power-up.

A system designer must guard against active writes for  $V_{CC}$  voltages above  $V_{LKO}$  when  $V_{PP}$  is active. Since both WE# and CE# must be low for a command write, driving either to  $V_{IH}$  will inhibit writes. The control register architecture provides an added level of protection since alteration of memory contents only occurs after successful completion of the two-step command sequences.

# 3.5 5 Volt Bulk Erase Power Dissipation

When designing portable systems, designers must consider battery power consumption not only during device operation, but also for data retention during system idle time. Flash nonvolatility increases the usable battery life of your system because the 5 Volt Bulk Erase does not consume any power to retain code or data when the system is off. Table 4 illustrates the power dissipated when updating the 5 Volt Bulk Erase.

Table 4. 5 Volt Bulk Erase Typical Update Power Dissipation(4)

| Operation                    | Notes | Power Dissipatio | n (Watt-Seconds) |

|------------------------------|-------|------------------|------------------|

|                              |       | 28F010           | 28F020           |

| Array Program/Program Verify | 1     | 0.171            | 0.34             |

| Array Erase/Erase Verify     | 2     | 0.136            | 0.37             |

| One Complete Cycle           | 3     | 0.478            | 1.05             |

- 1. Formula to calculate typical Program/Program Verify Power = [V<sub>PP</sub> × # Bytes × typical # Prog Pulses (t<sub>WHWH1</sub> × I<sub>PP2</sub> typical + t<sub>WHGL</sub> × I<sub>PP4</sub> typical)] + [V<sub>CC</sub> × # Bytes × typical # Prog Pulses (t<sub>WHWH1</sub> × I<sub>CC2</sub> typical + t<sub>WHGL</sub> × I<sub>CC4</sub> typical)].

- Formula to calculate typical Erase/Erase Verify Power = [V<sub>PP</sub> (V<sub>PP3</sub> typical × t<sub>ERASE</sub> typical + I<sub>PP5</sub> typical × t<sub>WHGL</sub> × # Bytes)] + [V<sub>CC</sub> (I<sub>CC3</sub> typical × t<sub>ERASE</sub> typical + I<sub>CC5</sub> typical × t<sub>WHGL</sub> × # Bytes)].

- 3. One Complete Cycle = Array Preprogram + Array Erase + Program.

- 4. "Typicals" are not guaranteed, but based on a limited number of samples from production lots.

### 4.0 ELECTRICAL SPECIFICATIONS

### 4.1 Absolute Maximum Ratings\*

| Operating Temperature                      |

|--------------------------------------------|

| During Read 0 °C to +70 °C(1)              |

| During Erase/Program 0 °C to +70 °C(1)     |

| Operating Temperature                      |

| During Read40 °C to +85 °C(2)              |

| During Erase/Program40 °C to +85 °C(2)     |

| Temperature Under Bias10 °C to +80 °C(1)   |

| Temperature Under Bias50 °C to +95 °C(2)   |

| Storage Temperature65 °C to +125 °C        |

| Voltage on Any Pin with                    |

| Respect to Ground2.0 V to +7.0 V(3)        |

| Voltage on Pin A <sub>9</sub> with         |

| Respect to Ground2.0 V to +13.5 V(3, 4)    |

| V <sub>PP</sub> Supply Voltage with        |

| Respect to Ground                          |

| During Erase/Program2.0 V to +14.0 V(3, 4) |

| V <sub>CC</sub> Supply Voltage with        |

| Respect to Ground2.0 V to +7.0 V(3)        |

| Output Short Circuit Current 100 mA(5)     |

|                                            |

NOTICE: This is a production datasheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the Absolute Maximum Ratings may cause permanent damage. These are stress ratings only. Operation beyond the Operating Conditions is not recommended and extended exposure beyond the Operating Conditions may affect device reliability.

#### NOTES:

- Operating Temperature is for commercial product as defined by this specification.

- 2. Operating Temperature is for extended temperature products as defined by this specification.

- Minimum DC input voltage is -0.5 V. During transitions, inputs may undershoot to -2.0 V for periods less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5 V, which may overshoot to V<sub>CC</sub> + 2.0 V for periods less than 20 ns.

- 4. Maximum DC voltage on A<sub>9</sub> or V<sub>PP</sub> may overshoot to +14.0 V for periods less than 20 ns.

- 5. Output shorted for no more than one second. No more than one output shorted at a time.

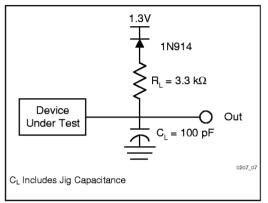

- See AC Testing Input/Output Waveform (Figure 6) and AC Testing Load Circuit (Figure 7) for testing characteristics.

### 4.2 Operating Conditions

|                 |                                                     | Lin  |      |      |

|-----------------|-----------------------------------------------------|------|------|------|

| Symbol          | Parameter                                           | Min  | Max  | Unit |

| T <sub>A</sub>  | Operating Temperature(1)                            | 0    | 70   | °C   |

| T <sub>A</sub>  | Operating Temperature(2)                            | -40  | +85  | °C   |

| Vcc             | V <sub>CC</sub> Supply Voltage (10%) <sup>(6)</sup> | 4.50 | 5.50 | V    |

| V <sub>CC</sub> | V <sub>CC</sub> Supply Voltage (5%) <sup>(7)</sup>  | 4.75 | 5.25 | V    |

### 4.3 Capacitance

$T_A = 25 \,^{\circ}C$ ,  $f = 1.0 \, MHz$

|                  |                             |       | Lin | nits |      |                        |

|------------------|-----------------------------|-------|-----|------|------|------------------------|

| Symbol           | Parameter                   | Notes | Min | Max  | Unit | Conditions             |

| C <sub>IN</sub>  | Address/Control Capacitance | 1     |     | 8    | pF   | V <sub>IN</sub> = 0 V  |

| C <sub>OUT</sub> | Output Capacitance          | 1     |     | 12   | pF   | V <sub>OUT</sub> = 0 V |

#### NOTE:

1. Sampled, not 100% tested.

# 4.4 DC Characteristics—28F010—TTL/NMOS Compatible Commercial Products

|                  |                                                  |       |       | Limits |                          |      |                                                                                                    |

|------------------|--------------------------------------------------|-------|-------|--------|--------------------------|------|----------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                        | Notes | Min   | Typ(3) | Max                      | Unit | Test Conditions                                                                                    |

| ILI              | Input Leakage Current                            | 1     |       |        | ±1.0                     | μΑ   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>      |

| ILO              | Output Leakage Current                           | 1     |       |        | ±10                      | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>OUT</sub> = V <sub>CC</sub> or V <sub>SS</sub>     |

| Iccs             | V <sub>CC</sub> Standby Current                  | 1     |       | 0.3    | 1.0                      | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE# = V <sub>IH</sub>                                     |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Read Current              | 1     |       | 10     | 30                       | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max, CE# = V <sub>IL</sub><br>f = 6 MHz, I <sub>OUT</sub> = 0 mA |

| I <sub>CC2</sub> | V <sub>CC</sub> Programming Current              | 1, 2  |       | 1.0    | 10                       | mA   | Programming in Progress                                                                            |

| I <sub>CC3</sub> | V <sub>CC</sub> Erase Current                    | 1, 2  |       | 5.0    | 15                       | mΑ   | Erasure in Progress                                                                                |

| I <sub>CC4</sub> | V <sub>CC</sub> Program Verify<br>Current        | 1, 2  |       | 5.0    | 15                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress                                   |

| I <sub>CC5</sub> | V <sub>CC</sub> Erase Verify Current             | 1, 2  |       | 5.0    | 15                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                     |

| I <sub>PPS</sub> | V <sub>PP</sub> Leakage Current                  | 1     |       |        | ±10                      | μΑ   | $V_{PP} \le V_{CC}$                                                                                |

| I <sub>PP1</sub> | V <sub>PP</sub> Read Current or Standby Current  | 1     |       | 90     | 200                      | μA   | V <sub>PP</sub> > V <sub>CC</sub>                                                                  |

|                  |                                                  |       |       |        | ±10.0                    |      | $V_{PP} \le V_{CC}$                                                                                |

| I <sub>PP2</sub> | V <sub>PP</sub> Programming Current              | 1, 2  |       | 8.0    | 30                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Programming in Progress                                      |

| I <sub>PP3</sub> | V <sub>PP</sub> Erase Current                    | 1, 2  |       | 6.0    | 30                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erasure in Progress                                          |

| I <sub>PP4</sub> | V <sub>PP</sub> Program Verify<br>Current        | 1, 2  |       | 2.0    | 5.0                      | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress                                   |

| I <sub>PP5</sub> | V <sub>PP</sub> Erase Verify Current             | 1, 2  |       | 2.0    | 5.0                      | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                     |

| VIL              | Input Low Voltage                                |       | -0.5  |        | 0.8                      | ٧    |                                                                                                    |

| V <sub>IH</sub>  | Input High Voltage                               |       | 2.0   |        | V <sub>CC</sub><br>+ 0.5 | ٧    |                                                                                                    |

| V <sub>OL</sub>  | Output Low Voltage                               |       |       |        | 0.45                     | ٧    | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OL</sub> = 5.8 mA                                  |

| V <sub>OH1</sub> | Output High Voltage                              |       | 2.4   |        |                          | ٧    | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OH</sub> = -2.5 mA                                 |

| V <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Voltage |       | 11.50 |        | 13.00                    | ٧    |                                                                                                    |

# 4.4 DC Characteristics—28F010—TTL/NMOS Compatible Commercial Products (Continued)

|                  |                                                  |       | Limits |        |       |      |                                                                           |

|------------------|--------------------------------------------------|-------|--------|--------|-------|------|---------------------------------------------------------------------------|

| Symbol           | Parameter                                        | Notes | Min    | Typ(3) | Max   | Unit | Test Conditions                                                           |

| I <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Current | 1, 2  |        | 90     | 200   | μΑ   | $A_9 = V_{ID}$                                                            |

| V <sub>PPL</sub> | V <sub>PP</sub> during Read-Only<br>Operations   |       | 0.00   |        | 6.5   | ٧    | NOTE: Erase/Program are Inhibited when V <sub>PP</sub> = V <sub>PPL</sub> |

| V <sub>PPH</sub> | V <sub>PP</sub> during Read/Write<br>Operations  |       | 11.40  |        | 12.60 | ٧    |                                                                           |

| V <sub>LKO</sub> | V <sub>CC</sub> Erase/Write Lock<br>Voltage      |       | 2.5    |        |       | ٧    |                                                                           |

### NOTES:

Sampled, not 100% tested.

- All currents are in RMS unless otherwise noted. Typical values at V<sub>CC</sub> = 5.0 V, V<sub>PP</sub> = 12.0 V, T = 25 °C. These currents are valid for all product versions (packages and speeds).

- 2. Not 100% tested: characterization data available.

- 3. "Typicals" are not guaranteed, but based on a limited number of samples from production lots.

21

# 4.5 DC Characteristics—28F020—TTL/NMOS Compatible Commercial Products

|                  |                                             |       |     | Limits             |      |      |                                                                                                     |

|------------------|---------------------------------------------|-------|-----|--------------------|------|------|-----------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                   | Notes | Min | Typ <sup>(3)</sup> | Max  | Unit | Test Conditions                                                                                     |

| ILI              | Input Leakage Current                       | 1     |     |                    | ±1.0 | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>       |

| I <sub>LO</sub>  | Output Leakage Current                      | 1     |     |                    | ±10  | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>OUT</sub> = V <sub>CC</sub> or V <sub>SS</sub>      |

| Iccs             | V <sub>CC</sub> Standby Current             | 1     |     | 0.3                | 1.0  | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE# = V <sub>IH</sub>                                      |

| Icc1             | V <sub>CC</sub> Active Read Current         | 1     |     | 10                 | 30   | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max CE# = V <sub>IL</sub><br>f = 6 MHz<br>I <sub>OUT</sub> = 0 mA |

| I <sub>CC2</sub> | V <sub>CC</sub> Programming Current         | 1, 2  |     | 1.0                | 10   | mA   | Programming in Progress                                                                             |

| I <sub>CC3</sub> | V <sub>CC</sub> Erase Current               | 1, 2  |     | 5.0                | 15   | mA   | Erasure in Progress                                                                                 |

| I <sub>CC4</sub> | V <sub>CC</sub> Program Verify<br>Current   | 1, 2  |     | 5.0                | 15   | mA   | V <sub>PP</sub> = V <sub>PPH</sub> Program Verify in Progress                                       |

| I <sub>CC5</sub> | V <sub>CC</sub> Erase Verify Current        | 1, 2  |     | 5.0                | 15   | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                      |

| I <sub>PPS</sub> | V <sub>PP</sub> Leakage Current             | 1     |     |                    | ±10  | μA   | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                                   |

| I <sub>PP1</sub> | V <sub>PP</sub> Read Current, ID<br>Current | 1     |     | 90                 | 200  | μA   | V <sub>PP</sub> > V <sub>CC</sub>                                                                   |

|                  | or Standby Current                          |       |     |                    | ±10  |      | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                                   |

| I <sub>PP2</sub> | V <sub>PP</sub> Programming Current         | 1, 2  |     | 8                  | 30   | mA   | V <sub>PP</sub> = V <sub>PPH</sub> Programming in<br>Progress                                       |

| I <sub>PP3</sub> | V <sub>PP</sub> Erase Current               | 1, 2  |     | 10                 | 30   | mA   | V <sub>PP</sub> = V <sub>PPH</sub>                                                                  |

| I <sub>PP4</sub> | V <sub>PP</sub> Program Verify<br>Current   | 1, 2  |     | 2.0                | 5.0  | mA   | V <sub>PP</sub> = V <sub>PPH</sub> Program Verify in<br>Progress                                    |

| I <sub>PP5</sub> | V <sub>PP</sub> Erase- Verify Current       | 1, 2  |     | 2.0                | 5.0  | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                      |

# 4.5 DC Characteristics—29F020—TTL/NMOS Compatible Commercial Products (Continued)

|                  |                                                  |       |       | Limits             |                       |      |                                                                           |

|------------------|--------------------------------------------------|-------|-------|--------------------|-----------------------|------|---------------------------------------------------------------------------|

| Symbol           | Parameter                                        | Notes | Min   | Typ <sup>(3)</sup> | Max                   | Unit | Test Conditions                                                           |

| V <sub>IL</sub>  | Input Low Voltage                                |       | -0.5  |                    | 0.8                   | ٧    |                                                                           |

| V <sub>IH</sub>  | Input High Voltage                               |       | 2.0   |                    | V <sub>CC</sub> + 0.5 | ٧    |                                                                           |

| V <sub>OL</sub>  | Output Low Voltage                               |       |       |                    | 0.45                  | V    | V <sub>CC</sub> = V <sub>CC</sub> Min I <sub>OL</sub> = 5.8 mA            |

| V <sub>OH1</sub> | Output High Voltage                              |       | 2.4   |                    |                       | V    | $V_{\rm CC} = V_{\rm CC}  \text{Min I}_{\rm OH} = -2.5  \text{mA}$        |

| V <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Voltage |       | 11.50 |                    | 13.00                 | ٧    |                                                                           |

| I <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Current | 1, 2  |       | 90                 | 200                   | μA   | $A_9 = V_{ID}$                                                            |

| V <sub>PPL</sub> | V <sub>PP</sub> during Read-Only<br>Operations   |       | 0.00  |                    | 6.5                   | ٧    | NOTE: Erase/Program are Inhibited when V <sub>PP</sub> = V <sub>PPL</sub> |

| V <sub>PPH</sub> | V <sub>PP</sub> during Read/Write<br>Operations  |       | 11.40 |                    | 12.60                 | ٧    |                                                                           |

| V <sub>LKO</sub> | V <sub>CC</sub> Erase/Write Lock<br>Voltage      |       | 2.5   |                    |                       | ٧    |                                                                           |

- All currents are in RMS unless otherwise noted. Typical values at V<sub>CC</sub> = 5.0 V, V<sub>PP</sub> = 12.0 V, T = 25 °C. These currents are valid for all product versions (packages and speeds).

- 2. Not 100% tested: Characterization data available.

- 3. "Typicals" are not guaranteed, but based on a limited number of samples from production lots.

# 4.6 DC Characteristics—28F010—CMOS Compatible Commercial Products

|                  |                                                                   |       |                          | Limits |                          |      |                                                                                                    |

|------------------|-------------------------------------------------------------------|-------|--------------------------|--------|--------------------------|------|----------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                         | Notes | Min                      | Typ(3) | Max                      | Unit | Test Conditions                                                                                    |

| ILI              | Input Leakage Current                                             | 1     |                          |        | ±1.0                     | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>      |

| I <sub>LO</sub>  | Output Leakage Current                                            | 1     |                          |        | ±10                      | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>OUT</sub> = V <sub>CC</sub> or V <sub>SS</sub>     |

| Iccs             | V <sub>CC</sub> Standby Current                                   | 1     |                          | 50     | 100                      | μА   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE# = V <sub>CC</sub> ±0.2 V                              |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Read Current                               | 1     |                          | 10     | 30                       | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max, CE# = V <sub>IL</sub><br>f = 6 MHz, I <sub>OUT</sub> = 0 mA |

| I <sub>CC2</sub> | V <sub>CC</sub> Programming Current                               | 1, 2  |                          | 1.0    | 10                       | mA   | Programming in Progress                                                                            |

| I <sub>CC3</sub> | V <sub>CC</sub> Erase Current                                     | 1, 2  |                          | 5.0    | 15                       | mA   | Erasure in Progress                                                                                |

| I <sub>CC4</sub> | V <sub>CC</sub> Program Verify<br>Current                         | 1, 2  |                          | 5.0    | 15                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress                                   |

| I <sub>CC5</sub> | V <sub>CC</sub> Erase Verify Current                              | 1, 2  |                          | 5.0    | 15                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                     |

| I <sub>PPS</sub> | V <sub>PP</sub> Leakage Current                                   | 1     |                          |        | ±10                      | μΑ   | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                                  |

| I <sub>PP1</sub> | V <sub>PP</sub> Read Current, ID<br>Current or Standby<br>Current | 1     |                          | 90     | 200                      | μА   | V <sub>PP</sub> > V <sub>CC</sub>                                                                  |

|                  |                                                                   |       |                          |        | ±10                      |      | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                                  |

| I <sub>PP2</sub> | V <sub>PP</sub> Programming Current                               | 1, 2  |                          | 8.0    | 30                       | mA   | V <sub>PP</sub> > = V <sub>PPH</sub><br>Programming in Progress                                    |

| I <sub>PP3</sub> | V <sub>PP</sub> Erase Current                                     | 1, 2  |                          | 6.0    | 30                       | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erasure in Progress                                          |

| I <sub>PP4</sub> | V <sub>PP</sub> Program Verify<br>Current                         | 1, 2  |                          | 2.0    | 5.0                      | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress                                   |

| I <sub>PP5</sub> | V <sub>PP</sub> Erase Verify Current                              | 1, 2  |                          | 2.0    | 5.0                      | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                                     |

| $V_{IL}$         | Input Low Voltage                                                 |       | <b>-</b> 0.5             |        | 0.8                      | ٧    |                                                                                                    |

| V <sub>IH</sub>  | Input High Voltage                                                |       | 0.7<br>V <sub>CC</sub>   |        | V <sub>CC</sub><br>+ 0.5 | V    |                                                                                                    |

| V <sub>OL</sub>  | Output Low Voltage                                                |       |                          |        | 0.45                     | V    | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OL</sub> = 5.8 mA                                  |

| V <sub>OH1</sub> | Output High Voltage                                               |       | 0.85<br>V <sub>CC</sub>  |        |                          | V    | $V_{CC} = V_{CC} Min$<br>$I_{OH} = -2.5 mA$                                                        |

| V <sub>OH2</sub> |                                                                   |       | V <sub>CC</sub><br>- 0.4 |        |                          |      | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OH</sub> = -100 μA                                 |

# 4.6 DC Characteristics—28F010—CMOS Compatible Commercial Products (Continued)

|                  |                                                  |       |       | Limits |       |      |                                                                            |

|------------------|--------------------------------------------------|-------|-------|--------|-------|------|----------------------------------------------------------------------------|

| Symbol           | Parameter                                        | Notes | Min   | Typ(3) | Max   | Unit | Test Conditions                                                            |

| V <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Voltage |       | 11.50 |        | 13.00 | V    |                                                                            |

| I <sub>ID</sub>  | A <sub>9</sub> Intelligent Identifier<br>Current | 1, 2  |       | 90     | 200   | μА   | $A_9 = V_{ID}$                                                             |

| V <sub>PPL</sub> | V <sub>PP</sub> during Read-Only<br>Operations   |       | 0.00  |        | 6.5   | ٧    | NOTE: Erase/Programs are Inhibited when V <sub>PP</sub> = V <sub>PPL</sub> |

| V <sub>PPH</sub> | V <sub>PP</sub> during Read/Write<br>Operations  |       | 11.40 |        | 12.60 | ٧    |                                                                            |

| V <sub>LKO</sub> | V <sub>CC</sub> Erase/Write Lock<br>Voltage      |       | 2.5   |        |       | ٧    |                                                                            |

### NOTES:

Refer to Section 4.4.

# 4.7 DC Characteristics—28F020—CMOS Compatible Commercial Products

|                  |                                           |       |     | Limits |      |      |                                                                                             |

|------------------|-------------------------------------------|-------|-----|--------|------|------|---------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                 | Notes | Min | Typ(3) | Max  | Unit | Test Conditions                                                                             |

| ILI              | Input Leakage Current                     | 1     |     |        | ±1.0 | μA   | $V_{CC} = V_{CC} Max$<br>$V_{IN} = V_{CC} or V_{SS}$                                        |

| ILO              | Output Leakage Current                    | 1     |     |        | ±10  | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max V <sub>OUT</sub> = V <sub>CC</sub> or V <sub>SS</sub> |

| Iccs             | V <sub>CC</sub> Standby Current           | 1     |     | 50     | 100  | μA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE# = V <sub>CC</sub> ±0.2 V                       |

| lcc <sub>1</sub> | V <sub>CC</sub> Active Read Current       | 1     |     | 10     | 30   | mA   | $V_{CC} = V_{CC}$ Max CE# = $V_{IL}$<br>f = 6 MHz,<br>$I_{OUT} = 0$ mA                      |

| I <sub>CC2</sub> | V <sub>CC</sub> Programming<br>Current    | 1, 2  |     | 1.0    | 10   | mA   | Programming in Progress                                                                     |

| I <sub>CC3</sub> | V <sub>CC</sub> Erase Current             | 1, 2  |     | 5.0    | 15   | mA   | Erasure in Progress                                                                         |

| I <sub>CC4</sub> | V <sub>CC</sub> Program Verify<br>Current | 1, 2  |     | 5.0    | 15   | mA   | V <sub>PP</sub> = V <sub>PPH</sub> Program Verify in Progress                               |

| I <sub>CC5</sub> | V <sub>CC</sub> Erase Verify Current      | 1, 2  |     | 5.0    | 15   | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress                              |

| I <sub>PPS</sub> | V <sub>PP</sub> Leakage Current           | 1     | ·   |        | ±10  | μA   | V <sub>PP</sub> ≤ V <sub>CC</sub>                                                           |

# 4.7 DC Characteristics—28F020—CMOS Compatible Commercial Products (Continued)

|                  |                                                                   |       |                          | Limits             |                       |      |                                                                                   |

|------------------|-------------------------------------------------------------------|-------|--------------------------|--------------------|-----------------------|------|-----------------------------------------------------------------------------------|

| Symbol           | Parameter                                                         | Notes | Min                      | Typ <sup>(3)</sup> | Max                   | Unit | Test Conditions                                                                   |

| I <sub>PP1</sub> | V <sub>PP</sub> Read Current,<br>ID Current or Standby<br>Current | 1     |                          | 90                 | 200                   | μА   | VPP > VCC                                                                         |

|                  |                                                                   |       |                          |                    | ±10                   |      | $V_{PP} \leq V_{CC}$                                                              |

| I <sub>PP2</sub> | V <sub>PP</sub> Programming<br>Current                            | 1, 2  |                          | 8                  | 30                    | mA   | $V_{PP} = V_{PPH}$ Programming in Progress                                        |

| I <sub>PP3</sub> | V <sub>PP</sub> Erase Current                                     | 1, 2  |                          | 10                 | 30                    | mA   | V <sub>PP</sub> = V <sub>PPH</sub> Erasure in<br>Progress                         |