# SN5495A, SN54LS95B, SN7495A, SN74LS95B

## 4-Bit Parallel-Access Shift Registers

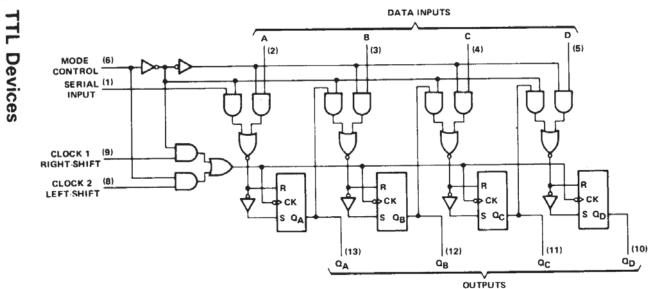

These 4-bit registers feature parallel and serial inputs, parallel outputs, mode control, and two clock inputs. The registers have three modes of operation: Parallel (broadside) load, shift right (the direction  $Q_A$  toward  $Q_D$ ), and shift left (the direction  $Q_D$  toward  $Q_A$ ). Parallel loading is accomplished by applying the four bits of data and taking the mode control input high. The data is loaded into the associated flip-flops and appears at the outputs after the high-to-low transition of the clock-2 input. During loading, the entry of serial data is inhibited.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

#### SN5495A, SN54LS95B, SN7495A, SN74LS95B 4-BIT PARALLEL-ACCESS SHIFT REGISTERS M

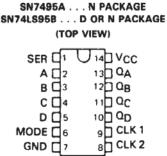

SN5495A, SN54LS95B . . . J OR W PACKAGE

| IARCH | 1974 | _ | REVISED | MARCH | 198 |

|-------|------|---|---------|-------|-----|

|       |      |   |         |       |     |

| TYPE   | TYPICAL MAXIMUM<br>CLOCK FREQUENCY | TYPICAL<br>POWER DISSIPATION |

|--------|------------------------------------|------------------------------|

| '95A   | 36 MHz                             | 195 mW                       |

| 'LS95B | 36 MHz                             | 65 mW                        |

#### description

These 4-bit registers feature parallel and serial inputs, parallel outputs, mode control, and two clock inputs. The registers have three modes of operation:

Parallel (broadside) load Shift right (the direction  $Q_A$  toward  $Q_D$ ) Shift left (the direction QD toward QA)

Parallel loading is accomplished by applying the four bits of data and taking the mode control input high. The data is loaded into the associated flip-flops and appears at the outputs after the high-to-low transition of the clock-2 input. During loading, the entry of serial data is inhibited.

Shift right is accomplished on the high-to-low transition of clock 1 when the mode control is low; shift left is accomplished on the high-to-low transition of clock 2 when the mode control is high by connecting the output of each flip-flop to the parallel input of the previous flip-flop (QD to input C, etc.) and serial data is entered at input D. The clock input may be applied commonly to clock 1 and clock 2 if both modes can be clocked from the same source. Changes at the mode control input should normally be made while both clock inputs are low; however, conditions described in the last three lines of the function table will also ensure that register contents are protected.

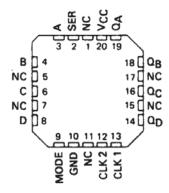

#### SN54LS95B . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

|         | INPUTS      |       |        |          |                 |     |   |     |                | PUTS |     |

|---------|-------------|-------|--------|----------|-----------------|-----|---|-----|----------------|------|-----|

| MODE    | MODE CLOCKS |       |        | PARALLEL |                 |     |   | 0.  | 0-             | 0.0  | 0-  |

| CONTROL | 2 (L)       | 1 (R) | SERIAL | A        | B               | С   | D | QA  | а <sub>в</sub> | ٥c   | ٥D  |

| н       | н           | x     | x      | x        | x               | x   | х | QAO | QB0            | QC0  | QD0 |

| н       | +           | х     | x      | а        | ь               | с   | đ | а   | b              | С    | d   |

| н       | L +         | x     | ×      | QBt      | QC <sup>†</sup> | QDt | d | QBn | QCn            | QDn  | đ   |

| L       | L           | н     | ×      | ×        | х               | ×   | x | QAO | OBO            | QC0  | QDO |

| L       | x           | 4     | н      | x        | ×               | ×   | × | н   | QAn            | QBn  | QCn |

| L       | x           | 4     | ι      | x        | х               | ×   | × | L   | QAn            | QBn  | QCn |

| t       | L           | L     | ×      | x        | x               | x   | × | QAO | QB0            | QCO  | QDO |

| Ļ       | ι           | L     | ×      | x        | x               | x   | x | QA0 | QB0            | QC0  | QDO |

| ŧ       | L           | н     | ×      | ×        | x               | ×   | × | QA0 | QBO            | QCO  | QDO |

| t       | н           | L     | ×      | x        | x               | x   | x | QAO | QB0            | QCO  | QDO |

| t       | н           | н     | x      | ×        | ×               | x   | × | QAO | QB0            | QC0  | QDO |

FUNCTION TABLE

<sup>†</sup>Shifting left requires external connection of  $\Omega_B$  to A,  $\Omega_C$  to B, and  $\Omega_D$  to C. Serial data is entered at input D. H = high level (steady state), L = low level (steady state), X = irrelevant (any input, including transitions)

1 = transition from high to low level, 1 = transition from low to high level

a, b, c, d = the level of steady state input at inputs A, B, C, or D, respectively.

QA0, QB0, QC0, QD0 = the level of QA, QB, QC, or QD, respectively, before the indicated steady-state input conditions were established.

QAn, QBn, QCn, QDn = the level of QA, QB, QC, or QD, respectively, before the most-recent 4 transition of the clock.

**PRODUCTION DATA documents contain information** current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

**ITL Devices**

## SN5495A, SN54LS95B, SN7495A, SN74LS95B 4-BIT PARALLEL-ACCESS SHIFT REGISTERS

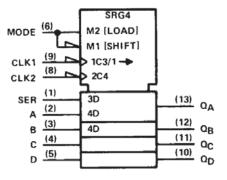

logic symbol<sup>†</sup>

2

ł

$^\dagger$  This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for D, J, N, and W packages.

## SN5495A, SN54LS95B, SN7495A, SN74LS95G 4-BIT PARALLEL-ACCESS SHIFT REGISTERS

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                      | SN54' | SN54LS' | SN74' | SN74LS' | UNIT |

|--------------------------------------|-------|---------|-------|---------|------|

| Supply voltage, VCC (see Note 1)     | 7     | 7       | 7     | 7       | V    |

| Input voltage                        | 5.5   | 7       | 5.5   | 7       | V    |

| Interemitter voltage (see Note 2)    | 5.5   |         | 5.5   |         | V    |

| Operating free-air temperature range | - 55  | to 125  | 0     | 0 to 70 |      |

| Storge temperature range             | - 65  | to 150  | °C    |         |      |

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor. This rating applies between the clock-2 input and the mode control input of the '95A.

## SN5495A, SN7495A **4-BIT PARALLEL-SHIFT REGISTERS**

## recommended operating conditions

|                                                                          |     | SN5495A |      |          | SN7495A |      |      |  |

|--------------------------------------------------------------------------|-----|---------|------|----------|---------|------|------|--|

|                                                                          | MIN | NOM     | MAX  | MIN      | NOM     | MAX  | UNIT |  |

|                                                                          | 4.5 | 5       | 5.5  | 4.75     | 5       | 5.25 | V    |  |

| Supply voltage, VCC                                                      |     |         | -800 |          |         | -800 | μA   |  |

| High-level output current, IOH                                           |     |         |      | <u> </u> |         | 16   | mA   |  |

| Low-level output current, IOL                                            |     |         | 16   | <u> </u> |         | 25   | MHz  |  |

| Clock frequency, fclock                                                  | 0   |         | 25   | 0        |         | 25   |      |  |

| Width of clock pulse, tw(clock) (See Figure 1)                           | 20  |         |      | 20       |         |      | ns   |  |

| Setup time, high-level or low-level data, t <sub>su</sub> (See Figure 1) | 15  |         |      | 15       |         |      | ns   |  |

| Hold time, high-level or low-level data, th (See Figure 1)               | 0   |         |      | 0        |         |      | ns   |  |

| Time to enable clock 1, tenable 1 (See Figure 2)                         | 15  |         |      | 15       |         |      | ns   |  |

| Time to enable clock 1, tenable 1, (cost 1, gate da                      | 15  |         |      | 15       |         |      | ns   |  |

| Time to enable clock 2 (See Figure 2)                                    | 5   |         |      | 5        |         |      | ns   |  |

| Time to inhibit clock 1, tinhibit 1 (See Figure 2)                       |     |         |      | 5        |         |      | ns   |  |

| Time to inhibit clock 2, tinhibit 2 (See Figure 2)                       |     |         | 105  |          |         | 70   | °c   |  |

| Operating free-air temperature, TA                                       | -55 | _       | 125  | 0        |         | /0   | L_~  |  |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                          |                              |                                                                                                   | 1                | N5495 | A    | SN7495A |     |       | UNIT  |

|-----------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------|------------------|-------|------|---------|-----|-------|-------|

| PARAMETER |                          | TEST CONDITIONS <sup>†</sup> |                                                                                                   | TYP <sup>‡</sup> | MAX   | MIN  | TYP‡    | MAX | 0.411 |       |

|           |                          |                              |                                                                                                   | 2                |       |      | 2       |     |       | v_    |

| VIH       | High-level input voltage |                              |                                                                                                   |                  |       | 0.8  |         |     | 0.8   | V     |

| VIL       | Low-level input voltage  |                              | Vcc = MIN, 11 = -12 mA                                                                            | <u>+</u>         |       | -1.5 |         |     | -1.5  | V     |

| Vik       | Input clamp voltage      |                              |                                                                                                   | +                |       |      |         |     |       |       |

|           |                          |                              | $V_{CC} = MIN, V_{IH} = 2V,$                                                                      | 2.4              | 3.4   |      | 2.4     | 3.4 |       | V     |

| ∨он       | High-level output voltag | e                            | VIL = 0.8 V, 10H = -800 µA                                                                        |                  |       |      |         |     |       |       |

|           |                          |                              | V <sub>CC</sub> = MIN, V <sub>1H</sub> = 2 V,<br>V <sub>1L</sub> = 0.8 V, I <sub>OL</sub> = 16 mA |                  | 0.2   | 0.4  | ļ       | 0.2 | 0.4   | V V   |

| Vol       | Low-level output voltag  | e                            |                                                                                                   |                  | 0.2   |      |         |     |       |       |

|           | Input current at         | ·                            | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V                                                     |                  |       | 1    | 1       |     | 1     | mA    |

| կ         | maximum input voltage    |                              | +CC                                                                                               |                  |       |      |         |     |       | +     |

|           |                          | Serial, A, B, C, D,          |                                                                                                   |                  |       | 40   |         |     | 40    | μΑ    |

| Чн        | High-level               | Clock 1 or 2                 | V <sub>CC</sub> = MAX, V <sub>1</sub> = 2.4 V                                                     |                  |       |      |         |     |       | - i - |

| .14       | input current            | Mode control                 | ]                                                                                                 |                  |       | 80   |         |     | 80    | +     |

|           |                          | Serial, A, B, C, D,          |                                                                                                   |                  |       | 1.6  |         |     | -1.6  |       |

| ЧL        | Low-level                | Clock 1 or 2                 | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V                                                     | L                |       |      |         |     |       | ^ mA  |

|           | input current            | Mode control                 |                                                                                                   |                  |       | -3.2 | +       |     | -3.2  |       |

| los       | Short-circuit output cu  | rrent§                       | V <sub>CC</sub> = MAX                                                                             | 18               |       | -57  | -18     |     | 57    | _     |

| 1cc       | Supply current           |                              | VCC = MAX, See Note 3                                                                             |                  | 39    | 63   |         | 39  | 63    | mA    |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25 °C$ .

§ Not more than one output should be shorted at a time.

NOTE 3: ICC is measured with all outputs and serial input open; A, B, C, and D inputs grounded; mode control at 4.5 V; and a momentary 3 V, then ground, applied to both clock inputs.

## switching characteristics, VCC = 5 V, TA = $25^{\circ}$ C

| PARAMETER                                                        | TEST CONDITION               | S MIN  | TYP | MAX | UNIT |

|------------------------------------------------------------------|------------------------------|--------|-----|-----|------|

| fmay Maximum clock frequency                                     |                              | 25     | 36  |     | MHz  |

| They are a service and a service high level output from clock    | $C_{L} = 15  pF, R_{L} = 40$ | 0 \$2, | 18  | 27  | ns   |

| tPLH Propagation delay time, high-to-low-level output from clock | See Figure 1                 |        | 21  | 32  | ns   |

2

**TTL Devices**

### recommended operating conditions

|                                                              | SI  | SN54LS95B |      | SN74LS95B |     |      |     |

|--------------------------------------------------------------|-----|-----------|------|-----------|-----|------|-----|

|                                                              | MIN | NOM       | MAX  | MIN       | NOM | MAX  |     |

| Supply voltage, V <sub>CC</sub>                              | 4.5 | 5         | 5.5  | 4.75      | 5   | 5.25 | V   |

| High-level output current, IOH                               |     |           | -400 |           |     | -400 | μA  |

| Low-level output current, IOL                                |     |           | 4    |           |     | 8    | mA  |

| Clock frequency, fclock                                      | 0   |           | 25   | 0         |     | 25   | MHz |

| Width of clock pulse, tw(clock) (see Figure 1)               | 20  |           |      | 20        |     |      | ns  |

| Setup time, high-level or low-level data, tsu (see Figure 1) | 20  |           |      | 20        |     |      | ns  |

| Hold time, high-level or low-level data, th (see Figure 1)   | 20  |           |      | 10        |     |      | ns  |

| Time to enable clock 1, tenable 1 (see Figure 2)             | 20  |           |      | 20        |     |      | ns  |

| Time to enable clock 2, tenable 2 (see Figure 2)             | 20  |           |      | 20        |     |      | ns  |

| Time to inhibit clock 1, tinhibit 1 (see Figure 2)           | 20  |           |      | 20        |     |      | ns  |

| Time to inhibit clock 2, tinhibit 2 (see Figure 2)           | 20  |           |      | 20        |     | -    | ns  |

| Operating free-air temperature, TA                           | -55 |           | 125  | 0         |     | 70   | °c  |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                                 | TEST CO                                          |                                                     | SI  | V54LS9 | 58   | S   |      |      |      |

|-----------------|-------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----|--------|------|-----|------|------|------|

|                 | PARAMETER                                 | TEST CO                                          | NDITIONS'                                           | MIN | TYP‡   | MAX  | MIN | TYP‡ | MAX  | UNIT |

| $V_{IH}$        | High-level input voltage                  |                                                  |                                                     | 2   |        |      | 2   |      |      | V    |

| VIL             | Low-level input voltage                   |                                                  | · · · · · · · · · · · · · · · · · · ·               |     |        | 0.7  |     |      | 0.8  | V    |

| VIK             | Input clamp voltage                       | V <sub>CC</sub> = MIN,                           | I₁'= −18 mA                                         |     |        | -1.5 | 1   |      | -1.5 | V    |

| v <sub>он</sub> | High-level output voltage                 | V <sub>CC</sub> = MIN,<br>VIL ≍ VIL max,         | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -400 µA | 2.5 | 3.4    |      | 2.7 | 3.4  |      | v    |

| Voi             | Low-level output voltage                  | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = 2 V, | IOL = 4 mA                                          |     | 0.25   | 0.4  |     | 0.25 | 0.4  |      |

| VOL             | Low-rever output vortage                  | VIL = VIL max                                    | I <sub>OL</sub> = 8 mA                              |     |        |      |     | 0.35 | 0.5  | ľ    |

| II.             | Input current at<br>maximum input voltage | V <sub>CC</sub> = MAX,                           | V <sub>1</sub> = 7 V                                |     |        | 0.1  |     |      | 0.1  | mA   |

| ŧн              | High-level                                | V <sub>CC</sub> = MAX,                           | V <sub>I</sub> = 2.7 V                              |     |        | 20   |     |      | 20   | μA   |

| 46              | Low-level input current                   | V <sub>CC</sub> = MAX,                           | V <sub>I</sub> = 0.4 V                              |     |        | -0.4 |     |      | 0.4  | mA   |

| los             | Short-circuit output current §            | V <sub>CC</sub> = MAX                            |                                                     | -20 |        | -100 | 20  |      | -100 | mA   |

| 1CC             | Supply current                            | $V_{CC} = MAX,$                                  | See Note 3                                          |     | 13     | 21   |     | 13   | 21   | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>5</sup> Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second. NOTE 3: I<sub>CC</sub> is measured with all outputs and serial input open; A, B, C, and D inputs grounded; mode control at 4.5 V; and a momentary 3 V,

then ground, applied to both clock inputs.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$

| PARAMETER                                                        | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| fmax Maximum clock frequency                                     | $C_{L} = 15  pF$ , $R_{L} = 2  k\Omega$ , | 25  | 36  |     | MHz  |

| tPLH Propagation delay time, low-to-high-level output from clock | See Figure 1                              |     | 18  | 27  | ns   |

| tPHL Propagation delay time, high-to-low-level output from clock | oee rigure r                              |     | 21  | 32  | ns   |

÷

TTL Devices

## SN5495A, SN54LS95B, SN7495A, SN74LS95B 4-BIT PARALLEL-ACCESS SHIFT REGISTERS

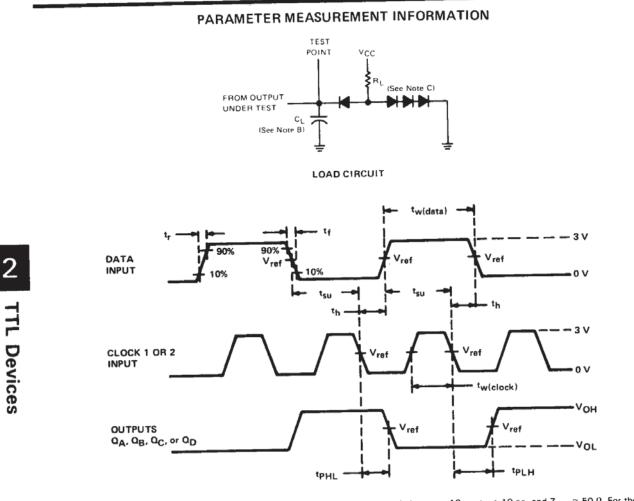

NOTES: A. Input pulses are supplied by a generator having the following characteristics:  $t_f \le 10 \text{ ns}$ ,  $t_f \le 10 \text{ ns}$ , and  $Z_{out} \approx 50 \Omega$ . For the data pulse generator, PRR = 500 kHz; for the clock pulse generator, PRR = 1 MHz. When testing  $f_{max}$ , vary PRR. For '95A,  $t_w(data) \ge 20 \text{ ns}$ ,  $t_w(clock) \ge 15 \text{ ns}$ .

- B. CL includes probe and jig capacitance.

- C. All diodes are 1N3064 equivalent.

- D. For '95A,  $V_{ref}$  = 1.5 V; for 'LS95B,  $V_{ref}$  = 1.3 V.

#### VOLTAGE WAVEFORMS FIGURE 1-SWITCHING TIMES

### PARAMETER MEASUREMENT INFORMATION

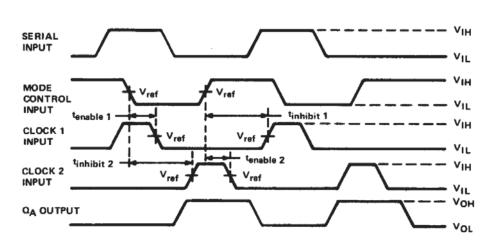

NOTES: A. Input is at a low level.

B. For '95A,  $V_{ref}$  = 1.5 V; for 'LS958,  $V_{ref}$  = 1.3 V.

VOLTAGE WAVEFORMS FIGURE 2-CLOCK ENABLE/INHIBIT TIMES