# 8291A

# **GPIB** Talker/Listener

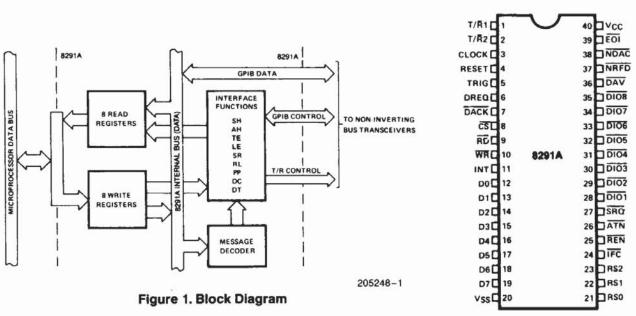

The 8291A is an enhanced version of the 8291 GPIB Talker/Listener designed to interface microprocessors to an IEEE Standard 488 Instrumentation Interface Bus. It implements all of the Standard's interface functions except for the controller. The controller function can be added with the 8292 GPIB Controller, and the 8293 GPIB Transceiver performs the electrical interface for Talker/Listener and Talker/Listener/Controller configurations.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# int<sub>el</sub>.

# 8291A GPIB TALKER/LISTENER

- Designed to Interface Microprocessors (e.g., 8048/49, 8051, 8080/85, 8086/88) to an IEEE Standard 488 Digital Interface Bus

- Programmable Data Transfer Rate

- Complete Source and Acceptor Handshake

- Complete Talker and Listener Functions with Extended Addressing

- Service Request, Parallel Poll, Device Clear, Device Trigger, Remote/Local Functions

- Selectable Interrupts

- On-Chip Primary and Secondary Address Recognition

- Automatic Handling of Addressing and Handshake Protocol

- Provision for Software Implementation of Additional Features

- 1-8 MHz Clock Range

- 16 Registers (8 Read, 8 Write), 2 for Data Transfer, the Rest for Interface Function Control, Status, etc.

- Directly Interfaces to External Non-Inverting Tranceivers for Connection to the GPIB

- Provides Three Addressing Modes, Allowing the Chip to be Addressed Either as a Major or a Minor Talker/ Listener with Primary or Secondary Addressing

- DMA Handshake Provision Allows for Bus Transfers without CPU Intervention

- Trigger Output Pin

- On-Chip EOS (End of Sequence) Message Recognition Facilitates Handling of Multi-Byte Transfers

The 8291A is an enhanced version of the 8291 GPIB Talker/Listener designed to interface microprocessors to an IEEE Standard 488 Instrumentation Interface Bus. It implements all of the Standard's interface functions except for the controller. The controller function can be added with the 8292 GPIB Controller, and the 8293 GPIB Transceiver performs the electrical interface for Talker/Listener and Talker/Listener/Controller configurations.

205248-2

3

Figure 2. Pin Configuration

## 8291A FEATURES AND IMPROVEMENTS

The 8291A is an improved design of the 8291 GPIB Talker/Listener. Most of the functions are identical to the 8291, and the pin configuration is unchanged.

The 8291A offers the following improvements to the 8291:

- 1. EOI is active with the data as a ninth data bit rather than as a control bit. This is to comply with some additions to the 1975 IEEE-488 Standard incorporated in the 1978 Standard.

- 2. The BO interrupt is not asserted until RFD is true. If the Controller asserts ATN synchronously, the data is guaranteed to be transmitted. If the Controller asserts ATN asynchronously, the SH (Source Handshake) will return to SIDS (Source idle State), and the output data will be cleared. Then, if ATN is released while the 8291A is addressed to talk, a new BO interrupt will be generated. This change fixes 8291 problems which caused data to be lost or repeated and a problem with the RQS bit (sometimes cannot be asserted while talking).

- 3. LLOC and REMC interrupts are setting flipflops rather than toggling flipflops in the interrupt backup register. This ensures that the CPU knows that these state changes have occurred. The actual state can be determined by checking the LLO and REM status bits in the upper nibble of the Interrupt Status 2 Register.

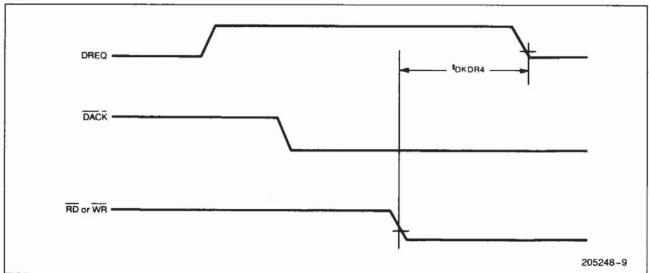

- DREQ is cleared by DACK (RD + WR). DREQ on the 8291 was cleared only by DACK which is not compatible with the 8089 I/O Processor.

- 5. The INT bit in Interrupt Status 2 Register is duplicated in bit 7 of the Address 0 Register. If software polling is used to check for an interrupt, INT in the Address 0 Register should be polled rather than the Interrupt Status 2 Register. This ensures that no interrupts are lost due to asynchronous status reads and interrupts.

- The 8291A's Send EOI Auxiliary Command works on any byte including the first byte of a message. The 8291 did not assert EOI after this command for a one byte message nor on two consecutive bytes.

- To avoid confusion between holdoff on DAV versus RFD if a device is readdressed from a talker

to a listener role or vice-versa during a holdoff, the "Holdoff on Source Handshake" has been eliminated. Only "Holdoff on Acceptor Handshake" is available.

- 8. The rsv local message is cleared automatically upon exit from SPAS if (APRS:STRS:SPAS) occurred. The automatic resetting of the bit after the serial poll is complete simplifies the service request software.

- 9. The SPASC interrupt on the 8291 has been replaced by the SPC (Serial Poll Complete) interrupt on the 8291A. SPC interrupt is set on exit from SPAS if APRS:STRS:SPAS occurred, indicating that the controller has read the bus status byte after the 8291A requested service. The SPASC interrupt was ambiguous because a controller could enter SPAS and exit SPAS generating two SPASC interrupts without reading the serial poll status byte. The SPC interrupt also simplifies the CPU's software by eliminating the interrupt when the serial poll is half way done.

- The rtl Auxiliary Command in the 8291 has been replaced by Set and Clear rtl Commands in the 8291A. Using the new commands, the CPU has the flexibility to extend the length of local mode or leave it as a short pulse as in the 8291.

- A holdoff RFD on GET, SDC, and DCL feature has been added to prevent additional bus activity while the CPU is responding to any of these commands. The feature is enabled by a new bit (B<sub>4</sub>) in the Auxiliary Register B.

- On the 8291, BO could cease to occur upon IFC going false if IFC occurred asynchronously. On the 8291A, BO continues to occur after IFC has gone false even if it arrived asynchronously.

- 13. User's software can distinguish between the 8291 and the 8291A as follows:

- a) pon (00H to register 5)

- b) RESET (02H to register 5)

- c) Read Interrupt Status 1 Register. If BO interrupt is set, the device is the 8291. If BO is clear, it is the 8291A.

This can be used to set a flag in the user's software which will permit special routines to be executed for each device. It could be included as part of a normal initialization procedure as the first step after a chip reset.

### **Table 1. Pin Description**

| Symbol                             | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                        |  |  |  |

|------------------------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D <sub>0</sub> -D <sub>7</sub>     | · 12–19    | 1/0  | DATA BUS PORT: To be connected to microprocessor data<br>bus.                                                                                                                                                                            |  |  |  |

| RS <sub>0</sub> -RS <sub>2</sub>   | 21–23      | I    | <b>REGISTER SELECT:</b> Inputs, to be connected to three<br>nonmultiplexed microprocessor address bus lines. Select<br>which of the 8 internal read (write) registers will be read from<br>(written into) with the execution of RD (WR). |  |  |  |

| CS                                 | 8          | 1    | CHIP SELECT: When low, enables reading from or writing into the register selected by RS <sub>0</sub> -RS <sub>2</sub> .                                                                                                                  |  |  |  |

| RD                                 | 9          | 1    | <b>READ STROBE:</b> When low with CS or DACK low, selected register contents are read.                                                                                                                                                   |  |  |  |

| WR                                 | 10         | . 1  | WRITE STROBE: When low with CS or DACK low, data is written into the selected register.                                                                                                                                                  |  |  |  |

| INT (ÎNT)                          | 11         | 0    | <b>INTERRUPT REQUEST:</b> To the microprocessor, set high for request and cleared when the appropriate register is accessed by the CPU. May be software configured to be active low.                                                     |  |  |  |

| DREQ                               | 6          | 0    | <b>DMA REQUEST:</b> Normally low, set high to indicate byte output or byte input in DMA mode; reset by DACK.                                                                                                                             |  |  |  |

| DACK                               | 7          | 1    | DMA ACKNOWLEDGE: When low, resets DREQ and selects<br>data in/data out register for DMA data transfer (actual transfer<br>done by RD/WR pulse).<br>Must be high if DMA is not used.                                                      |  |  |  |

| TRIG                               | 5          | 0    | <b>TRIGGER OUTPUT:</b> Normally low; generates a triggering pulse with 1 $\mu$ sec min. width in response to the GET bus command or Trigger auxiliary command.                                                                           |  |  |  |

| CLOCK                              | 3          | 1    | EXTERNAL CLOCK: Input, used only for T, delay generator.<br>May be any speed in 1-8 MHz range.                                                                                                                                           |  |  |  |

| RESET                              | 4          | I    | <b>RESET INPUT:</b> When high, forces the device into an "idle" (initialization) mode. The device will remain at "idle" until released by the microprocessor, with the "Immediate Execute pon" local message.                            |  |  |  |

| DIO <sub>1</sub> -DIO <sub>8</sub> | 28–35      | 1/0  | 8-BIT GPIB DATA PORT: Used for bidirectional data byte<br>transfer between 8291A and GPIB via non-inverting external<br>line transceivers.                                                                                               |  |  |  |

| DAV                                | 36         | 1/0  | <b>DATA VALID:</b> GPIB handshake control line. Indicates the availability and validity of information on the $\overline{DIO}_1 - \overline{DIO}_8$ and $\overline{EOI}$ lines.                                                          |  |  |  |

| NRFD                               | 37         | 1/0  | NOT READY FOR DATA: GPIB handshake control line.<br>Indicates the condition of readiness of device(s) connected to<br>the bus to accept data.                                                                                            |  |  |  |

| NDAC                               | 38         | 1/0  | <b>NOT DATA ACCEPTED:</b> GPIB handshake control line.<br>Indicates the condition of acceptance of data by the device(s connected to the bus.                                                                                            |  |  |  |

| ATN                                | 26         | 1    | ATTENTION: GPIB command line. Specifies how data on DIC lines are to be interpreted.                                                                                                                                                     |  |  |  |

3

| Table 1. Pin Description (Cont | inued) |

|--------------------------------|--------|

|--------------------------------|--------|

| Symbol          | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IFC             | 24 1       |      | INTERFACE CLEAR: GPIB command line. Places the<br>interface functions in a known quiescent state.                                                                                                                                                                                                                                                                                                                                         |  |

| SRQ             | 27         | 0    | SERVICE REQUEST: GPIB command line. Indicates the need<br>for attention and requests an interruption of the current<br>sequence of events on the GPIB.                                                                                                                                                                                                                                                                                    |  |

| REN             | 25         | 1    | <b>REMOTE ENABLE:</b> GPIB command line. Selects (in conjunction with other messages) remote or local control of the device.                                                                                                                                                                                                                                                                                                              |  |

| EOI             | 39         | 1/0  | <b>END OR IDENTITY:</b> GPIB command line. Indicates the end<br>a multiple byte transfer sequence or, in conjunction with $\overline{AT}$<br>addresses the device during a polling sequence.                                                                                                                                                                                                                                              |  |

| T/R1            | 1          | 0    | <b>EXTERNAL TRANSCEIVERS CONTROL LINE:</b> Set high t<br>indicate output data/signals on the $\overline{DIO_1}$ - $\overline{DIO_8}$ and $\overline{DAV}$ li<br>and input signals on the NRFD and NDAC lines (active sou<br>handshake). Set low to indicate input data/signals on the<br>$\overline{DIO_1}$ - $\overline{DIO_8}$ and $\overline{DAV}$ lines and output signals on the NRFD<br>and NDAC lines (active acceptor handshake). |  |

| T/R2            | 2          | 0    | EXTERNAL TRANSCEIVERS CONTROL LINE: Set to<br>indicate output signals on the EOI line. Set low to indicate<br>expected input signal on the EOI line during parallel poll.                                                                                                                                                                                                                                                                 |  |

| V <sub>CC</sub> | 40         | P.S. | POSITIVE POWER SUPPLY: (5V ±10%).                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| GND             | 20         | P.S. | CIRCUIT GROUND POTENTIAL.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

#### NOTE:

All signals on the 8291A pins are specified with positive logic. However, IEEE 488 specifies negative logic on its 16 signal lines. Thus, the data is inverted once from  $D_0 - D_7$  to  $\overline{DIO}_0 - \overline{DIO}_8$  and non-inverting bus transceivers should be used.

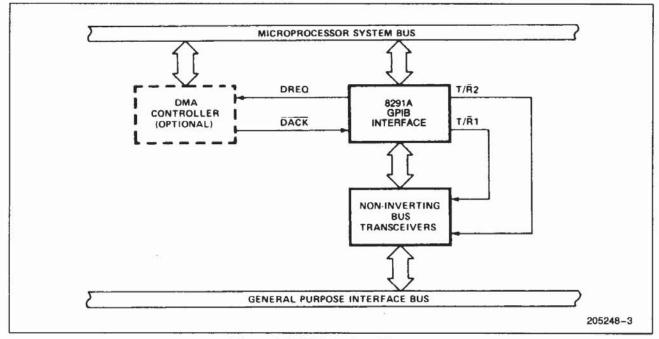

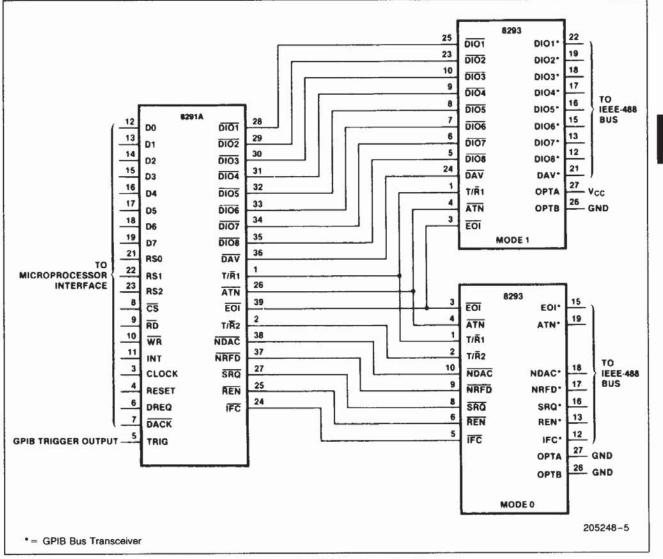

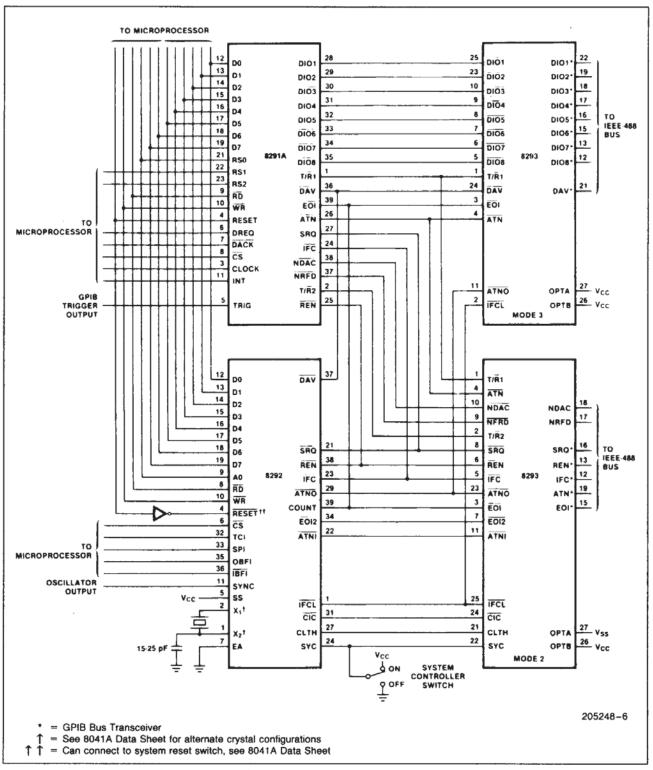

Figure 3. 8291A System Diagram

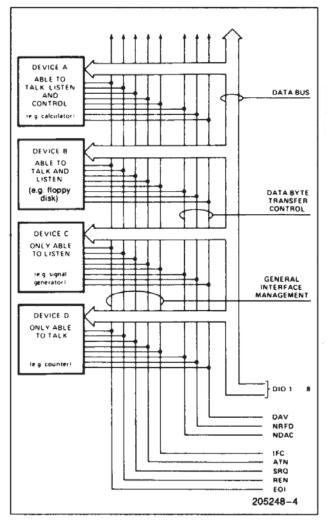

# THE GENERAL PURPOSE INTERFACE BUS (GPIB)

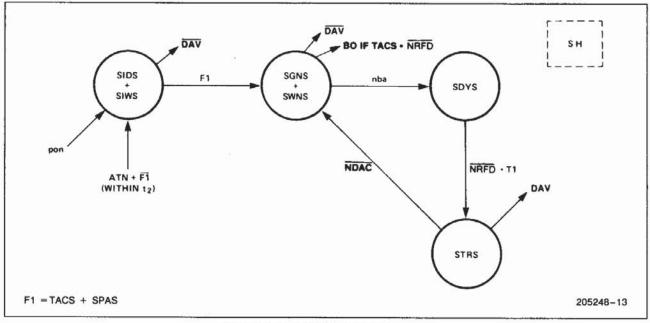

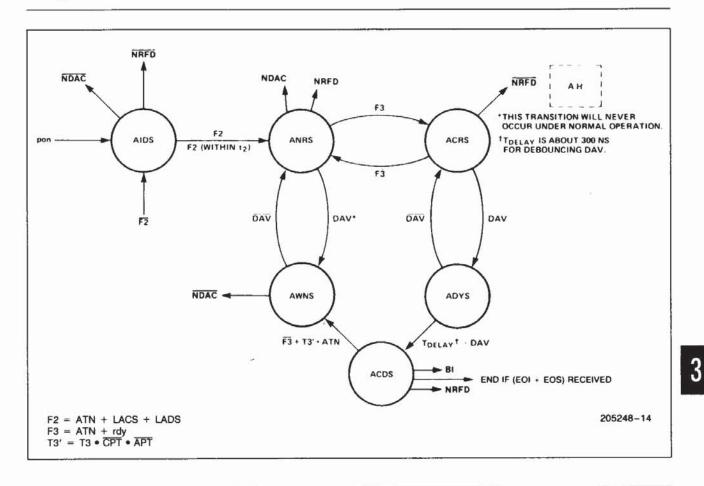

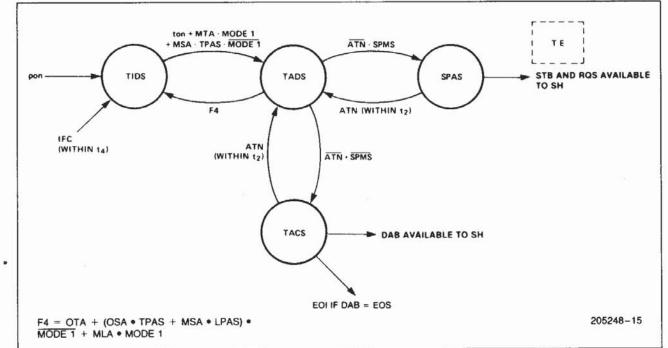

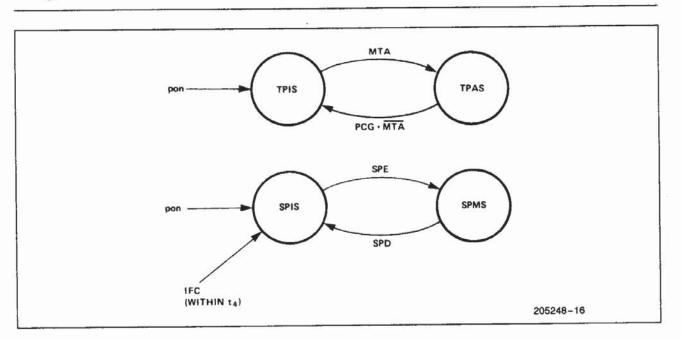

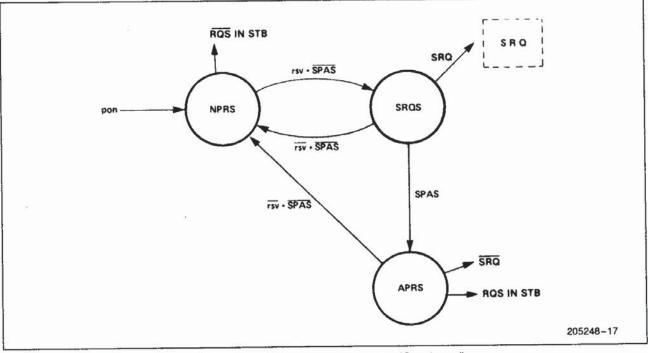

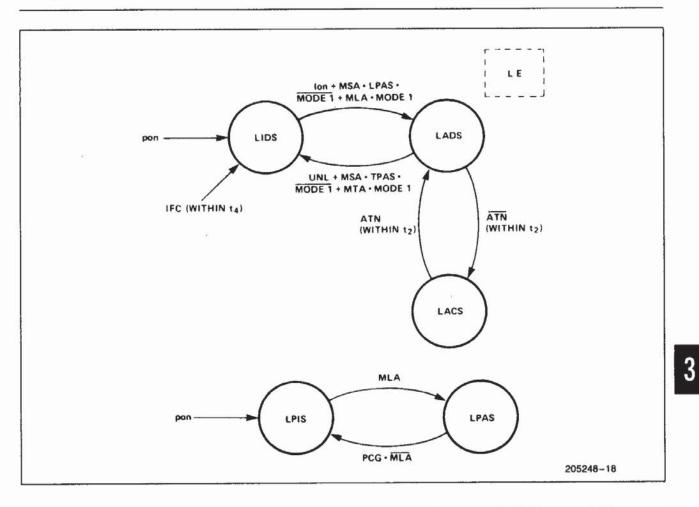

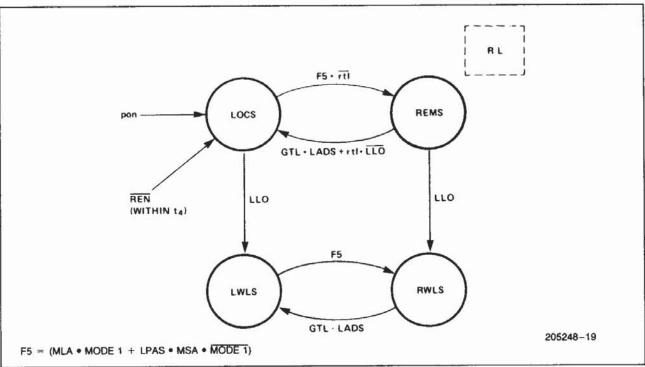

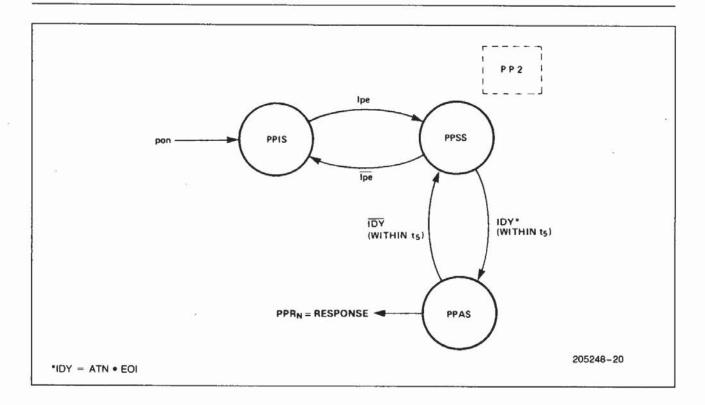

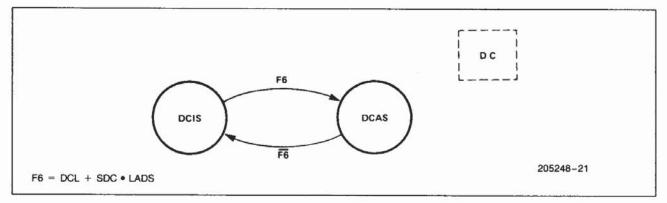

The General Purpose Interface Bus (GPIB) is defined in the IEEE Standard 488-1978 "Digital Interface for Programmable Instrumentation." Although a knowledge of this standard is assumed, Figure 4 provides the bus structure for quick reference. Also, Tables 2 and 3 reference the interface state mnemonics and the interface messages respectively. Modified state diagrams for the 8291A are presented in Appendix A.

# **General Description**

The 8291A is a microprocessor-controlled device designed to interface microprocessors, e.g., 8048/49, 8051, 8080/85, 8086/88 to the GPIB. It implements all of the interface functions defined in the IEEE-488 Standard except for the controller function. If an implementation of the Standard's Controller is desired, it can be connected with an Intel® 8292 to form a complete interface.

The 8291A handles communication between a microprocessor-controlled device and the GPIB. Its capabilities include data transfer, handshake protocol, talker/listener addressing procedures, device clearing and triggering, service request, and both serial and parallel polling. In most procedures, it does not disturb the microprocessor unless a byte has arrived (input buffer full) or has to be sent out (output buffer empty).

The 8291A architecture includes 16 registers. Eight of these registers may be written into by the microprocessor. The other eight registers may be read by the microprocessor. One each of these read and write registers is for direct data transfers. The rest of the write registers control the various features of the chip, while the rest of the read registers provide the microprocessor with a monitor of GPIB states, various bus conditions, and device conditions.

# **GPIB Addressing**

Each device connected to the GPIB must have at least one address whereby the controller device in charge of the bus can configure it to talk, listen, or send status. An 8291A implementation of the GPIB offers the user three alternative addressing modes for which the device can be initialized for each application. The first of these modes allows for the device to have two separate primary addresses. The second mode allows the user to implement a single talker/listener with a two byte address (primary address + secondary address). The third mode again allows for two distinct addresses but in this instance, they can each have a ten-bit address (5 low-order bits of each of two bytes). However, this mode requires that the secondary addresses be passed to the microprocessor for verification. These three addressing schemes are described in more detail in the discussion of the Address Registers.

3

Figure 4. Interface Capabilities and Bus Structure

| Mnemonic | State Represented                      | Mnemonic | State Represented                      |

|----------|----------------------------------------|----------|----------------------------------------|

| ACDS     | Accept Data State                      | PPSS     | Parallel Poll Standby State            |

| ACRS     | Acceptor Ready State                   | PUCS     | Parallel Poll Unaddressed to Configure |

| AIDS     | Acceptor Idle State                    |          | State                                  |

| ANRS     | Acceptor Not Ready State               | REMS     | Remote State                           |

| APRS     | Affirmative Poll Response State        | RWLS     | Remote With Lockout State              |

| AWNS     | Acceptor Wait for New Cycle State      | SACS     | System Control Active State            |

| CACS     | Controller Active State                | SDYS     | Source Delay State                     |

| CADS     | Controller Addressed State             | SGNS     | Source Generate State                  |

| CAWS     | Controller Active Wait State           | SIAS     | System Control Interface Clear Active  |

| CIDS     | Controller Idle State                  |          | State                                  |

| CPPS     | Controller Parallell Poll State        | SIDS     | Source Idle State                      |

| CPWS     | Controller Parallel Poll Wait State    | SIIS     | System Control Interface Clear Idle    |

| CSBS     | Controller Standby State               |          | State                                  |

| CSNS     | Controller Service Not Requested State | SINS     | System Control Interface Clear Not     |

| CSRS     | Controller Service Requested State     |          | Active State                           |

| CSWS     | Controller Synchronous Wait State      | SIWS     | Source Idle Wait State                 |

| CTRS     | Controller Transfer State              | SNAS     | System Control Not Active State        |

| DCAS     | Device Clear Active State              | SPAS     | Serial Poll Active State               |

| DCIS     | Device Clear Idle State                | SPIS     | Serial Poll Idle State                 |

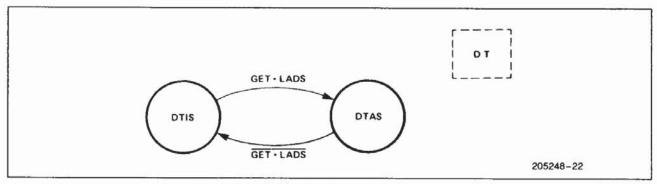

| DTAS     | Device Trigger Active State            | SPMS     | Serial Poll Mode State                 |

| DTIS     | Device Trigger Idle State              | SRAS     | System Control Remote Enable Active    |

| LACS     | Listener Active State                  |          | State                                  |

| LADS     | Listener Addressed State               | SRIS     | System Control Remote Enable Idle      |

| LIDS     | Listener Idle State                    |          | State                                  |

| LOCS     | Local State                            | SRNS     | System Control Remote Enable Not       |

| LPAS     | Listener Primary Addressed State       |          | Active State                           |

| LPIS     | Listener Primary Idle State            | SRQS     | Service Request State                  |

| LWLS     | Local With Lockout State               | STRS     | Source Transfer State                  |

| NPRS     | Negative Poll Response State           | SWNS     | Source Wait for New Cycle State        |

| PACS     | Parallel Poll Addressed to Configure   | TACS     | Talker Active State                    |

|          | State                                  | TADS     | Talker Addressed State                 |

| PPAS     | Parallel Poll Active State             | TIDS     | Talker Idle State                      |

| PPIS     | Parallel Poll Idle State               | TPIS     | Talker Primary Idle State              |

| Table 2. | <b>IEEE 488</b> | Interface State | Mnemonics |

|----------|-----------------|-----------------|-----------|

|----------|-----------------|-----------------|-----------|

The Controller function is implemented on the Intel® 8292.

| Table 3. IEEE | 488 Interface | Message | Reference List |

|---------------|---------------|---------|----------------|

|---------------|---------------|---------|----------------|

| Mnemonic           | Message                              | Interface Function(s)               |

|--------------------|--------------------------------------|-------------------------------------|

| LOCAL MESSAG       | ES RECEIVED (By Interface Functions) |                                     |

| gts(1)             | go to standby                        | С                                   |

| ist                | individual status                    | PP                                  |

| lon                | listen only                          | L, LE                               |

| lpe                | local poll enable                    | PP                                  |

| nba                | new byte available                   | SH                                  |

| pon                | power on                             | SH, AH, T, TE, L, LE, SR, RL, PP, C |

| rdy                | ready                                | АН                                  |

| rpp(1)             | request parallel poll                | С                                   |

| rsc(1)             | request system control               | C                                   |

| rsv                | request service                      | SR                                  |

| rtl                | return to local                      | RL                                  |

| sic(1)             | send interface clear                 | С                                   |

| sre(1)             | send remote enable                   | С                                   |

| tca <sup>(1)</sup> | take control asynchronously          | С                                   |

| Mnemonic            | Message                    | Interface Function(s)       |

|---------------------|----------------------------|-----------------------------|

| tcs(1)              | take control synchronously | AH, C                       |

| ton                 | talk only                  | T, TE                       |

| REMOTE MESSAGE      | ES RECEIVED                |                             |

| ATN                 | Attention                  | SH, AH, T, TE, L, LE, PP, C |

| DAB                 | Data Byte                  | (Via L, LE)                 |

| DAC                 | Data Accepted              | SH                          |

| DAV                 | Data Valid                 | AH                          |

| DCL                 | Device Clear               | DC                          |

| END                 | End                        | (via L, LE)                 |

| GET                 | Group Execute Trigger      | DT                          |

| GTL                 | Go to Local                | RL                          |

| IDY                 | Identify                   | L, LE, PP                   |

| IFC                 | Interface Clear            | T, TE, L, LE, C             |

| LLO                 | Local Lockout              | RL                          |

|                     | My Listen Address          | L, LE, RL, T, TE            |

| MLA                 | -                          | TE, LE, RL                  |

| MSA                 | My Secondary Address       |                             |

| MTA                 | My Talk Address            | T, TE, L, LE                |

| OSA                 | Other Secondary Address    | TE                          |

| ΟΤΑ                 | Other Talk Address         | T, TE                       |

| PCG                 | Primary Command Group      | TE, LE, PP                  |

| PPC(2)              | Parallel Poll Configure    | PP                          |

| [PPD](2)            | Parallel Poll Disable      | PP                          |

| [PPE](2)            | Parallel Poll Enable       | PP                          |

| PPRN <sup>(1)</sup> | Parallel Poll Response N   | (via C)                     |

| PPU(2)              | Parallel Poll Unconfigure  | PP                          |

| REN                 | Remote Enable              | RL                          |

| RFD                 | Ready for Data             | SH                          |

| RQS                 | Request Service            | (via L, LE)                 |

| [SDC]               | Select Device Clear        | DC                          |

| SPD                 | Serial Poll Disable        | Т, ТЕ                       |

| SPE                 | Serial Poll Enable         | T, TE                       |

| SQR(1)              | Service Request            | (via C)                     |

| STB                 | Status Byte                | (via L, LE)                 |

| TCT or [TCT](1)     | Take Control               | C                           |

| UNL                 | Unlisten                   | L, LE                       |

| REMOTE MESSAGI      |                            |                             |

| ATN                 | Attentions                 | С                           |

| DAB                 | Data Byte                  | (Via T,TE)                  |

| DAC                 | Data Accepted              | AH                          |

| DAV                 | Data Valid                 | SH                          |

| DCL                 | Device Clear               | (via C)                     |

|                     | End                        | (via T)                     |

| END                 | Group Execute Trigger      | (via C)                     |

| GET                 | Go to Local                | (via C)                     |

| GTL                 |                            |                             |

| IDY                 | Identify                   | c                           |

| IFC                 | Interface Clear            |                             |

| LLO                 | Local Lockout              | (via C)                     |

| MLA or [MLA]        | My Listen Address          | (via C)                     |

| MSA or [MSA]        | My Secondary Address       | (via C)                     |

| MTA or [MTA]        | My Talk Address            | (via C)                     |

| OSA                 | Other Secondary Address    | (via C)                     |

Table 3. IEEE 488 Interface Message Reference List (Continued)

| Mnemonic | Message                   | Interface Function(s) <sup>(3)</sup> |

|----------|---------------------------|--------------------------------------|

| ΟΤΑ      | Other Talk Address        | (via C)                              |

| PCG      | Primary Command Group     | (via C)                              |

| PPC      | Parallel Poll Configure   | (via C)                              |

| [PPD]    | Parallel Poll Disable     | (via C)                              |

| [PPE]    | Parallel Poll Enable      | (via C)                              |

| PPRN     | Parallel Poll Response N  | PP                                   |

| PPU      | Parallel Poll Unconfigure | (via C)                              |

| REN      | Remote Enable             | c                                    |

| RFD      | Ready for Data            | AH                                   |

| RQS      | Request Service           | T, TE                                |

| [SDC]    | Selected Device Clear     | (via C)                              |

| SPD      | Serial Poll Disable       | (via C)                              |

| SPE      | Serial Poll Enable        | (via C)                              |

| SRQ      | Service Request           | SR                                   |

| STB      | Status Byte               | (via T,TE)                           |

| тст      | Take Control              | (via C)                              |

| UNL      | Unlisten                  | (via C)                              |

#### Table 3. IEEE 488 Interface Message Reference List (Continued)

#### NOTES:

1. These messages are handled only by Intel's 8292.

2. Undefined commands which may be passed to the microprocessor.

3. All Controller messages must be sent via Intel's 8292.

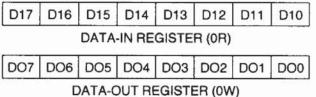

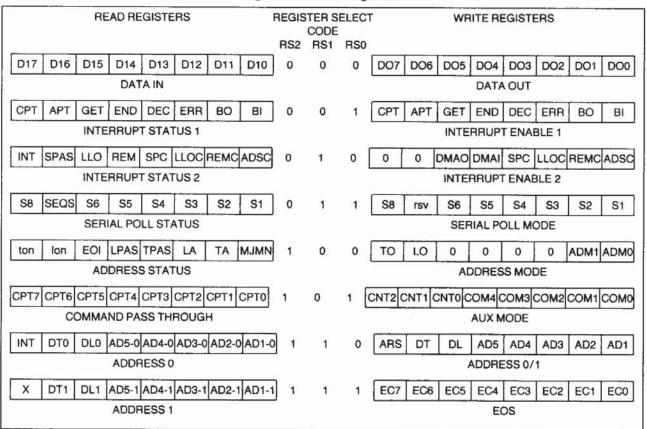

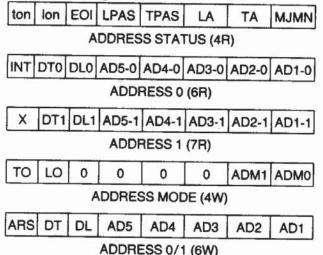

#### 8291A Registers

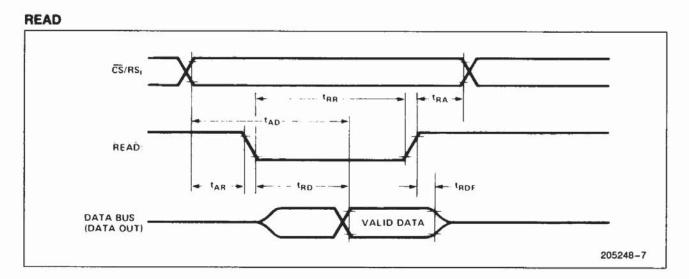

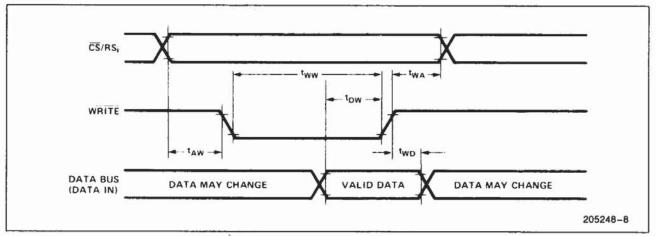

A bit-by-bit map of the 16 registers on the 8291A is presented in Figure 5. A more detailed explanation of each of these registers and their functions follows. The access of these registers by the micro-processor is accomplished by using the  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , and  $RS_0-RS_2$  pins.

| Register            | CS | RD | WR | RS0-RS2 |

|---------------------|----|----|----|---------|

| All Read Registers  | 0  | 0  | 1  | CCC     |

| All Write Registers | 0  | 1  | 0  | CCC     |

| High Impedance      | 1  | d  | d  | ddd     |

## **Data Registers**

The Data-In Register is used to move data from the GPIB to the microprocessor or to memory when the 8291A is addressed to listen. Incoming information is separately latched by this register, and its contents are not destroyed by a write to the data-out register. The RFD (Ready for Data) message is held false until the byte is removed from the data in register, either by the microprocessor or by DMA. The 8291A then completes the handshake automatically. In RFD holdoff mode (see Auxiliary Register A), the handshake is not finished until a command is sent

telling the 8291A to release the holdoff. In this way, the same byte may be read several times, or an over anxious talker may be held off until all available data has been processed.

When the 8291A is addressed to talk, it uses the data-out register to move data onto the GPIB. After the BO interrupt is received and a byte is written to this register, the 8291A initiates and completes the handshake while sending the byte out over the bus. In the BO interrupt disable mode, the user should wait until BO is active before writing to the register. (In the DMA mode, this will happen automatically.) A read of the Data-In Register does not destroy the information in the Data-Out Register.

### Interrupt Registers

| construction of |      |    |     |       |        |          |       |       |

|-----------------|------|----|-----|-------|--------|----------|-------|-------|

| CP1             | r Af | РΤ | GE  | T END | DEC    | ERR      | BO    | BI    |

|                 |      | I  | NTE | RRUP  | T STAT | TUS 1 (  | 1R)   |       |

| INT             | SP   | AS | LLC | REM   | SPC    | LLOC     | REMC  | ADSC  |

|                 |      | I  | NTE | RRUP  | T STAT | TUS 2 (2 | 2R)   |       |

| CPT             | r Ał | эт | GE  | T END | DEC    | ERR      | BO    | BI    |

|                 |      | 1  | NTE | RRUPT | ENAE   | BLE 1 (* | IW)   |       |

| 0               | 0    | DN | IAO | DMAI  | SPC    | LLOC     | REMC  | ADSC  |

|                 |      | I  | NTE | RRUPT | ENAE   | BLE 2 (2 | 2W)   | -     |

| INT             | DTO  | D  | LO  | AD5-0 | AD4-0  | AD3-0    | AD2-0 | AD1-0 |

|                 |      |    | AD  | DRESS | SORE   | GISTER   | 3     |       |

Figure 5. 8291A Registers

3

The 8291A can be configured to generate an interrupt to the microprocessor upon the occurrence of any of 12 conditions or events on the GPIB. Upon receipt of an interrupt, the microprocessor must read the Interrupt Status Registers to determine which event has occurred, and then execute the appropriate service routine (if necessary). Each of the 12 interrupt status bits has a matching enable bit in the interrupt enable registers. These enable bits are used to select the events that will cause the INT pin to be asserted. Writing a logic "1" into any of these bits enables the corresponding interrupt status bits to generate an interrupt. Bits in the Interrupt Status Registers are set regardless of the states of the enable bits. The Interrupt Status Registers are then cleared upon being read or when a local pon (poweron) message is executed. If an event occurs while one of the Interrupt Status Registers is being read. the event is held until after its register is cleared and then placed in the register.

#### NOTE:

Reading the interrupt status registers clears the bits which were set. The software must examine *all* relevant bits in the interrupt status registers before disregarding the value or an important interrupt may be missed. The mnemonics for each of the bits in these registers and a brief description of their respective functions appears in Table 4. This table also indicates how each of the interrupt bits is set.

#### NOTE:

The INT bit in the Address 0 Register is a duplicate of the INT bit in the Interrupt Status 2 Register. It is only a status bit. It does not generate interrupts and thus does not have a corresponding enable bit.

The BO and BI interrupts enable the user to perform data transfer cycles. BO indicates that a data byte should be written to the Data Out Register. It is set by TACS • (SWNS + SGNS) • RFD. It is reset when the data byte is written. ATN is asserted, or the 8291A exits TACS. Data should never be written to the Data Out Register before BO is set. Similarly, BI is set when an input byte is accepted into the 8291A and reset when the microprocessor reads the Data In Register. BO and BI are also reset by pon (poweron local message) and by a read of the Interrupt Status 1 Register. However, if it is so desired, data transfer cycles may be performed without reading the Interrupt Status 1 Register if all interrupts except for BO or BI are disabled; BO and BI will automatically reset after each byte is transferred.

#### **Table 4. Interrupt Bits**

If the 8291A is used in the interrupt mode, the INT and DREQ pins can be dedicated to data input and output interrupts respectively by enabling BI and DMAO, provided that no other interrupts are enabled. This eliminates the need to read the interrupt status registers if a byte is received or transmitted.

The ERR bit is set to indicate the bus error condition when the 8291A is an active talker and tries to send a byte to the GPIB, but there are no active listeners (e.g., all devices on the GPIB are in AIDS). The logical equivalent of (nba  $\bullet$  TACS  $\bullet$  DAC  $\bullet$  RFD) will set this bit.

The DEC bit is set whenever DCAS has occurred. The user must define a known state to which all device functions will return in DCAS. Typically this state will be a power-on state. However, the state of the device functions at DCAS is at the designer's discretion. It should be noted that DCAS has no effect on the interface functions which are returned to a known state by the IFC (interface clear) message or the pon local message.

The END interrupt bit may be used by the microprocessor to detect that a multi-byte transfer has been completed. The bit will be set when the 8291A is an active listener (LACS) and either EOS (provided the End on EOS Received feature is enabled in the Auxiliary Register A) or EOI is received. EOS will generate an interrupt when the byte in the Data In Register matches the byte in the EOS register. Otherwise the interrupt will be generated when a true input is detected on EOI.

The GET interrupt bit is used by the microprocessor to detect that DTAS has occurred. It is set by the 8291A when the GET message is received while it is addressed to listen. The TRIG output pin of the 8291A fires when the GET message is received. Thus, the basic operation of device trigger may be started without microprocessor software intervention.

The APT interrupt bit indicates to the processor that a secondary address is available in the CPT register for validation. This interrupt will only occur if Mode 3 addressing is in effect. (Refer to the section on addressing.) In Mode 2, secondary addresses will be recognized automatically on the 8291A. They will be ignored in Mode 1. The CPT interrupt bit flags the occurrence of an undefined command and of all secondary commands following an undefined command. The Command Pass Through feature is enabled by the B0 bit of Auxiliary Register B. Any message not decoded by the 8291A (not included in the state diagrams in Appendix B) becomes an undefined command. Note that any addressed command is automatically ignored when the 8291A is not addressed.

Undefined commands are read by the CPU from the Command Pass Through register of the 8291A. This register reflects the logic levels present on the data lines at the time it is read. If the CPT feature is enabled, the 8291A will hold off the handshake until this register is read.

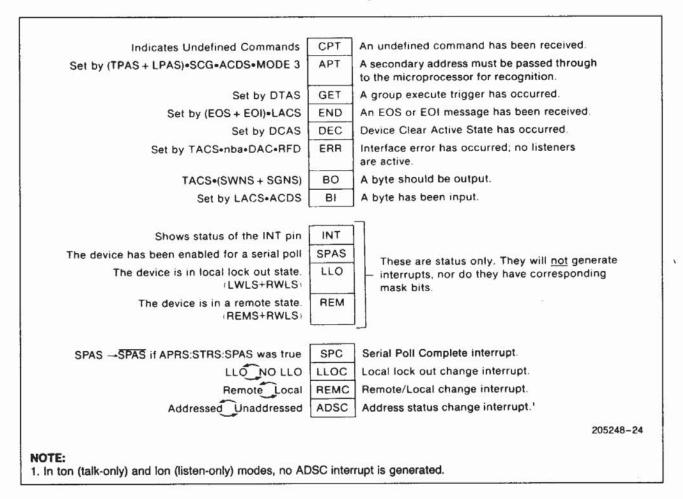

An especially useful feature of the 8291A is its ability to generate interrupts from state transitions in the interface functions. In particular, the lower 3 bits of the Interrupt Status 2 Register, if enabled by the corresponding enable bits, will cause an interrupt upon changes in the following states as defined in the IEEE 488 Standard.

| Bit 0 | ADSC | change in LIDS or TIDS or MJMN |

|-------|------|--------------------------------|

| Bit 1 | REMC | change in LOCS or REMS         |

| Bit 2 | LLOC | change in LWLS or RWLS         |

The upper 4 bits of the Interrupt Status 2 Register are available to the processor as status bits. Thus, if one of the bits 0-2 generates an interrupt indicating a state change has taken place, the corresponding status bit (bits 3-5) may be read to determine what the new state is. To determine the nature of a change in addressed status (bit 0) the Address Status Register is available to be read. The SPC interrupt (bit 3 in Interrupt Status 2) is set upon exit from SPAS if APRS:STRS:SPAS occurred which indicates that the GPIB controller has read the bus serial poll status byte after the 8291A requested service (asserted SRQ). The SPC interrupt occurs once after the controller reads the status byte if service was requested. The controller may read the status byte later, and the byte will contain the last status the 8291A's CPU wrote to the Serial Poll Mode Register, but the SRQS bit will not be set and no interrupt will be generated. Finally, bit 7 monitors the state of the 8291A INT pin. Logically, it is an OR of all enabled interrupt status bits. One should note that bits 3-6 of the Interrupt Status 2 Register do not generate interrupts, but are available only to be read as status bits by the processor. Bit 7 in Interrupt Status 2 is duplicated in Address 0 Register, and the latter should be used when polling for interrupts to avoid losing one of the interrupts in Interrupt Status 2 Register.

Bits 4 and 5 (DMAI, DMAO) of the Interrupt Mask 2 Register are available to enable direct data transfers between memory and the GPIB; DMAI (DMA in) enables the DREQ (DMA request) pin of the 8291A to be asserted upon the occurrence of BI. Similarly, DMAO (DMA out) enables the DREQ pin to be asserted upon the occurrence of BO. One might note that the DREQ pin may be used as a second interrupt output pin, monitoring BI and/or BO and enabled by DMAI and DMAO. One should note that the DREQ pin is not affected by a read of the Interrupt Status 1 Register. It is reset whenever a byte is written to the Data Out Register or read from the Data In Register.

To ensure that an interrupt status bit will not be cleared without being read, and will not remain uncleared after being read, the 8291A implements a special interrupt handling procedure. When an enabled interrupt bit is set in either of the Interrupt Status Registers, the input of the registers are blocked until the set bit is read and reset by the microprocessor. Thus, potential problems arise when interrupt status changes while the register is being blocked. However, the 8291A stores all new interrupts in a temporary register and transfers them to the appropriate Interrupt Status Register after the interrupt has been reset. This transfer takes place only if the corresponding bits were read as zeroes.

# Serial Poll Registers

| S8                       | SRQS | S6 | S5 | S4 | S3 | S2 | S1 |  |  |

|--------------------------|------|----|----|----|----|----|----|--|--|

| SERIAL POLL STATUS (3R)  |      |    |    |    |    |    |    |  |  |

| S8 rsv S6 S5 S4 S3 S2 S1 |      |    |    |    |    |    |    |  |  |

|                          |      |    |    |    |    |    |    |  |  |

SERIAL POLL MODE (3W)

The Serial Poll Mode Register determines the status byte that the 8291A sends out on the GPIB data lines when it receives the SPE (Serial Poll Enable) message. Bit 6 of this register is reserved for the rsv (request service) local message. Setting this bit to 1 causes the 8291A to assert its SRQ line, indicating its need for attention from the controller-in-charge of the GPIB. The other bits of this register are available for sending status information over the GPIB. Sometime after the microprocessor initiates a request for service by setting bit 6, the controller of the GPIB sends the SPE message and then addresses the 8291A to talk. At this point, one byte of status is returned by the 8291A via the Serial Poll Mode Register. After the status byte is read by the controller, rsv is automatically cleared by the 8291A and an SPC interrupt is generated. The CPU may request service again by writing another byte to the Serial Poll Mode Register with the rsv bit set. If the controller performs a serial poll when the rsv bit is clear, the last status byte written will be read, but the SRQ line will not be driven by the 8291A and the SRQS bit will be clear in the status byte.

The Serial Poll Status Register is available for reading the status byte in the Serial Poll Mode Register. The processor may check the status of a request for service by polling bit 6 of this register, which corresponds to SRQS (Service Request State). When a Serial Poll is conducted and the controller-in-charge reads the status byte, the SRQS bit is cleared. The SRQ line and the rsv bit are tied together.

# **Address Registers**

The Address Mode Register is used to select one of the five modes of addressing available on the 8291A. It determines the way in which the 8291A uses the information in the Address 0 and Address 1 Registers.

-In Mode 1, the contents of the Address 0 Register constitute the "Major" talker/listener address while the Address 1 Register represents the "Minor" talker/listener address. In applications where only one address is needed, the major talker/listener is used, and the minor talker/listener should be disabled. Loading an address via the Address 0/1 Register into Address Registers 0 and 1 enables the major and minor talker/listener functions respectively.

-In Mode 2 the 8291A recognizes two sequential address bytes: a primary followed by a secondary. Both address bytes must be received in order to enable the device to talk or listen. In this manner, Mode 2 addressing implements the extended talker and listener functions as defined in IEEE-488. To use Mode 2 addressing the primary address must be loaded into the Address 0 Register, and the Secondary Address is placed in the Address 1 Register. With both primary and secondary addresses residing on chip, the 8291A can handle all addressing sequences without processor intervention.

-In Mode 3, the 8291A handles addressing just as it does in Mode 1, except that each Major or Minor primary address must be followed by a secondary address. All secondary addresses must be verified by the microprocessor when Mode 3 is used. When the 8291A is in TPAS or LPAS (talker/listener primary addressed state), and it does not recognize the byte on the DIO lines, an APT interrupt is generated (see section on Interrupt Registers) and the byte is available in the CPT (Command Pass-Through) Register. As part of its interrupt service routine, the microprocessor must read the CPT Register and write one of the following responses to the Auxiliary Mode Register:

- 1. 07H implies a non-valid secondary address

- 2. 0FH implies a valid secondary address

Setting the TO bit generates the local ton (talk-only) message and sets the 8291A to a talk-only mode. This mode allows the device to operate as a talker in an interface system without a controller.

Setting the LO bit generates the local lon (listenonly) message and sets the 8291A to a listen-only mode. This mode allows the device to operate as a listener in an interface system without a controller. The above bits may also be used by a controller-incharge to set itself up for remote command or data communication.

The mode of addressing implemented by the 8291A may be selected by writing one of the following bytes to the Address Mode Register.

| Register |                                  |

|----------|----------------------------------|

| Contents | Mode                             |

| 10000000 | Enable talk only mode (ton)      |

| 01000000 | Enable listen only mode (lon)    |

| 11000000 | The 8291 may talk to itself      |

| 0000001  | Mode 1, (Primary-Primary)        |

| 00000010 | Mode 2 (Primary-Secondary)       |

| 00000011 | Mode 3 (Primary/APT-Primary/APT) |

The Address Status Register contains information used by the microprocessor to handle its own addressing. This information includes status bits that monitor the address state of each talker/listener, "ton" and "lon" flags which indicate the talk and listen only states, and an EOI bit which, when set, signifies that the END message came with the last data byte. LPAS and TPAS indicate that the listener or talker primary address has been received. The microprocessor can use these bits when the secondary address is passed through to determine whether the 8291A is addressed to talk or listen. The LA (listener addressed) bit will be set when the 8219A is in LACS (Listener Active State ) or in LADS (Listener Addressed State), Similarly, the TA (Talker Addressed bit) will be set to indicate TACS or TADS. but also to indicate SPAS (Serial Poll Active State). The MJMN bit is used to determine whether the information in the other bits applies to the Major or Minor talker/listener. It is set to "1" when the Minor talker/listener is addressed. It should be noted that only one talker/listener may be active at any one time. Thus, the MJMN bit will indicate which, if either, of the talker/listeners is addressed or active.

The Address 0/1 Register is used for specifying the device's addresses according to the format selected in the Address Mode Register. Five bit addresses may be loaded into the Address 0 and Address 1 Registers by writing into the Address 0/1 Register. The ARS bit is used to select which of these registers the other seven bits will be loaded into. The DT and DL bits may be used to disable the talker or listener function at the address signified by the other five bits. When Mode 1 addressing is used and only one primary address is desired, *both* the talker and the listener should be disabled at the Minor address.

As an example of how the Address 0/1 Register might be used, consider an example where two primary addresses are needed in the device. The Major primary address will be selectable only as a talker and the Minor primary address will be selectable only as a listener. This configuration of the 8291A is formed by the following sequence of writes by the microprocessor.

| Operation                                                                               | ĊS | RD | WR | Data     | RS <sub>2</sub> -RS <sub>0</sub> |

|-----------------------------------------------------------------------------------------|----|----|----|----------|----------------------------------|

| 1. Select addressing<br>Mode 1                                                          | 0  | 1  | 0  | 00000001 | 100                              |

| 2. Load major address<br>into Address 0 Register<br>with listener function<br>disabled. | 0  | 1  | 0  | 001AAAAA | 110                              |

| 3. Load minor address<br>into Address 1 Register<br>with talker function<br>disabled.   | 0  | 1  | 0  | 110BBBBB | 110                              |

At this point, the addresses AAAAA and BBBBB are stored in the Address 0 and Address 1 Registers respectively, and are available to be read by the microprocessor. Thus, it is not necessary to store any address information elsewhere. Also, with the information stored in the Address 0 and Address 1 Registers, processor intervention is not required to recognize addressing by the controller. Only in Mode 3, where secondary addresses are passed through, must the processor intervene in the addressing sequence.

The Address 0 Register contains a copy of bit 7 of the Interrupt Status 2 Register (INT). This is to be used when polling for interrupts. Software should poll register 6 checking for INT (bit 7) to be set. When INT is set, the Interrupt Status Register should be read to determine which interrupt was received.

# **Command Pass Through Register**

| CPT7 CPT6 CPT5 CPT4 CPT3 CPT2 CPT1 CPT0 |

|-----------------------------------------|

|-----------------------------------------|

#### COMMAND PASS THROUGH (5R)

The Command Pass Through Register is used to transfer undefined 8-bit remote message codes from the GPIB to the microprocessor. When the CPT feature is enabled (bit BO in Auxiliary Register B), any message not decoded by the 8291A becomes an undefined command. When Mode 3 addressing is used secondary addresses are also passed through the CPT Register. In either case, the 8291A will hold-off the handshake until the microprocessor reads this register and issues the VSCMD auxiliary command.

The CPT and APT interrupts flag the availability of undefined commands and secondary addresses in the CPT Register. The details of these interrupts are explained in the section on Interrupt Registers.

An added feature of the 8291A is its ability to handle undefined secondary commands following undefined primaries. Thus, the number of available commands for future IEEE-488 definition is increased; one undefined primary command followed by a sequence of as many as 32 secondary commands can be processed. The IEEE-488 Standard does not permit users to define their own commands, but upgrades of the standard are thus provided for.

The recommended use of the 8291A's undefined command capabilities is for a controller-configured Parallel Poll. The PPC message is an undefined primary command typically followed by PPE, and undefined secondary command. For details on this procedure, refer to the section on Parallel Poll Protocol.

## **Auxiliary Mode Register**

|      | Chitte | 0.170 | 0000 | 000  | 00100 | 0014 | 0000 |  |

|------|--------|-------|------|------|-------|------|------|--|

| CN12 | CN11   | CNIU  | COM4 | COM3 | COM2  | COMI | COM0 |  |

AUX MODE (5W) CNT0-2:CONTROL BITS COM0-4:COMMAND BITS The Auxiliary Mode Register contains a three-bit control field and a five-bit command field. It is used for several purposes on the 8291A:

- 1. To load "hidden" auxiliary registers on the 8291A.

- To issue commands from the microprocessor to the 8291A.

- To preset an internal counter used to generate T1, delay in the Source Handshake function, as defined in IEEE-488.

Table 5 summarizes how these tasks are performed with the Auxiliary Mode Register. Note that the three control bits determine how the five command bits are interpreted.

Table 5

| C               | ode                                            |                                                                                                                                                                                      |  |  |  |  |  |

|-----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Control<br>Bits | Command<br>Bits                                | Command                                                                                                                                                                              |  |  |  |  |  |

| 000<br>001      |                                                | Execute auxiliary command CCCC<br>Preset internal counter to<br>match external clock<br>frequency of DDDD MHz<br>(DDDD binary representation<br>of 1 to 8 MHz)                       |  |  |  |  |  |

| 100             | DDDDD                                          | Write DDDDD into<br>auxiliary register A                                                                                                                                             |  |  |  |  |  |

| 101             | DDDDD                                          | Write DDDDD into<br>auxiliary register B                                                                                                                                             |  |  |  |  |  |

| 011             | USP <sub>3</sub> P <sub>2</sub> P <sub>1</sub> | Enable/disable parallel<br>poll either in response to remote<br>messages (PPC followed by<br>PPE or PPD) or as a local<br>lpe message. (Enable if $U = 0$ ,<br>disable if $U = 1$ .) |  |  |  |  |  |

#### AUXILIARY COMMANDS

Auxiliary commands are executed by the 8291A whenever 0000CCCC is written into the Auxiliary Mode Register, where CCCC is the 4-bit command code.

**0000**—Immediate Execute pon: This command resets the 8291A to a power up state (local pon message as defined in IEEE-488).

The following conditions constitute the power up state:

- 1. All talkers and listeners are disabled.

- 2. No interrupt status bits are set.

The 8291A is designed to power up in certain states as specified in the IEEE-488 state diagrams. Thus, the following states are in effect in the power up state: SIDS, AIDS, TIDS, LIDS, NPRS, LOCS, and PPIS.

The "0000" pon is an immediate execute command (a pon pulse). It is also used to release the "initialize" state generated by either an external reset pulse or the "0010" Chip Reset command.

**0010**—Chip Reset (Initialize): This command has the same effect as a pulse applied to the Reset pin. (Refer to the section on Reset Procedure.)

0011—Finish Handshake: This command finishes a handshake that was stopped because of a holdoff on RFD. (Refer to Auxiliary Register A.)

**0100**---Trigger: A "Group Execute Trigger" is forced by this command. It has the same effect as a GET command issued by the controller-in-charge of the GPIB, but does not cause a GET interrupt.

0101, 1101—Clear/Set rtl: These commands correspond to the local rtl message as defined by the IEEE-488. The 8291A will go into local mode when a Set rtl Auxiliary Command is received if local lockout is not in effect. The 8291A will exit local mode after receiving a Clear rtl Auxiliary Command if the 8291A is addressed to listen.

0110—Send EOI: The EOI line of the 8291A may be asserted with this command. The command causes EOI to go true with the next byte transmitted. The EOI line is then cleared upon completion of the handshake for that byte.

**0111, 1111**—Non Valid/Valid Secondary Address or Command (VSCMD): This command informs the 8291A that the secondary address received by the microprocessor was valid or invalid (0111 = invalid, 1111 = valid). If Mode 3 addressing is used, the processor must field each extended address and respond to it, or the GPIB will hang up. Note that the COM3 bit is the invalid/valid flag.

The valid (1111) command is also used to tell the 8291A to continue from the command-pass-throughstate, or from RFD holdoff on GET, SDC or DCL.

1000—pon: This command puts the 8291A into the pon (power on) state and holds it there. It is similar to a Chip Reset except none of the Auxiliary Mode Registers are cleared. In this state, the 8291A does not participate in any bus activity. An Immediate Execute pon releases the 8291A from the pon state and permits the device to participate in the bus activity again. **0001, 1001**—Parallel Poll Flag (local "ist" message): This command sets (1001) or clears (0001) the parallel poll flag. A "1" is sent over the assigned data line (PRR = Parallel Poll Response true) only if the parallel poll flag matches the sense bit from the lpe local message (or indirectly from the PPE message). For a more complete description of the Parallel Poll features and procedures refer to the section on Parallel Poll Protocol.

#### INTERNAL COUNTER

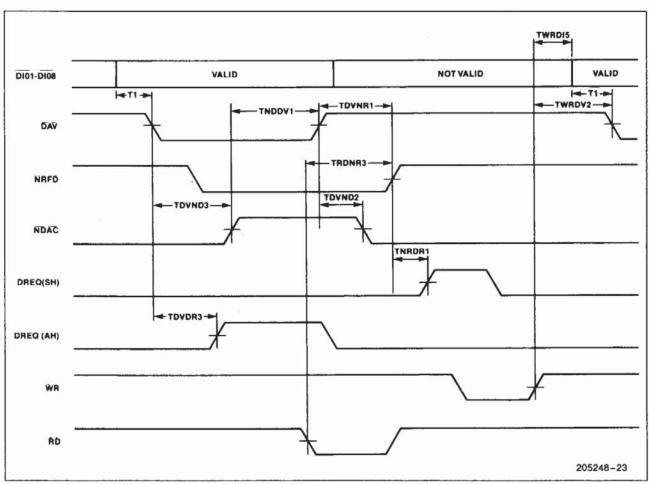

The internal counter determines the delay time allowed for the setting of data on the DIO lines. This delay time is defined as  $T_1$  in IEEE-488 and appears in the Source Handshake state diagram between the SDYS and STRS. As such, DAV is asserted  $T_1$  after the DIO lines are driven. Consequently,  $T_1$  is a major factor in determining the data transfer rate of the 8291A over the GPIB ( $T_1 = TWRDV2-TWRD15$ ).

When open-collector transceivers are used for connection to the GPIB, T<sub>1</sub> is defined by IEEE-488 to be 2  $\mu$ s. By writing 0010DDDD into the Auxiliary Mode Register, the counter is preset to match a f<sub>C</sub> MHz clock input, where DDDD is the binary representation of N<sub>F</sub> [1 ≤ N<sub>F</sub> ≤ 8, N<sub>F</sub> = (DDDD)<sub>2</sub>]. When N<sub>F</sub> = f<sub>C</sub>, a 2  $\mu$ s T<sub>1</sub> delay will be generated before each DAV asserted.

$$T_{1(\mu s)} = \frac{2N_F}{f_c} + t_{SYNC}, 1 \le N_F \le 8$$

$t_{SYNC}$  is a synchronization error, greater than zero and smaller than the larger of T clock high and T clock low. (For a 50% duty cycle clock,  $t_{SYNC}$  is less than half the clock cycle).

If it is necessary that T<sub>1</sub> be different from 2  $\mu$ s, N<sub>F</sub> may be set to a value other than f<sub>C</sub>. In this manner, data transfer rates may be programmed for a given system. In small systems, for example, where transfer rates exceeding GPIB specifications are required, one may set N<sub>F</sub> < f<sub>C</sub> and decrease T<sub>1</sub>.

When tri-state transceivers are used, IEEE-488 allows a higher transfer rate (lower T<sub>1</sub>). Use of the 8291A with such transceivers is enabled by setting B<sub>2</sub> in Auxilliary Register B. In this case, setting N<sub>F</sub> =  $f_c$  causes a T<sub>1</sub> delay of 2µs to be generated for the first byte transmitted—all subsequent bytes will have a delay of 500 ns.

$$T_1$$

(High Speed)  $\mu s = \frac{N_F}{2f_C} + t_{SYNC}$

Thus, the shortest  $T_1$  is achieved by setting  $N_F = 1$  using an 8 MHz clock with a 50% duty cycle clock ( $t_{SYNC} < 63$  ns):

$$T_{1(HS)} = \frac{1}{2 \times 8} + 0.063 = 125 \text{ ns max}.$$

#### **AUXILIARY REGISTER A**

Auxiliary Register A is a "hidden" 5-bit register which is used to enable some of the 8291A features. Whenever a 100  $A_4A_3A_2A_1A_0$  byte is written into the Auxiliary Register, it is loaded with the data  $A_4A_3A_2A_1A_0$ . Setting the respective bits to "1" enables the following features.

Ag-RFD Holdoff on all Data: If the 8291A is listening, RFD will not be sent true until the "finish handshake" auxiliary command is issued by the microprocessor. The holdoff will be in effect for each data byte.

A<sub>1</sub>—RFD Holdoff on End: This feature enables the holdoff on EOI or EOS (if enabled). However, no hold-off will be in effect on any other data bytes.

3

A<sub>2</sub>-End on EOS Received: Whenever the byte in the Data In Register matches the byte in the EOS Register, the END interrupt bit will be set in the Interrupt Status 1 Register.

$A_3$ —Output EOI on EOS Sent: Any occurrence of data in the Data Out Register matching the EOS Register causes the EOI line to be sent true along with the data.

$A_4$ —EOS Binary Compare: Setting this bit causes the EOS Register to function as a full 8-bit word. When it is not set, the EOS Register is a 7-bit word (for ASCII characters).

If A<sub>0</sub> = A<sub>1</sub> = 1, a special "continuous Acceptor Handshake cycling" mode is enabled. This mode should be used only in a controller system configuration, where both the 8291A and the 8292 are used. It provides a continuous cycling through the Acceptor Handshake state diagram, requiring no local messages from the microprocessor; the rdy local message is automatically generated when in ANRS. As such, the 8291A Acceptor Handshake serves as the controller Acceptor Handshake. Thus, the controller cycles through the Acceptor Handshake without delaying the data transfer in progress. When the tcs local message is executed, the 8291A should be taken out of the "continuous AH cycling" mode, the GPIB will hang up in ANRS, and a BI interrupt will be generated to indicate that control may be taken. A simpler procedure may be used when a "tcs on end of block" is executed; the 8291A may stay in "continuous AH cycling". Upon the end of a block (EOI or EOS received), a holdoff is generated, the GPIB hangs up in ANRS, and control may be taken.

#### AUXILIARY REGISTER B

Auxiliary Register B is a "hidden" 4-bit register which is used to enable some of the features of the 8291A. Whenever a 101  $B_4B_3B_2B_1B_0$  is written into the Auxiliary Mode Register, it is loaded with the data  $B_4B_3B_2B_1B_0$ . Setting the respective bits to "1" enables the following features:

**B**<sub>0</sub>—Enable Undefined Command Pass Through: This feature allows any commands not recognized by the 8291A to be handled in software. If enabled, this feature will cause the 8291A to holdoff the handshake when an undefined command is received. The microprocessor must then read the command from the Command Pass Through Register and send the VSCMD auxiliary command. Until the VSCMD command is sent, the handshake holdoff will be in effect.

**B**<sub>1</sub>—Send EOI in SPAS: This bit enables EOI to be sent with the status byte; EOI is sent true in Serial Poll Active State. Otherwise, EOI is sent false in SPAS.

**B**<sub>2</sub>—Enable High Speed Data Transfer: This feature may be enabled when tri-state external transceivers are used. The data transfer rate is limited by T<sub>1</sub> delay time generated in the Source Handshake function, which is defined according to the type of transceivers used. When the "High Speed" feature is enabled, T<sub>1</sub> = 2 microseconds is generated for the first byte transmitted after each true to false transition of ATN. For all subsequent bytes, T<sub>1</sub> = 500 ns. Refer to the Internal Counter section for an explanation of T<sub>1</sub> duration as a function of B<sub>2</sub> and of clock frequency.

**B**<sub>3</sub>—Enable Active Low Interrupt: Setting this bit causes the polarity of the INT pin to be reversed, providing an output signal compatible with Intel's MCS-48® Family. Interrupt registers are not affected by this bit.

$B_4$ —Enable RFD Holdoff on GET or DEC: Setting this bit causes RFD to be held false until the "VSCMD" auxiliary command is written after GET, SDC, and DCL commands. This allows the device to hold off the bus until it has completed a clear or trigger similar to an unrecognized command.

#### PARALLEL POLL PROTOCOL

Writing a 011USP<sub>3</sub>P<sub>2</sub>P<sub>1</sub> into the Auxiliary Mode Register will enable (U = 0) or disable (U = 1) the 8291A for a parallel poll. When U = 0, this command is the "lpe" (local poll enable) local message as defined in IEEE-488. The "S" bit is the sense in which the 8291A is enabled; only if the Parallel Poll Flag ("ist" local message) matches this bit will the Parallel Poll Response, PPR<sub>N</sub>, be sent true (Response = S + ist). The bits P<sub>3</sub>P<sub>2</sub>P<sub>1</sub> specify which of the eight data lines PPR<sub>N</sub> will be sent over. Thus, once the 8291A has been configured for Parallel Poll, whenever it senses both EOI and ATN true, it will automatically compare its PP flag with the sense bit and send PPR<sub>N</sub> true or false according to the comparison.

If a PP2\* implementation is desired, the "Ipe" and "jst" local messages are all that are needed. Typically, the user will configure the 8291A for Parallel Poll immediately after initialization. During normal operation the microprocessor will set or clear the Parallel Poll Flag (ist) according to the device's need for service. Consequently the 8291A will be set up to give the proper response to IDY (EOI • ATN) without directly involving the microprocessor.

If a PP1\* implementation is desired, the undefined command features of the 8291A must be used. In PP1, the 8291A is indirectly configured for Parallel Poll by the active controller on the GPIB. The sequence at the 8291A being enabled or disabled remotely is as follows:

- The PPC message is received and is loaded into the Command Pass Through Register as an undefined command. A CPT Interrupt is sent to the microprocessor; the handshake is automatically held off.

- The microprocessor reads the CPT Register and sends VSCMD to the 8291A, releasing the handshake.

- Having recieved an undefined primary command, the 8291A is set up to receive an undefined secondary command (the PPE or PPD message). This message is also received into the CPT Register, the handshake is held off, and the CPT interrupt is generated.

- 4. The microprocessor reads the PPE or PPD message and writes the command into the Auxiliary Mode Register (bit 7 should be cleared first). Finally, the microprocessor sends VSCMD and the handshake is released.

#### NOTE:

\*As defined in IEEE Standard 488.

# End of Sequence (EOS) Register

| EC7          | EC6 | EC5 | EC4 | EC3 | EC2 | EC1 | EC0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| EOS BEGISTEB |     |     |     |     |     |     |     |  |

The EOS Register and its features offer an alternative to the "Send EOI" auxiliary command. A seven or eight bit byte (ASCII or binary) may be placed in the register to flag the end of a block or read. The type of EOS byte to be used is selected in Auxiliary Register bit  $A_4$ .

If the 8291A is a listener, and the "End on EOS Received" is enabled with bit  $A_2$ , then an END interrupt is generated in the Interrupt Status 1 Register whenever the byte in the Data-In Register matches the byte in the EOS Register.

If the 8291A is a talker, and the "Output EOI on EOS Sent" is enabled with bit  $A_3$ , then the EOI line is sent true with the next byte whenever the contents of the Data Out Register match the EOS register.

# **Reset Procedure**

The 8291A is reset to an initialization state either by a pulse applied to its Reset pin, or by a reset auxiliary command (02H written into the Auxiliary Command Register). The following conditions are caused by a reset pulse (or local reset command):

- 1. A "pon" local message as defined by IEEE-488 is held true until the initialization state is released.

- 2. The Interrupt Status Registers are cleared (not Interrupt Enable Registers).

- 3. Auxiliary Registers A and B are cleared.

- 4. The Serial Poll Mode Register is cleared.

- 5. The Parallel Poll Flag is cleared.

- 6. The EOI bit in the Address Status Register is cleared.

- 7. N<sub>F</sub> in the Internal Counter is set to 8 MHz. This setting causes the longest possible T<sub>1</sub> delay to be generated in the Source Handshake (16  $\mu$ s for 1 MHz clock).

- 8. The rdy local message is sent.

The initialization state is released by an "immediate execute pon" command (00H written into the Auxiliary Command Register).

The suggested initialization sequence is:

1. Apply a reset pulse or send the reset auxiliary command.

- 2. Set the desired initial conditions by writing into the Interrupt Enable, Serial Poll Mode, Address Mode, Address 0/1, and EOS Registers. Auxiliary Registers A and B, and the internal counter should also be initialized.

- 3. Send the "immediate execute pon" auxiliary command to release the initialization state.

- 4. If a PP2 Parallel Poll implementation is to be used the "lpe" local message may be sent, enabling the 8291A for a Parallel Poll Response on an assigned line. (Refer to the section on Parallel Poll Protocol.)

# Using DMA

The 8291A may be connected to the Intel® 8237 or 8257 DMA Controllers or the 8089 I/O Processor for DMA operation. The 8237 will be used to refer to any DMA controller. The DREQ pin of the 8291A requests a DMA byte transfer from the 8237. It is set by BO or BI flip flops, enabled by the DMAO and DMAI bits in the Interrupt Enable 2 Register. (After reading , the INT1 register BO and BI interrupts will be cleared but not BO and BI in DREQ equation.)

The DACK pin is driven by the 8237 in response to the DMA request. When DACK is true (active low) it sets  $\overline{CS} = RS0 = RS1 = RS2 = 0$  such that the RD and WR signals sent by the 8237 refer to the Data In and Data Out Registers. Also, the DMA request line is reset by DACK (RD + WR).

DMA input sequence:

- 1. A data byte is accepted from the GPIB by the 8291A.

- 2. A BI interrupt is generated and DREQ is set.

- DACK and RD are driven by the 8237, the contents of the Data In Register are transferred to the system bus, and DREQ is reset.

- 4. The 8291A sends RFD true on the GPIB and proceeds with the Acceptor Handshake protocol.

DMA output sequence:

- 1. A BO interrupt is generated (indicating that a byte should be output) and DREQ is asserted.

- 2. DACK and WR are driven by the 8237, a byte is transferred from the MCS bus into the Data Out Register, and DREQ is reset.

- 3. The 8291A sends DAV true on the GPIB and proceeds with the Source Handshake protocol.

It should be noted that each time the device is addressed (MTA + MLA + ton + Ion), the Address Status Register should be read, and the 8237 should be initialized accordingly. (Refer to the 8237 or 8257 Data Sheets.)

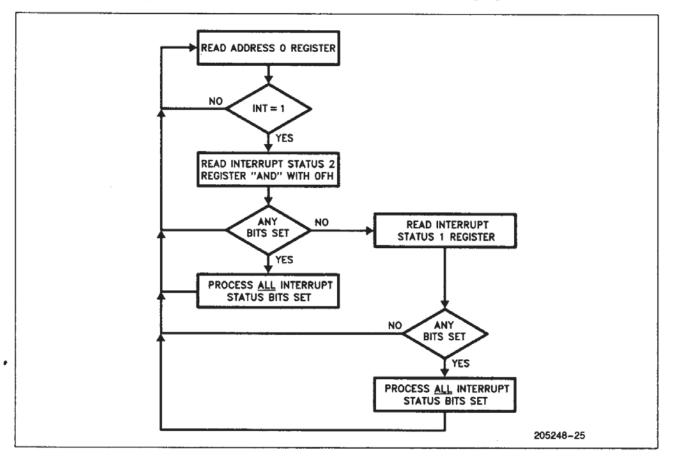

# Polling the 8291A

If polling is used to determine the 8291A's service needs, the CPU must poll the INT bit in the address

0 register. All relevant interrupt status bits must be enabled during initialization for them to affect the INT status bit. The following flow chart illustrates the recommended polling algorithm.

# APPLICATION BRIEF

## System Configuration

#### MICROPROCESSOR BUS CONNECTION

The 8291A is 8048/49, 8051, 8080/85, and 8086/88 compatible. The three address pins (RS<sub>0</sub>, RS<sub>1</sub>, and RS<sub>2</sub>) should be connected to the non-multiplexed address bus (for example:  $A_8$ ,  $A_9$ ,  $A_{10}$ ). In case of 8080, any address lines may be used. If the

three lowest address bits are used  $(A_0, A_1, A_2)$ , then they must be demultiplexed first.

#### EXTERNAL TRANSCEIVERS CONNECTION

The 8293 GPIB Transceiver interfaces the 8291A directly to the IEEE-488 bus. The 8291A and two 8293's can be configured as a talker/listener (see Figure 6) or with the 8292 as a talker/listener/controller (see Figure 7). Absolutely no active or passive external components are required to comply with the complete IEEE-488 electrical specification.

3

Figure 6. 8291A and 8293 System Configuration

Figure 7. 8291A, 8292, and 8293 System Configuration

# Start-Up Procedures

The following section describes the steps needed to initialize a typical 8291A system implementing a talker/listener interface and an 8291A/8292 system implementing a talker/listener/controller interface.

#### TALKER/LISTENER SYSTEM

Assume a general system configuration with the following features: (i) Polled system interface; (ii) Mode 1 addressing; (iii) same address for talker and listener; (iv) ASCII carriage return as the end-of-sequence (EOS) character; (v) EOI sent true with the last byte; and, (vi) 8 MHz clock.

Initialization. Initialization is accomplished with the following steps:

- Pulse the RESET input or write 02H to the Auxiliary Mode Register.

- Write 00H to the Interrupt Enable Registers 1 and

This disables interrupt and DMA.

- Write 01H to the Address Mode Register to select Mode 1 addressing.

- 4. Write 28H to the Auxiliary Mode Register. This loads 8H to the Auxiliary Register A matching the 8 MHz clock input to the internal T1 delay counter to generate the delay meeting the IEEE spec.

- Write the talker/listener address to the Address 0/1 register. The three most significant bits are zero.

- Write an ASCII carriage return (0DH) to the EOS register.

- Write 84H to the Auxiliary Mode Register to allow EOI to be sent true when the EOS character is sent.