### **General Description**

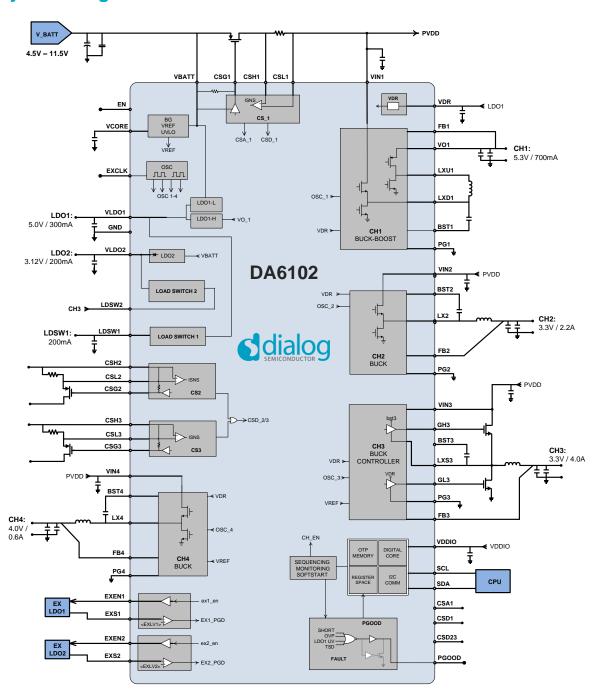

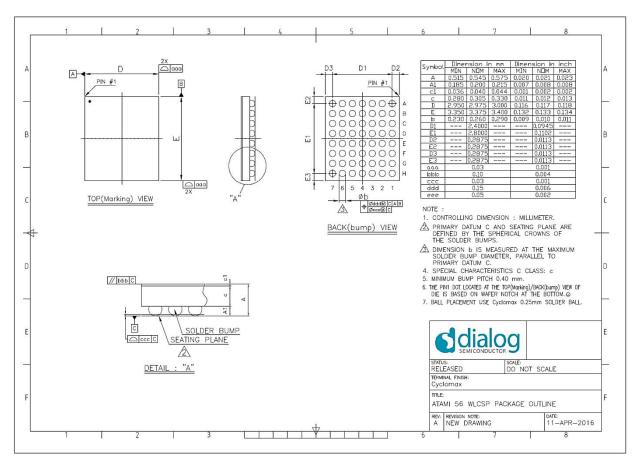

The DA6102 is a highly integrated multi-channel PMIC designed for 2-cell lithium-ion battery powered systems. The wide input voltage range allows direct battery connection for each channel to maximize battery life. The PMIC also includes a highly accurate input current sense with circuit breaker control for battery current sensing and over-current shutdown. The DA6102 integrates two buck regulators, a BuckBoost regulator, a high current buck controller, and two always-on LDOs. This high level of integration combined with high frequency operation (up to 3 MHz) minimizes both PCB size and external component count for the smallest possible solution size. The DA6102 uses extremely low RDSon FETs to enable very high efficiency buck and BuckBoost regulation. Additional features include two external load switches, two LDO controllers, external clock synchronization, global enable pin, and configurable PGOOD pin. An I²C interface enables flexibility and easy configuration of each regulator's output voltage, switching frequency, power sequencing, and fault protection. Most features are configurable by OTP, allowing simplified setting of output voltages and start-up sequence. Each channel has dedicated current limit, over-voltage, and under-voltage protection, with programmable masking and shutdown timer options. The DA6102 is available in a 56-ball 2.975 mm x 3.375 mm, 0.4 mm pitch WLCSP package.

### **Key Features**

- 4.5 V to 11.5 V input range

- Input current sense with circuit breaker

- □ +/- 1% accuracy monitoring

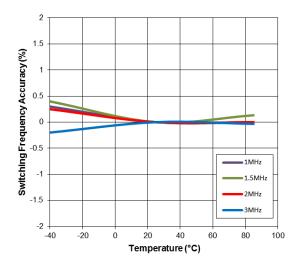

- Programmable internal switching frequency

- □ 1.0 MHz, 1.5 MHz, 2.0 MHz, and 3.0 MHz

- □ +/- 2 % accuracy

- External sync clock input

- □ 1.5 MHz to 3 MHz range

- Programmable sequencing and soft-start

- 2 Always-on LDOs with integrated load switches

- 2 Integrated buck converters

- 1 Integrated BuckBoost converter

- 1 High current buck controller

- 2 Load switch controllers

- 2 External LDO monitors

- Power Good flag

- Global enable input

- Smallest total solution size

- 2.975 mm x 3.375 mm WLCSP package

- CH1: BuckBoost regulator

- □ 700 mA max

- □ 5.1 V to 5.8 V output range

- CH2: Buck regulator

- □ 2.2A max

- □ 3.0 V to 4.55 V output range

- CH3: Buck controller

- □ Synchronous NFET drivers

- □ 3.0 V to 3.75 V output range

- CH4: Buck regulator

- □ 600 mA max

- □ 3.2 V to 4.2 V output range

- LDO1: 300 mA, always-on

- LDO2: 200 mA, always-on

- Protection features on each channel

- □ Current limit

- Short circuit

- □ Over-voltage

- Output discharge

## **Applications**

- DSLR cameras

- MILC cameras

# **System Diagram**

Figure 1: System Diagram

## **Contents**

| Ge   | neral   | Description                                               |    |

|------|---------|-----------------------------------------------------------|----|

| Ke   | y Feat  | tures                                                     | 1  |

| Аp   | plicati | tions                                                     | 1  |

| Sys  | stem I  | Diagram                                                   | 2  |

| -    |         | s                                                         |    |

|      |         |                                                           |    |

| ·    |         |                                                           |    |

| 1 a. |         | out                                                       |    |

|      |         |                                                           |    |

| 2    |         | olute Maximum Ratings                                     |    |

| 3    |         | ommended Operating Conditions                             |    |

| 4    |         | trical Characteristics                                    |    |

| 5    |         | ng Characteristics                                        |    |

| 6    | Ther    | mal Characteristics                                       | 17 |

| 7    | Туріс   | cal Performance                                           | 18 |

| 8    | Туріс   | cal Schematic                                             | 22 |

| 9    | Func    | ctional Description                                       | 23 |

|      | 9.1     | General                                                   | 23 |

|      | 9.2     | Always-on LDOs and Internal Load Switches                 | 23 |

|      | 9.3     | ENABLE, UVLO, and Operating State Transitions             |    |

|      | 9.4     | Sequencer and Soft-start                                  |    |

|      | 9.5     | Channel 1 to Channel 4, Common Features and Functionality |    |

|      | 9.6     | Channel 1, BuckBoost Regulator                            |    |

|      | 9.7     | Channels 2 and 4, Buck Regulators                         | 37 |

|      | 9.8     | Channel 3, Buck Controller                                | 38 |

|      | 9.9     | Inductors, Output Capacitors, and Input Capacitors        | 39 |

|      | 9.10    | CS1, CS2, and CS3: Current Sense and Load Switches        |    |

|      | 9.11    | External LDO Control                                      | 42 |

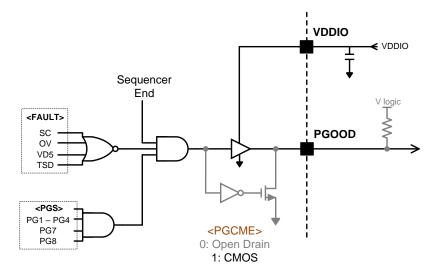

|      | 9.12    | PGOOD and FAULT Handling                                  | 42 |

|      | 9.13    | VDDIO and VCORE                                           | 46 |

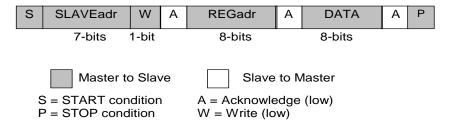

|      | 9.14    | I <sup>2</sup> C Communication                            | 46 |

|      | 9.15    | PCB Layout Guidelines                                     | 50 |

| 10   | Regis   | ster Definitions                                          | 52 |

|      | 10.1    | Register Map                                              | 52 |

|      | 10.2    | Register Details                                          | 54 |

| Аp   | pendi   | ix A Optimizing Transient Performance                     | 76 |

| 11   | Pack    | rage Information                                          | 80 |

|      |         | Package Outlines                                          |    |

|      | 11.2    | Moisture Sensitivity Level                                | 80 |

|      | 11.3    | Soldering Information                                     | 80 |

| 12   | Orde    | ering Information                                         | 81 |

# **Figures**

**Datasheet**

| Figure 1: System Diagram                            |    |

|-----------------------------------------------------|----|

| Figure 2: Connection Diagram (Top View)             |    |

| Figure 3: I <sup>2</sup> C Timing                   | 17 |

| Figure 4: Frequency vs Temperature                  | 18 |

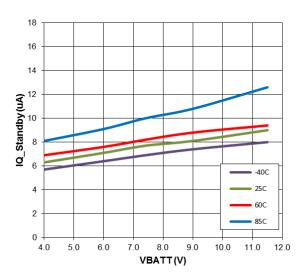

| Figure 5: IQ_Standby vs VBATT                       |    |

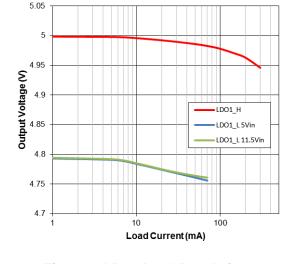

| Figure 6: LDO1 Load Regulation                      | 18 |

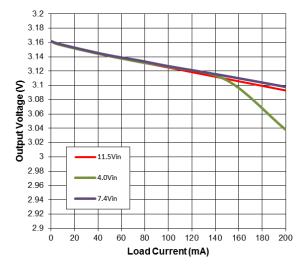

| Figure 7: LDO2 Load Regulation                      |    |

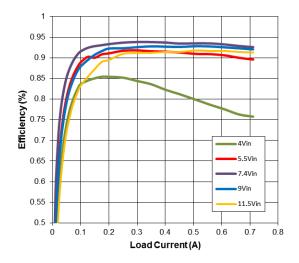

| Figure 8: Ch 1 Efficiency (Vout = 5.3 V)            | 19 |

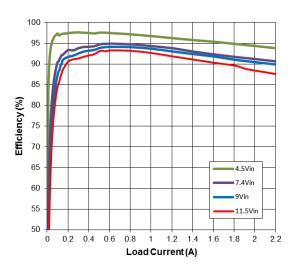

| Figure 9: Ch 2 Efficiency (Vout = 4.25 V)           |    |

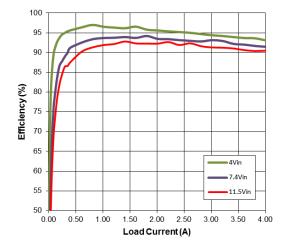

| Figure 10: Ch 3 Efficiency (Vout = 3.3 V)           |    |

| Figure 11: Ch 4 Efficiency (Vout = 4.0 V)           |    |

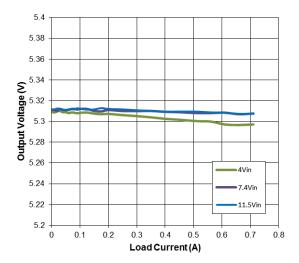

| Figure 12: Ch 1 Load Regulation                     |    |

| Figure 13: Ch 2 Load Regulation                     |    |

| Figure 14: Ch 3 Load Regulation                     |    |

| Figure 15: Ch 4 Load Regulation                     |    |

| Figure 16: Ch 1 Load Transient Response             |    |

| Figure 17: Ch 2 Load Transient Response             |    |

| Figure 18: Ch 3 Load Transient Response             |    |

| Figure 19: Ch 4 Load Transient Response             |    |

| Figure 20: CS1 Accuracy                             |    |

| Figure 21: CS2 Accuracy                             |    |

| Figure 22: CS3 Accuracy                             |    |

| Figure 23: Example Start-up Sequence                |    |

| Figure 24: Shutdown Sequence                        |    |

| Figure 25: Typical Application Schematic            |    |

| Figure 26: LDO1 and LDSW1 Architecture              |    |

| Figure 25: LDOT and LDSWT Atchitecture              |    |

| Figure 28: LDO Start-up Start-up and LDSW1 Timing   | 20 |

|                                                     |    |

| Figure 29: Operating State Transitions              |    |

| Figure 30: Sequencer, Enable, and FAULT logic       |    |

| Figure 31: Sequencer Start-Up Example               |    |

| Figure 32: Frequency Selection and Distribution     | 33 |

| Figure 33: OV and SC Fault Protection Example       | 35 |

| Figure 34: CS1 Functional Diagram                   |    |

| Figure 35: PGOOD Function                           |    |

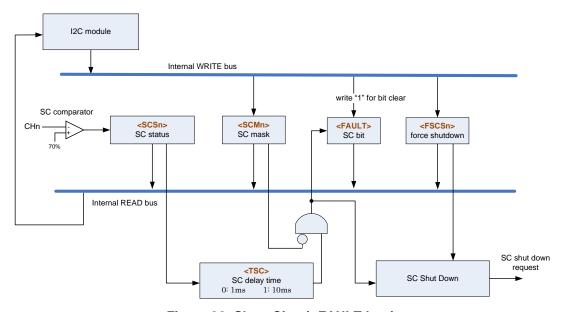

| Figure 36: Short Circuit FAULT Logic                | 43 |

| Figure 37: I <sup>2</sup> C Start (S) and Stop (P)  |    |

| Figure 38: Single Write Command                     |    |

| Figure 39: Consecutive Write Command                |    |

| Figure 40: Single Read Command (Two Methods)        |    |

| Figure 41: Sequential Address Multiple Read Command |    |

| Figure 42: PCB Layout Guidelines                    |    |

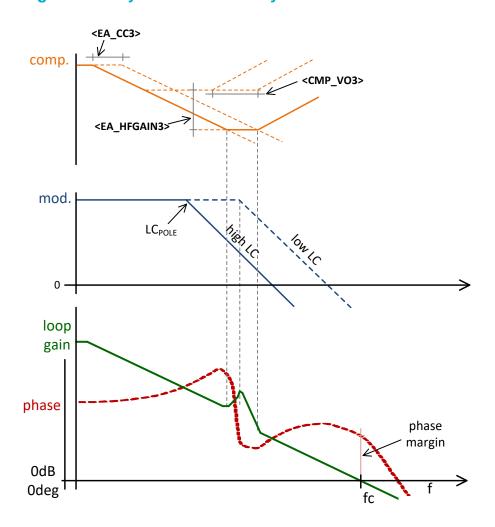

| Figure 43: Current Mode Loop Gain                   |    |

| Figure 44: Voltage Mode Loop Gain (Channel3)        |    |

| Figure 45: Package Outline Drawing                  | 80 |

| Tables                                              |    |

| Table 1: Pin Description                            | 7  |

| Table 1: Fill Description                           |    |

| Table 2: Absolute Maximum Ratings                   |    |

| Table 3: Absolute Maximum Ratings                   |    |

|                                                     |    |

| Table 5: DC Characteristics                         |    |

| Table 6: AC Characteristics                         |    |

| Table 7: I <sup>2</sup> C Timing Characteristics    | 17 |

|                                                     |    |

15-May-2019

# **DA6102**

| Table 8: Thermal Characteristics                                     | 17 |

|----------------------------------------------------------------------|----|

| Table 9: External Clock and Switching Frequency Selection            |    |

| Table 10: Recommended Slope Compensation Settings: CH1, CH2, and CH4 |    |

| Table 11: Recommended Inductor and Output Capacitor Values           | 40 |

| Table 12: Protection Features per Channel                            | 45 |

| Table 13: Register Map                                               | 52 |

| Table 14: Channel 1, 2, and 4 Optional Compensation Settings         | 77 |

| Table 15: Channel 3 Optional Compensation Settings                   | 78 |

| Table 16: MSL Classification                                         | 80 |

| Table 17: Ordering Information                                       | 81 |

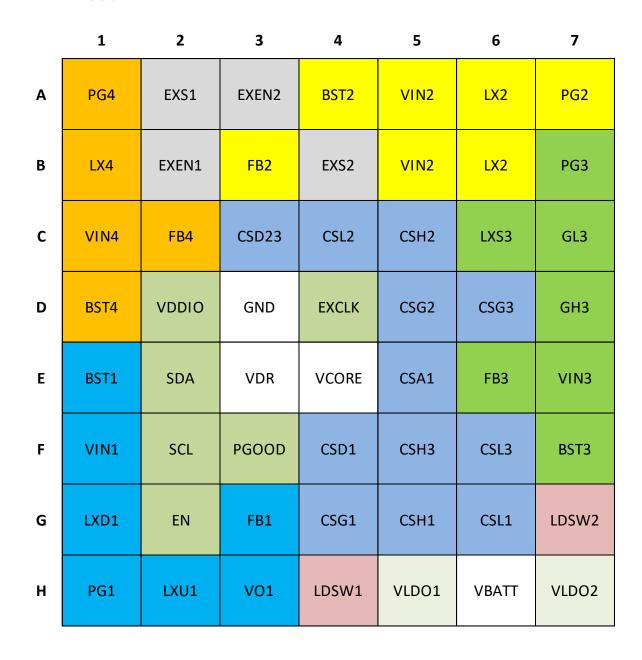

### 1 Pinout

#### **COLOR KEY:**

Figure 2: Connection Diagram (Top View)

**Table 1: Pin Description**

| Pin No.    | Pin Name      | Type (Table 2) | Description                                                                      |

|------------|---------------|----------------|----------------------------------------------------------------------------------|

| Voltage Ra | ails          | •              |                                                                                  |

| H6         | VBATT         | PS             | Supply voltage battery connection and LDO input supply                           |

| E3         | VDR           | PS             | Driver voltage input. Connect to VLDO1 and bypass with a 10 µF capacitor         |

| E4         | VCORE         | PS             | 1.5 V internal supply voltage, bypass with a 1 µF capacitor                      |

| D2         | VDDIO         | PS             | I/O voltage supply                                                               |

| D3         | GND           | GND            | Analog ground connection                                                         |

| System Di  | gital         |                |                                                                                  |

| G2         | EN            | DI             | Enable input                                                                     |

| F2         | SCL           | DI             | I <sup>2</sup> C clock input                                                     |

| E2         | SDA           | DIO            | I <sup>2</sup> C data I/O                                                        |

| D4         | EXCLK         | DI             | External clock sync input                                                        |

| F3         | PGOOD         | DO             | Power Good flag (open drain or cmos configurable)                                |

| LDOs and   | Load Switches |                |                                                                                  |

| H5         | VLDO1         | AO             | LDO1 output                                                                      |

| H7         | VLDO2         | AO             | LDO2 output                                                                      |

| H4         | LDSW1         | AO             | Load Switch 1 output                                                             |

| G7         | LDSW2         | Al             | Load Switch 2 input                                                              |

| CHANNEL    | . 1           |                |                                                                                  |

| F1         | VIN1          | PS             | Channel 1, power supply input                                                    |

| E1         | BST1          | AI             | Channel 1 bootstrap connection, connect a 100 nF capacitor from this pin to LXD1 |

| G1         | LXD1          | AO             | Channel 1, buck side switch node                                                 |

| H2         | LXU1          | AO             | Channel 1, boost side switch node                                                |

| НЗ         | VO1           | AO             | Channel 1 output voltage                                                         |

| G3         | FB1           | Al             | Channel 1, output voltage sense                                                  |

| H1         | PG1           | GND            | Channel 1 power ground                                                           |

| CHANNEL    | . 2           |                |                                                                                  |

| A5         | VIN2          | PS             | Channel 2, power supply input                                                    |

| B5         | VIN2          | PS             | Channel 2, power supply input                                                    |

| A4         | BST2          | AI             | Channel 2 bootstrap connection, connect a 100 nF capacitor from this pin to LX2  |

| A6         | LX2           | AO             | Channel 2, switch node                                                           |

| B6         | LX2           | AO             | Channel 2, switch node                                                           |

| В3         | FB2           | Al             | Channel 2, output voltage sense                                                  |

| A7         | PG2           | GND            | Channel 2 power ground                                                           |

| Pin No. | Pin Name      | Type<br>(Table 2) | Description                                                                      |

|---------|---------------|-------------------|----------------------------------------------------------------------------------|

| CHANNEL | 3             |                   |                                                                                  |

| E7      | VIN3          | Al                | Channel 3, power supply input                                                    |

| F7      | BST3          | Al                | Channel 3 bootstrap connection, connect a 100 nF capacitor from this pin to LXS3 |

| D7      | GH3           | AO                | Channel 3, high side gate drive                                                  |

| C6      | LXS3          | Al                | Channel 3, switch node sense connection                                          |

| C7      | GL3           | AO                | Channel 3, low side gate drive                                                   |

| E6      | FB3           | Al                | Channel 3, output voltage feedback                                               |

| В7      | PG3           | GND               | Global power ground, connect to GND plane                                        |

| CHANNEL | 4             |                   |                                                                                  |

| C1      | VIN4          | PS                | Channel 4, power supply input                                                    |

| D1      | BST4          | Al                | Channel 4 bootstrap connection, connect a 100 nF capacitor from this pin to LX4  |

| B1      | LX4           | AO                | Channel 4, switch node                                                           |

| C2      | FB4           | Al                | Channel 4, output voltage feedback                                               |

| A1      | PG4           | GND               | Channel 4 power ground                                                           |

| CURRENT | SENSE 1       |                   |                                                                                  |

| G4      | CSG1          | AO                | Current Sense 1, circuit breaker gate drive                                      |

| G5      | CSH1          | Al                | Current Sense 1, high side sense                                                 |

| G6      | CSL1          | Al                | Current Sense 1, low side sense                                                  |

| E5      | CSA1          | AO                | Current Sense 1 analog output voltage                                            |

| F4      | CSD1          | DO                | Current Sense 1, current limit flag                                              |

| CURRENT | SENSE 2 and 3 |                   |                                                                                  |

| D5      | CSG2          | AO                | Current Sense 2, gate drive output                                               |

| C5      | CSH2          | Al                | Current Sense 2, high side sense                                                 |

| C4      | CSL2          | Al                | Current Sense 2, low side sense                                                  |

| D6      | CSG3          | AO                | Current Sense 3, gate drive output                                               |

| F5      | CSH3          | Al                | Current Sense 3, high side sense                                                 |

| F6      | CSL3          | Al                | Current Sense 3, low side sense                                                  |

| C3      | CSD23         | DO                | Current Sense 2 and 3, open drain current limit flag                             |

| EXTERNA | L LDOs        |                   |                                                                                  |

| B2      | EXEN1         | DO                | External LDO1 enable output                                                      |

| A2      | EXS1          | Al                | External LDO1 voltage sense input                                                |

| А3      | EXEN2         | DO                | External LDO2 enable output                                                      |

| B4      | EXS2          | Al                | External LDO2 voltage sense input                                                |

**Table 2: Pin Type Definition**

| Pin type | Description          | Pin type | Description          |

|----------|----------------------|----------|----------------------|

| DI       | Digital Input        | Al       | Analog Input         |

| DO       | Digital Output       | AO       | Analog Output        |

| DIO      | Digital Input/Output | AIO      | Analog Input/Output  |

| GND      | Ground               | PS       | Power Supply Voltage |

## 2 Absolute Maximum Ratings

Stresses beyond those listed under Absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 3: Absolute Maximum Ratings**

| Parameter          | Description                                                                                           | Conditions (Note 1) | Min                   | Max                                                      | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------------------------------------------|------|

| TA                 | Operating ambient temperature                                                                         |                     | -40                   | +85                                                      | °C   |

| Ts                 | Storage temperature                                                                                   |                     | -60                   | +150                                                     | °C   |

| Vватт              | Supply battery voltage (VBATT pin)                                                                    |                     | -0.3                  | 12.0                                                     | V    |

| V <sub>IN</sub>    | VINx, LXx, CSL1-2, CSH1-2,<br>CSG1-2                                                                  |                     | -0.3                  | VBATT + 0.3                                              | V    |

| V <sub>BST</sub>   | BSTx, GH3                                                                                             |                     | LX <sub>X</sub> - 0.3 | LX <sub>X</sub> + 5.5                                    | V    |

| V <sub>VO1</sub>   | VO1, LXU1, FB1                                                                                        |                     | -0.3                  | 6.5                                                      | V    |

| V <sub>VCORE</sub> | VCORE                                                                                                 |                     | -0.3                  | 1.8                                                      | V    |

| V <sub>DDIO</sub>  | VDDIO (Note 2)                                                                                        |                     | -0.3                  | 5.5                                                      | V    |

| V <sub>LOGIC</sub> | SDA, SCL, CSD1, CSD23,<br>EXENx                                                                       |                     | -0.3                  | VDDIO +<br>0.3                                           | V    |

| Vsignal            | FBx, GL3, VDR, EXSx,<br>VLDO1, VLDO2, EN,<br>PGOOD, LDSW1, LDSW2,<br>CSA1, CSL3, CSH3, CSG3,<br>EXCLK |                     | -0.3                  | 5.5                                                      | V    |

| GND                | PGx                                                                                                   |                     | -0.3                  | +0.3                                                     | V    |

| .,                 |                                                                                                       | HBM (VIN3 – LXS3)   | ±1.0                  | 12.0  VBATT + 0.3  LXx + 5.5  6.5  1.8  5.5  VDDIO + 0.3 | kV   |

| V <sub>ESD</sub>   | ESD susceptibility (Note 3)                                                                           | HBM (Others)        | ±1.5                  |                                                          | kV   |

|                    |                                                                                                       | CDM                 | ±500                  |                                                          | V    |

- Note 1 All voltages are referenced to the GND pin.

- Note 2 VDDIO is not allowed to be higher than VBATT.

- Note 3 Compliance with ESD-HBM as defined in ANSI/ESDA/JEDEC JS-001-2014. Compliance with ESD-CDM as defined in JEDEC JESD22-C101

# 3 Recommended Operating Conditions

**Table 4: Recommended Operating Conditions**

| Parameter                           | Description                    | Conditions | Min | Тур | Max  | Unit |

|-------------------------------------|--------------------------------|------------|-----|-----|------|------|

| VBATT                               | Battery supply voltage         |            | 4.5 |     | 11.5 | V    |

| V <sub>DDIO</sub>                   | I/O supply voltage             |            | 1.5 |     | 5.0  | V    |

| V <sub>IN1</sub> , V <sub>IN3</sub> | Channel 1 and 3 supply voltage |            | 4.5 |     | 11.5 | V    |

| V <sub>IN2</sub> , V <sub>IN4</sub> | Channel 2 and 4 supply voltage |            | 5.0 |     | 11.5 | V    |

### 4 Electrical Characteristics

### **Table 5: DC Characteristics**

(Unless otherwise noted, VBATT = 7.4 V, VDDIO = 1.8 V, TA = -40  $^{\circ}$ C to +85  $^{\circ}$ C)

| Parameter            | Description                               | Conditions                                        | Min | Тур  | Max  | Unit |

|----------------------|-------------------------------------------|---------------------------------------------------|-----|------|------|------|

| System Spe           | ecifications                              |                                                   |     |      |      |      |

| IQ_ <sub>STBY</sub>  | Standby quiescent current                 | EN=Low, CS1 disabled (-40°C to 60°C)              |     | 6    | 12   | uA   |

| IQ_stby              | Standby quiescent current                 | EN=Low, CS1 disabled (85°C)                       |     |      | 20   | uA   |

| IQ_EN                | Non-switching quiescent current           | EN=HIGH CH1 to 4 disabled CS1 enabled             |     | 695  |      | uA   |

| IQ_ <sub>VDDIO</sub> | VDDIO quiescent current                   |                                                   |     | 0.14 |      | uA   |

| \/                   | VBATT under-voltage                       | VBATT falling                                     |     | 2.9  |      | V    |

| Vuvlo_batt           | lockout                                   | VBATT rising                                      |     | 3.8  | 4.0  | V    |

| Vuvlo_vdr            | VDR under-voltage threshold               | VDR falling (VD5 fault)<br>EN=high                |     | 3.55 | 3.60 | V    |

| Vvcore               | VCORE voltage                             |                                                   |     | 1.5  |      | V    |

| Fosc                 | Switching frequency range                 |                                                   | 1   |      | 3    | MHz  |

| Fosc_acc             | Switching frequency accuracy              | All frequency settings<br><ex_osc> = low</ex_osc> | -2  |      | +2   | %    |

| F <sub>EX_OSC</sub>  | External sync oscillator frequency range  |                                                   | 1.4 |      | 3    | MHz  |

| D <sub>EX_</sub> OSC | External sync oscillator duty cycle range |                                                   | 40  |      | 60   | %    |

| T <sub>SS</sub>      | Soft-start time accuracy                  | CH1 to 4, all SS settings                         | -5  |      | +5   | %    |

| T <sub>I2C</sub>     | I <sup>2</sup> C start-up time            | From UVLO release                                 |     |      | 10   | ms   |

| LDOs                 |                                           |                                                   |     |      |      |      |

| V <sub>LDO1_L</sub>  | LDO1 standby output voltage (LDO1-L)      | EN=low<br>5.0 V < VBATT < 11.5 V                  | 4.7 | 4.8  | 4.9  | V    |

| V <sub>LDO1_H</sub>  | LDO1 operating output voltage (LDO1-H)    | CH1 > 5.3 V                                       | 4.9 | 5.0  | 5.1  | V    |

| Parameter               | Description                                | Conditions                                                    | Min  | Тур   | Max  | Unit |

|-------------------------|--------------------------------------------|---------------------------------------------------------------|------|-------|------|------|

| V <sub>TH_IN_LDO1</sub> | LDO1 input switch                          | VO1 rising                                                    |      |       | 5.1  | V    |

|                         | threshold                                  | VO1 falling                                                   |      | 5.0   |      | V    |

| V <sub>DO_1_L</sub>     | LDO1_L dropout voltage                     | VBATT = 4.8 V, 25 mA                                          |      | 0.13  |      | V    |

| V <sub>DO_1_H</sub>     | LDO1_H dropout voltage                     | CH1 = 5.1 V, 100 mA                                           |      | 0.11  |      | V    |

| $\Delta V_{LDO1\_L}$    | LDO1_L load regulation                     | VBATT = 7.4 V<br>0 mA to 25 mA                                |      | 0.024 |      | %/mA |

| $\Delta V_{LDO1\_H}$    | LDO1_H load regulation                     | CH1 = 5.3 V<br>0 mA to100 mA                                  |      | 4.4   |      | %/A  |

| I <sub>LDO1_H</sub>     | LDO1_H current limit                       | CH1 > 5.2 V                                                   | 300  | 510   |      | mA   |

| I <sub>LDO1_L</sub>     | LDO1_L current limit                       | CH1 < 5.2 V                                                   | 70   | 110   |      | mA   |

| V <sub>LDO2</sub>       | LDO2 output voltage range                  |                                                               | 3.12 |       | 3.27 | V    |

| V <sub>VLDO2</sub>      | LDO2 output voltage accuracy               | Default value = 3.12 V<br>3.3 V < VBATT (or LDSW2)<br><11.5 V | -2   |       | +2   | %    |

| $\Delta V_{LDO2}$       | LDO2 load regulation                       | 0 A to 100 mA                                                 |      | 11    |      | %/A  |

| I <sub>LDO2</sub>       | LDO2 current limit                         |                                                               | 200  | 270   |      | mA   |

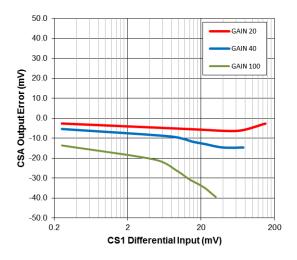

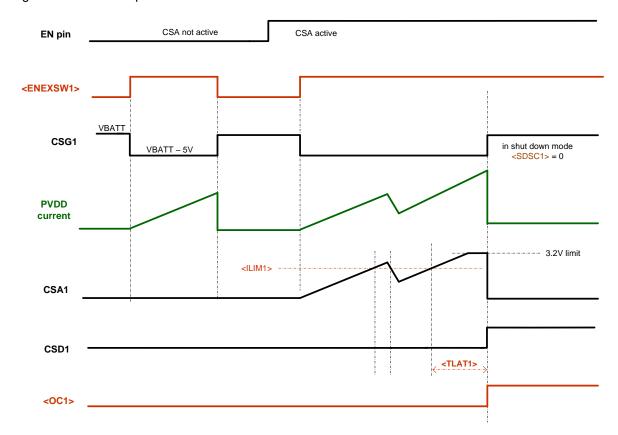

| Current Ser             | nse, Load Switches, and Cir                | cuit Breaker                                                  |      |       |      |      |

| VCMcs_1                 | CSH1 and CSL1 input voltage range          | Common mode                                                   |      |       | 11.5 | V    |

| VDMcs_1                 | CSH1 and CSL1 input voltage range          | Differential mode                                             |      |       | 150  | mV   |

| Acs <sub>1_2</sub>      | Current sense 1 amplifier gain             | setting 1                                                     |      | 20    |      | V/V  |

| Acs <sub>1_3</sub>      | Current sense 1 amplifier gain             | setting 2                                                     |      | 40    |      | V/V  |

| A <sub>CS1_4</sub>      | Current sense 1 amplifier gain             | setting 3                                                     |      | 100   |      | V/V  |

| Vcsa1                   | CSA1, current sense output accuracy        | CSA1 > 2.0 V<br>setting 1, 2                                  | -1   |       | +1   | %    |

| V <sub>CSA1_3</sub>     | CSA1, current sense output accuracy        | CSA1 > 2.0 V<br>setting 3                                     | -2.5 |       | +2.5 | %    |

| V <sub>CSA1</sub>       | CSA1, current sense output accuracy        | CSA1 < 2.0 V<br>setting 1, 2                                  | -20  |       | +20  | mV   |

| Vcsa1_3                 | CSA1, current sense output accuracy        | CSA1 < 2.0 V<br>setting 3                                     | -50  |       | +50  | mV   |

| V <sub>CSG1</sub>       | CSG1 PGATE drive voltage                   | CSG1 gate drive low referenced to VBATT                       |      | -4.5  | -4.0 | V    |

| Ron_cs1                 | CSG1 sink resistance                       | CSG1 gate drive low                                           |      | 0.7   | 1    | kΩ   |

| Rcsg1                   | CSG1 pull-up resistance                    | CSG1 gate drive high                                          |      | 0.7   |      | MΩ   |

| V <sub>OC_CS1</sub>     | Current Sense 1 Over-<br>Current threshold | CSH1-CSL1 register programmable                               | -2   |       | +2   | %    |

| Ts_cs1                  | Current Sense 1 settling time              | At CSA1                                                       |      | 5     |      | us   |

| Parameter                     | Description                                | Conditions                                       | Min  | Тур  | Max  | Unit |

|-------------------------------|--------------------------------------------|--------------------------------------------------|------|------|------|------|

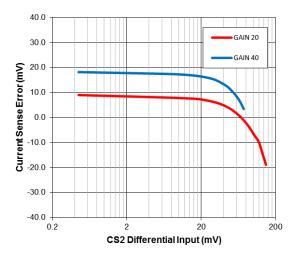

| Acs <sub>2_1</sub>            | Current Sense 2 Amplifier gain             | setting 1                                        |      | 20   |      | V/V  |

| Acs2_2                        | Current Sense 2 Amplifier gain             | setting 2                                        |      | 40   |      | V/V  |

| Vcsg2                         | Current Sense 2 PGATE drive voltage        | CSG2 gate drive low referenced to CSL2           |      | -4.5 | -4.0 | V    |

| Ron_cs2                       | CSG2 sink resistance                       | CSG2 gate drive low                              |      | 0.7  | 1    | kΩ   |

| Rcsg2                         | CSG2 pull-up resistance                    | CSG2 gate drive high                             |      | 700  |      | kΩ   |

| Voc_cs2                       | Current Sense 2 Over-<br>Current threshold | CSH2-CSL2, register programmable                 | -2   |      | +2   | %    |

| Acs3_1                        | Current sense 3 Amplifier gain             | setting 1                                        |      | 20   |      | V/V  |

| A <sub>CS3_2</sub>            | Current sense 3 Amplifier gain             | setting 2                                        |      | 40   |      | V/V  |

| V <sub>CSG3</sub>             | Current Sense 3 PGATE drive voltage        | CSG3 gate drive low referenced to CSL3           | 0    |      | 0.3  | V    |

| Ron_cs3                       | CSG3 sink resistance                       | CSG3 gate drive low                              |      | 0.5  | 1    | kΩ   |

| Rcsg3                         | CSG3 pull-up resistance                    | CSG3 gate drive high                             |      | 700  |      | kΩ   |

| Voc_cs3                       | Current Sense 3 Over-<br>Current threshold | CSH3-CSL3, register programmable                 | -2   |      | +2   | %    |

| Ron_LDSW1                     | Load switch 1 Rds_on                       | LDSW1F (0x22) = 0<br>LDO1 > 4.5 V                |      | 0.55 | 0.85 | Ω    |

| Ron_ldsw1_                    | Load switch 1 Rds_on<br>Force-On mode      | LDSW1F (0x22) = 1                                |      | 0.10 | 0.23 | Ω    |

| VLIM_LDSW1                    | Load switch 1 input limit voltage          | Falling voltage at LDO1_H increases LDSW1 Rds_on | 4.4  | 4.5  |      | V    |

| Tss_ldsw1                     | Load switch 1 soft-start period            | Iss_LDSW1 current limited                        |      | 1    |      | ms   |

| I <sub>SS_LDSW1</sub>         | Load switch 1 soft-start current limit     |                                                  | 45   | 70   | 150  | mA   |

| RDIS_LDSW1                    | Load switch 1 discharge resistance         | EN5 = low<br>DISC5 (0x18) = 0                    | 70   | 100  | 130  | Ω    |

| R <sub>ON_LDSW2</sub>         | Load switch 2 Rds_on                       |                                                  |      |      | 0.24 | Ω    |

| ILIM_LDSW2                    | Load switch 2 start-up limit               |                                                  |      | 50   | 100  | mA   |

| T <sub>SS_LDSW2</sub>         | Load switch 2 start-up time                |                                                  |      | 1    |      | ms   |

| Channel 1                     |                                            |                                                  | •    |      |      | •    |

| V <sub>CH1</sub>              | Channel 1 output voltage range             | Register programmable in 50 mV steps             | 5.1  |      | 5.8  | V    |

| V <sub>VO1</sub>              | Channel 1 output voltage accuracy          | Default setting = 5.3 V<br>5.0 V < VIN1 < 11.5 V | -2.5 |      | +2.5 | %    |

| $\Delta V_{\text{VO1\_LOAD}}$ | Channel 1 load regulation                  | Default setting 0 A to 400 mA                    |      | 0.1  |      | %/A  |

| I <sub>LIM_1</sub>            | Channel 1 current limit threshold          | Peak inductor current                            | 2.0  | 2.6  |      | Α    |

| Parameter              | Description                               | Conditions                                      | Min  | Тур  | Max  | Unit |

|------------------------|-------------------------------------------|-------------------------------------------------|------|------|------|------|

| Toff_MIN_A1            | Channel 1 buck minimum off time           | At LXD1 (LXU1 boost turn-<br>on threshold)      |      | 83   |      | ns   |

| TON_MIN_A1             | Channel 1 buck minimum on time            | At LXD1                                         |      | 100  |      | ns   |

| Rds_on_a1H             | Channel 1 buck high side on resistance    |                                                 |      | 154  |      | mΩ   |

| Rds_on_a1L             | Channel 1 buck low side on resistance     |                                                 |      | 183  |      | mΩ   |

| R <sub>DS_ON_B1H</sub> | Channel 1 boost high side on resistance   |                                                 |      | 121  |      | mΩ   |

| R <sub>DS_ON_B1L</sub> | Channel 1 boost low side on resistance    |                                                 |      | 147  |      | mΩ   |

| R <sub>DISC1</sub>     | Channel 1 output discharge resistance     | EN=low, NDISC1 (0x18)=0                         | 70   | 100  | 130  | Ω    |

| Channel 2              |                                           |                                                 |      |      |      |      |

| V <sub>CH2</sub>       | Channel 2 output voltage range            | Register programmable in 50 mV steps            | 3.00 |      | 4.55 | V    |

| V <sub>VO2</sub>       | Channel 2 output voltage accuracy         | Default setting: 3.3 V<br>5.0 V < VIN1 < 11.5 V | -2.5 |      | +2.5 | %    |

| $\Delta V$ vo2_load    | Channel 2 load regulation                 | Default setting: 0 A to 2.2 A                   |      | 0.02 |      | %/A  |

| I <sub>LIM_2</sub>     | Channel 2 current limit threshold         | Peak inductor current                           | 3.6  | 5.0  |      | А    |

| Toff_MIN_2             | Channel 2 minimum off time                | At LX2                                          |      | 83   |      | ns   |

| T <sub>ON_MIN_2</sub>  | Channel 2 minimum on time                 | At LX2                                          |      | 100  |      | ns   |

| R <sub>DS_ON_2H</sub>  | Channel 2 high side on resistance         |                                                 |      | 107  |      | mΩ   |

| R <sub>DS_ON_2L</sub>  | Channel 2 low side on resistance          |                                                 |      | 123  |      | mΩ   |

| R <sub>DISC2</sub>     | Channel 2 output discharge resistance     | EN=low<br>NDISC2 (0x18)=0                       | 70   | 100  | 130  | Ω    |

| Channel 3              |                                           |                                                 |      | .1   | .1   |      |

| Vснз                   | Channel 3 output voltage range            | Register programmable in 50 mV steps            | 3.00 |      | 3.75 | V    |

| V <sub>VO3</sub>       | Channel 3 output voltage accuracy         | Default setting: 3.3 V<br>4.5 V < VIN1 < 11.5 V | -2.5 |      | +2.5 | %    |

| ΔVvo3_load             | Channel 3 load regulation                 | Default setting: 0 A to 4 A                     |      | 0.02 |      | %/A  |

| V <sub>ILIM_3_0</sub>  | Channel 3 current limit threshold voltage | EXTFET (0x21) = 0<br>VIN3-LXS3                  | 240  | 270  | 300  | mV   |

| VILIM_3_1              | Channel 3 current limit threshold voltage | EXTFET (0x21) = 1<br>VIN3-LXS3                  | 120  | 135  | 150  | mV   |

| T <sub>OFF_MIN_3</sub> | Channel 3 minimum off time                | At GH3                                          |      | 83   |      | ns   |

| Ton_min_3              | Channel 3 minimum on time                 | At GH3                                          |      | 100  |      | ns   |

| Parameter              | Description                                  | Conditions                                      | Min  | Тур  | Max  | Unit  |

|------------------------|----------------------------------------------|-------------------------------------------------|------|------|------|-------|

| R <sub>SO3_H</sub>     | Channel 3 high side driver source resistance |                                                 |      | 1.1  |      | Ω     |

| R <sub>SK3_H</sub>     | Channel 3 high side driver sink resistance   |                                                 |      | 0.9  |      | Ω     |

| R <sub>SO3_L</sub>     | Channel 3 low side driver source resistance  |                                                 |      | 1.1  |      | Ω     |

| Rsk3_L                 | Channel 3 low side driver sink resistance    |                                                 |      | 0.9  |      | Ω     |

| R <sub>DISC3</sub>     | Channel 3 output discharge resistance        | EN=low, NDISC3 (0x18)=0                         | 70   | 100  | 130  | Ω     |

| Channel 4              |                                              |                                                 |      |      |      |       |

| V <sub>CH4</sub>       | Channel 4 output voltage range               | Register programmable in 50 mV steps            | 3.20 |      | 4.20 | V     |

| V <sub>VO4</sub>       | Channel 4 output voltage accuracy            | Default setting: 4.0 V<br>5.0 V < VIN1 < 11.5 V | -2.5 |      | +2.5 | %     |

| $\Delta V_{VO4\_LOAD}$ | Channel 4 load regulation                    | Default setting: 0 A to 0.6 A                   |      | 0.08 |      | %/A   |

| I <sub>LIM_4</sub>     | Channel 4 current limit threshold            | Peak inductor current                           | 2.0  | 2.6  |      | А     |

| T <sub>OFF_MIN_4</sub> | Channel 4 minimum off time                   | At LX4                                          |      | 83   |      | ns    |

| T <sub>ON_MIN_4</sub>  | Channel 4 minimum on time                    | At LX4                                          |      | 100  |      | ns    |

| Rds_on_4H              | Channel 4 high side on resistance            |                                                 |      | 342  |      | mΩ    |

| R <sub>DS_ON_4L</sub>  | Channel 4 low side on resistance             |                                                 |      | 342  |      | mΩ    |

| R <sub>DISC4</sub>     | Channel 4 output discharge resistance        | EN=low<br>NDISC4 (0x18)=0                       | 70   | 100  | 130  | Ω     |

| Fault Detec            | tion                                         |                                                 |      | •    | •    | 1     |

| $V_{PGOOD\_H}$         | Power good rising threshold                  | CH1 to 4<br>VOx rising                          |      | 90   |      | %     |

| V <sub>PGOOD_L</sub>   | Power good falling threshold                 | CH1 to 4<br>VOx falling                         |      | 85   |      | %     |

| SCP                    | Short Circuit Protection threshold           | CH1 to 4 and LDSW1, falling                     |      | 70   |      | %     |

| OVP                    | Over-Voltage Protection threshold            | CH2 to 4<br>VOx rising                          |      | 120  |      | %     |

| OVP_1                  | CH1 Over-Voltage<br>Protection threshold     | VO1 rising                                      |      | 110  |      | %     |

| $V_{PGOOD\_EX}$        | EXS1-2 power good accuracy                   |                                                 |      | TBD  |      | +/-mV |

| V <sub>PGOOD_EXL</sub> | EXS1-2 power good hysteresis                 | PG7 and PG8 status low                          |      | -100 |      | mV    |

| TSD                    | Thermal Shut Down threshold                  |                                                 |      | 150  |      | °C    |

| Parameter           | Description                    | Conditions                                      | Min            | Тур | Max            | Unit |

|---------------------|--------------------------------|-------------------------------------------------|----------------|-----|----------------|------|

| Digital             |                                |                                                 |                |     | •              |      |

| V <sub>IH</sub>     | Input High Voltage             | EXCLK, EN                                       | 1.2            |     |                | V    |

| VIL                 | Input Low Voltage              | EXCLK, EN                                       |                |     | 0.3            | V    |

| VIH_I2C             | Input High Voltage             | SCL, SDA                                        | VDDIO<br>x 0.7 |     |                | V    |

| V <sub>IL_I2C</sub> | Input Low Voltage              | SCL, SDA                                        |                |     | 0.3 x<br>VDDIO | V    |

| Vон                 | Output High Voltage            | CSD1, EXEN1-2, PGOOD (cmos mode) 1 mA source    | VDDIO<br>x 0.7 |     |                | V    |

| VoL                 | Output Low Voltage             | CSD1, EXEN1-2<br>PGOOD (cmos mode)<br>1 mA sink |                |     | 0.3 x<br>VDDIO | V    |

| VoL                 | Output Low Voltage             | SDA at < 3 mA sink current                      |                |     | 0.4            | V    |

| RPGOOD              | Power Good pulldown resistance | Open drain mode                                 |                |     | 100            | Ω    |

### **Table 6: AC Characteristics**

External components are as shown in Figure 25, VBATT = 7.4 V, TA = 25 °C

| Parameter            | Description                     | Conditions                                                        | Min | Тур | Max | Unit  |

|----------------------|---------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| VTR <sub>LO_1A</sub> | CH1 load transient response     | Io=0 A to 400 mA<br>50 mA/µs<br>Fsw = 2MHz                        |     |     | 85  | +/-mV |

| VTR <sub>LO_1B</sub> | CH1 load transient response     | Io= 0 A to 300 mA<br>1 mA/µs<br>Fsw = 2 MHz                       |     |     | 85  | +/-mV |

| VTR <sub>LI_1</sub>  | CH1 line transient response     | VBATT = 5.5 V to 10.5 V<br>0.1 V/μs<br>Fsw = 2 MHz<br>Io = 200 mA |     |     | 150 | +/-mV |

| VTR <sub>LO_2A</sub> | CH2 load transient response     | Io = 0 A to 2.2 A<br>250 mA/µs<br>Fsw = 2 MHz                     |     |     | 400 | +/-mV |

| VTR <sub>LO_2B</sub> | CH2 60% load transient response | Io = 0 A to 1.3 A<br>4 mA/μs<br>Fsw = 2 MHz                       |     |     | 80  | +/-mV |

| VTR <sub>LI_2</sub>  | CH2 line transient response     | VBATT = 5.5 V to 10.5 V<br>0.1 V/µs<br>Fsw = 2 MHz<br>Io = 1 A    |     |     | 150 | +/-mV |

| VTR <sub>LO_3A</sub> | CH3 load transient response     | Io = 0 A to 1 A<br>55 mA/μs<br>Fsw = 1 MHz                        |     |     | 90  | +/-mV |

| VTR <sub>LO_3B</sub> | CH3 60% load transient response | Io = 0 A to 660 mA<br>55 mA/μs<br>Fsw = 1 MHz                     |     |     | 80  | +/-mV |

| VTR <sub>LI_3</sub>  | CH3 line transient response     | VBATT = 5.5 V to 10.5 V<br>0.1 V/µs<br>Fsw = 1 MHz<br>Io = 1 A    |     |     | 70  | +/-mV |

| VTR <sub>LO_4A</sub> | CH4 load transient response     | Io =0 A to 600 mA<br>50 mA/µs<br>Fsw = 2 MHz                      |     |     | 150 | +/-mV |

| VTR <sub>LO_4B</sub> | CH4 60% load transient response | Io = 100 mA to 450 mA<br>50 mA/µs<br>Fsw = 2 MHz                  |     |     | 85  | +/-mV |

| VTR <sub>LI_4</sub>  | CH4 line transient response     | VBATT = 5.5 V to 10.5 V<br>0.1 V/μs<br>Fsw = 2 MHz<br>Io = 300 mA |     |     | 100 | +/-mV |

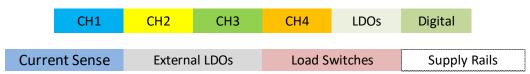

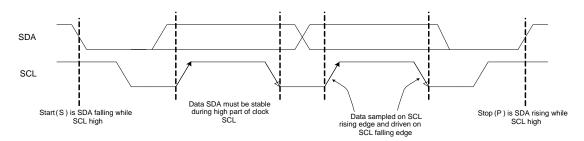

Figure 3: I<sup>2</sup>C Timing

# 5 Timing Characteristics

### Table 7: I<sup>2</sup>C Timing Characteristics

$(VBATT = 7.4 \text{ V}, VDDIO = 1.8 \text{ V}, TA = -40 ^{\circ}C \text{ to } +85 ^{\circ}C)$

| Parameter           | Description                 | Conditions                                        | Min | Тур | Max | Unit |

|---------------------|-----------------------------|---------------------------------------------------|-----|-----|-----|------|

| C <sub>BUS</sub>    | Bus line capacitive load    |                                                   |     |     | 400 | pF   |

| T <sub>SPK</sub>    | Spike suppression           | SDA and SCL input filters suppress spikes < 50 ns |     |     | 50  | ns   |

| FscL                | SCL frequency               |                                                   |     |     | 400 | kHz  |

| T <sub>STA</sub>    | Start condition set-up time |                                                   | 0.6 |     |     | μs   |

| T <sub>STA_HO</sub> | Start condition hold time   |                                                   | 0.6 |     |     | μs   |

| T <sub>STO</sub>    | Stop condition set-up time  |                                                   | 0.6 |     |     | μs   |

| T <sub>BUF</sub>    | Bus free time               | Between STOP and START                            | 1.3 |     |     | μs   |

| T <sub>SCL_L</sub>  | SCL clock low time          |                                                   | 0.6 |     |     | μs   |

| T <sub>SCL_H</sub>  | SCL clock high time         |                                                   | 0.6 |     |     | μs   |

| Tr                  | SCL, SDA rise time          | (input requirement)                               |     |     | 300 | ns   |

| Tf                  | SCL, SDA fall time          | (input requirement)                               |     |     | 300 | ns   |

| T <sub>DA</sub>     | Data set-up time            |                                                   | 100 |     |     | ns   |

| T <sub>DA_HO</sub>  | Data hold-time              |                                                   | 0   |     |     | ns   |

## **6 Thermal Characteristics**

**Table 8: Thermal Characteristics**

| Parameter | Description                            | Conditions (Note 1)                 | Тур | Unit |

|-----------|----------------------------------------|-------------------------------------|-----|------|

| θја_ј     | Junction to ambient thermal resistance | JEDEC standard, 2s4p                | 30  | °C/W |

| θЈА_Е     | Junction to ambient thermal resistance | Evaluation board, 6-layer           | 34  | °C/W |

| θјв       | Junction to board thermal resistance   | 1 mm from IC edge, evaluation board | 9.5 | °C/W |

Note 1 Based on simulation with no air flow and 2.0 W power dissipation.

## 7 Typical Performance

Unless otherwise noted, VBATT = 7.4 V, TA = 25 °C, external components as shown in Figure 25.

Figure 4: Frequency vs Temperature

Figure 6: LDO1 Load Regulation

(LDO1 input is Vo1: 5.3 V)

Figure 5: IQ\_Standby vs VBATT

Figure 7: LDO2 Load Regulation

90 85 75 70 65 60 55 50 0 0.1 0.2 0.3 0.4 0.5 0.6 Load Current (A)

100

95

Figure 8: Ch 1 Efficiency (Vout = 5.3 V)

Figure 11: Ch 4 Efficiency (Vout = 4.0 V)

Figure 9: Ch 2 Efficiency (Vout = 4.25 V)

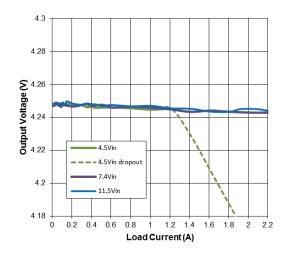

Figure 12: Ch 1 Load Regulation

Figure 10: Ch 3 Efficiency (Vout = 3.3 V)

Figure 13: Ch 2 Load Regulation

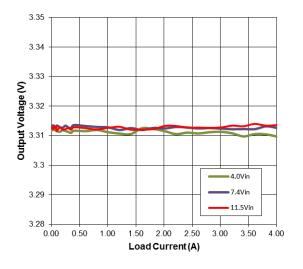

Figure 14: Ch 3 Load Regulation

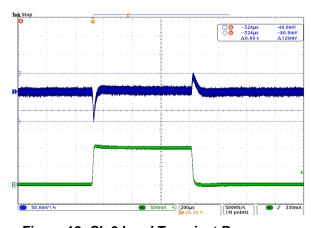

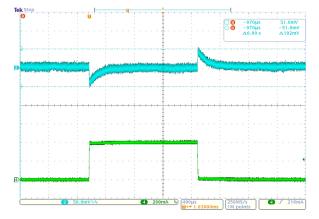

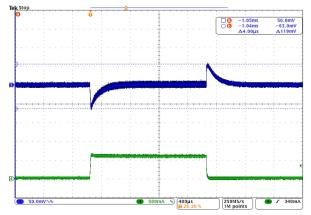

Figure 17: Ch 2 Load Transient Response (0 A to 2.2 A, 250 mA/µs)

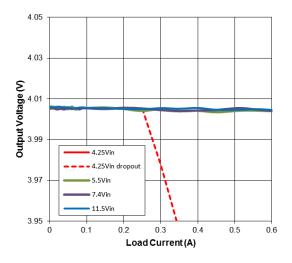

Figure 15: Ch 4 Load Regulation

Figure 18: Ch 3 Load Transient Response (0 A to 1.0 A, 55 mA/µs)

Figure 16: Ch 1 Load Transient Response

(0 A to 0.4 A, 50 mA/µs)

Figure 19: Ch 4 Load Transient Response (0 A to 0.6 A, 50 mA/µs)

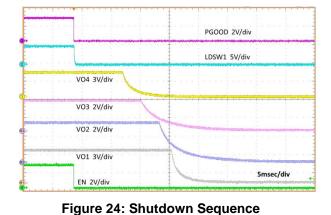

PGOOD 2V/div

LDSW1 5V/div

VO3 2V/div

VO4 3V/div

VO1 3V/div

EN 2V/div

2msec/div

Figure 23: Example Start-up Sequence

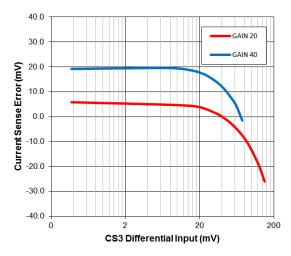

Figure 20: CS1 Accuracy

Figure 21: CS2 Accuracy

(Reverse mode, all channels discharge on)

Figure 22: CS3 Accuracy

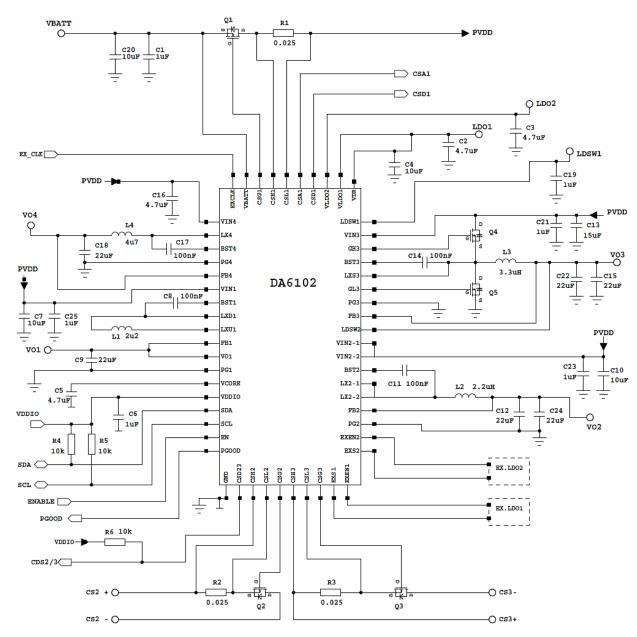

# 8 Typical Schematic

Figure 25: Typical Application Schematic

### 9 Functional Description

#### 9.1 General

The DA6102 is a multi-channel Power Management Integrated Circuit (PMIC) designed to operate from a widely varying input supply to regulate multiple high efficiency outputs. As a system power block, the DA6102 provides two always-on LDOs, a battery side current sense and circuit breaker, and fully configurable sequencing and fault protection. The PMIC also includes two integrated buck converters, an integrated BuckBoost converter, a buck controller, and two external voltage monitors. Default register values are set by One Time Programmable (OTP) for output voltages, fault behavior, switching frequency, start-up sequence, and many other functions. All register settings can also be programmed directly via the I<sup>2</sup>C interface.

Complete device functionality is described in detail below, where all component references refer to the Figure 25 schematic and register references refer to the register map in Table 13.

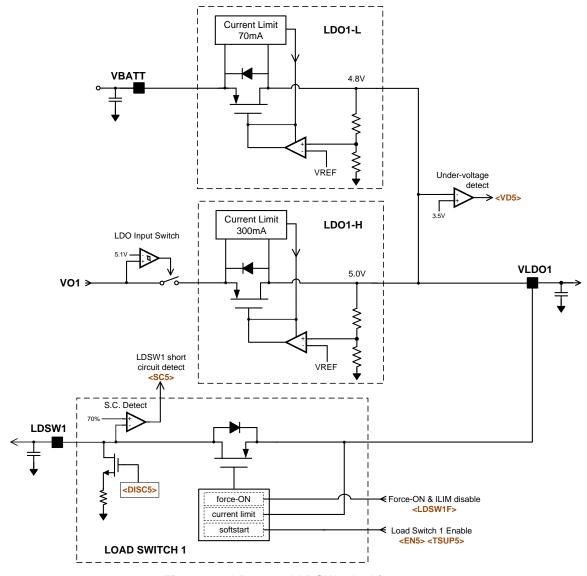

#### 9.2 Always-on LDOs and Internal Load Switches

LDO1 and LDO2 are always enabled regardless of battery voltage or EN pin state. Each LDO's output must be bypassed with a minimum capacitance of 4.7  $\mu$ F. For the LDOs and all other channels, it is recommended to use capacitors whose value is greater than 50 % of the nominal value at the operating voltage. A capacitor voltage rating of approximately twice the operating voltage is normally sufficient.

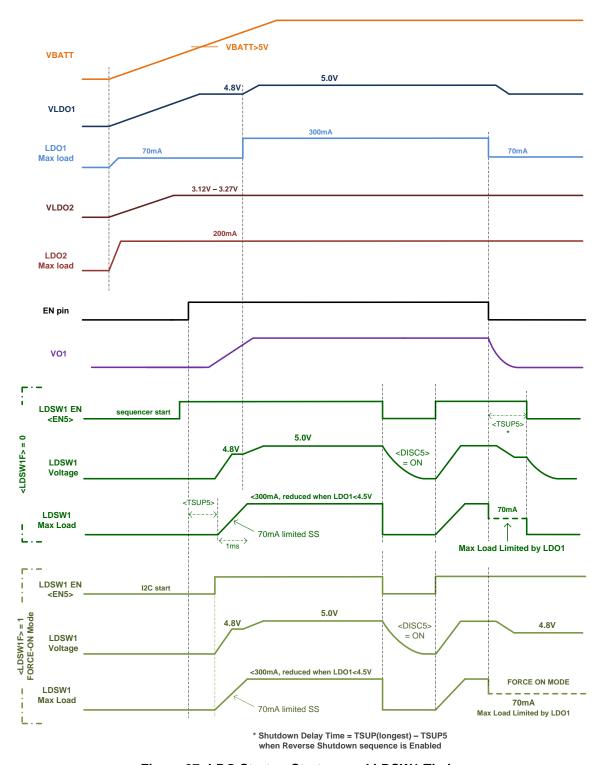

#### LDO1 and LDSW1

LDO1 operates in two states. When the Channel 1 output voltage is disabled or below the switch-over threshold (5.1 V typical), the LDO1 output voltage is set to 4.8 V. In this state, LDO1 is supplied directly from VBAT, and its load current capability is limited to 70 mA. In normal operation, with Channel1 enabled, the LDO1 input switches to Channel1 and its output is regulated at 5.0 V. In this state, the LDO1 current limit increases to 300 mA (minimum). Having two modes of operation improves system efficiency by reducing the input voltage to LDO1 when Channel 1 is available. In either state, LDO1 output accuracy is within  $\pm$  2% provided that its input supply is at least 200 mV above the target output voltage.

LDO1 connects internally to Load Switch 1, LDSW1, which is enabled and disabled via the EN1 register (0x05, D4). LDSW1 allows the always-on LDO voltage to be used as an independent channel with soft-start, sequencing, output discharge, current limit, and short circuit protection. To prevent overloading LDO1, LDSW1 begins limiting current when LDO1 drops below 4.5 V. However, as both outputs come from the same source, the combination of loads should not exceed the LDO1 current limit. LDSW1 soft-start is achieved by engaging a 70 mA current limit during the start-up period, thus preventing any sudden load steps on LDO1.

Additionally, LDSW1 has a Force-ON mode, set with the LDSW1F bit in register 0x22. In this mode, LDSW1 current limit is disabled and the on resistance is minimized. In Force-ON mode, LDSW1 is not controlled by the EN pin, but only by its EN1 register bit. If the EN pin is pulled low to shut down the PMIC channels, LDSW1 will remain on (along with LDO1 and LDO2) as shown in Figure 27 below. To prevent excessive droop on LDO1 when the EN pin is low, ensure that the LDSW1 current is below the 70 mA limit of LDO1.

Because Channel 1 serves as the primary supply for LDSW1 (via LDO1) in normal operation, an OV or SC fault shutdown on Channel 1 will cause LDSW1 to automatically switch off. This is the same functionality as FSCS and FOVS described in the short circuit and over-voltage protection sections.

Figure 26: LDO1 and LDSW1 Architecture

Figure 27: LDO Start-upStart-up and LDSW1 Timing

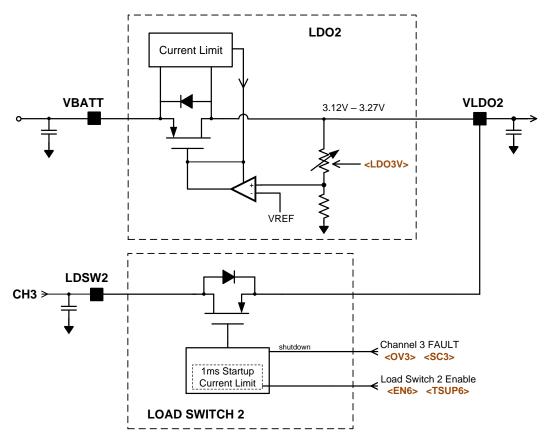

#### LDO2 and LDSW2

The LDO2 output voltage is programmable between 3.12 V and 3.27 V in 50 mV steps, from the CTL register (0x22, D5:4). The LDO2 current limit is fixed at 200 mA minimum, however there is no fault indicator associated with LDO2.

The LDO2 output is internally connected to Load Switch 2 (LDSW2). In a typical application when the PMIC is enabled, the LDO2 output will be bypassed by the higher efficiency switching regulator connected to the LDSW2 input. This is shown as Channel3 in Figure 28. This configuration improves system efficiency by eliminating the high losses of the LDO when in normal operation. With LDSW2

enabled through the EN1 register (0x05, D5) the voltage at VLDO2 is supplied through LDSW2. Note that the voltage at LDSW2 must be greater than the LDO2 set voltage. To ensure a smooth transition when LDSW2 is enabled, a fixed current limit is enforced for 1 ms. This limits glitches at VLDO2 and prevents reverse current from LDO2 to the supply connected to LDSW2. LDSW2 start-up delay can be programmed by sequencer but should only be enabled after the supply voltage (Channel3 typically) has reached its target.

Because Channel 3 typically serves as the primary supply for LDSW2 in normal operation, an OV or SC fault shutdown on Channel 3 will cause LDSW2 to automatically switch off. This is the same functionality as FSCS and FOVS, described in Section 9.12.

Figure 28: LDO2 and LDSW2 Architecture

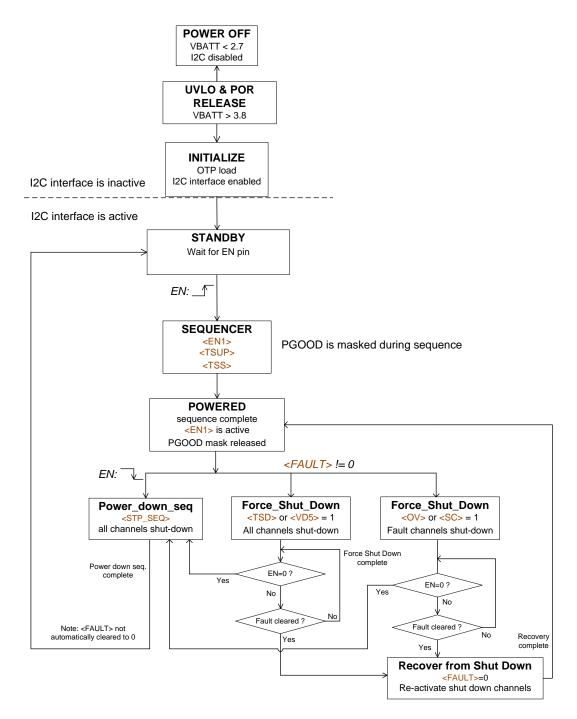

#### 9.3 ENABLE, UVLO, and Operating State Transitions

The DA6102 has multiple operating states including a low quiescent current standby mode and a wide hysteresis UVLO (Under-Voltage Lock-Out) feature that contribute to both a high system efficiency and robust performance. As the name implies, the always-on LDOs are always enabled, regardless of the state of the EN pin or battery voltage.

Referring to Figure 29, as the battery voltage increases from 0 V, the PMIC first crosses the upper UVLO threshold of approximately 3.8 V. Above this threshold the IC is initialized, allowing the OTP settings to be loaded and I²C communication becomes active. Once the UVLO is released, the DA6102 is in standby mode with input quiescent current less than 10  $\mu$ A. From the standby state, the EN pin can be driven high to start the sequencer and start up the desired channels. Once the sequencer begins starting the last channel, the PMIC is considered in Powered mode and all functions are active. Pulling the EN pin low at any time will start the powerdown sequencer and return the DA6102 to standby mode.

If the VBATT voltage drops to 2.9 V typical, the UVLO re-engages and all channels will shut down, including the CS blocks. However, the PMIC will not automatically restart if the VBATT voltage returns above 3.8 V. To restart after a UVLO event, the EN pin must be toggled. Below this lower UVLO threshold, all stored registers will be reset to their default values and the DA6102 is completely off with the exception of LDO1 and LDO2.

This large hysteresis in the UVLO circuit ensures that there is a high enough input voltage to support a smooth start-up with proper regulation, while at the same time giving additional headroom and time to keep the channels alive if the input voltage should droop during operation. Although all functions are active when the DA6102 is operating below 4 V, not all channels will be in regulation and some faults may be indicated such as under-voltage or current limit. To prevent momentary under-voltage droops at the input, follow all recommendations for input capacitors and use a minimum of 10  $\mu$ F at the VBATT pin.

The DA6102 has a secondary UVLO threshold of 3.5 V at the VDR pin, referred to as VD5, see Section 9.12. VDR is supplied by the Channel 1 BuckBoost via external connection the VLDO1 pin. Therefore, if Channel 1 is not enabled, the VDR UVLO will supersede the battery UVLO.

Figure 29: Operating State Transitions

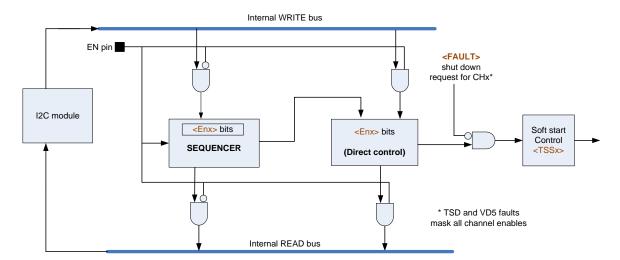

### 9.4 Sequencer and Soft-start

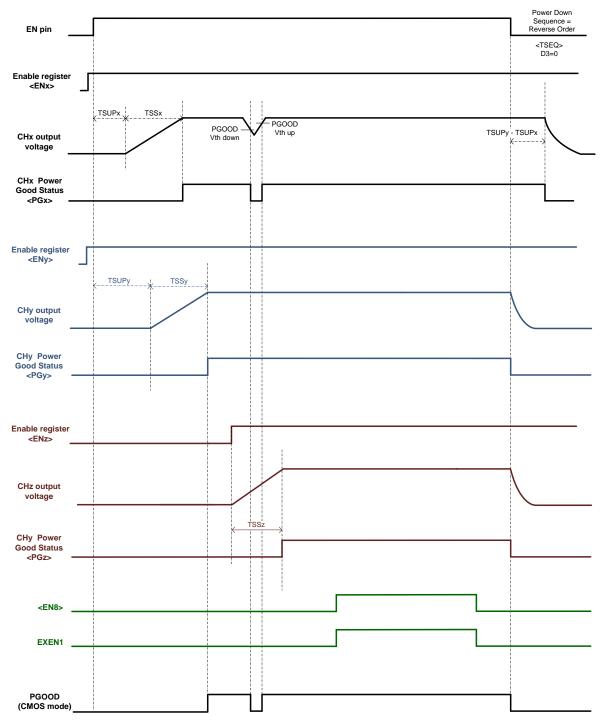

The DA6102 features an integrated start-up sequencer for eight of the channel blocks: CH1, CH2, CH3, CH4, EXEN1, EXEN2, LDSW1, and LDSW2. Each of these channels can be set to start either automatically by sequencer control, or by direct register control. To turn on sequencer control, set the appropriate bit in the EN1 register (0x05) to high before driving the EN pin high. When the EN pin goes high, the start-up delay timers are initiated. Delay time for each channel can be set between 0 ms and 32 ms in the TSUP12 through TSUP78 registers. The programmed delay time sets the time interval between the EN pin rising and the beginning of the soft-start ramp.

The external LDO channels (EXEN1 and EXEN2) are digital outputs. Therefore no soft-start time applies and they will go high immediately after the start-up delay time expires. LDSW1 has a fixed start-up current limit and will begin to ramp up the output once the start-up delay time expires. LDSW1 start-up time can be calculated as shown below. The fixed current limit allows up to 10  $\mu$ F to be charged within the 1 ms (typical) soft-start period.

$$T_{START-LDSW1} = \frac{C_{LDSW1} \times Vldo1}{70 \, mA}$$

LDSW2 also has a fixed current limit during start-up which is designed to limit reverse current; it is not a soft-start function.

Channels 1 through 4 include programmable soft-start times. After the delay time for a channel has completed, that channel's output voltage will begin to ramp up according to the programmed soft-start time, TSS. Soft-start times are set in the TSS register (0x10) with a range of 1 ms to 10 ms.

The soft-start function prevents output voltage overshoot and excessive inrush current by slowly ramping up the output voltage in a controlled manner. Faster soft-start times will result in higher inrush current; larger output capacitance will also increase inrush current. To prevent a pre-biased output from discharging during start-up, each channel operates in DCM within the first 75% of the soft-start ramp.

The PGOOD pin will remain low until the last channel in the sequence has completed its soft-start ramp and its power good status bit (PGS, 0x01) is high.

During sequencer start-up, the EN1 register bits (0x05) can be written, but any channels to be included in the sequence must be set before the EN pin goes high. Once the sequence is completed any channel can be disabled or enabled at any time through the EN1 register.

When a channel is enabled by EN1 direct register write (not in the sequencer) the TSUP delay time register settings are not applied. The soft-start ramp set by TSS will begin as soon as the EN1 bit is set high.

Figure 30: Sequencer, Enable, and FAULT logic

When the EN pin is pulled low, the shutdown sequencer is initiated. The shutdown sequencer can be set to shut down all channels immediately or in the reverse order from the start-up sequence. This option is available in the TSEQ register (0x11, D3). When shutting down in reverse order from start-up, all channels that were not initially set to sequenced start-up will be shut down immediately. Additionally there is no shutdown delay time applied to the first channel to shut down (last channel to start). Toggling a bit in the EN1 register after a sequenced start-up does not change a channel's status in sequenced shutdown.

Note that LDSW1 can be included in the start-up sequence, only if the LDSW1F bit (0x22) is set low. If LDSW1 is not in sequencer mode, it will be controlled only by the EN1 register and will not be shut down by the EN pin. After a FAULT shutdown, the EN pin can be toggled to restart the sequencer

and EN1 register bits can be written. However, channels that shut down will have their EN1 register bit outputs masked and will not turn on. Any FAULT condition must be first cleared by I<sup>2</sup>C write to allow the channel to restart. A channel will restart immediately if the FAULT condition is cleared while its EN1 register bit is high.

Figure 31: Sequencer Start-Up Example

### 9.5 Channel 1 to Channel 4, Common Features and Functionality

#### **Basic Buck Operation**

All four switching regulators are fixed frequency PWM control. Each switching regulator can support the full input voltage range up to 11.5 V and must be separately bypassed at the VIN pins. In steady state operation, a buck switching regulator works by alternately turning on the high side and low side switches with a duty cycle controlled to regulate the output voltage. When the high side turns on, LX equals VIN, the voltage across the inductor is Vin-Vout and inductor current ramps up. When the low side switch turns on, the LX voltage equals GND and the inductor ramps down. The average inductor current is equal to the load current, and will rise and fall as the load demands. The inductor ripple current is filtered by the output capacitors to provide a low ripple voltage at the output. The output voltage is sensed by the feedback pin which is compared to a reference voltage to generate the PWM duty cycle.

The duty cycle for a buck converter can be approximated as:

$$D_{BUCK} = \frac{Vout}{Vin}$$

Peak-to-peak inductor ripple current can be approximated as:

$$\Delta IL = \frac{(Vin - Vo)D}{fsw \times L}$$

And peak inductor current as:

$$IL_{PEAK} = \frac{\Delta IL}{2} + I_{LOAD}$$

#### **Output Voltage and DVS**

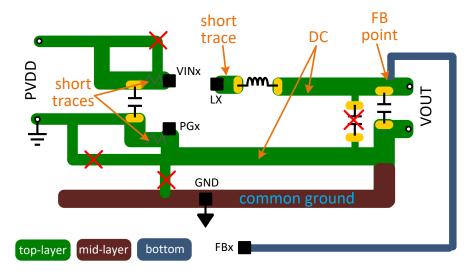

The output voltage for each channel is register programmable in 50 mV steps at registers DVS1 through DVS4 (0x0B to 0x0E). These registers set the reference voltage for each channel, and can be dynamically changed during operation. Each channel's voltage feedback pin (FB) should be connected at the output capacitor with the FB trace routed to avoid primary sources of noise such as inductor and switching nodes. Shielding FB traces with a ground plane is highly recommended.

When dynamically changing the voltage of any switching channel, the FB voltage will be stepped up or down towards the new target value in 50 mV steps. The time between each step is set at 50  $\mu$ s or 100  $\mu$ s using the TSEQ register (0x11, D2). The linearity of the output voltage response depends on several factors including inductance, output capacitance, step time, and switching frequency. Larger output capacitance values will require more current to charge (or more negative current to discharge) which may result in overshoots or undershoots at the output. To avoid false error detection, 10 ms OV and SC masking times can be enabled in the TSEQ register (0x11, D1:D0). The power good status bits (0x01) for each channel are masked during DVS transitions.

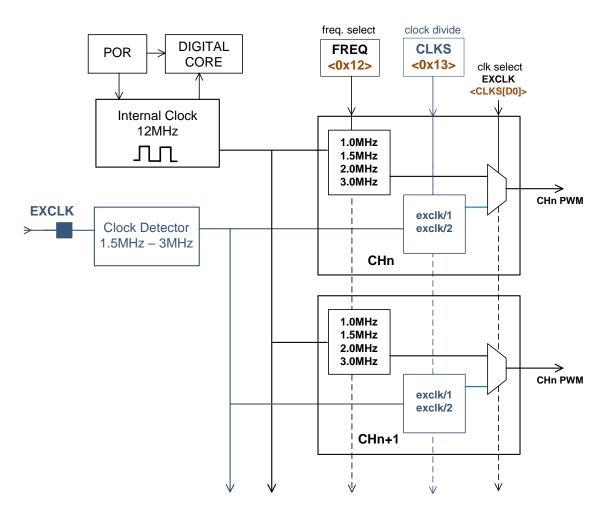

#### **Switching Frequency**

Each channel's switching frequency can be independently selected within a 1 MHz to 3 MHz range. The source clock must be selected as either internal or external. If internal, any of four frequencies can be selected, all with an accuracy within  $\pm$  2 %. An overview is shown in Figure 32 below. Channel 3 switches 180 degrees out of phase with the other channels. This reduces input ripple current, which helps to reduce input noise and stress on the input capacitors.

If the external clock option is selected via the CLKS register (0x13, D0), the external clock must be between 1.5 MHz and 3 MHz with a near 50 % duty. The external clock is applied to all channels. However, the external clock can be divided in half, providing two frequency options for each channel.

It is not recommended to divide external clock frequencies of less than 2 MHz. Frequencies higher than 3 MHz or lower than 1 MHz cannot be used.

If the external clock becomes inactive, or the external frequency is outside of the specified range, the DA6102 automatically switches to the internal clock. Similarly, when a valid external clock is detected at the EXCLK pin, the external clock will take over from the internal clock (assuming that external clock is selected in the CLKS register). The switching clock operation is designed to ensure robust operation in any condition. However, real time clock detection and switch-over requires several cycles of delay. Therefore, to avoid output voltage glitches during normal operation the clock frequency should not be changed, nor should control be switched from internal to external clock or vice versa during PMIC operation.

In general, a higher switching frequency requires smaller external components and can have a better transient response. The trade-off is that a higher switching frequency will have higher losses and therefore lower efficiency.

**Table 9: External Clock and Switching Frequency Selection**

| Clock Select<br><clks><br/>0x13 [D0]</clks> | External Clock Input<br>EXCLK | Clock Divider<br><clks><br/>0x13 [D4:D1]</clks> | Switching Frequency<br>Ch1 to Ch4   |

|---------------------------------------------|-------------------------------|-------------------------------------------------|-------------------------------------|

|                                             | <1.5 MHz                      | -                                               | Not allowed: internal clock is used |

|                                             | 1.5 MHz to 2 MHz              | 1 (x1/2)                                        | Not allowed                         |

| 1                                           | 1.5 MHz to 2 MHz              | 0 (x1)                                          | 1.5 MHz to 2 MHz                    |

| (External)                                  | 2 MHz to 3 MHz                | 0 (x1)                                          | 2 MHz to 3 MHz                      |

|                                             | 2 MHz to3 MHz                 | 1 (x1/2)                                        | 1 MHz to 1.5 MHz                    |

|                                             | > 3 MHz                       | -                                               | Not allowed: internal clock is used |

Figure 32: Frequency Selection and Distribution

#### BST, VDR, and Pulse Skipping

For the highest efficiency, all of the switching channels in the DA6102 use NFETs, except for the Channel 1 high side boost switch. NFETs require a drive voltage higher than the LX voltage, which is generated by the bootstrap capacitor at the BST pins. When the low side switch is on, the LX pin is at GND and the bootstrap capacitor is charged to approximately 5 V from VDR through an internal switch. When the high side turns on, the LX voltage increases to VIN and the voltage at BST follows, remaining 5 V above LX. For each switching channel in the DA6102, the BST voltage is the drive voltage for the high side NFET. A 100 nF capacitor at BST is sufficient to provide gate drive under all conditions. However, some time is required to continuously replenish the bootstrap charge. This time is imposed as the minimum high side off-time of 83 ns (on all channels). The minimum off-time defines the maximum duty cycle capability for a given frequency as shown below.

$$D_{MAX} = 1 - (fsw \times 83ns)$$

VDR supplies the gate drive voltage rail for all switching channels. The VDR pin must be externally connected to LDO1. The VDR voltage charges the BST capacitor for the high side drive and also drives the low side. Due to the fast switching currents required, VDR must be bypassed with a minimum of 10 µF ceramic capacitor placed close to the pin. When the Channel 1 BuckBoost is enabled, LDO1 and therefore VDR have a high enough input voltage for sufficient gate driving even when the battery voltage drops below 4 V. This is also the highest efficiency configuration. However, should the battery voltage drop below 4 V without Channel 1 enabled, the gate drive may not be sufficient, in which case a VD5 fault will occur.

The maximum duty cycle defines the point at which the input voltage is too low for the output voltage to be regulated. If the input voltage continues to drop, the duty cycle will remain fixed at maximum

thus causing the output voltage to drop. In this condition, up to eight off pulses can be skipped in order to maximize the duty cycle and extend the operation range of the channel. Maximum duty cycle with pulse skipping enabled is calculated as shown below.

$$D_{MAX-PSM} = 1 - \left(\frac{fsw \times 83ns}{9}\right)$$

Pulse skipping is available on channels 2, 3, and 4 via the CTL register (0x22), and on Channel 1 via BB\_OPT (0x31). With or without pulse skipping, PGOOD and short circuit detection will be triggered as input voltage falls below the maximum duty.

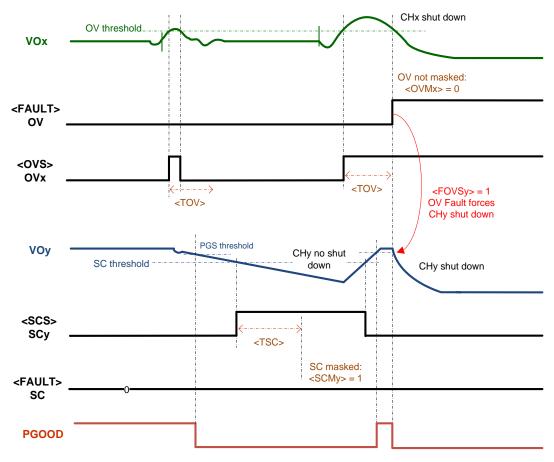

#### **Current Limit and Short Circuit Protection**

The DA6102 incorporates cycle-by-cycle current limit on each channel. The sensed high side switch current that is used for PWM control is also used to limit the peak current. Each channel has a specified current limit threshold based on the current handling capability of that channel. When the inductor current ramps up to a peak value equal to the current limit threshold, the high side switch is immediately turned off until the next cycle. This ensures that the inductor current will not exceed the limit. Because inductor ripple current is not constant, the average load current at which the current limit is triggered will depend on frequency, inductance, and duty cycle. The current limit threshold as average load current can be calculated as shown follows.

$$I_{LOAD\_MAX} = ILIM - \frac{\Delta IL}{2}$$

The peak current limit threshold must be taken into consideration when selecting an inductor value and switching frequency. For a given inductance, ripple and peak current will increase with lower frequency. Selecting too low an inductor value may cause a channel to trigger the current limit below the required load current.

When in current limit, the switching duty cycle is reduced causing a reduction in output voltage (as the load increases, duty cycle decreases). When the output voltage drops to 85 % of nominal, the PGOOD register (PGS, 0x01) for that channel will go low. To prevent runaway inductor current, when the output is below 85% one switching cycle will be skipped after a current limit detection. If the load current continues to increase, forcing the output voltage to drop to 70 % of nominal, the short circuit status register (SCS, 0x02) for that channel will go high. The LDSW1 output also has a short circuit detection function nearly identical to that of the switching channels.

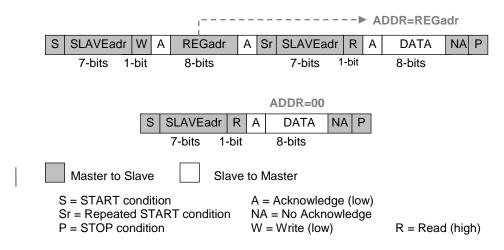

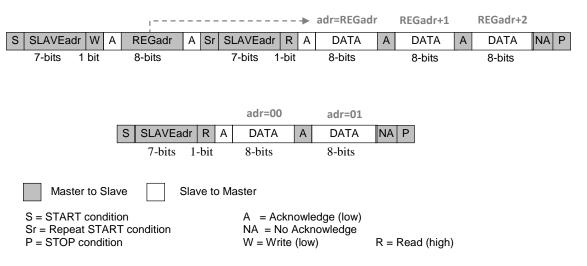

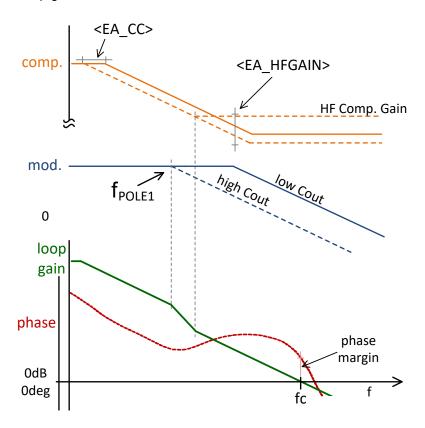

Furthermore, if the output voltage drops below 50 % of nominal, because of an output short to ground for example, the HDSRT flag (D7 in the FAULT register) will go high after four current limit cycles and the affected channel will shut down. Writing '1' to the HDSRT bit will clear the fault flag and restart the channel.