## **General Description**

PV88090 is a power management unit (PMU) optimized for supplying systems with central processing units (CPU), input/output (I/O), and dual data rate (DDR) memory. The target application range covers television, set-up box, wifi routers, and enterprise access point and network addressable servers.

PV88090 features a two-phase buck converter providing up to 9.5 A current, and two one-phase buck converters for dual date rate (DDR) memory and auxiliary power. High efficiency is achieved over a wide load range by using automatic pulse frequency modulation (PFM). All power switches are integrated, eliminating the need for external Schottky diodes are not needed. This optimizes power efficiency and reduces the external component count. Two LDO regulators with programmable output voltage are integrated and provide up to 400 mA. PV88090 provides dynamic voltage control (DVC) via I²C command to support adaptive adjustment of the supply voltage based on the processor loading. All power blocks have over-current circuit protection and the start-up timing can be controlled through the I²C interface. The supply voltages of PV88090 control can be realized via direct register writes through the I²C interface to the operating point of the system.

PV88090 includes over-temperature and over-current protection for increased system reliability, without external sensing components. A soft-start mechanism limits the inrush current from the input node and secures a slope-controlled rail activation. A standby mode provides reduced power consumption. Optional standby operation for DDR memory, auxiliary buck, and analog core LDO are configurable in PV88090 for optimizing the power rails. The PV88090 available in a 30-pin QFN package and is specified from -40 °C to 85 °C ambient temperature.

## **Key Features**

- Input voltage 4.75 V to 5.25 V

- Three synchronous buck converters with integrated low R<sub>ON</sub> FET

- Buck1: Programmable output voltage from 0.9 V to 1.3 V with 9.5 A continuous output current, 11 A peak current if standalone

- Buck2: Programmable output voltage from 1 V to 2.5 V with 2 A continuous output current

- Buck3: Programmable output voltage

1.3 V to 3.4 V with 2 A continuous output current

- □ 93 % efficiency

- Auto mode on all three buck converters

- Integrated power switches

- DVC for buck converters

- 2 LDO regulators

- LDO1: 1.05 V to 1.23 V, 400 mA

LDO2: 1.8 V to 3.3 V, 250 mA

- Adjustable soft-start

- I<sup>2</sup>C compatible interface

- -40 °C to +85 °C ambient temperature range

- Custom 30-pin FC-MQFN package with thermal pad, 0.5 mm pin pitch

## **Applications**

- Supply for digital television processor

- Power supply for digital set top box (STB)

- Networking home terminal

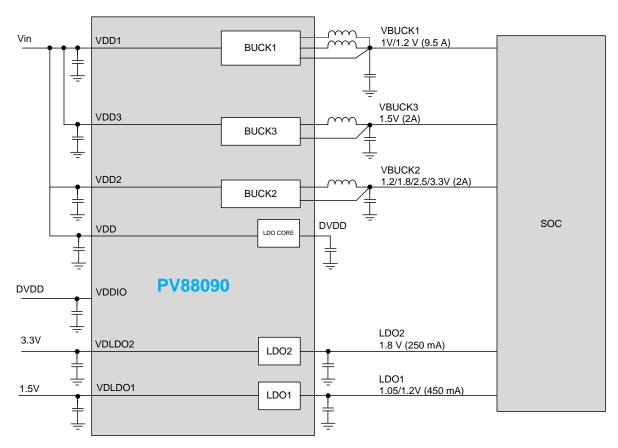

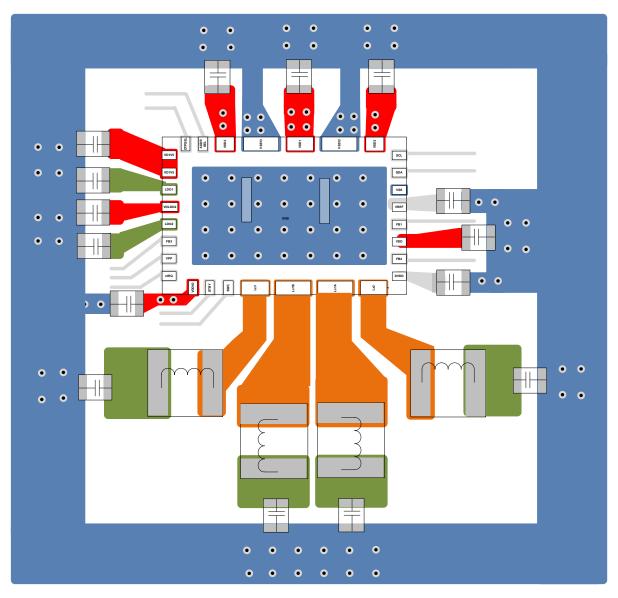

## **System Diagram**

Figure 1: System Diagram

## **Contents**

| Key Features Applications System Diagram Contents Figures Tables 1 Terms and definitions 2 References 3 Block Diagram 4 Pinout 5 Characteristics 5.1 Absolute Maximum Ratings 5.2 Recommended Operating Conditions 5.3 ESD Ratings 5.4 Electrical Characteristics 5.4.1 Digital I/O 5.4.2 PC Interface 5.4.3 Buck Converter Electrical Characteristics 5.4.3 Buck Converter Electrical Characteristics 5.4.3.2 Buck 2 Electrical Characteristics 5.4.3.3 Buck 3 Electrical Characteristics 5.5.5 LDO Electrical Characteristics 5.5.5 LDO Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC. 6.1.6 Interrupt Request - nIRQ 6.1.7 PC Interface 6.1.8 FCProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOS 6.3 Buck Converters                                                                                                                                                                                 | Ge | neral  | Descrip    | tion                     |                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|------------|--------------------------|------------------------------------|----|

| System Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ke | y Fea  | tures      |                          |                                    | 1  |

| Terms and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Αp | plicat | tions      |                          |                                    | 1  |

| Terms and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Sy | stem   | Diagram    | ١                        |                                    | 2  |

| Figures Tables  1 Terms and definitions 2 References 3 Block Diagram 4 Pinout 5 Characteristics 5.1 Absolute Maximum Ratings 5.2 Recommended Operating Conditions. 5.3 ESD Ratings 5.4 Electrical Characteristics 5.4.1 Digital I/O 5.4.2   2C Interface 5.4.3 Buck Converter Electrical Characteristics 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5.4.3 Buck Electrical Characteristics 5.5.5 LDO Electrical Characteristics 5.5.1 LDO1. 5.5.2 LDO2. 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC. 6.1.6 Interrupt Request - nIRQ 6.1.7   PC Interface 6.1.8   PCProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOS                                                                                                                                                                                                                                                     | -  |        | _          |                          |                                    |    |

| Tables           1         Terms and definitions           2         References           3         Block Diagram           4         Pinout           5         Characteristics           5.1         Absolute Maximum Ratings           5.2         Recommended Operating Conditions           5.3         ESD Ratings           5.4         Electrical Characteristics           5.4.1         Digital I/O           5.4.2         I²C Interface           5.4.3         Buck Converter Electrical Characteristics           5.4.3.1         Buck1 Electrical Characteristics           5.4.3.2         Buck2 Electrical Characteristics           5.4.3.3         Buck3 Electrical Characteristics           5.5         LDO Electrical Characteristics           5.5.1         LDO1           5.5.2         LDO2           5.5.3         Core LDO Electrical Characteristics           5.6         Reference Voltage and Bias Current Generation           5.7         Supply Monitoring Electrical Characteristics           5.8         Current Consumption           5.8.1         Power Use Case           6         Functional Description           6.1         Contr                                                                                                                                       |    |        |            |                          |                                    |    |

| Terms and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •  | •      |            |                          |                                    |    |

| 2 References           3 Block Diagram           4 Pinout           5 Characteristics           5.1 Absolute Maximum Ratings           5.2 Recommended Operating Conditions           5.3 ESD Ratings           5.4 Electrical Characteristics           5.4.1 Digital I/O           5.4.2 IPC Interface           5.4.3 Buck Converter Electrical Characteristics           5.4.3.1 Buch1 Electrical Characteristics           5.4.3.2 Buck2 Electrical Characteristics           5.4.3.3 Buck3 Electrical Characteristics           5.5.1 LDO1           5.5.2 LDO2           5.5.3 Core LDO Electrical Characteristics           5.6 Reference Voltage and Bias Current Generation           5.7 Supply Monitoring Electrical Characteristics           5.8 Current Consumption           5.8.1 Power Use Case           6 Functional Description           6.1 Control Signals           6.1.1 OTP Bank Select - ADRSEL           6.1.2 Address Select - ADRSEL           6.1.3 Standby Pin - STBY           6.1.4 Programming Voltage Input - VPP           6.1.5 Single Wire Communication I/O - SWC           6.1.6 Interrupt Request - nIRQ           6.1.7 IPC Interface           6.1.8 IPCProtocol           6.1.9 Dynamic Voltage Control </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> |    |        |            |                          |                                    |    |

| 3 Block Diagram 4 Pinout 5 Characteristics 5.1 Absolute Maximum Ratings 5.2 Recommended Operating Conditions 5.3 ESD Ratings 5.4 Electrical Characteristics 5.4.1 Digital I/O 5.4.2   ^2C Interface 5.4.3 Buck Converter Electrical Characteristics 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7  ^2C Interface 6.1.9 Dynamic Voltage Control 6.2 LDOS                                                                                                                                                                                                                                                                                                                                                                                                           |    |        |            |                          |                                    |    |

| 4 Pinout  5 Characteristics  5.1 Absolute Maximum Ratings  5.2 Recommended Operating Conditions  5.3 ESD Ratings  5.4 Electrical Characteristics  5.4.1 Digital I/O  5.4.2   2°C Interface  5.4.3 Buck Converter Electrical Characteristics  5.4.3.1 Buck1 Electrical Characteristics  5.4.3.2 Buck2 Electrical Characteristics  5.4.3.3 Buck3 Electrical Characteristics  5.5.1 LDO Electrical Characteristics  5.5.1 LDO1  5.5.2 LDO2  5.5.3 Core LDO Electrical Characteristics  5.6 Reference Voltage and Bias Current Generation  5.7 Supply Monitoring Electrical Characteristics  5.8 Current Consumption  5.8.1 Power Use Case  6 Functional Description  6.1 Control Signals  6.1.1 OTP Bank Select - OTPSEL  6.1.2 Address Select - ADRSEL  6.1.3 Standby Pin - STBY  6.1.4 Programming Voltage Input - VPP  6.1.5 Single Wire Communication I/O - SWC  6.1.6 Interrupt Request - nIRQ  6.1.7   2°C Interface  6.1.8   2°CProtocol  6.1.9 Dynamic Voltage Control  6.2 LDOS                                                                                                                                                                                                                                                                                                                                  | 2  |        |            |                          |                                    |    |

| 5 Characteristics           5.1 Absolute Maximum Ratings           5.2 Recommended Operating Conditions           5.3 ESD Ratings           5.4 Electrical Characteristics           5.4.1 Digital I/O           5.4.2 I²C Interface           5.4.3 Buck Converter Electrical Characteristics           5.4.3.1 Buck1 Electrical Characteristics           5.4.3.2 Buck2 Electrical Characteristics           5.4.3.3 Buck3 Electrical Characteristics           5.5 LDO Electrical Characteristics           5.5.1 LDO1           5.5.2 LDO2           5.5.3 Core LDO Electrical Characteristics           5.6 Reference Voltage and Bias Current Generation           5.7 Supply Monitoring Electrical Characteristics           5.8 Current Consumption           5.8.1 Power Use Case           6 Functional Description           6.1.1 OTP Bank Select - OTPSEL           6.1.2 Address Select - ADRSEL           6.1.3 Standby Pin - STBY           6.1.4 Programming Voltage Input - VPP           6.1.5 Single Wire Communication I/O - SWC           6.1.6 Interrupt Request - nIRQ           6.1.7 I²C Interface           6.1.8 I²CProtocol           6.1.9 Dynamic Voltage Control           6.2 LDOs                                                                                                    | 3  | Bloc   | k Diagra   | ım                       |                                    | 7  |

| 5.1 Absolute Maximum Ratings 5.2 Recommended Operating Conditions 5.3 ESD Ratings 5.4 Electrical Characteristics 5.4.1 Digital I/O 5.4.2 I²C Interface 5.4.3 Buck Converter Electrical Characteristics 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I²C Interface 6.1.8 I²CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                      | 4  | Pino   | ut         |                          |                                    | 7  |

| 5.2       Recommended Operating Conditions         5.3       ESD Ratings         5.4       Electrical Characteristics         5.4.1       Digital I/O         5.4.2       I²C Interface         5.4.3       Buck Converter Electrical Characteristics         5.4.3.1       Buck1 Electrical Characteristics         5.4.3.2       Buck2 Electrical Characteristics         5.4.3.3       Buck3 Electrical Characteristics         5.5.1       LDO1         5.5.2       LDO2         5.5.3       Core LDO Electrical Characteristics         5.6       Reference Voltage and Bias Current Generation         5.7       Supply Monitoring Electrical Characteristics         5.8       Current Consumption         5.8.1       Power Use Case         6       Functional Description         6.1       Control Signals         6.1.1       OTP Bank Select - OTPSEL         6.1.2       Address Select - ADRSEL         6.1.3       Standby Pin - STBY         6.1.4       Programming Voltage Input - VPP         6.1.5       Single Wire Communication I/O - SWC         6.1.6       Interrupt Request - nIRQ         6.1.7       I²C Interface         6.1.8       I²CPro                                                                                                                                            | 5  | Char   | racteristi | ics                      |                                    | 9  |

| 5.3       ESD Ratings         5.4       Electrical Characteristics         5.4.1       Digital I/O         5.4.2       I²C Interface         5.4.3       Buck Converter Electrical Characteristics         5.4.3.1       Buck1 Electrical Characteristics         5.4.3.2       Buck2 Electrical Characteristics         5.4.3.3       Buck3 Electrical Characteristics         5.5       LDO Electrical Characteristics         5.5.1       LDO1         5.5.2       LDO2         5.5.3       Core LDO Electrical Characteristics         5.6       Reference Voltage and Bias Current Generation         5.7       Supply Monitoring Electrical Characteristics         5.8       Current Consumption         5.8.1       Power Use Case         6       Functional Description         6.1       Control Signals         6.1.1       OTP Bank Select - OTPSEL         6.1.2       Address Select - ADRSEL         6.1.3       Standby Pin - STBY         6.1.4       Programming Voltage Input - VPP         6.1.5       Single Wire Communication I/O - SWC         6.1.6       Interrupt Request - nIRQ         6.1.7       I²C Interface         6.1.8       I²CProto                                                                                                                                            |    | 5.1    | Absolu     | te Maximum               | n Ratings                          | 9  |

| 5.4 Electrical Characteristics  5.4.1 Digital I/O  5.4.2 I²C Interface  5.4.3 Buck Converter Electrical Characteristics  5.4.3.1 Buck1 Electrical Characteristics  5.4.3.2 Buck2 Electrical Characteristics  5.4.3.3 Buck3 Electrical Characteristics  5.5.1 LDO1  5.5.1 LDO1  5.5.2 LDO2  5.5.3 Core LDO Electrical Characteristics  5.6 Reference Voltage and Bias Current Generation  5.7 Supply Monitoring Electrical Characteristics  5.8 Current Consumption  5.8.1 Power Use Case  6 Functional Description  6.1 Control Signals  6.1.1 OTP Bank Select - OTPSEL  6.1.2 Address Select - ADRSEL  6.1.3 Standby Pin - STBY  6.1.4 Programming Voltage Input - VPP  6.1.5 Single Wire Communication I/O - SWC  6.1.6 Interrupt Request - nIRQ  6.1.7 I²C Interface  6.1.8 I²CProtocol  6.1.9 Dynamic Voltage Control  6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 5.2    | Recom      | mended Op                | perating Conditions                | 9  |

| 5.4.1       Digital I/O         5.4.2       I²C Interface         5.4.3       Buck Converter Electrical Characteristics         5.4.3.1       Buck2 Electrical Characteristics         5.4.3.2       Buck2 Electrical Characteristics         5.4.3.3       Buck3 Electrical Characteristics         5.5       LDO Electrical Characteristics         5.5.1       LDO1         5.5.2       LDO2         5.5.3       Core LDO Electrical Characteristics         5.6       Reference Voltage and Bias Current Generation         5.7       Supply Monitoring Electrical Characteristics         5.8       Current Consumption         5.8.1       Power Use Case         6       Functional Description         6.1       Control Signals         6.1.1       OTP Bank Select - OTPSEL         6.1.2       Address Select - ADRSEL         6.1.3       Standby Pin - STBY         6.1.4       Programming Voltage Input - VPP         6.1.5       Single Wire Communication I/O - SWC         6.1.6       Interrupt Request - nIRQ         6.1.7       I²C Interface         6.1.8       I²CProtocol         6.1.9       Dynamic Voltage Control                                                                                                                                                                        |    | 5.3    | ESD R      | atings                   |                                    | 10 |

| 5.4.2 IPC Interface 5.4.3 Buck Converter Electrical Characteristics 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 5.4    | Electric   | al Characte              | pristics                           | 10 |

| 5.4.3 Buck Converter Electrical Characteristics 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5.1 LDO Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        | 5.4.1      | Digital I/C              | )                                  | 10 |

| 5.4.3.1 Buck1 Electrical Characteristics 5.4.3.2 Buck2 Electrical Characteristics 5.4.3.3 Buck3 Electrical Characteristics 5.5 LDO Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |        | 5.4.2      | I <sup>2</sup> C Interfa | ace                                | 10 |

| 5.4.3.2         Buck2 Electrical Characteristics           5.4.3.3         Buck3 Electrical Characteristics           5.5         LDO Electrical Characteristics           5.5.1         LDO1           5.5.2         LDO2           5.5.3         Core LDO Electrical Characteristics           5.6         Reference Voltage and Bias Current Generation           5.7         Supply Monitoring Electrical Characteristics           5.8         Current Consumption           5.8.1         Power Use Case           6         Functional Description           6.1         Control Signals           6.1.1         OTP Bank Select - OTPSEL           6.1.2         Address Select - ADRSEL           6.1.3         Standby Pin - STBY           6.1.4         Programming Voltage Input - VPP           6.1.5         Single Wire Communication I/O - SWC           6.1.6         Interrupt Request - nIRQ           6.1.7         12C Interface           6.1.8         12CProtocol           6.1.9         Dynamic Voltage Control           6.2         LDOs                                                                                                                                                                                                                                                  |    |        | 5.4.3      | Buck Cor                 | nverter Electrical Characteristics | 12 |

| 5.4.3.3 Buck3 Electrical Characteristics  5.5 LDO Electrical Characteristics  5.5.1 LDO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |            | 5.4.3.1                  | Buck1 Electrical Characteristics   | 12 |

| 5.5 LDO Electrical Characteristics 5.5.1 LDO1 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case 6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |        |            | 5.4.3.2                  | Buck2 Electrical Characteristics   | 12 |

| 5.5.1 LDO1. 5.5.2 LDO2. 5.5.3 Core LDO Electrical Characteristics.  5.6 Reference Voltage and Bias Current Generation. 5.7 Supply Monitoring Electrical Characteristics. 5.8 Current Consumption. 5.8.1 Power Use Case.  6 Functional Description. 6.1 Control Signals. 6.1.1 OTP Bank Select - OTPSEL. 6.1.2 Address Select - ADRSEL. 6.1.3 Standby Pin - STBY. 6.1.4 Programming Voltage Input - VPP. 6.1.5 Single Wire Communication I/O - SWC. 6.1.6 Interrupt Request - nIRQ. 6.1.7 I <sup>2</sup> C Interface. 6.1.8 I <sup>2</sup> CProtocol. 6.1.9 Dynamic Voltage Control. 6.2 LDOs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |        |            |                          |                                    |    |

| 5.5.2 LDO2 5.5.3 Core LDO Electrical Characteristics  5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case  6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I²C Interface 6.1.8 I²CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 5.5    | LDO EI     |                          |                                    |    |

| 5.5.3 Core LDO Electrical Characteristics  5.6 Reference Voltage and Bias Current Generation  5.7 Supply Monitoring Electrical Characteristics.  5.8 Current Consumption.  5.8.1 Power Use Case.  6 Functional Description.  6.1 Control Signals.  6.1.1 OTP Bank Select - OTPSEL.  6.1.2 Address Select - ADRSEL.  6.1.3 Standby Pin - STBY.  6.1.4 Programming Voltage Input - VPP.  6.1.5 Single Wire Communication I/O - SWC.  6.1.6 Interrupt Request - nIRQ.  6.1.7 I²C Interface.  6.1.8 I²CProtocol.  6.1.9 Dynamic Voltage Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |        | 5.5.1      | LDO1                     |                                    | 14 |

| 5.6 Reference Voltage and Bias Current Generation 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case  6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |        | 5.5.2      |                          |                                    |    |

| 5.7 Supply Monitoring Electrical Characteristics 5.8 Current Consumption 5.8.1 Power Use Case  6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I²C Interface 6.1.8 I²CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |        |            |                          |                                    |    |

| 5.8 Current Consumption 5.8.1 Power Use Case  6 Functional Description 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 5.6    |            | _                        |                                    |    |

| 5.8.1 Power Use Case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |        |            | J                        |                                    |    |

| 6.1 Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 5.8    |            | •                        |                                    |    |

| 6.1 Control Signals 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |        |            |                          |                                    |    |

| 6.1.1 OTP Bank Select - OTPSEL 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY 6.1.4 Programming Voltage Input - VPP 6.1.5 Single Wire Communication I/O - SWC 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6  | Fund   | ctional D  | escription .             |                                    | 18 |

| 6.1.2 Address Select - ADRSEL 6.1.3 Standby Pin - STBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 6.1    | Control    | U                        |                                    |    |

| 6.1.3 Standby Pin - STBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        | 6.1.1      |                          |                                    |    |

| 6.1.4 Programming Voltage Input - VPP  6.1.5 Single Wire Communication I/O - SWC  6.1.6 Interrupt Request - nIRQ  6.1.7 I <sup>2</sup> C Interface  6.1.8 I <sup>2</sup> CProtocol  6.1.9 Dynamic Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |        |            |                          |                                    |    |

| 6.1.5 Single Wire Communication I/O - SWC. 6.1.6 Interrupt Request - nIRQ. 6.1.7 I <sup>2</sup> C Interface. 6.1.8 I <sup>2</sup> CProtocol. 6.1.9 Dynamic Voltage Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |        | 6.1.3      |                          |                                    |    |

| 6.1.6 Interrupt Request - nIRQ 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |        |            | •                        |                                    |    |

| 6.1.7 I <sup>2</sup> C Interface 6.1.8 I <sup>2</sup> CProtocol 6.1.9 Dynamic Voltage Control 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |        |            | Ŭ                        |                                    |    |

| 6.1.8 I <sup>2</sup> CProtocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |        |            | •                        | •                                  |    |

| 6.1.9 Dynamic Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |        | _          |                          |                                    |    |

| 6.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |            |                          |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |        |            | •                        | •                                  |    |

| 6.3 Buck Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |        |            |                          |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 6.3    | Buck C     | onverters                |                                    | 22 |

|     |        | 6.3.1     | Buck1                                   | 22       |

|-----|--------|-----------|-----------------------------------------|----------|

|     |        | 6.3.2     | Buck2                                   | 22       |

|     |        | 6.3.3     | Buck3                                   | 23       |

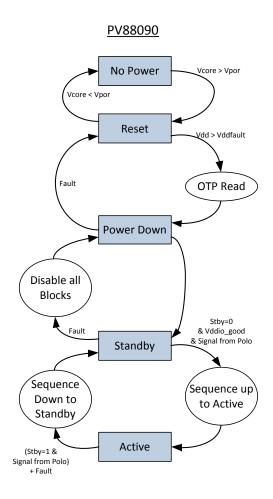

|     | 6.4    | Power N   | Modes                                   | 23       |

|     |        | 6.4.1     | Normal Mode - Default Power-Up State    | 23       |

|     |        | 6.4.2     | Normal Mode                             | 23       |

|     |        | 6.4.3     | Standby Mode                            | 23       |

|     |        | 6.4.4     | Power Supply Sequencer                  | 24       |

|     |        | 6.4.5     | Boot Sequence                           | 24       |

|     | 6.5    | Monitori  | ing and Interrupts                      | 27       |

|     | 6.6    | Power-0   | On-Reset                                | 27       |

|     | 6.7    | Referen   | nce Voltage and Bias Current Generation | 27       |

|     | 6.8    | Over-Te   | emperature                              | 27       |

|     | 6.9    | Supply    | Monitoring                              | 27       |

|     | 6.10   | Fault Co  | ondition                                | 28       |

| 7   | Regis  | ster Defi | nitions                                 | 29       |

|     | 7.1    | Registe   | r Page Control                          | 29       |

|     | 7.2    | Status a  | and Events                              | 30       |

|     |        | 7.2.1     | Register STATUS_A                       | 30       |

|     |        | 7.2.2     | Register STATUS_B                       | 30       |

|     |        | 7.2.3     | Register EVENT_A                        | 30       |

|     |        | 7.2.4     | Register EVENT_B                        | 31       |

|     |        | 7.2.5     | Register FAULT_LOG                      | 31       |

|     |        | 7.2.6     | Register IRQ_MASK_A                     | 32       |

|     |        | 7.2.7     | Register IRQ_MASK_B                     | 32       |

|     |        | 7.2.8     | Register CONTROL_B                      | 32       |

|     |        | 7.2.9     | Register INTERFACE                      | 33       |

|     | 7.3    | Supplies  | s (Bucks and LDOs)                      | 33       |

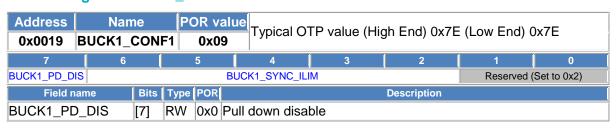

|     |        | 7.3.1     | Register BUCK1_CONF0                    | 33       |

|     |        | 7.3.2     | Register BUCK1_CONF1                    | 33       |

|     |        | 7.3.3     | Register BUCK2_CONF0                    | 34       |

|     |        | 7.3.4     | Register BUCK2_CONF1                    | 34       |

|     |        | 7.3.5     | Register BUCK3_CONF0                    | 35       |

|     |        | 7.3.6     | Register BUCK3_CONF1                    | 35       |

|     |        | 7.3.7     | Register LDO2                           | 36       |

|     |        | 7.3.8     | Register LDO1a [1.5V Supply]            | 36       |

| 8   | Pack   | age Info  | rmation                                 | 38       |

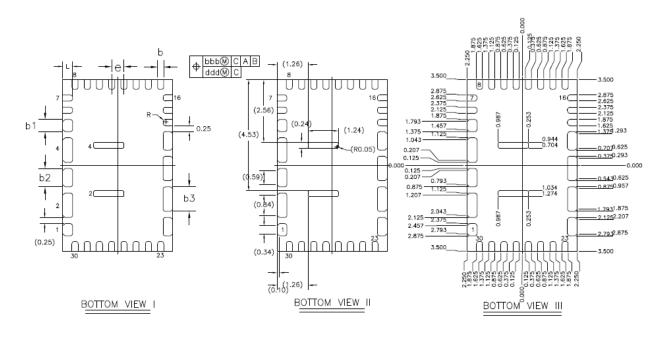

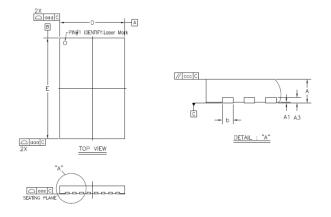

|     | 8.1    | Package   | e Outlines                              | 38       |

| 9   | Orde   | ring Info | ormation                                | 39       |

| 10  |        | •         | nformation                              |          |

| . • |        |           | ors Selection                           |          |

|     |        | •         | r Selection                             |          |

| 11  |        |           | elines                                  |          |

|     | _u y U | a. Juiuc  | ······································  | <b>7</b> |

CFR0011-120-00

# **Figures**

| Figure 1: System Diagram                          | 2  |

|---------------------------------------------------|----|

| Figure 1: System DiagramFigure 2: Block Diagram   | 7  |

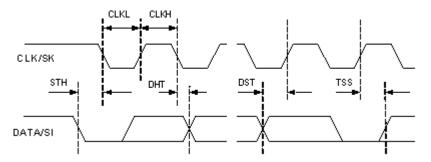

| Figure 3: I2C Interface Timing                    | 11 |

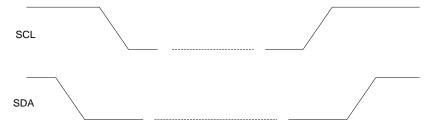

| Figure 4: Timing of the START and STOP conditions | 19 |

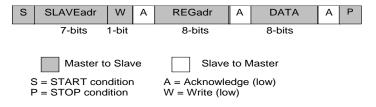

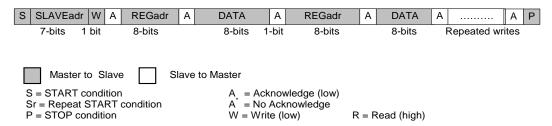

| Figure 5: Byte Write Operation                    | 19 |

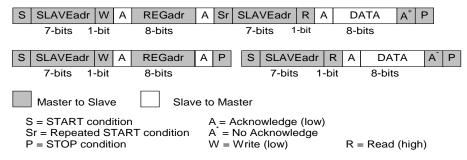

| Figure 6: Examples of Byte Read Operations        | 20 |

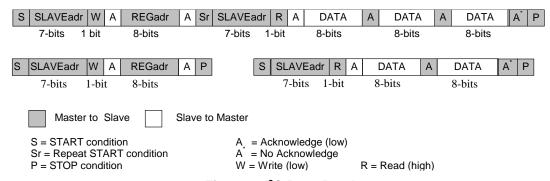

| Figure 7: I <sup>2</sup> C Page Read              | 20 |

| Figure 8: I <sup>2</sup> C Page Write             | 20 |

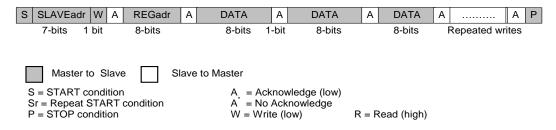

| Figure 9: I <sup>2</sup> C Repeated Write         | 21 |

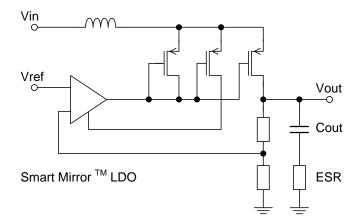

| Figure 10: Smart Mirror™ Voltage Regulator        | 21 |

| Figure 11: Boot Sequence                          | 26 |

| Figure 12: Package Outline Drawing                | 38 |

|                                                   |    |

|                                                   |    |

|                                                   |    |

# **Tables**

| Table 1: Pin Description                                                           | 7  |

|------------------------------------------------------------------------------------|----|

| Table 2: Pin Type Definition                                                       | 8  |

| Table 3: Absolute Maximum Ratings                                                  |    |

| Table 4: Recommended Operating Conditions                                          | 9  |

| Table 5: ESD Characteristics                                                       |    |

| Table 6: Digital I/O Electrical Characteristics                                    | 10 |

| Table 7: I <sup>2</sup> C Interface Electrical Characteristics                     | 10 |

| Table 8: Buck2 Electrical Characteristics                                          | 12 |

| Table 9: Buck3 Electrical Characteristics                                          | 13 |

| Table 10: LDO1 Electrical Characteristics                                          |    |

| Table 11: LDO2 Electrical Characteristics                                          |    |

| Table 12: Core LDO Electrical Characteristics                                      | 16 |

| Table 13: Reference Voltage and Bias Current Generation Electrical Characteristics |    |

| Table 14: Supply Monitoring Electrical Characteristics                             | 16 |

| Table 15: Power Dissipation                                                        |    |

| Table 16: Buck Converter Summary                                                   | 22 |

| Table 17: Function Block of Mode Operation                                         |    |

| Table 18: The Start-Up Sequence at POR                                             | 24 |

| Table 19: Start-Up Sequence Example from Standby                                   |    |

| Table 20: Shutdown Sequence Example to Standby                                     | 25 |

| Table 21: Functional Block Mode of Monitoring and Interrupts                       | 27 |

| Table 22: Ordering Information                                                     | 39 |

### 1 Terms and definitions

CCM Continuous Conduction Mode

DCM Discontinuous Conduction Mode

HBM Human Body Model

OTP One Time Programmable

PCB Printed Circuit Board

PG Power Good

PMIC Power Management Integrated Circuit

POR Power On Reset

PVC Power Voltage Converter

PWC Power Cycle

### 2 References

[1] UM10204 I2C bus specification and user manual

[2] PV88080 High Efficiency Advanced Feature 4-Channel PMIC datasheet

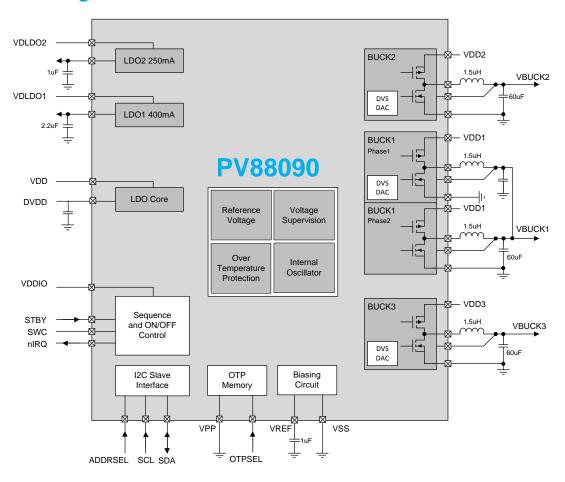

# 3 Block Diagram

Figure 2: Block Diagram

### 4 Pinout

**Table 1: Pin Description**

| Pin No. | Pin Name | Type<br>(Table 2) | Description                                                           |

|---------|----------|-------------------|-----------------------------------------------------------------------|

| 1       | VDD2     | PWR               | Supply voltage for Buck2 To be connected to VDD after input capacitor |

| 2       | VSS12    | GND               | Ground voltage for Buck2 and Buck1 phase1                             |

| 3       | VDD1     | PWR               | Supply voltage Buck1 To be connected to VDD after input capacitor     |

| 4       | VSS13    | GND               | Ground voltage for Buck3 and Buck1 phase2                             |

| 5       | VDD3     | PWR               | Supply voltage for Buck3 To be connected to VDD after input capacitor |

| 6       | ADDRSEL  | DI                | I <sup>2</sup> C alternate address select                             |

| 7       | OTPSEL   | DI                | OTP page select (high end / low end)                                  |

| 8       | VDLDO1   | PWR               | Supply voltage for LDO1                                               |

| 9       | VDLDO1   | PWR               | Supply voltage for LDO1                                               |

| 10      | LDO1     | AO                | LDO1 output                                                           |

| 11      | VDLDO2   | PWR               | Supply voltage for LDO2                                               |

Datasheet Revision 2.6 04-Aug-2017

| Pin No. | Pin Name | Type<br>(Table 2) | Description                                                 |

|---------|----------|-------------------|-------------------------------------------------------------|

| 12      | LDO2     | AO                | LDO2 output                                                 |

| 13      | FB3      | Al                | Feedback node Buck3                                         |

| 14      | VPP      | PWR               | OTP programming voltage input Connect to VSS in application |

| 15      | nIRQ     | DO                | Interrupt line towards the host                             |

| 16      | VDDIO    | PWR               | Supply voltage for I/O rail                                 |

| 17      | STBY     | DI                | System standby signal                                       |

| 18      | SWC      | DIO               | Connect to VSS for normal application                       |

| 19      | LX3      | AO                | Switching node for Buck3                                    |

| 20      | LX1B     | AO                | Switching node for Buck1 phase 2                            |

| 21      | LX1A     | AO                | Switching node for Buck1 phase 1                            |

| 22      | LX2      | AO                | Switching node for Buck2                                    |

| 23      | DVDD     | AIO               | Core digital supply voltage                                 |

| 24      | FB2      | Al                | Feedback node Buck2                                         |

| 25      | VDD      | PWR               | Supply voltage                                              |

| 26      | FB1      | Al                | Feedback node Buck1                                         |

| 27      | VREF     | AO                | Voltage reference decouple                                  |

| 28      | VSS      | GND               | Quiet ground                                                |

| 29      | SDA      | DIO               | I2C data                                                    |

| 30      | SCL      | DI                | I2C clock                                                   |

## **Table 2: Pin Type Definition**

| Pin Type | Description                     | Pin Type | Description                   |

|----------|---------------------------------|----------|-------------------------------|

| DI       | Digital input                   | Al       | Analog input                  |

| DO       | Digital output                  | AO       | Analog output                 |

| DIO      | Digital input/output            | AIO      | Analog input/output           |

| DIOD     | Digital input/output open drain | BP       | Back drive protection         |

| PU       | Pull-up resistor (fixed)        | SPU      | Switchable pull-up resistor   |

| PD       | Pull-down resistor (fixed)      | SPD      | Switchable pull-down resistor |

| PWR      | Power                           | GND      | Ground                        |

### 5 Characteristics

### 5.1 Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

**Table 3: Absolute Maximum Ratings**

| Parameter           | Description                                               | Conditions                       | Min  | Max                    | Unit |

|---------------------|-----------------------------------------------------------|----------------------------------|------|------------------------|------|

| T <sub>STG</sub>    | Storage temperature                                       |                                  | -60  | +165                   | °C   |

| TJ                  | Junction temperature                                      |                                  | -40  | +125                   | °C   |

| V <sub>VDD</sub>    | Power supply input<br>VDD, VDD1, VDD2, VDD3               | STBY =0 and VIN ramp < 1<br>V/µs | -0.3 | 5.5                    | V    |

| V <sub>VLDO2</sub>  | Power supply input VLDO2                                  |                                  | -0.3 | 5.5                    | V    |

| V <sub>VDLDO1</sub> | Power supply input<br>VDLDO1                              |                                  | -0.3 | 2.75                   | V    |

| V <sub>DVDD</sub>   | Power supply input DVDD                                   |                                  | -0.3 | 5.5                    | V    |

| V <sub>L</sub> X    | Power supply input<br>LX1A, Lx1B, LX2, LX3                |                                  | -0.3 | 5.5                    | V    |

| Vvref               | Power supply input<br>VREF                                |                                  | -0.3 | 2.75                   | V    |

| V <sub>IN_MAX</sub> | Maximum input voltage ADRSEL, OTPSEL, SCL, SDA, SWC, STBY |                                  | -0.3 | V <sub>VDD</sub> + 0.3 | V    |

## **5.2** Recommended Operating Conditions