# RENESAS

# EL7457

40MHz Non-Inverting Quad CMOS Driver

The EL7457 is a high speed, non-inverting, quad CMOS driver. It is capable of running at clock rates up to 40MHz and features 2A peak drive capability and a nominal on-resistance of just  $3\Omega$ . The EL7457 is ideal for driving highly capacitive loads, such as storage and vertical clocks in CCD applications. It is also well suited to ATE pin driving, level-shifting, and clock-driving applications.

The EL7457 is capable of running from single or dual power supplies while using ground referenced inputs. Each output can be switched to either the high ( $V_H$ ) or low ( $V_L$ ) supply pins, depending on the related input pin. The inputs are compatible with both 3V and 5V CMOS and TTL logic. The output enable (OE) pin can be used to put the outputs into a high-impedance state. This is especially useful in CCD applications, where the driver should be disabled during power down.

The EL7457 also features very fast rise and fall times which are matched to within 1ns. The propagation delay is also matched between rising and falling edges to within 2ns.

The EL7457 is available in 16-pin QSOP, 16-pin SO (0.150"), and 16-pin QFN packages. All are specified for operation over the full -40°C to +85°C temperature range.

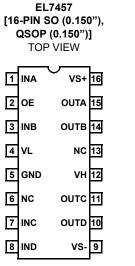

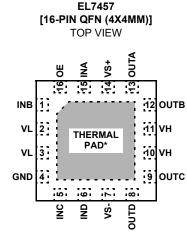

# Pinouts

\* THERMAL PAD CONNECTED TO PIN 7 (V<sub>S</sub>-)

## Features

- Clocking speeds up to 40MHz

- 4 channels

- 12ns t<sub>R</sub>/t<sub>F</sub> at 1000pF C<sub>LOAD</sub>

- · 1ns rise and fall time match

- 1.5ns prop delay match

- Low quiescent current <1mA</li>

- Fast output enable function 12ns

- Wide output voltage range

- $8V \ge V_L \ge -5V$

- $-2V \le V_H \le 16.5V$

- 2A peak drive

- 3Ω on resistance

- · Input level shifters

- TTL/CMOS input-compatible

- Pb-free (RoHS compliant)

## Applications

- CCD drivers

- Digital cameras

- Pin drivers

- · Clock/line drivers

- · Ultrasound transducer drivers

- Ultrasonic and RF generators

- · Level shifting

DATASHEET

FN7288 Rev.5.00 Jul 17, 2020

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART<br>MARKING | TEMP.<br>RANGE (°C) | TAPE AND REEL<br>(Units) (Note 1) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|-----------------------------|-----------------|---------------------|-----------------------------------|-----------------------------|----------------|

| EL7457CUZ                   | 7457CUZ         | -40°C to +85°C      | -                                 | 16 Ld QSOP (0.150")         | MDP0040        |

| EL7457CUZ-T13               | 7457CUZ         | -40°C to +85°C      | 2.5k                              | 16 Ld QSOP (0.150")         | MDP0040        |

| EL7457CUZ-T7                | 7457CUZ         | -40°C to +85°C      | 1k                                | 16 Ld QSOP (0.150")         | MDP0040        |

| EL7457CUZ-T7A               | 7457CUZ         | -40°C to +85°C      | 250                               | 16 Ld QSOP (0.150")         | MDP0040        |

| EL7457CSZ                   | EL7457CSZ       | -40°C to +85°C      | -                                 | 16 Ld SO (0.150")           | MDP0027        |

| EL7457CSZ-T13               | EL7457CSZ       | -40°C to +85°C      | 2.5k                              | 16 Ld SO (0.150")           | MDP0027        |

| EL7457CSZ-T7                | EL7457CSZ       | -40°C to +85°C      | 1k                                | 16 Ld SO (0.150")           | MDP0027        |

| EL7457CSZ-T7A               | EL7457CSZ       | -40°C to +85°C      | 250                               | 16 Ld SO (0.150")           | MDP0027        |

| EL7457CLZ                   | 7457CLZ         | -40°C to +85°C      | -                                 | 16 Ld QFN (4x4mm)           | L16.4X4H       |

| EL7457CLZ-T13               | 7457CLZ         | -40°C to +85°C      | 2.5k                              | 16 Ld QFN (4x4mm)           | L16.4X4H       |

| EL7457CLZ-T7                | 7457CLZ         | -40°C to +85°C      | 1k                                | 16 Ld QFN (4x4mm)           | L16.4X4H       |

| EL7457CLZ-T7A               | 7457CLZ         | -40°C to +85°C      | 250                               | 16 Ld QFN (4x4mm)           | L16.4X4H       |

NOTES:

1. See <u>TB347</u> for details on reel specifications.

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see device information page for EL7457. For more information about MSL see TB363.

| Absolute Maximum R | <b>atings</b> (T <sub>A</sub> = 25°C) |

|--------------------|---------------------------------------|

|--------------------|---------------------------------------|

| Supply Voltage (V <sub>S</sub> + to V <sub>S</sub> -) | +18V           |

|-------------------------------------------------------|----------------|

| Input Voltage                                         |                |

| Continuous Output Current                             |                |

| Storage Temperature Range                             | 65°C to +150°C |

#### **Thermal Information**

| Thermal Resistance            | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------|------------------------|------------------------|

| 16 Ld QFN (Notes 4, 5)        | 43                     | 5                      |

| 16 Ld SOIC (Notes 6, 7)       | 73                     | 45                     |

| 16 Ld QSOP (Note 6)           | 112                    | N/A                    |

| Ambient Operating Temperature | 4(                     | 0°C to +85°C           |

| Maximum Die Temperature       |                        | +125°C                 |

| Power Dissipation             |                        | See Curves             |

| Pb-Free Reflow Profile        |                        | . see TB493            |

|                               |                        |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 6.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See <u>TB379</u> for details.

- 7. For  $\theta_{JC},$  the "case temp" location is taken at the package top center.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### **Electrical Specifications** $V_S$ + = +5V, $V_S$ - = -5V, $V_H$ = +5V, $V_L$ = -5V, $T_A$ = 25°C, unless otherwise specified.

| PARAMETER           | DESCRIPTION                                  | CONDITION                        | MIN<br>(Note 8) | ТҮР  | MAX<br>(Note 8) | UNIT |

|---------------------|----------------------------------------------|----------------------------------|-----------------|------|-----------------|------|

| INPUT               |                                              |                                  |                 |      | 1               |      |

| V <sub>IH</sub>     | Logic "1" Input Voltage                      |                                  | 2.0             |      |                 | V    |

| IIH                 | Logic "1" Input Current                      | V <sub>IH</sub> = 5V             |                 | 0.1  | 10              | μA   |

| V <sub>IL</sub>     | Logic "0" Input Voltage                      |                                  |                 |      | 0.8             | V    |

| ΙL                  | Logic "0" Input Current                      | V <sub>IL</sub> = 0V             |                 | 0.1  | 10              | μA   |

| C <sub>IN</sub>     | Input Capacitance                            |                                  |                 | 3.5  |                 | pF   |

| R <sub>IN</sub>     | Input Resistance                             |                                  |                 | 50   |                 | MΩ   |

| OUTPUT              |                                              |                                  | I               |      |                 |      |

| R <sub>OH</sub>     | ON Resistance V <sub>H</sub> to OUTx         | I <sub>OUT</sub> = -100mA        |                 | 4.5  | 6               | Ω    |

| R <sub>OL</sub>     | ON Resistance V <sub>L</sub> to OUTx         | I <sub>OUT</sub> = +100mA        |                 | 4    | 6               | Ω    |

| ILEAK               | Output Leakage Current                       | $V_{H} = V_{S}+, V_{L} = V_{S}-$ |                 | 0.1  | 10              | μA   |

| I <sub>PK</sub>     | Peak Output Current                          | Source                           |                 | 2.0  |                 | А    |

|                     |                                              | Sink                             |                 | 2.0  |                 | А    |

| POWER SUPPL         | Y                                            | I                                | I               |      |                 |      |

| IS                  | Power Supply Current                         | Inputs = V <sub>S</sub> +        |                 | 0.5  | 1.5             | mA   |

| SWITCHING CH        | IARACTERISTICS                               |                                  | I               |      |                 |      |

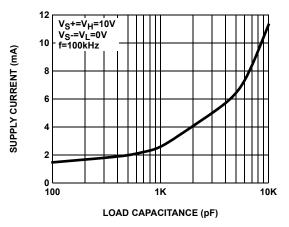

| t <sub>R</sub>      | Rise Time                                    | C <sub>L</sub> = 1000pF          |                 | 13.5 |                 | ns   |

| t <sub>F</sub>      | Fall Time                                    | C <sub>L</sub> = 1000pF          |                 | 13   |                 | ns   |

| $t_{RF\Delta}$      | t <sub>R</sub> , t <sub>F</sub> Mismatch     | C <sub>L</sub> = 1000pF          |                 | 0.5  |                 | ns   |

| t <sub>D</sub> +    | Turn-Off Delay Time                          | C <sub>L</sub> = 1000pF          |                 | 12.5 |                 | ns   |

| t <sub>D</sub> -    | Turn-On Delay Time                           | C <sub>L</sub> = 1000pF          |                 | 14.5 |                 | ns   |

| t <sub>DD</sub>     | t <sub>D-1</sub> - t <sub>D-2</sub> Mismatch | C <sub>L</sub> = 1000pF          |                 | 2    |                 | ns   |

| t <sub>ENABLE</sub> | Enable Delay Time                            |                                  |                 | 12   |                 | ns   |

| Electrical Spe       | <b>Electrical Specifications</b> $V_{S}$ + = +5V, $V_{S}$ - = -5V, $V_{H}$ = +5V, $V_{L}$ = -5V, $T_{A}$ = 25°C, unless otherwise specified. |           |                 |     |                 |      |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|-----|-----------------|------|--|--|--|--|

| PARAMETER            | DESCRIPTION                                                                                                                                  | CONDITION | MIN<br>(Note 8) | ТҮР | MAX<br>(Note 8) | UNIT |  |  |  |  |

| t <sub>DISABLE</sub> | Disable Delay Time                                                                                                                           |           |                 | 12  |                 | ns   |  |  |  |  |

## **Electrical Specifications** $V_{S}$ + = +15V, $V_{S}$ - = 0V, $V_{H}$ = +15V, $V_{L}$ = 0V, $T_{A}$ = 25°C, unless otherwise specified

| PARAMETER            | DESCRIPTION                                  | CONDITION                        | MIN<br>(Note 8) | ТҮР  | MAX<br>(Note 8) | UNIT |

|----------------------|----------------------------------------------|----------------------------------|-----------------|------|-----------------|------|

| INPUT                |                                              | ŀ                                |                 |      | 1               |      |

| V <sub>IH</sub>      | Logic "1" Input Voltage                      |                                  | 2.4             |      |                 | V    |

| I <sub>IH</sub>      | Logic "1" Input Current                      | V <sub>IH</sub> = 5V             |                 | 0.1  | 10              | μA   |

| VIL                  | Logic "0" Input Voltage                      |                                  |                 |      | 0.8             | V    |

| կլ                   | Logic "0" Input Current                      | V <sub>IL</sub> = 0V             |                 | 0.1  | 10              | μA   |

| C <sub>IN</sub>      | Input Capacitance                            |                                  |                 | 3.5  |                 | pF   |

| R <sub>IN</sub>      | Input Resistance                             |                                  |                 | 50   |                 | MΩ   |

| OUTPUT               |                                              |                                  | II              |      | 1               |      |

| R <sub>OH</sub>      | ON Resistance V <sub>H</sub> to OUT          | I <sub>OUT</sub> = -100mA        |                 | 3.5  | 5               | Ω    |

| R <sub>OL</sub>      | ON Resistance V <sub>L</sub> to OUT          | I <sub>OUT</sub> = +100mA        |                 | 3    | 5               | Ω    |

| I <sub>LEAK</sub>    | Output Leakage Current                       | $V_{H} = V_{S}+, V_{L} = V_{S}-$ |                 | 0.1  | 10              | μA   |

| I <sub>PK</sub>      | Peak Output Current                          | Source                           |                 | 2.0  |                 | А    |

|                      |                                              | Sink                             |                 | 2.0  |                 | А    |

| POWER SUPPL          | Y                                            | I                                |                 |      | 4               |      |

| I <sub>S</sub>       | Power Supply Current                         | Inputs = V <sub>S</sub> +        |                 | 0.8  | 2               | mA   |

| SWITCHING CH         | IARACTERISTICS                               |                                  | II              |      | 1               |      |

| t <sub>R</sub>       | Rise Time                                    | C <sub>L</sub> = 1000pF          |                 | 11   |                 | ns   |

| t <sub>F</sub>       | Fall Time                                    | C <sub>L</sub> = 1000pF          |                 | 12   |                 | ns   |

| $t_{RF\Delta}$       | t <sub>R</sub> , t <sub>F</sub> Mismatch     | C <sub>L</sub> = 1000pF          |                 | 1    |                 | ns   |

| t <sub>D</sub> +     | Turn-Off Delay Time                          | C <sub>L</sub> = 1000pF          |                 | 11.5 |                 | ns   |

| t <sub>D</sub> -     | Turn-On Delay Time                           | C <sub>L</sub> = 1000pF          |                 | 13   |                 | ns   |

| t <sub>DD</sub>      | t <sub>D-1</sub> - t <sub>D-2</sub> Mismatch | C <sub>L</sub> = 1000pF          |                 | 1.5  |                 | ns   |

| t <sub>ENABLE</sub>  | Enable Delay Time                            |                                  |                 | 12   |                 | ns   |

| <sup>t</sup> DISABLE | Disable Delay Time                           |                                  |                 | 12   |                 | ns   |

NOTE:

8. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

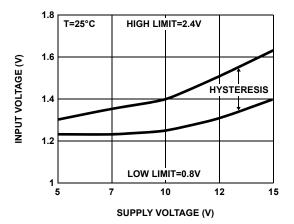

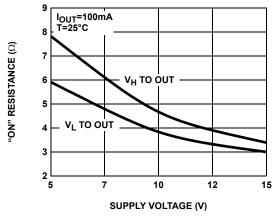

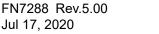

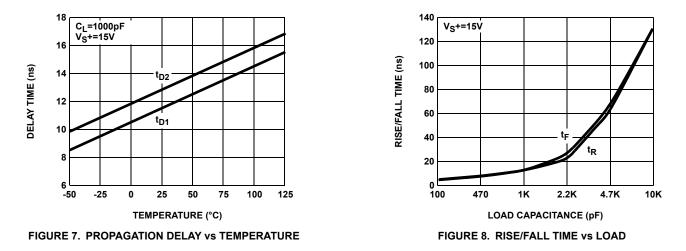

# **Typical Performance Curves**

FIGURE 1. SWITCH THRESHOLD vs SUPPLY VOLTAGE

FIGURE 3. "ON" RESISTANCE vs SUPPLY VOLTAGE

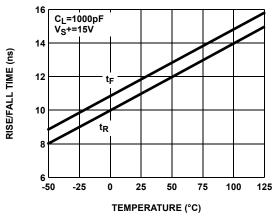

FIGURE 5. RISE/FALL TIME vs TEMPERATURE

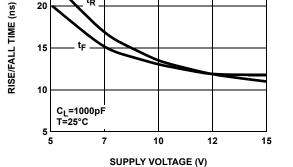

FIGURE 4. RISE/FALL TIME vs SUPPLY VOLTAGE

t<sub>D2</sub>

12

15

t<sub>D1</sub>

10

SUPPLY VOLTAGE (V)

FIGURE 6. PROPAGATION DELAY vs SUPPLY VOLTAGE

25

20

25

20

15

10

5

5

7

DELAY TIME (ns)

C<sub>L</sub>=1000pF

C۵

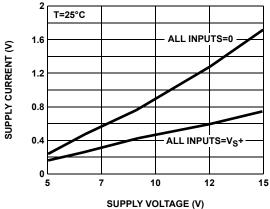

FIGURE 2. QUIESCENT SUPPLY CURRENT vs SUPPLY

# Typical Performance Curves (Continued)

FIGURE 9. SUPPLY CURRENT PER CHANNEL vs CAPACITIVE LOAD

TABLE 1. NOMINAL OPERATING VOLTAGE RANGE

| PIN                                | MIN                     | MAX              |

|------------------------------------|-------------------------|------------------|

| $V_{S}$ + to $V_{S}$ -             | 5V                      | 16.5V            |

| V <sub>S</sub> - to GND            | -5V                     | 0V               |

| V <sub>H</sub>                     | V <sub>S</sub> - + 2.5V | V <sub>S</sub> + |

| VL                                 | V <sub>S</sub> -        | V <sub>S</sub> + |

| V <sub>H</sub> to V <sub>L</sub>   | 0V                      | 16.5V            |

| V <sub>L</sub> to V <sub>S</sub> - | 0V                      | 8V               |

**Timing Diagram**

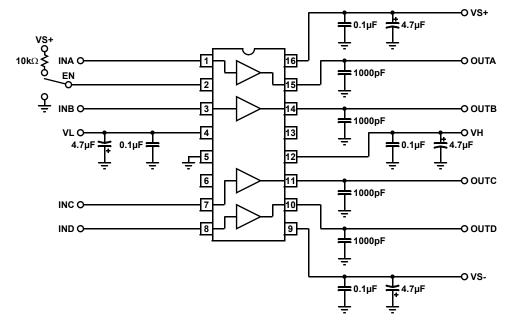

Standard Test Configuration (CS/CU)

# **Pin Descriptions**

| 16-PIN<br>QSOP (0.150"),<br>SO (0.150") | 16-PIN QFN<br>(4x4mm) | NAME | FUNCTION                | EQUIVALENT CIRCUIT                                                  |

|-----------------------------------------|-----------------------|------|-------------------------|---------------------------------------------------------------------|

| 1                                       | 15                    | INA  | Input channel A         | INPUT O<br>VS+<br>VS+<br>VS+<br>VS+<br>VS+<br>VS+<br>VS+<br>VS+     |

| 2                                       | 16                    | OE   | Output Enable           | (Reference Circuit 1)                                               |

| 3                                       | 1                     | INB  | Input channel B         | (Reference Circuit 1)                                               |

| 4                                       | 2, 3                  | VL   | Low voltage input pin   |                                                                     |

| 5                                       | 4                     | GND  | Input logic ground      |                                                                     |

| 6, 13                                   |                       | NC   | No connection           |                                                                     |

| 7                                       | 5                     | INC  | Input channel C         | (Reference Circuit 1)                                               |

| 8                                       | 6                     | IND  | Input channel D         | (Reference Circuit 1)                                               |

| 9                                       | 7                     | VS-  | Negative supply voltage |                                                                     |

| 10                                      | 8                     | OUTD | Output channel D        | O VH<br>VS+<br>O OUTPUT<br>VS-<br>VS-<br>O VS-<br>O VL<br>CIRCUIT 2 |

| 11                                      | 9                     | OUTC | Output channel C        | (Reference Circuit 2)                                               |

| 12                                      | 10, 11                | VH   | High voltage input pin  |                                                                     |

| 14                                      | 12                    | OUTB | Output channel B        | (Reference Circuit 2)                                               |

| 15                                      | 13                    | OUTA | Output channel A        | (Reference Circuit 2)                                               |

| 16                                      | 14                    | VS+  | Positive supply voltage |                                                                     |

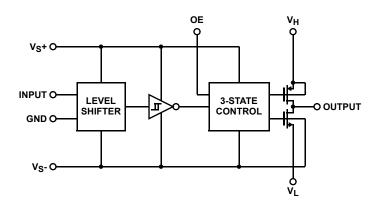

# Block Diagram

# **Applications Information**

## **Product Description**

The EL7457 is a high performance 40MHz high speed quad driver. Each channel of the EL7457 consists of a single P-channel high side driver and a single N-channel low side driver. These  $3\Omega$  devices will pull the output (OUT<sub>X</sub>) to either the high or low voltage, on V<sub>H</sub> and V<sub>L</sub> respectively, depending on the input logic signal (IN<sub>X</sub>). It should be noted that there is only one set of high and low voltage pins.

A common output enable (OE) pin is available on the EL7457. This pin, when pulled low will put all outputs in to the high impedance state.

The EL7457 is available in 16-pin SO (0.150"), 16-pin QSOP, and ultra-small 16-pin QFN packages. The relevant package should be chosen depending on the calculated power dissipation.

## Supply Voltage Range and Input Compatibility

The EL7457 is designed for operation on supplies from 5V to 15V with 10% tolerance (i.e. 4.5V to 18V). The table on page 6 shows the specifications for the relationship between the V<sub>S</sub>+, V<sub>S</sub>-, V<sub>H</sub>, V<sub>L</sub>, and GND pins. The EL7457 does not contain a true analog switch and therefore V<sub>L</sub> should always be less than V<sub>H</sub>.

All input pins are compatible with both 3V and 5V CMOS signals With a positive supply (V<sub>S</sub>+) of 5V, the EL7457 is also compatible with TTL inputs.

## Power Supply Bypassing

When using the EL7457, it is very important to use adequate power supply bypassing. The high switching currents developed by the EL7457 necessitate the use of a bypass capacitor on both the positive and negative supplies. It is recommended that a 4.7 $\mu$ F tantalum capacitor be used in parallel with a 0.1 $\mu$ F low-inductance ceramic MLC capacitor. These should be placed as close to the supply pins as possible. It is also recommended that the V<sub>H</sub> and V<sub>L</sub> pins have some level of bypassing, especially if the EL7457 is driving highly capacitive loads.

## Power Dissipation Calculation

When switching at high speeds, or driving heavy loads, the EL7457 drive capability is limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{JMAX}$  (125°C). It is necessary to calculate the power dissipation for a given application prior to selecting package type.

Power dissipation may be calculated:

$$PD = (V_{S} \times I_{S}) + \sum_{1}^{\cdot} (C_{INT} \times V_{S}^{2} \times f) + (C_{L} \times V_{OUT}^{2} \times f)$$

(EQ. 1)

where:

$V_{S}$  is the total power supply to the EL7457 (from  $V_{S}\text{+}$  to  $V_{S}\text{-})$

$V_{OUT}$  is the swing on the output ( $V_H$  -  $V_L$ )

C<sub>L</sub> is the load capacitance

CINT is the internal load capacitance (80pF max)

I<sub>S</sub> is the quiescent supply current (3mA max)

f is frequency

Having obtained the application's power dissipation, the maximum junction temperature can be calculated:

$$T_{JMAX} = T_{MAX} + \Theta_{JA} \times PD$$

(EQ. 2)

where:

$T_{JMAX}$  is the maximum junction temperature (125°C)

T<sub>MAX</sub> is the maximum ambient operating temperature

PD is the power dissipation calculated above

$\theta_{JA}$  is the thermal resistance, junction to ambient, of the application (package + PCB combination). Refer to the Package Power Dissipation curves on page 6.

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jul 17, 2020 | 5.00     | Updated links throughout.<br>Updated Ordering Information table adding the tape and reel column.<br>Added Revision History section.<br>Updated POD L16.4X4H to the latest revision, the changes are as follows:<br>Added note 7 and the Note 7 references to bottom view and Typ Pattern view<br>Removed "base plane" from side view<br>Updated the lead width dimension from 0.33 ±0.02 to 0.33 ±0.05 |

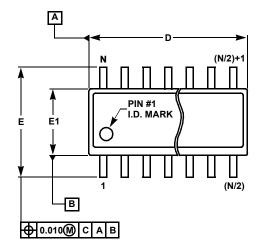

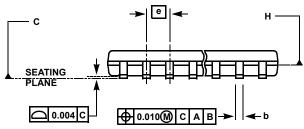

## Package Outline Drawings

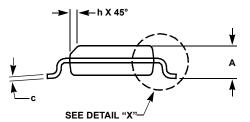

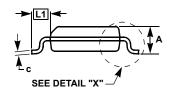

## MDP0027

SMALL OUTLINE PACKAGE FAMILY (SO)

|       |           |                  |                  |                  | INCHES                    |                  |       |       |             |  |  |  |  |

|-------|-----------|------------------|------------------|------------------|---------------------------|------------------|-------|-------|-------------|--|--|--|--|

| NOTES | TOLERANCE | SO28<br>(SOL-28) | SO24<br>(SOL-24) | SO20<br>(SOL-20) | SO16 (0.300")<br>(SOL-16) | SO16<br>(0.150") | SO-14 | SO-8  | SYMBOL SO-8 |  |  |  |  |

| -     | MAX       | 0.104            | 0.104            | 0.104            | 0.104                     | 0.068            | 0.068 | 0.068 | А           |  |  |  |  |

| -     | ±0.003    | 0.007            | 0.007            | 0.007            | 0.007                     | 0.006            | 0.006 | 0.006 | A1          |  |  |  |  |

| -     | ±0.002    | 0.092            | 0.092            | 0.092            | 0.092                     | 0.057            | 0.057 | 0.057 | A2          |  |  |  |  |

| -     | ±0.003    | 0.017            | 0.017            | 0.017            | 0.017                     | 0.017            | 0.017 | 0.017 | b           |  |  |  |  |

| -     | ±0.001    | 0.011            | 0.011            | 0.011            | 0.011                     | 0.009            | 0.009 | 0.009 | С           |  |  |  |  |

| 1, 3  | ±0.004    | 0.704            | 0.606            | 0.504            | 0.406                     | 0.390            | 0.341 | 0.193 | D           |  |  |  |  |

| -     | ±0.008    | 0.406            | 0.406            | 0.406            | 0.406                     | 0.236            | 0.236 | 0.236 | Е           |  |  |  |  |

| 2, 3  | ±0.004    | 0.295            | 0.295            | 0.295            | 0.295                     | 0.154            | 0.154 | 0.154 | E1          |  |  |  |  |

| -     | Basic     | 0.050            | 0.050            | 0.050            | 0.050                     | 0.050            | 0.050 | 0.050 | е           |  |  |  |  |

| -     | ±0.009    | 0.030            | 0.030            | 0.030            | 0.030                     | 0.025            | 0.025 | 0.025 | L           |  |  |  |  |

| -     | Basic     | 0.056            | 0.056            | 0.056            | 0.056                     | 0.041            | 0.041 | 0.041 | L1          |  |  |  |  |

| -     | Reference | 0.020            | 0.020            | 0.020            | 0.020                     | 0.013            | 0.013 | 0.013 | h           |  |  |  |  |

| -     | Reference | 28               | 24               | 20               | 16                        | 16               | 14    | 8     | Ν           |  |  |  |  |

#### NOTES:

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions "D" and "E1" are measured at Datum Plane "H".

4. Dimensioning and tolerancing per ASME Y14.5M-1994

For the most recent package outline drawing, see MDP0040.

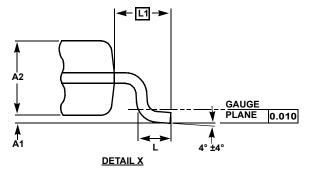

#### MDP0040

QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        | INCHES |        |        |           |            |

|--------|--------|--------|--------|-----------|------------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES      |

| Α      | 0.068  | 0.068  | 0.068  | Max.      | -          |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -          |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -          |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -          |

| С      | 0.008  | 0.008  | 0.008  | ±0.001    | -          |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3       |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -          |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3       |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -          |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -          |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -          |

| Ν      | 16     | 24     | 28     | Reference | -          |

|        |        |        |        | R         | ev. F 2/07 |

#### NOTES:

5. Plastic or metal protrusions of 0.006" maximum per side are not included.

6. Plastic interlead protrusions of 0.010" maximum per side are not included.

7. Dimensions "D" and "E1" are measured at Datum Plane "H".

8. Dimensioning and tolerancing per ASME Y14.5M-1994.

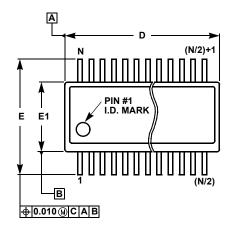

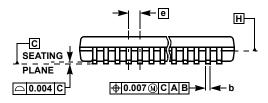

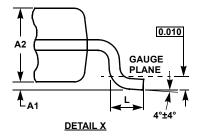

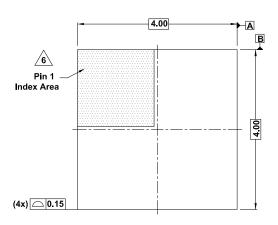

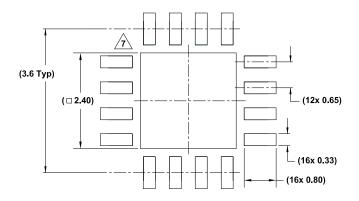

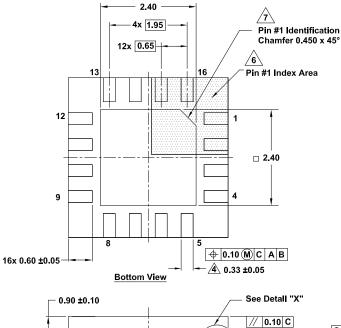

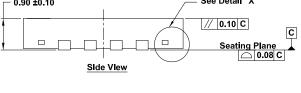

# L16.4x4H

16 Lead Quad Flat No-Lead Plastic Package Rev 1, 7/20

#### For the most recent package outline drawing, see L16.4x4H.

Top View

#### Typical Recommended Land Pattern

Notes:

- 1. Dimensions are in millimeters.

- Dimensions in ( ) for reference only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance: Decimal ±0.05

- A Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone Indicated. The pin #1 identifier can be either a mold or mark feature.

- Pin 1 corner chamfer not required.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/