## **PAC5523 Data Sheet**

**Power Application Controller®**

Multi-Mode Power Manager™

Configurable Analog Front End™

Application Specific Power Drivers™

Arm® Cortex®-M4F Controller Core

### **TABLE OF CONTENTS**

| 1  | GEI         | NERAL DESCRIPTION                              | 9  |  |  |  |  |  |  |  |  |

|----|-------------|------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 2  | PAC         | AC FAMILY APPLICATIONS10                       |    |  |  |  |  |  |  |  |  |

| 3  | PRO         | DDUCT SELECTION SUMMARY                        | 11 |  |  |  |  |  |  |  |  |

| 4  | ORI         | DERING INFORMATION                             | 12 |  |  |  |  |  |  |  |  |

| 5  | FE <i>F</i> | ATURES                                         | 13 |  |  |  |  |  |  |  |  |

|    | 5.1         | Feature Overview                               | 13 |  |  |  |  |  |  |  |  |

| 6  | ABS         | SOLUTE MAXIMUM RATINGS                         | 15 |  |  |  |  |  |  |  |  |

| 7  | ARO         | CHITECTURAL BLOCK DIAGRAM                      | 16 |  |  |  |  |  |  |  |  |

| 8  | PIN         | CONFIGURATION                                  | 17 |  |  |  |  |  |  |  |  |

|    | 8.1         | PAC5523QM                                      | 17 |  |  |  |  |  |  |  |  |

| 9  | PIN         | DESCRIPTION                                    | 18 |  |  |  |  |  |  |  |  |

| 1( | 0 M         | IULTI-MODE POWER MANAGER (MMPM)                | 23 |  |  |  |  |  |  |  |  |

|    | 10.1        | Features                                       | 23 |  |  |  |  |  |  |  |  |

|    | 10.2        | Functional Description                         | 23 |  |  |  |  |  |  |  |  |

|    | 10.3        | Multi-Mode Switching Supply (MMSS) Controller  | 24 |  |  |  |  |  |  |  |  |

|    | 10.4        | Linear Regulators                              | 26 |  |  |  |  |  |  |  |  |

|    | 10.5        | Power-up Sequence                              | 27 |  |  |  |  |  |  |  |  |

|    | 10.6        | Hibernate Mode                                 | 27 |  |  |  |  |  |  |  |  |

|    | 10.7        | Power and Temperature Monitor                  | 28 |  |  |  |  |  |  |  |  |

|    | 10.8        | Voltage Reference                              | 28 |  |  |  |  |  |  |  |  |

|    | 10.9        | Electrical Characteristics                     | 29 |  |  |  |  |  |  |  |  |

|    | 10.10       | Typical Performance Characteristics            | 32 |  |  |  |  |  |  |  |  |

| 1  | 1 C         | ONFIGURABLE ANALOG FRONT END (CAFE)            | 33 |  |  |  |  |  |  |  |  |

|    | 11.1        | Block Diagram                                  | 33 |  |  |  |  |  |  |  |  |

|    | 11.2        | Functional Description                         | 34 |  |  |  |  |  |  |  |  |

|    | 11.3        | Differential Programmable Gain Amplifier (DA)  | 34 |  |  |  |  |  |  |  |  |

|    | 11.4        | Single-Ended Programmable Gain Amplifier (AMP) | 34 |  |  |  |  |  |  |  |  |

|    | 11.5        | General Purpose Comparator (CMP)               | 34 |  |  |  |  |  |  |  |  |

|    | 11.6        | Phase Comparator (PHC)                         | 35 |  |  |  |  |  |  |  |  |

|    | 11.7        | Protection Comparator (PCMP)                   | 35 |  |  |  |  |  |  |  |  |

|    | 11.8  | Analog Output Buffer (BUF)                | 35 |

|----|-------|-------------------------------------------|----|

|    | 11.9  | Analog Front End I/O (AIO)                | 35 |

|    | 11.10 | Push Button (PBTN)                        | 36 |

|    | 11.11 | HP DAC and LP DAC                         | 36 |

|    | 11.12 | ADC Pre-Multiplexer                       | 36 |

|    | 11.13 | Configurable Analog Signal Matrix (CASM)  | 37 |

|    | 11.14 | Configurable Digital Signal Matrix (CDSM) | 37 |

|    | 11.15 | Electrical Characteristics                | 38 |

|    | 11.16 | Typical Performance Characteristics       | 42 |

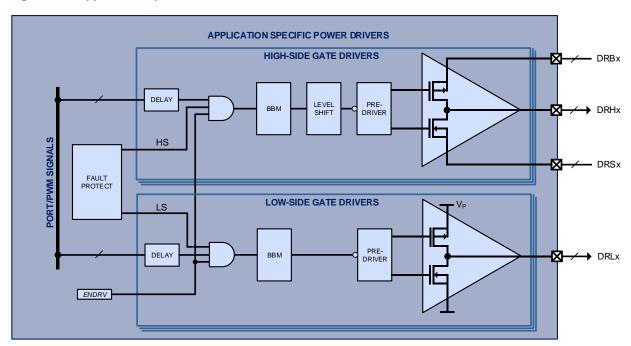

| 12 | 2 A   | PPLICATION SPECIFIC POWER DRIVERS (ASPD)  | 43 |

|    | 12.1  | Features                                  | 43 |

|    | 12.2  | Block Diagram                             | 43 |

|    | 12.3  | Functional Description                    | 43 |

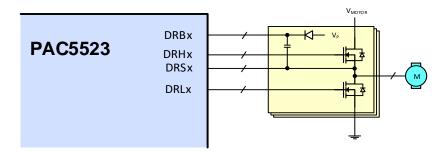

|    | 12.4  | Low-Side Gate Driver                      | 44 |

|    | 12.5  | High-Side Gate Driver                     | 44 |

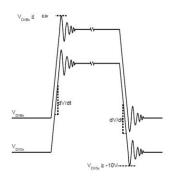

|    | 12.6  | High-Side Switching Transients            | 45 |

|    | 12.7  | Power Drivers Control                     | 45 |

|    | 12.8  | Gate Driver Fault Protection              | 46 |

|    | 12.9  | Electrical Characteristics                | 46 |

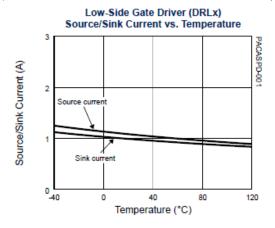

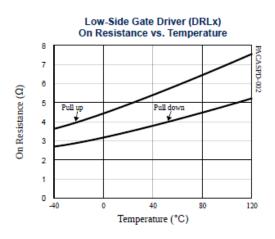

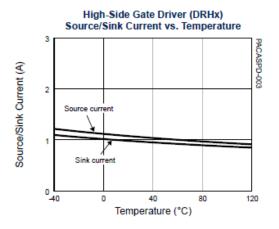

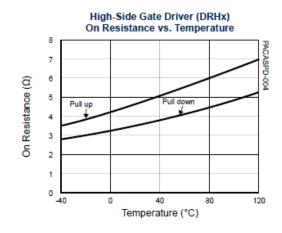

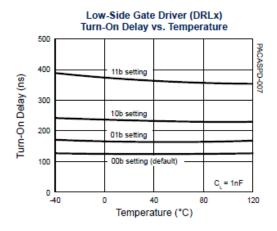

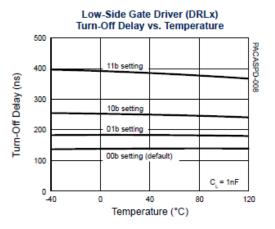

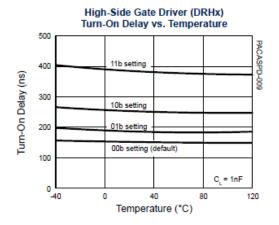

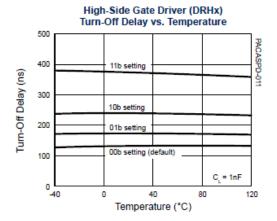

|    | 12.10 | Typical Performance Characteristics       | 48 |

| 1: | 3 S   | OC CONTROL SIGNALS                        | 50 |

|    | 13.1  | High-side and Low-Side Gate Drivers       | 50 |

|    | 13.2  | SPI SOC Bus                               | 52 |

|    | 13.3  | ADC EMUX                                  | 53 |

|    | 13.4  | Analog Interrupts                         | 53 |

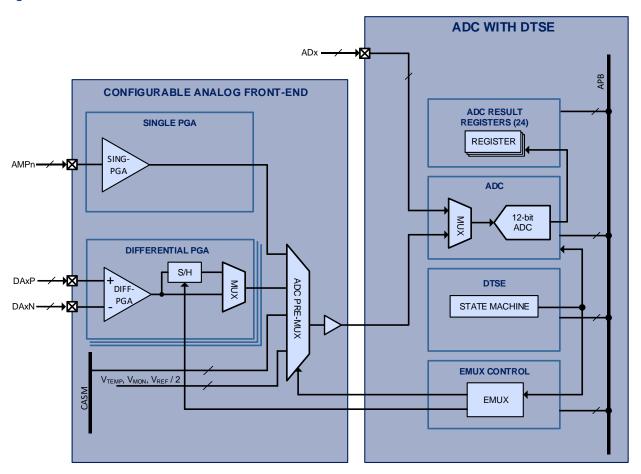

| 14 | 4 A   | .DC/DTSE                                  | 54 |

|    | 14.1  | ADC Block Diagram                         | 54 |

|    | 14.2  | Functional Description                    | 54 |

|    | 14.2  | 2.1 ADC                                   | 54 |

|    | 14.2  | 2.2 Dynamic Triggering and Sample Engine  | 55 |

|    | 14.2  | 2.3 EMUX Control                          | 55 |

|    | 14.3  | Electrical Characteristics                | 56 |

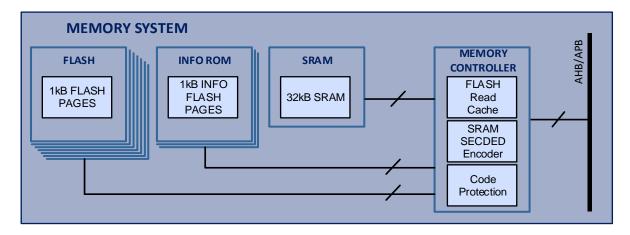

| 15   | MEM   | ORY SYSTEM                            | 57 |

|------|-------|---------------------------------------|----|

| 15.1 | Fea   | atures                                | 57 |

| 15.2 | Me    | mory System Block Diagram             | 57 |

| 15.3 | B Fur | nctional Description                  | 58 |

| 15.4 | Pro   | pgram FLASH                           | 58 |

| 15.5 | INF   | FO FLASH                              | 58 |

| 15.6 | SR    | AM                                    | 58 |

| 15.7 | Co    | de Protection                         | 59 |

| 15.8 | B Ele | ectrical Characteristics              | 60 |

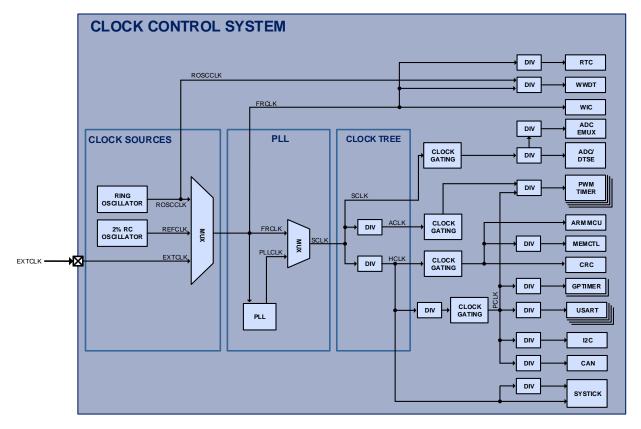

| 16   | SYST  | FEM AND CLOCK CONTROL                 | 61 |

| 16.1 | Fea   | atures                                | 61 |

| 16.2 | 2 Blo | ck Diagram                            | 61 |

| 16.3 | S Clo | ock Sources                           | 62 |

| 16   | 5.3.1 | Ring Oscillator                       | 62 |

| 16   | 5.3.2 | Reference Clock                       | 62 |

| 16   | 5.3.3 | External Clock Input                  | 62 |

| 16.4 | . PLI | L                                     | 62 |

| 16.5 | Clo   | ock Tree                              | 62 |

| 16   | 6.5.1 | FRCLK                                 | 63 |

| 16   | 6.5.2 | SCLK                                  | 63 |

| 16   | 6.5.3 | PCLK                                  | 63 |

| 16   | 6.5.4 | ACLK                                  | 63 |

| 16   | 6.5.5 | HCLK                                  | 63 |

| 16.6 | Ele   | ectrical Characteristics              | 64 |

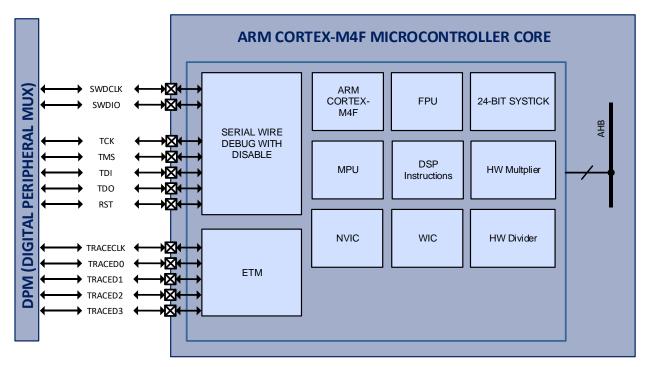

| 17   | ARM   | ® CORTEX®-M4F MCU CORE                | 65 |

| 17.1 | Fea   | atures                                | 65 |

| 17.2 | Blo   | ock Diagram                           | 65 |

| 17.3 | B Fur | nctional Description                  | 66 |

| 17.4 | l Apı | plication Typical Current Consumption | 67 |

| 17.5 | . Ele | ectrical Characteristics              | 68 |

| 18   | 10 CC | ONTROLLER                             | 69 |

| 18.1 | Fea   | atures                                | 69 |

| 18.2 Bl               | ock Diagram                         | 69 |

|-----------------------|-------------------------------------|----|

| 18.3 Fu               | nctional Description                | 70 |

| 18.4 GF               | PIO Current Injection               | 70 |

| 18.5 Pe               | ripheral MUX                        | 71 |

| 18.6 El               | ectrical Characteristics            | 72 |

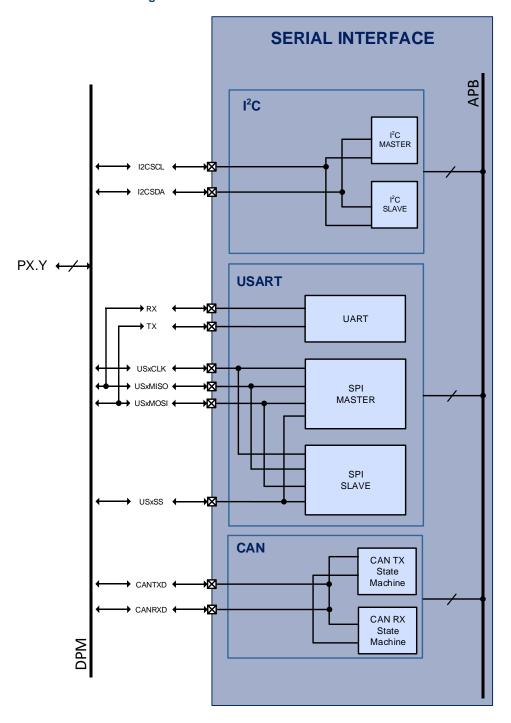

| 19 SER                | IAL INTERFACE                       | 73 |

| 19.1 Blo              | ock Diagram                         | 73 |

| 19.2 Fu               | nctional Description                | 74 |

| 19.3 l <sup>2</sup> C | Controller                          | 74 |

| 19.4 US               | SART                                | 74 |

| 19.4.1                | USART SPI Mode                      | 74 |

| 19.4.2                | USART UART Mode                     | 75 |

| 19.5 CA               | AN                                  | 75 |

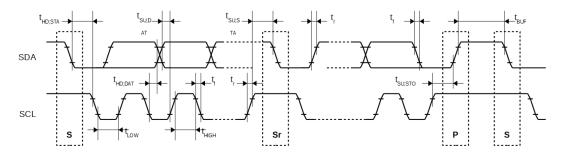

| 19.6 Dy               | namic Characteristics               | 76 |

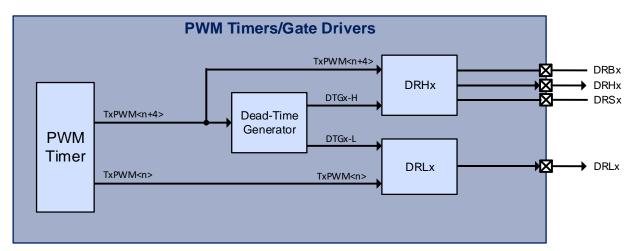

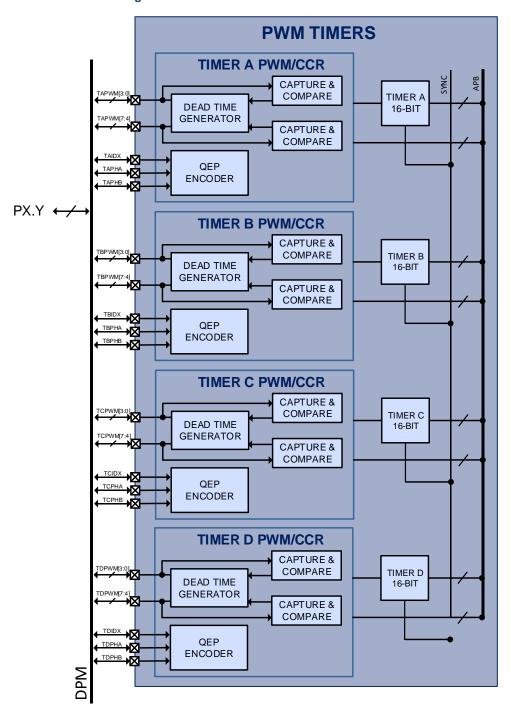

| 20 PWN                | /I TIMERS                           | 78 |

| 20.1 Blo              | ock Diagram                         | 78 |

| 20.2 Tir              | mer Features                        | 79 |

| 20.2.1                | CCR/PWM Timer                       | 79 |

| 20.2.2                | Dead-time Generators (DTG)          | 79 |

| 20.2.3                | QEP Decoder                         | 80 |

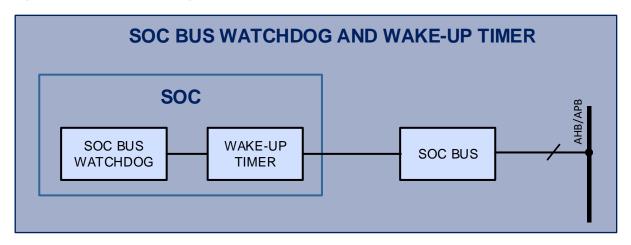

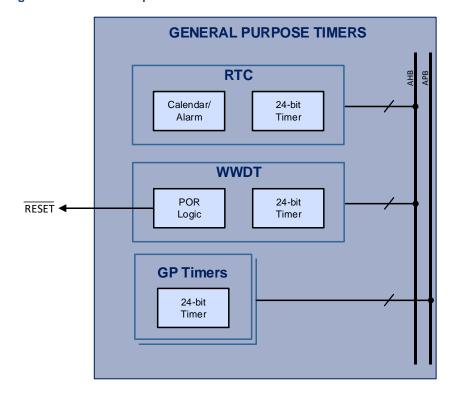

| 21 GEN                | ERAL PURPOSE TIMERS                 | 81 |

| 21.1 Blo              | ock Diagram                         | 81 |

| 21.2 Fu               | nctional Description                | 82 |

| 21.2.1                | SOC Bus Watchdog Timer              | 82 |

| 21.2.2                | Wake-up Timer                       | 82 |

| 21.2.3                | Real-time Clock with Calendar (RTC) | 82 |

| 21.2.4                | Windowed Watchdog Timer (WWDT)      | 82 |

| 21.2.5                | GP Timer (GPT)                      | 82 |

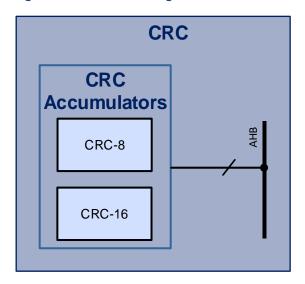

| 22 CRC                |                                     | 83 |

|                       | ock Diagram                         |    |

|                       | nctional Description                |    |

| 23 THE                | RMAL CHARACTERISTICS                | 84 |

# PAC5523 Power Application Controller®

| 24 | APPLICATION EXAMPLES           | .85 |

|----|--------------------------------|-----|

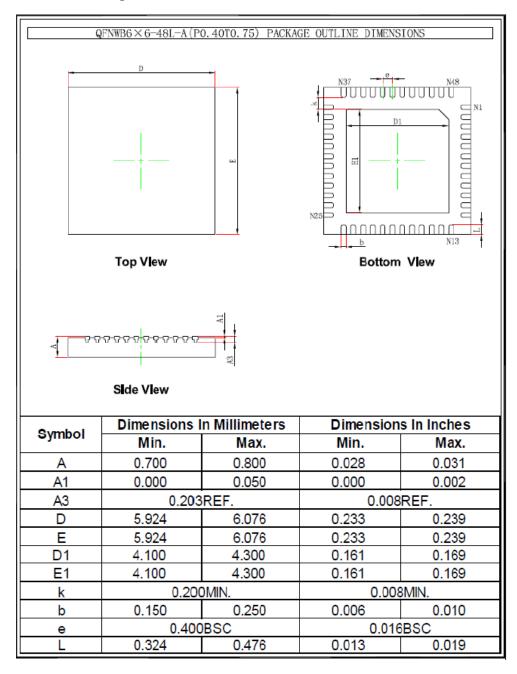

| 25 | PACKAGE OUTLINE AND DIMENSIONS | .86 |

### **LIST OF FIGURES**

| Figure 1-1. PAC5523 Power Application Controller                               | 9  |

|--------------------------------------------------------------------------------|----|

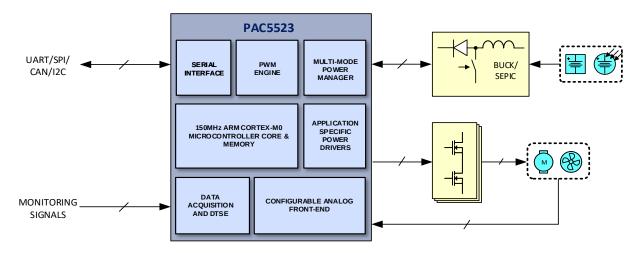

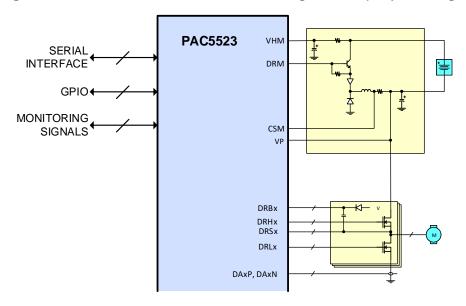

| Figure 2-1 Simplified Application Diagram                                      | 10 |

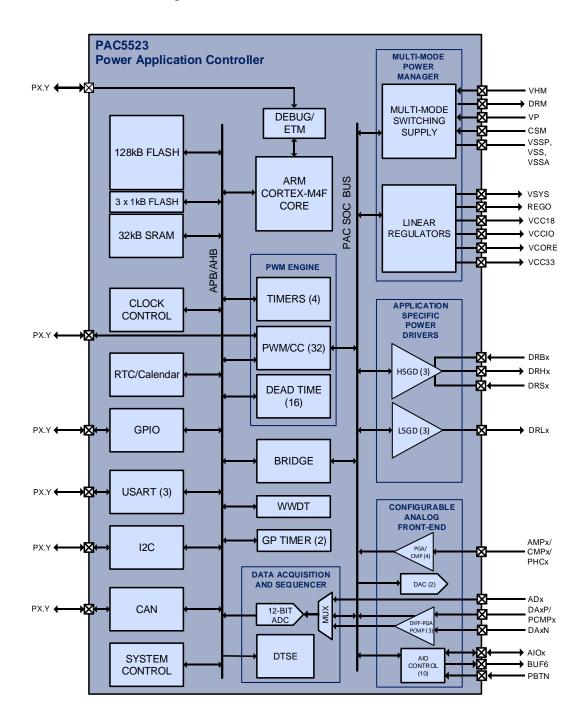

| Figure 7-1 Architectural Block Diagram                                         | 16 |

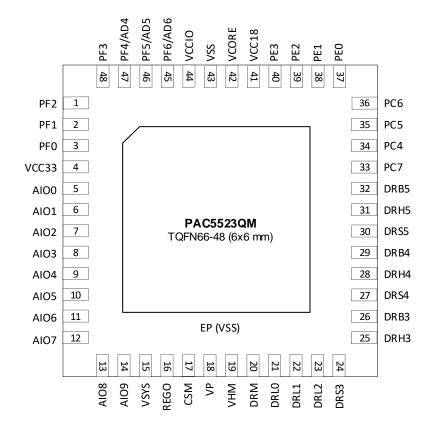

| Figure 8-1 PAC5523QM Pin Configuration (TQFN66-48 Package)                     | 17 |

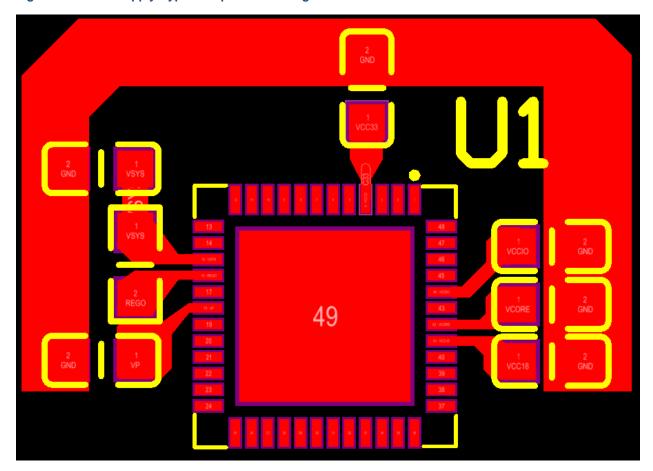

| Figure 9-1 Power Supply Bypass Capacitor Routing                               | 22 |

| Figure 10-1 MMPM Block Diagram                                                 |    |

| Figure 10-2 Buck Mode                                                          | 24 |

| Figure 10-3 SEPIC Mode                                                         | 25 |

| Figure 10-4 Direct Battery Supply                                              | 25 |

| Figure 10-5 Linear Regulators                                                  | 26 |

| Figure 10-6 Power-Up Sequence                                                  | 27 |

| Figure 11-1 Configurable Analog Front End                                      | 33 |

| Figure 11-2 PGA Typical Performance Characteristics                            | 42 |

| Figure 12-1 Application Specific Power Drivers                                 | 43 |

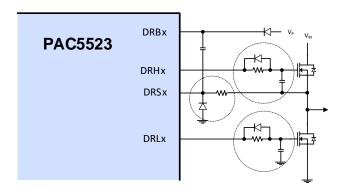

| Figure 12-2 Typical Gate Driver Connections                                    | 44 |

| Figure 12-3 High-Side Switching Transients and Optional Circuitry              | 45 |

| Figure 12-4 ASPD Gate Driver Typical Performance Characteristics               | 48 |

| Figure 12-5 ASPD Gate Driver Typical Performance Characteristics (cont)        | 49 |

| Figure 13-1 SOC Signals for Gate Drivers                                       | 50 |

| Figure 14-1 ADC with DTSE                                                      | 54 |

| Figure 15-1 Memory System                                                      | 57 |

| Figure 16-1 Clock Control System                                               | 61 |

| Figure 17-1 Arm® Cortex®-M4F Microcontroller Core                              |    |

| Figure 18-1 IO Controller Block Diagram                                        | 69 |

| Figure 19-1 Serial Interface Block Diagram                                     | 73 |

| Figure 19-2 I <sup>2</sup> C Timing Diagram                                    | 77 |

| Figure 20-1 PWM Timers Block Diagram                                           | 78 |

| Figure 21-1 SOC Bus Watchdog and Wake-up Timer                                 | 81 |

| Figure 21-2 General Purpose Timers                                             | 81 |

| Figure 22-1 CRC Block Diagram                                                  | 83 |

| Figure 24-1 Sensorless FOC/BEMF Motor Drive Using PAC5523 (Simplified Diagram) | 85 |

| Figure 25-1 TQFN66-48 Package Outline and Dimensions                           | 86 |

### **LIST OF TABLES**

| Table 3-1 Product Selection Summary                                                  | 11 |

|--------------------------------------------------------------------------------------|----|

| Table 4-1 Ordering Information                                                       | 12 |

| Table 6-1 Absolute Maximum Ratings                                                   | 15 |

| Table 9-1 Multi-Mode Power Manager (MMPM) and System Pin Description                 | 18 |

| Table 9-2 Configurable Analog Front End (CAFE) Pin Description                       | 19 |

| Table 9-3 Application Specific Power Drivers (ASPD) Pin Description                  | 20 |

| Table 9-4 I/O Ports Pin Description                                                  | 21 |

| Table 10-1 Multi-Mode Switching Supply Controller Electrical Characteristics         | 29 |

| Table 10-2 Linear Regulators Electrical Characteristics                              | 30 |

| Table 10-3. Power System Electrical Characteristics                                  | 31 |

| Table 11-1 Differential Programmable Gain Amplifier (DA) Electrical Characteristics  | 38 |

| Table 11-2 Single-Ended Programmable Gain Amplifier (AMP) Electrical Characteristics | 39 |

| Table 11-3 General Purpose Comparator (CMP) Electrical Characteristics               | 39 |

| Table 11-4 Phase Comparator (PHC) Electrical Characteristics                         | 40 |

| Table 11-5 Protection Comparator (PCMP) Electrical Characteristics                   | 40 |

| Table 11-6 Analog Output Buffer (BUF) Electrical Characteristics                     | 40 |

| Table 11-7 Analog Front End (AIO) Electrical Characteristics                         | 41 |

| Table 11-8 Push Button (PBTN) Electrical Characteristics                             | 41 |

| Table 11-9 HP DAC and LP DAC Electrical Characteristics                              | 41 |

| Table 12-1 Power Driver Resources by Part Numbers                                    | 44 |

| Table 12-2 Power Driver Delay Configuration                                          | 45 |

| Table 12-3 Gate Driver Electrical Characteristics                                    | 46 |

| Table 13-1 PWM to ASPD Gate Driver Options (DTG Enabled)                             | 51 |

| Table 13-2 PWM to ASPD Gate Driver Options (DTG Disabled)                            | 51 |

| Table 13-3 SPI SOC Bus Connections                                                   | 52 |

| Table 13-4 SPI SOC Bus Connections                                                   | 53 |

| Table 13-5 Analog Interrupts                                                         | 53 |

| Table 14-1 ADC and DTSE Electrical Characteristics                                   | 56 |

| Table 15-1 Code Protection Level Description                                         | 59 |

| Table 15-2 Memory System Electrical Characteristics                                  | 60 |

| Table 16-1 CCS Electrical Characteristics                                            |    |

| Table 17-1 PAC55XX Application Typical Current Consumption                           | 67 |

| Table 17-2 MCU and Clock Control System Electrical Characteristics                   | 68 |

| Table 18-1 PAC5523 Peripheral Pin MUX                                                | 71 |

| Table 18-2 IO Controller Electrical Characteristics                                  | 72 |

| Table 19-1 Serial Interface Dynamic Characteristics                                  | 76 |

| Table 19-2 I <sup>2</sup> C Dynamic Characteristics                                  | 76 |

| Table 23-1 Thermal Characteristics                                                   | 84 |

#### 1 GENERAL DESCRIPTION

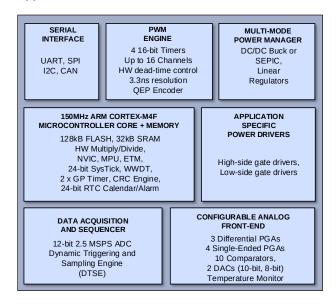

The PAC5523 is a Power Application Controller® (PAC) product that is optimized for high-speed BLDC motor control. The PAC5523 integrates a 150MHz Arm® Cortex®-M4F 32-bit microcontroller core with Active-Semi's proprietary and patent-pending Multi-Mode Power Manager<sup>TM</sup>, Configurable Analog Front-End<sup>TM</sup> and Application Specific Power Drivers<sup>TM</sup> to form the most compact microcontroller-based power and motor control solution available.

The PAC5523 microcontroller features 128kB of embedded FLASH and 32kB of SRAM memory, a 2.5MSPS analog-to-digital converter (ADC) with programmable auto-sampling of up to 24 conversion sequences, 3.3V IO, flexible clock control system, PWM and general-purpose timers and several serial communications interfaces.

The Multi-Mode Power Manager (MMPM) provides "all-in-one" efficient power management solution for multiple types of power sources. It features a configurable multi-mode switching supply controller capable of operating a buck or SEPIC converter and up to four linear regulated voltage supplies. The Application Specific Power Drivers (ASPD) are power drivers designed for half bridge, H-bridge, 3-phase, intelligent power module (IPM), and general-purpose driving. The Configurable Analog Front End (CAFE) comprises differential programmable gain amplifiers, single-ended programmable gain amplifiers, comparators, digital-to-analog converters, and I/Os for programmable and inter-connectible signal sampling, feedback amplification, and sensor monitoring of multiple analog input signals.

Figure 1-1. PAC5523 Power Application Controller

The PAC5523 is available in a 48-pin, 6x6mm TQFN package.

### 2 PAC FAMILY APPLICATIONS

- General-purpose high-voltage system controllers

- Home appliances

- Ceiling Fans

- Standing Fans

- Compressors

- Power Tools

- Garden Tools

- Motor Controllers

- Industrial Applications

- Drone/RC

Figure 2-1 Simplified Application Diagram

### 3 PRODUCT SELECTION SUMMARY

**Table 3-1 Product Selection Summary**

|         |                       | _            | WER<br>AGER   |               | CONF     |     |            |     | S           | APPLICA<br>PECIFIC F<br>DRIVE              | POWER            |             | M           | ICRO       | CONTROLL                      | .ER                                             |      |                                                                |                        |

|---------|-----------------------|--------------|---------------|---------------|----------|-----|------------|-----|-------------|--------------------------------------------|------------------|-------------|-------------|------------|-------------------------------|-------------------------------------------------|------|----------------------------------------------------------------|------------------------|

|         | PIN<br>PKG            |              | INPUT VOLTAGE | MULTI-MODE SW | DIFF-PGA | PGA | COMPARATOR | DAC | ADC CHANNEL | VSRC                                       | POWER DRIVER     | PWM CHANNEL | SPEED (MHz) | FLASH (KB) | SRAM (kB)                     | GPIO                                            | COMM | XTAL                                                           | PRIMARY<br>APPLICATION |

| PAC5523 | 48-pin<br>6x6<br>TQFN | 5.2 –<br>70V | Y             | 3             | 4        | 10  | 2          | 15  | 70V         | 3 LS<br>(1.5A/1.5A)<br>3 HS<br>(1.5A/1.5A) | 6@VP<br>15@VCCIO | 150         | 128         | 32         | 10@VSYS<br>3 @ VP<br>15@VCCIO | UART<br>SPI<br>I2C<br>CAN<br>SWD<br>JTAG<br>ETM | N    | 3 half-bridge<br>3 phase control<br>BEMF Trapezoidal<br>or FOC |                        |

Notes: DIFF-PGA = differential programmable gain amplifier; HS = high-side, LS = low-side, PGA = programmable gain amplifier, VSRC = Bootstrap Voltage Source

### 4 ORDERING INFORMATION

#### **Table 4-1 Ordering Information**

| PART NUMBER <sup>1</sup> | TEMPERATURE<br>RANGE | PACKAGE   | PINS             | PACKING                    |  |

|--------------------------|----------------------|-----------|------------------|----------------------------|--|

| PAC5523QM                | 1000 to 10500        | TOFNES 49 | 40 L Evenand Dad | Tray (4900 piece)          |  |

| PAC5523QM-T              | -40°C to 125°C       | TQFN66-48 | 48 + Exposed Pad | Tape and Reel (3000 piece) |  |

<sup>&</sup>lt;sup>1</sup> See *Product Selection Summary* for product features for each part number

### **5 FEATURES**

#### 5.1 Feature Overview

#### Proprietary Multi-Mode Power Manager

- Multi-mode switching supply controller configurable for DC/DC Buck or SEPIC topologies

- Direct battery supply from 5V 20V

- o 4 Linear regulators with power and hibernate management

- Power and temperature monitor, warning, fault detection

#### Proprietary Configurable Analog Front-End

- o 10 Analog Front-End IO pins

- o 3 Differential Programmable Gain Amplifiers

- o 4 Single-ended Programmable Gain Amplifiers

- o Programmable Over-Current Protection

- o 10 Comparators

- o 2 DACs (10-bit and 8-bit)

- Integrated BEMF comparator mode with virtual center-tap

#### Proprietary Application Specific Power Drivers

- o 3 Low-side and 3 High-Side gate drivers with 1.5A gate driving capacity

- Configurable propagation delay and fault protection

#### 150MHz Arm® Cortex®-M4F 32-bit Microcontroller Core

- o Single-cycle 32-bit x 32-bit hardware multiplier

- 32-bit hardware divider

- DSP Instructions and Saturation Arithmetic Support

- Integrated sleep and deep sleep modes

- Single-precision Floating Point Unit (FPU)

- 8-region Memory Protection Unit (MPU)

- Nested Vectored Interrupt Controller (NVIC) with 32 Interrupts with 8 levels of priority

- 24-Bit SysTick Timer

- Wake-up Interrupt Controller (WIC) allowing power-saving sleep modes

- Clock-gating allowing low-power operation

- Embedded Trace Macrocell (ETM) for in-system debugging at real-time without breakpoints

#### Memory

- 128kB FLASH

- 32kB SRAM with ECC

- o 2 x 1kB INFO FLASH area for manufacturing information

- 1 x 1kB INFO FLASH area for user parameter storage and application configuration or code

- Code Protection

#### Analog to Digital Converter (ADC)

- o 12-bit resolution

- 2.5MSPS

- Programmable Dynamic Triggering and Sampling Engine (DTSE)

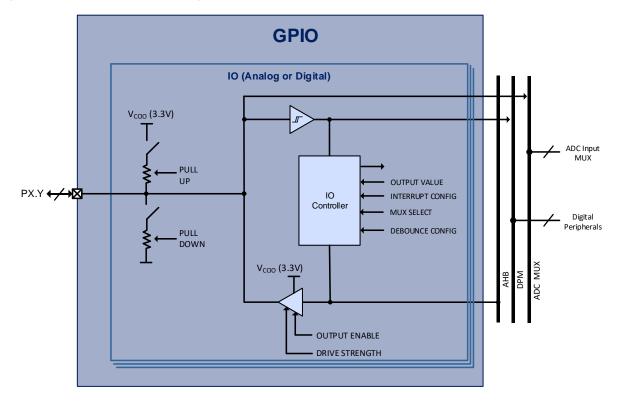

#### I/O

- 3.3V Digital Input/Output or Analog Input for ADC

- Configurable weak pull-up and pull-down

- Configurable drive strength (6mA to 25mA minimum)

- Dedicated Integrated IO power supply (3.3V)

- Flexible peripheral MUX allowing each IO pin to be configured with one of up to 8 peripheral functions

- o Flexible Interrupt Controller

#### Flexible Clock Control System (CCS)

- 300MHz PLL from internal 2% oscillator

- o 20MHz Ring Oscillator

- 20MHz External Clock Input

#### Timing Generators

- Four 16-bit timers with up to 32 PWM/CC blocks

- 16 Programmable Hardware Dead-time generators

- Up to 300MHz input clock for high-resolution PWM

- 16-bit Windowed Watchdog Timer (WWDT)

- o 24-bit Real-time Clock (RTC) with Calendar and Alarm Functions

- 24-bit SysTick Timer

- 2 x 24-bit General-purpose count-down timers with interrupt

- Wake-up timer for sleep modes from 0.125s to 8s

#### Communication Peripherals

- o 3 x USART

- SPI or UART modes

- SPI Master/Slave, up to 25MHz

- UART, up to 1Mbps

- I2C Master/Slave

- CAN 2.0A/B Controller

- Single Wire Debugger (SWD)/JTAG

- Embedded Trace Macrocell (ETM)

#### 4-Level User-Configurable Code Protection

- 96-bit Unique ID

- CRC Engine

- o Offloads software for communications and safety protocol through hardware acceleration

- Configurable Polynomial (CRC-16 or CRC-8)

- o Configurable Input Data Width, Input and Output Reflection

- Programmable Seed Value

### **6 ABSOLUTE MAXIMUM RATINGS**

Table 6-1 Absolute Maximum Ratings<sup>2</sup>

| PARA                                        | VALUE                        | UNIT                           |                  |

|---------------------------------------------|------------------------------|--------------------------------|------------------|

| VHM, DRM to VSSP                            | -0.3 to 72                   | V                              |                  |

| VP to VSS                                   | -0.3 to 20                   | V                              |                  |

| CSM, REGO to VSS                            | -0.3 to V <sub>P</sub> + 0.3 | V                              |                  |

| VSYS, VCCIO, AIO6 to VSS                    | -0.3 to 6                    | V                              |                  |

| VCC33 to VSS                                |                              | -0.3 to 4.1                    | V                |

| VCORE to VSS                                |                              | -0.3 to 1.44                   | V                |

| VCC18 to VSS                                |                              | -0.3 to 2.5                    | V                |

| AIO[05, 79] to VSS                          |                              | -0.3 to V <sub>SYS</sub> + 0.3 | V                |

| PC[07], PE[07], PF[07] to VSS               |                              | -0.3 to 4.6                    | V                |

| PC[07], PE[07], PF[07] pin injection curre  | nt                           | 25                             | mA               |

| PC[07], PE[07], PF[07] sum of all pin inje- | 50                           | mA                             |                  |

| DRLx to VSSP                                | -0.3 to VP + 0.3             | V                              |                  |

| DRBx to VSSP                                |                              | -0.3 to 84                     | V                |

| DRSx to VSSP                                |                              | -6 to 72                       | V                |

| DRSx allowable offset slew rate (dVDRSx/dt) |                              | 5                              | V/ns             |

| DRBx, DRHx to respective DRSx               |                              | -0.3 to 20                     | V                |

| VSSP, VSSA to VSS                           |                              | -0.3 to 0.3                    | V                |

| VSS, VSYS, DRLx, DRHx, VSYSSW RMS cu        | urrent <sup>3</sup>          | 0.2                            | A <sub>RMS</sub> |

| VSSP RMS current <sup>3</sup>               | 0.4                          | A <sub>RMS</sub>               |                  |

| VP RMS current <sup>3</sup>                 | 0.6                          | A <sub>RMS</sub>               |                  |

| Operating temperature range                 | -40 to 125                   | °C                             |                  |

| Floatroctatio Discharge (FCD)               | Human body model (JEDEC)     | 2                              | kV               |

| Electrostatic Discharge (ESD)               | Charge device model (JEDEC)  | 1                              | kV               |

<sup>&</sup>lt;sup>2</sup> Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

<sup>&</sup>lt;sup>3</sup> Peak current can be 10 times higher than RMS value for pulses shorter than 10μs

### 7 ARCHITECTURAL BLOCK DIAGRAM

Figure 7-1 Architectural Block Diagram

### 8 PIN CONFIGURATION

#### 8.1 PAC5523QM

Figure 8-1 PAC5523QM Pin Configuration (TQFN66-48 Package)

### 9 PIN DESCRIPTION

Table 9-1 Multi-Mode Power Manager (MMPM) and System Pin Description

| PIN NAME | PIN<br>NUMBER | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

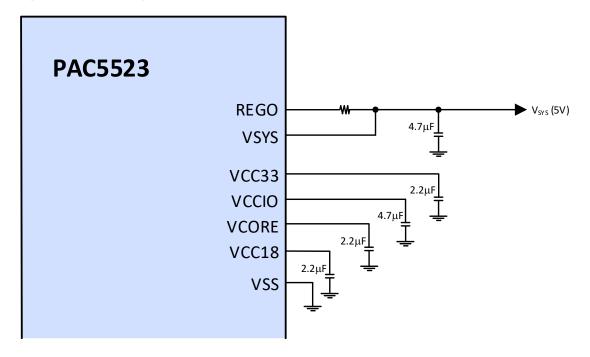

| VCC33    | 4             | Power | Internally generated 3.3V power supply. Connect to a 2.2µF or higher value ceramic capacitor from V <sub>CC33</sub> to V <sub>SSA</sub> .                                                                                                                                                                                                                                                                                   |

| VSYS     | 15            | Power | 5V System power supply. Connect to a 6.8μF (20%) or higher ceramic capacitor from V <sub>SYS</sub> to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                     |

| REGO     | 16            | Power | System regulator output. Connect to V <sub>SYS</sub> directly or through an external power-dissipating resistor.                                                                                                                                                                                                                                                                                                            |

| CSM      | 17            | Power | Switching supply current sense input. Connect to the positive side of the current sense resistor.                                                                                                                                                                                                                                                                                                                           |

| VP       | 18            | Power | Main power supply. Provides power to the power drivers as well as voltage feedback path for the switching supply. Connect a properly sized supply bypass capacitor in parallel with a $0.1\mu F$ ceramic capacitor from $V_P$ to $V_{SS}$ for voltage loop stabilization. This pin requires good capacitive bypassing to $V_{SS}$ , so the ceramic capacitor must be connected with a shorter than 10mm trace from the pin. |

| VHM      | 19            | Power | Switching supply controller supply input. Connect a 1 $\mu$ F or higher value ceramic capacitor, or a 0.1 $\mu$ F ceramic capacitor in parallel with a 10 $\mu$ F or higher electrolytic capacitor from V <sub>HM</sub> to V <sub>SSP</sub> . This pin requires good capacitive bypassing to V <sub>SSP</sub> , so the ceramic capacitor must be connected with a shorter than 10mm trace from the pin.                     |

| DRM      | 20            | Power | Switching supply driver output. Connect to the base or gate of the external power NPN or n-channel MOSFET. See User Guide and application notes.                                                                                                                                                                                                                                                                            |

| VCC18    | 41            | Power | Internally generated 1.8V power supply. Connect a 2.2µF or higher value ceramic capacitor from V <sub>CC18</sub> to V <sub>SSA</sub> .                                                                                                                                                                                                                                                                                      |

| VCORE    | 42            | Power | Internally generated 1.2V core power supply. Connect a 2.2 $\mu$ F or higher value ceramic capacitor from V <sub>CORE</sub> to V <sub>SSA</sub> .                                                                                                                                                                                                                                                                           |

| VSS      | 43            | Power | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCCIO    | 44            | Power | Internally generated digital I/O 3.3V power supply. Connect a 4.7 $\mu$ F or higher value ceramic capacitor from V <sub>CCIO</sub> to V <sub>SSA</sub> .                                                                                                                                                                                                                                                                    |

| EP (VSS) | EP            | Power | Exposed pad. Must be connected to $V_{\text{SS}}$ in a star ground configuration. Connect to a large PCB copper area for power dissipation heat sinking.                                                                                                                                                                                                                                                                    |

Table 9-2 Configurable Analog Front End (CAFE) Pin Description

| PIN NAME | PIN<br>NUMBER | FUNCTION | TYPE   | DESCRIPTION                        |

|----------|---------------|----------|--------|------------------------------------|

| AIO0     | 5             | AIO0     | I/O    | Analog front end I/O 0.            |

| Alou     | 3             | DA0N     | Analog | Differential PGA 0 negative input. |

| AIO1     | 6             | AIO1     | I/O    | Analog front end I/O 1.            |

| AIO1     | O             | DA0P     | Analog | Differential PGA 0 positive input. |

| AIO2     | 7             | AIO2     | I/O    | Analog front end I/O 2.            |

| AIOZ     | 1             | DA1N     | Analog | Differential PGA 1 negative input. |

| AIO3     | 8             | AIO3     | I/O    | Analog front end I/O 3.            |

| AlO3     | 0             | DA1P     | Analog | Differential PGA 1 positive input. |

| AIO4     | 9             | AIO4     | I/O    | Analog front end I/O 4.            |

| AIO4     | 9             | DA2N     | Analog | Differential PGA 2 negative input. |

| 4105     | 40            | AIO5     | I/O    | Analog front end I/O 5.            |

| AIO5     | 10            | DA2P     | Analog | Differential PGA 2 positive input. |

|          |               | AIO6     | I/O    | Analog front end I/O 6.            |

|          | 11            | AMP6     | Analog | PGA input 6.                       |

| AIO6     |               | CMP6     | Analog | Comparator input 6.                |

|          |               | BUF6     | Analog | Buffer output 6.                   |

|          |               | PBTN     | Analog | Push button input.                 |

|          | 40            | AIO7     | I/O    | Analog front end I/O 7.            |

| 4107     |               | AMP7     | Analog | PGA input 7.                       |

| AIO7     | 12            | CMP7     | Analog | Comparator input 7.                |

|          |               | PHC7     | Analog | Phase comparator input 7.          |

|          |               | AIO8     | I/O    | Analog front end I/O 8.            |

| 4100     | 40            | AMP8     | Analog | PGA input 8.                       |

| AIO8     | 13            | CMP8     | Analog | Comparator input 8.                |

|          |               | PHC8     | Analog | Phase comparator input 8.          |

|          |               | AIO9     | I/O    | Analog front end I/O 9.            |

| 4100     | 4.4           | AMP9     | Analog | PGA input 9.                       |

| AIO9     | 14            | CMP9     | Analog | Comparator input 9.                |

|          |               | PHC9     | Analog | Phase comparator input 9.          |

#### Table 9-3 Application Specific Power Drivers (ASPD) Pin Description

| PIN NAME | PIN<br>NUMBER | TYPE   | DESCRIPTION                        |

|----------|---------------|--------|------------------------------------|

| DRL0     | 21            | Analog | Low-side gate driver 0.            |

| DRL1     | 22            | Analog | Low-side gate driver 1.            |

| DRL2     | 23            | Analog | Low-side gate driver 2.            |

| DRS3     | 24            | Analog | High-side gate driver source 3.    |

| DRH3     | 25            | Analog | High-side gate driver 3.           |

| DRB3     | 26            | Analog | High-side gate driver bootstrap 3. |

| DRS4     | 27            | Analog | High-side gate driver source 4.    |

| DRH4     | 28            | Analog | High-side gate driver 4.           |

| DRB4     | 29            | Analog | High-side gate driver bootstrap 4. |

| DRS5     | 30            | Analog | High-side gate driver source 5.    |

| DRH5     | 31            | Analog | High-side gate driver 5.           |

| DRB5     | 32            | Analog | High-side gate driver bootstrap 5. |

#### **Table 9-4 I/O Ports Pin Description**

| PIN NAME | PIN<br>NUMBER | FUNCTION | TYPE         | DESCRIPTION <sup>4</sup> |

|----------|---------------|----------|--------------|--------------------------|

| PF2      | 1             | PF2      | I/O          | I/O port PF2.            |

| PF1      | 2             | PF1      | I/O          | I/O port PF1.            |

| PF0      | 3             | PF0      | I/O          | I/O port PF0.            |

| PC7      | 33            | PC7      | I/O          | I/O port PC7.            |

| PC4      | 34            | PC4      | I/O          | I/O port PC4.            |

| PC5      | 35            | PC5      | I/O          | IO port PC5.             |

| PC6      | 36            | PC6      | I/O          | I/O port PC6.            |

| PE0      | 37            | PE0      | I/O          | I/O port PE0.            |

| PE1      | 38            | PE1      | I/O          | I/O port PE1.            |

| PE2      | 39            | PE2      | I/O          | I/O port PE2.            |

| PE3      | 40            | PE3      | I/O          | I/O port PE3.            |

| PF6      | 45            | PF6      | I/O          | I/O port PF6.            |

| PFO      |               | AD6      | Analog Input | ADC channel ADC6.        |

| PF5      | 46            | PF5      | I/O          | I/O port PF5.            |

| FFS      |               | AD5      | Analog Input | ADC channel ADC5.        |

| PF4      | 47            | PF4      | I/O          | I/O port PF4.            |

| F F 4    |               | AD4      | Analog Input | ADC channel ADC4.        |

| PF3      | 48            | PF3      | I/O          | I/O port PF3.            |

$<sup>^4</sup>$  For a full description of all of the pin configurations for each digital I/O, see the PAC55XX Family User Guide for the Peripheral MUX.

Figure 9-1 Power Supply Bypass Capacitor Routing

### 10 MULTI-MODE POWER MANAGER (MMPM)

#### 10.1 Features

- Multi-mode switching supply controller configurable as buck or SEPIC

- DC supply up to 70V input

- Direct DC input of up to 20V with no DC/DC

- 5 linear regulators with power and hibernate management, including V<sub>REF</sub> for ADC

- Power and temperature monitor, warning, and fault detection

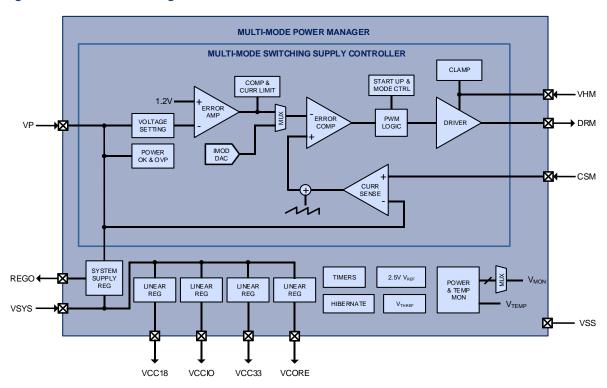

Figure 10-1 MMPM Block Diagram

#### 10.2 Functional Description

The Multi-Mode Power Manager (Figure 10-1) is optimized to efficiently provide "all-in-one" power management required by the PAC and associated application circuitry. It incorporates a dedicated multi-mode switching supply (MMSS) controller operable as a Buck or SEPIC converter to efficiently convert power from a DC input source to generate a main supply output  $V_P$ . Five linear regulators provide  $V_{CC18}$ ,  $V_{SYS}$ ,  $V_{CCIO}$ ,  $V_{CC33}$ , and  $V_{CORE}$  supplies for MCU FLASH, 5V system, 3.3V I/O, 3.3V mixed signal, and 1.2V microcontroller core circuitry. The power manager also handles system functions including internal reference generation, timers, hibernate mode management, and power and temperature monitoring.

#### 10.3 Multi-Mode Switching Supply (MMSS) Controller

The MMSS controller drives an external power transistor for pulse-width modulation switching of an inductor or transformer for power conversion. The DRM output drives the gate of the N-CH MOSFET or the base of the NPN between the V<sub>HM</sub> on state and V<sub>SSP</sub> off state at proper duty cycle and switching frequency to ensure that the main supply voltage V<sub>P</sub> is regulated. The V<sub>P</sub> regulation voltage is initially set to 15V during start up, and can be reconfigured to be 9V or 12V by the microcontroller after initialization. When V<sub>P</sub> is lower than the target regulation voltage, the internal feedback control circuitry causes the inductor current to increase to raise V<sub>P</sub>. Conversely, when V<sub>P</sub> is higher than the regulation voltage, the feedback loop control causes the inductor current to decrease to lower V<sub>P</sub>. The feedback loop is internally stabilized. The output current capability of the switching supply is determined by the external current sense resistor. In the high-side current sense buck or SEPIC mode, the inductor current signal is sensed differentially between the CSM pin and V<sub>P</sub>, and has a peak current limit threshold of 0.26V.

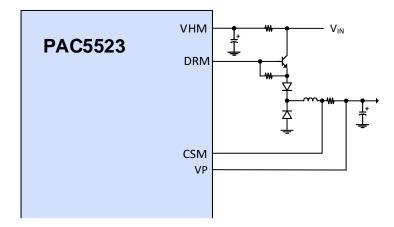

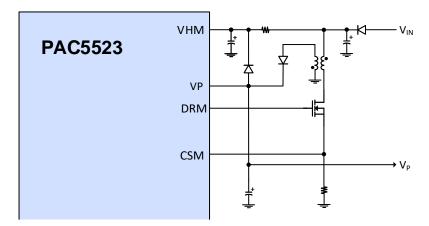

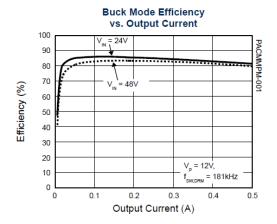

The MMSS controller is flexible and configurable as a buck or SEPIC converter. Input sources include battery supply for buck mode (Figure 10-2) or SEPIC mode (Figure 10-3). The MMSS controller operational mode is determined by external configuration and register settings from the microcontroller after power up. It can operate in either high-side or low-side current sense mode, and does not require external feedback loop compensation circuitry.

Figure 10-2 Buck Mode

Figure 10-3 SEPIC Mode

The MMSS detects and selects between high-side and low-side mode during start up based on the placement of the current sense resistor and the CSM pin voltage. It employs a safe start up mode with a 9.5kHz switching frequency until VP exceeds 4.3V under-voltage-lockout threshold, then transitions to the 45kHz default switching frequency for at least 6ms to bring VP close to the target voltage, before enabling the linear regulators. Any extra load should only be applied after the supplies are available and the microprocessor has initialized. The switching frequency can be reconfigured by the microprocessor to be 181kHz to 500kHz in the high switching frequency mode for battery-based applications, and to be 45kHz to 125kHz in the low switching frequency mode. Upon initialization, the microcontroller must reconfigure the MMSS to the desired settings for VP regulation voltage, switching mode, switching frequency, and VHM clamp. Refer to the PAC application notes and user guide for MMSS controller design and programming.

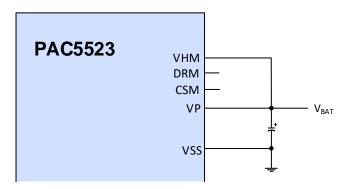

If a stable external 5V to 20V power source is available, it can power the V<sub>P</sub> main supply and all the linear regulators directly without requiring the MMSS controller to operate. In such applications, V<sub>HM</sub> can be connected directly to V<sub>P</sub> and the microcontroller should disable the MMSS upon initialization to reduce power loss.

Figure 10-4 Direct Battery Supply

#### 10.4 Linear Regulators

The MMPM includes four linear regulators. The system supply regulator (VSYS) is a medium voltage regulator that takes the  $V_P$  supply and sources up to 200mA at REGO until  $V_{SYS}$ , externally coupled to REGO, reaches 5V. This allows a properly rated external resistor to be connected from REGO to  $V_{SYS}$  to close the loop and offload power dissipation between  $V_P$  and  $V_{SYS}$ .

Once VSYS is above 4V, the four additional linear regulators for VCC18, VCCIO, VCC33, and VCORE supplies sequentially power up. Figure 10-5 shows typical circuit connections for the linear regulators. The VCC18 regulator generates a dedicated 1.8V supply for FLASH on the MCU. The VCCIO regulator generates a dedicated 3.3V supply for IO. The VCC33 and VCORE regulators generate 3.3V and 1.2V, respectively. When VSYS, VCCIO, VCC33, and VCORE are all above their respective power good thresholds, and the configurable power on reset duration has expired, the microcontroller is initialized.

Figure 10-5 Linear Regulators

#### 10.5 Power-up Sequence

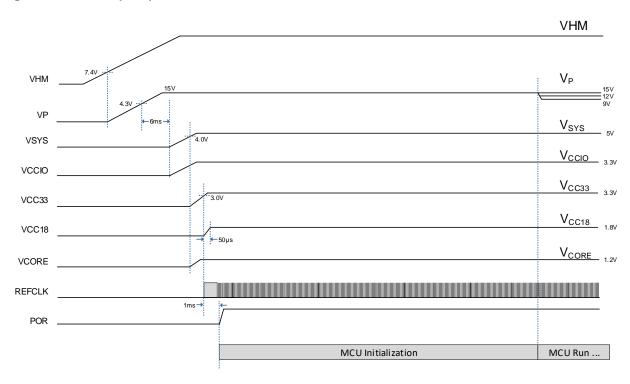

The MMPM follows a typical power up sequence as in the Figure 10-6 below. A typical sequence begins with input power supply being applied, followed by the safe start up and start up durations to bring the switching supply output V<sub>P</sub> to 15V, before the linear regulators are enabled. When all the supplies are ready, the internal clocks become available, and the microcontroller starts executing from the program memory. During initialization, the microcontroller can reconfigure the switching supply to a different V<sub>P</sub> regulation voltage such as 9V or 12V and to an appropriate switching frequency and switching mode. The total loading on the switching supply must be kept below 25% of the maximum output current until after the reconfiguration of the switching supply is complete.

Figure 10-6 Power-Up Sequence

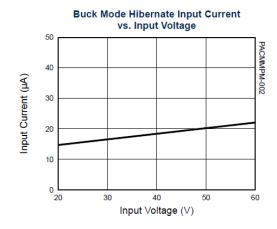

#### 10.6 Hibernate Mode

The IC can go into an ultra-low power hibernate mode via the microcontroller firmware or via the optional push button (PBTN, see *Push Button* description in *Configurable Analog Front End*). In hibernate mode, only a minimal amount (typically 18µA) of current is used by V<sub>P</sub>, and the MMSS controller and all internal regulators are shut down to eliminate power drain from the output supplies. The system exits hibernate mode after a wake-up timer duration (configurable from 125ms to 8s or infinite) has expired or, if push button enabled, after an additional push button event has been detected. When exiting the hibernate mode, the power manager goes through

the start up cycle and the microcontroller is reinitialized. Only the persistent power manager status bits (resets and faults) are retained during hibernation.

#### **10.7 Power and Temperature Monitor**

Whenever any of the  $V_{SYS}$ ,  $V_{CCIO}$ ,  $V_{CC33}$ , or  $V_{CORE}$  power supplies falls below their respective power good threshold voltage, a fault event is detected and the microcontroller is reset. The microcontroller stays in the reset state until  $V_{SYS}$ ,  $V_{CCIO}$ ,  $V_{CC33}$ , and  $V_{CORE}$  supply rails are all good again and the reset time has expired. A microcontroller reset can also be initiated by a maskable temperature fault event that occurs when the IC temperature reaches 170°C. The fault status bits are persistent during reset, and can be read by the microcontroller upon reinitialization to determine the cause of previous reset.

A power monitoring signal  $V_{MON}$  is provided onto the ADC pre-multiplexer for monitoring various internal power supplies.  $V_{MON}$  can be set to be  $V_{CORE}$ , 0.4• $V_{CC33}$ , 0.4• $V_{CCIO}$ , 0.4• $V_{SYS}$ , 0.1• $V_{P}$ , or the internal compensation voltage  $V_{COMP}$  for switching supply power monitoring.

For power and temperature warning, an IC temperature warning event at 140°C are provided as a maskable interrupt to the microcontroller. This warning allows the microcontroller to safely power down the system.

In addition to the temperature warning interrupt and fault reset, a temperature monitor signal  $V_{TEMP} = 1.5 + 5.04e-3 \cdot (T - 25^{\circ}C)$  (V) is provided onto the ADC pre-multiplexer for IC temperature measurement.

#### 10.8 Voltage Reference

The reference block includes a 2.5V high precision reference voltage that provides the 2.5V reference voltage for the ADC, the DACs, and the 4-level programmable threshold voltage  $V_{THREF}$  (0.1V, 0.2V, 0.5V, and 1.25V).

#### 10.9 Electrical Characteristics

#### **Table 10-1 Multi-Mode Switching Supply Controller Electrical Characteristics**

$(V_{HM} = 24V, V_P = 12V \text{ and } T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C unless otherwise specified})$

| SYMBOL                  | PARAMETER                                        | CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------------|--------------------------------------------------|---------------------------------------------------------------------|------|------|------|------|

| Input Supply (V         | ·<br>/нм)                                        |                                                                     |      |      |      |      |

| I <sub>HIB;VHM</sub>    | V <sub>HM</sub> hibernate mode supply current    | V <sub>HM</sub> , hibernate mode                                    |      | 18   | 36   | μΑ   |

| I <sub>SU;VHM</sub>     | V <sub>HM</sub> start-up supply current          | V <sub>HM</sub> < V <sub>UVLOR;VHM</sub>                            |      | 75   | 120  | μΑ   |

| I <sub>OP;VHM</sub>     | V <sub>HM</sub> operating supply current         | DRM floating                                                        |      | 0.3  | 0.5  | mA   |

| $V_{OP;VHM}$            | V <sub>HM</sub> operating voltage range          |                                                                     | 5    |      | 70   | V    |

| $V_{\text{UVLOR;VHM}}$  | V <sub>HM</sub> under-voltage lockout rising     |                                                                     | 6.8  | 7.4  | 8    | V    |

| $V_{\text{UVLOF;VHM}}$  | V <sub>HM</sub> under-voltage lockout falling    |                                                                     | 6    | 6.6  | 7    | V    |

| $V_{\text{CLAMP;VHM}}$  | V <sub>HM</sub> clamp voltage                    | Clamp enabled, sink current = 100 µA                                | 14.5 | 16.9 | 19.5 | V    |

| I <sub>CLAMP;VHM</sub>  | V <sub>HM</sub> clamp sink current limit         | Clamp enabled                                                       |      | 4    |      | mA   |

| Output Supply           | and Feedback (V <sub>P</sub> )                   |                                                                     | I    |      |      |      |

| $V_{REG;VP}$            | V <sub>P</sub> output regulation voltage         | Programmable to 9V, 12V or 15V,<br>Load = 0 to 500mA                | -7   | -1   | 5    | %    |

| k <sub>POK;VP</sub>     | V <sub>P</sub> power OK threshold                | V <sub>P</sub> rising, hysteresis = 10%                             | 82   | 87   | 92   | %    |

| k <sub>OVP;VP</sub>     | V <sub>P</sub> over-voltage protection threshold | V <sub>P</sub> rising, hysteresis = 15%,<br>MMPM Controller enabled |      | 136  |      | %    |

| Switching Cont          | trol                                             |                                                                     |      |      |      |      |

| £                       | Switching frequency programmable range           | High-frequency mode, 8 settings                                     | 181  |      | 500  | kHz  |

| f <sub>SWM;DRM</sub>    |                                                  | Low-frequency mode, 8 settings                                      | 45   |      | 125  | kHz  |

| f <sub>SSU;DRM</sub>    | Safe start-up switching frequency                |                                                                     |      | 9.5  |      | kHz  |

| t <sub>ONMIN;DRM</sub>  | Minimum on-time                                  |                                                                     |      | 440  |      | ns   |

|                         | Minimum off-time                                 | Low duty-cycle and low-frequency mode                               |      | 25   |      | %    |

| t <sub>OFFMIN;DRM</sub> |                                                  | Low duty-cycle and high-<br>frequency mode                          |      | 440  |      | ns   |

|                         |                                                  | High duty-cycle mode                                                |      | 820  |      | ns   |

| Current Sense           | (CSM pin)                                        |                                                                     | •    | •    |      |      |

| $V_{DET;CSM}$           | CSM mode detection threshold                     | Rising, hysteresis = 50mV                                           | 0.40 | 0.55 | 0.69 | V    |

| V <sub>HSLIM;CSM</sub>  | High-side current limit threshold                | 181kHz, duty = 25%, relative to V <sub>P</sub>                      | 0.17 | 0.26 | 0.35 | V    |

| V <sub>LSLIM;CSM</sub>  | Low-side current limit threshold                 | 45kHz, duty = 25%                                                   | 0.7  | 1    | 1.48 | V    |

| t <sub>BLANK;CSM</sub>  | Current sense blanking time                      |                                                                     |      | 200  |      | ns   |

|                         | Low-side abnormal current sense                  | V <sub>P</sub> < 4.3V                                               |      | 0.8  |      | V    |

| $V_{PROT;CSM}$          | protection threshold                             | V <sub>P</sub> > 4.3V                                               |      | 1.9  |      |      |

|                         |                                                  | l .                                                                 | l    | L    |      |      |

| Gate Driver Outp    | Gate Driver Output (DRM pin)     |                                      |                   |      |     |    |  |  |  |

|---------------------|----------------------------------|--------------------------------------|-------------------|------|-----|----|--|--|--|

| V <sub>OH;DRM</sub> | High-level output voltage        | 5% I <sub>OH</sub> , relative to VHM | V <sub>HM</sub> – |      |     | V  |  |  |  |

| V <sub>OL;DRM</sub> | Low-level output voltage         | 5% I <sub>OL</sub>                   |                   |      | 0.6 | ٧  |  |  |  |

| I <sub>OH;DRM</sub> | High-level output source current | $V_{DRM} = V_{HM} - 5V$              |                   | -0.3 |     | Α  |  |  |  |

| I <sub>OL;DRM</sub> | Low-level output sink current    | $V_{DRM} = 5V$                       |                   | 0.5  |     | Α  |  |  |  |

| t <sub>PD;DRM</sub> | Strong pull-down pulse width     | High-side current sense mode         |                   | 240  |     | ns |  |  |  |

#### **Table 10-2 Linear Regulators Electrical Characteristics**

( $V_P = 12V$  and  $T_A = -40$ °C to 125°C unless otherwise specified)

| SYMBOL                            | PARAMETER                                        | CONDITIONS                                                                  | MIN  | TYP | MAX  | UNIT     |

|-----------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------|------|-----|------|----------|

| $V_{OP;VP}$                       | V <sub>P</sub> operating voltage range           |                                                                             | 4.5  |     | 20   | V        |

| V <sub>UVLO</sub> ; <sub>VP</sub> | V <sub>P</sub> under-voltage lockout threshold   | V <sub>P</sub> rising, hysteresis = 0.2V                                    | 4    | 4.3 | 4.6  | V        |

| I <sub>Q</sub> ; <sub>VP</sub>    | V <sub>P</sub> quiescent supply current          | Power manager only, including I <sub>Q</sub> ;V <sub>SYS</sub>              |      | 400 | 750  | μА       |

| I <sub>Q</sub> ; <sub>VSYS</sub>  | V <sub>SYS</sub> quiescent supply current        | V <sub>CCIO</sub> , V <sub>CC33</sub> and V <sub>CORE</sub> regulators only |      | 350 | 600  | μΑ       |

| $V_{\mathtt{SYS}}$                | V <sub>SYS</sub> output voltage                  | Load = 10μA to 200mA                                                        | 4.8  | 5   | 5.18 | V        |

| V <sub>CCIO</sub>                 | V <sub>CCIO</sub> output voltage                 | Load = 10mA                                                                 | 3.15 | 3.3 | 3.4  | <b>V</b> |

| V <sub>CC33</sub>                 | V <sub>CC33</sub> output voltage                 | Load = 10mA                                                                 | 3.15 | 3.3 | 3.4  | <b>V</b> |

| $V_{CORE}$                        | V <sub>CORE</sub> output voltage                 | Load = 10mA                                                                 | 1.14 | 1.2 | 1.26 | V        |

| I <sub>LIM;VSYS</sub>             | V <sub>SYS</sub> regulator current limit         |                                                                             | 220  | 330 |      | mA       |

| I <sub>LIM;VCCIO</sub>            | V <sub>CCIO</sub> regulator current limit        |                                                                             | 45   | 80  |      | mA       |

| I <sub>LIM;VCC33</sub>            | V <sub>CC33</sub> regulator current limit        |                                                                             | 45   | 80  |      | mA       |

| I <sub>LIM;VCORE</sub>            | V <sub>CORE</sub> regulator current limit        |                                                                             | 45   | 80  |      | mA       |

| k <sub>SCFB</sub>                 | Short-circuit current fold-back                  |                                                                             |      | 50  |      | %        |

| $V_{DO;VSYS}$                     | V <sub>SYS</sub> dropout voltage                 | V <sub>P</sub> = 5V, I <sub>SYS</sub> = 100mA                               |      | 350 | 680  | mV       |

| V <sub>UVLO;VSYS</sub>            | V <sub>SYS</sub> under-voltage lockout threshold | V <sub>SYS</sub> rising, hysteresis = 0.2V                                  | 3.5  | 4   | 4.4  | V        |

| k <sub>POK;VCCIO</sub>            | V <sub>CCIO</sub> power OK threshold             | V <sub>CCIO</sub> rising, hysteresis = 10%                                  | 79   | 85  | 91   | %        |

| k <sub>POK;VCC33</sub>            | V <sub>CC33</sub> power OK threshold             | V <sub>CC33</sub> rising, hysteresis = 10%                                  | 79   | 85  | 91   | %        |

| k <sub>POK;VCORE</sub>            | V <sub>CORE</sub> power OK threshold             | V <sub>CORE</sub> falling, hysteresis = 10%                                 | 79   | 85  | 91   | %        |

|                                   |                                                  |                                                                             |      |     |      |          |

#### **Table 10-3. Power System Electrical Characteristics**

$(T_A = -40$ °C to 125°C unless otherwise specified)

| SYMBOL                  | PARAMETER                                                | CONDITIONS                                               | MIN   | TYP  | MAX   | UNIT |

|-------------------------|----------------------------------------------------------|----------------------------------------------------------|-------|------|-------|------|

| V <sub>REF</sub>        | Defenses Maltana                                         | T <sub>A</sub> = 25°C                                    | 2.487 | 2.5  | 2.513 | V    |

|                         | Reference Voltage                                        | T <sub>A</sub> = -40°C to 125°C                          | 2.463 | 2.5  | 2.537 | V    |

| <b>k</b> <sub>MON</sub> | Power monitoring voltage (V <sub>MON</sub> ) coefficient | V <sub>CORE</sub>                                        |       | 1    |       | V/V  |

|                         |                                                          | V <sub>SYS</sub> , V <sub>CCIO</sub> , V <sub>CC33</sub> |       | 0.4  |       |      |

|                         |                                                          | V <sub>P</sub> , V <sub>REGO</sub>                       |       | 0.1  |       |      |

| $V_{TEMP}$              | Temperature monitor voltage at 25°C                      | T <sub>A</sub> = 25°C, at ADC                            | 1.475 | 1.5  | 1.54  | V    |

| k <sub>TEMP</sub>       | Temperature monitor coefficient                          | At ADC                                                   |       | 5.04 |       | mV/K |

| T <sub>WARN</sub>       | Over-temperature warning threshold                       | Hysteresis = 10°C                                        |       | 140  |       | °C   |

| T <sub>FAULT</sub>      | Over-temperature fault threshold                         | Hysteresis = 10°C                                        |       | 170  |       | °C   |

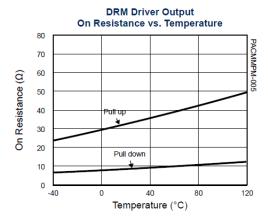

#### 10.10 Typical Performance Characteristics

$(V_P = 12V \text{ and } T_A = 25^{\circ}C \text{ unless otherwise specified})$

### 11 CONFIGURABLE ANALOG FRONT END (CAFE)

#### 11.1 Block Diagram

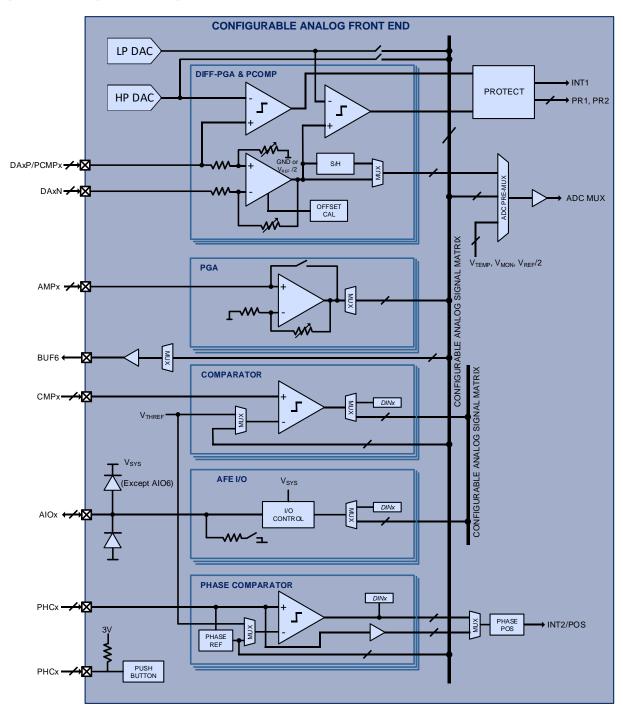

**Figure 11-1 Configurable Analog Front End**

#### 11.2 Functional Description

The device includes a Configurable Analog Front End (CAFE, Figure 11-1) accessible through 10 analog and I/O pins. These pins can be configured to form flexible interconnected circuitry made up of 3 differential programmable gain amplifiers, 4 single-ended programmable gain amplifiers, 4 general purpose comparators, 3 phase comparators, 10 protection comparators, and one buffer output. These pins can also be programmed as analog feed-through pins, or as analog front end I/O pins that can function as digital inputs or digital open-drain outputs. The PAC proprietary configurable analog signal matrix (CASM) and configurable digital signal matrix (CDSM) allow real time asynchronous analog and digital signals to be routed in flexible circuit connections for different applications. A push button function is provided for optional push button on, hibernate, and off power management function.

#### 11.3 Differential Programmable Gain Amplifier (DA)

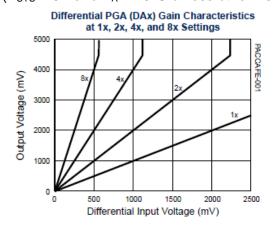

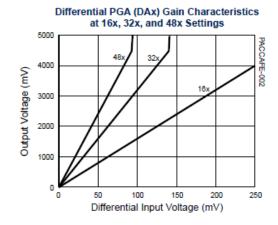

The DAxP and DAxN pin pair are positive and negative inputs, respectively, to a differential programmable gain amplifier. The differential gain can be programmable to be 1x, 2x, 4x, 8x, 16x, 32x, and 48x for zero ohm signal source impedance. The differential programmable gain amplifier has -0.3V to 2.5V input common mode range, and its output can be configured for routing directly to the ADC pre-multiplexer, or through a sample-and-hold circuit synchronized with the ADC auto-sampling mechanism. Each differential amplifier is accompanied by offset calibration circuitry, and two protection comparators for protection event monitoring. The programmable gain differential amplifier is optimized for use with signal source impedance lower than  $500\Omega$  and with matched source impedance on both positive and negative inputs for minimal offset. The effective gain is scaled by  $13.5k / (13.5k + R_{SOURCE})$ , where  $R_{SOURCE}$  is the matched source impedance of each input.

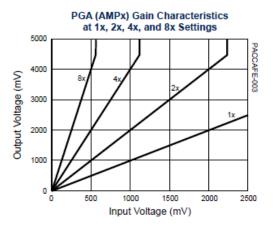

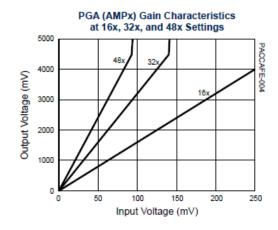

#### 11.4 Single-Ended Programmable Gain Amplifier (AMP)

Each AMPx input goes to a single-ended programmable gain amplifier with signal relative to  $V_{SSA}$ . The amplifier gain can be programmed to be 1x, 2x, 4x, 8x, 16x, 32x, and 48x, or as analog feed-through. The programmable gain amplifier output is routed via a multiplexer to the configurable analog signal matrix CASM.

#### 11.5 General Purpose Comparator (CMP)

The general purpose comparator takes the CMPx input and compares it to either the programmable threshold voltage (V<sub>THREF</sub>) or a signal from the configurable analog signal matrix CASM. The comparator has 0V to V<sub>SYS</sub> input common mode range, and its polarity-selectable output is routed via a multiplexer to either a data input bit or the configurable digital signal matrix CDSM. Each general purpose comparator has two mask bits to prevent or allow rising or falling edge of its output to trigger second microcontroller interrupt INT2, where INT2 can be configured to active protection event PR1.

#### 11.6 Phase Comparator (PHC)

The phase comparator takes the PHCx input and compares it to either the programmable threshold voltage (VTHREF) or a signal from the configurable analog signal matrix CASM. The comparison signal can be set to a phase reference signal generated by averaging the PHCx input voltages. In a three-phase motor control application, the phase reference signal acts as a virtual center tap for BEMF detection. The PHCx inputs are optionally fed through to the CASM. The PHC inputs can be compared to the virtual center-tap, or phase to phase for the most efficient BEMF zero-cross detection. The phase comparators have configurable asymmetric hysteresis.

The phase comparator has 0V to  $V_{SYS}$  input common mode range, and its polarity-selectable output is routed to a data input bit and to the phase/position multiplexer synchronized with the auto-sampling sequencers.

#### 11.7 Protection Comparator (PCMP)

Two protection comparators are provided in association with each differential programmable gain amplifier, with outputs available to trigger protection events and accessible as read-back output bits. The high-speed protection (HP) comparator compares the PCMPx pin to the 8-bit HP DAC output voltage, with full scale voltage of 2.5V. The limit protection (LP) comparator compares the differential programmable gain amplifier output to the 10-bit LP DAC output voltage, with full scale voltage of 2.5V.

Each protection comparator has a mask bit to prevent or allow it to trigger the main microcontroller interrupt INT1. Each protection comparator also has one mask bit to prevent or allow it to activate protection event PR1, and another mask bit to prevent or allow it to activate protection event PR2. These two protection events can be used directly by protection circuitry in the Application Specific Power Drivers (ASPD) to protect devices being driven.

#### 11.8 Analog Output Buffer (BUF)

A subset of the signals from the configurable analog signal matrix CASM can be multiplexed to the BUF6 pin for external use. The buffer offset voltage can be minimized with the built-in swap function.

#### 11.9 Analog Front End I/O (AIO)

Up to 10 AlOx pins are available in the device, depending on the product<sup>5</sup>. In the analog front end I/O mode, the pin can be configured to be a digital input or digital open-drain output. The AlOx input or output signal can be set to a data input or output register bit, or multiplexed to one of the signals in the configurable digital signal matrix CDSM. The signal can be set to active high (default) or active low, with V<sub>SYS</sub> supply rail. Where AlO<sub>6.7.8.9</sub> supports microcontroller

<sup>&</sup>lt;sup>5</sup> See the pin configuration and description for specific information on which pins are available in this product.

interrupt for external signals. Each has two mask bits to prevent or allow rising or falling edge of its corresponding digital input to trigger second microcontroller interrupt INT2.

#### 11.10 Push Button (PBTN)

The push button PBTN, when enabled, can be used by the MCU to detect a user active-low push button event and to put the system into an ultra-low-power hibernate mode. Once the system is in hibernate mode, PBTN can be used to wake up the system.

In addition, PBTN can also be used as a hardware reset for the microcontroller when it is held low for longer than 8s during normal operation. The PBTN input is active low and has a  $55k\Omega$  pull-up resistor to 3V.

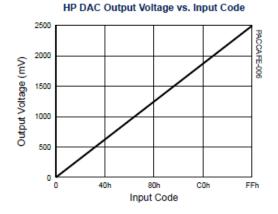

#### 11.11 HP DAC and LP DAC

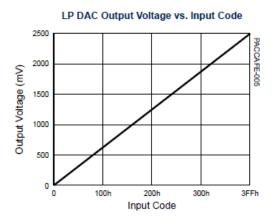

The 8-bit HP DAC can be used as the comparison voltage for the high-speed protection (HP) comparators, or routed for general purpose use via the AB2 signal in the CASM. The HP DAC output full scale voltage is 2.5V.

The 10-bit LP DAC can be used as the comparison voltage for the limit protection (LP) comparators, or routed for general purpose use via the AB3 signal in the CASM. The LP DAC output full scale voltage is 2.5V.

#### 11.12 ADC Pre-Multiplexer

The ADC pre-multiplexer is a 16-to-1 multiplexer that selects between the 3 differential programmable gain amplifier outputs, AB1 through AB9, temperature monitor signal ( $V_{TEMP}$ ), power monitor signal ( $V_{MON}$ ), and offset calibration reference ( $V_{REF}$  / 2). The ADC pre-multiplexer can be directly controlled or automatically scanned by the auto-sampling sequencer.

When the ADC pre-multiplexer is automatically scanned, the unbuffered or sensitive signals should be masked by setting appropriate register bits.

#### 11.13 Configurable Analog Signal Matrix (CASM)

The CASM has 12 general purpose analog signals labeled AB1 through AB12 that can be used for:

- Routing the single-ended programmable gain amplifier or analog feed-through output to AB1 through AB9

- Routing an analog signal via AB1, AB2, or AB3 to the negative input of a general purpose comparator or phase comparator

- Routing the 8-bit HP DAC output to AB2

- Routing the 10-bit LP DAC output to AB3

- Routing analog signals via AB1 through AB12 to the ADC pre-multiplexer

- Routing phase comparator feed-through signals to AB7, AB8, and AB9, and averaged voltage to AB1

### 11.14 Configurable Digital Signal Matrix (CDSM)

The CDSM has 7 general purpose bi-directional digital signals labeled DB1 through DB7 that can be used for:

- Routing the AlOx input to or output signals from DB1 through DB7

- Routing the general-purpose comparator output signals to DB1 through DB7

#### 11.15 Electrical Characteristics

#### Table 11-1 Differential Programmable Gain Amplifier (DA) Electrical Characteristics

(V<sub>SYS</sub> = 5V, V<sub>CCIO</sub> = 3.3V and T<sub>A</sub> = -40°C to 125°C unless otherwise specified.)

| SYMBOL                | PARAMETER                    | CONDITIONS                                          | MIN                                  | TYP | MAX                       | UNIT |

|-----------------------|------------------------------|-----------------------------------------------------|--------------------------------------|-----|---------------------------|------|

| I <sub>CC;DA</sub>    | Operating supply current     | Each enabled amplifier                              |                                      | 150 | 300                       | μΑ   |

| $V_{\text{ICMR;DA}}$  | Input common mode range      |                                                     | -0.3                                 |     | 2.5                       | V    |

| $V_{OLR;DA}$          | Output linear range          |                                                     | 0.1                                  |     | V <sub>SYS</sub><br>- 0.1 | V    |

| $V_{SHR;DA}$          | Sample and hold range        |                                                     | 0.1                                  |     | 3.5                       | V    |

| $V_{\text{OS;DA}}$    | Input offset voltage         | Gain = 48x, $V_{DAxP}=V_{DAxN}=0V$ ,<br>$T_A=25$ °C | -8                                   |     | 8                         | mV   |

|                       |                              | Gain = 1x                                           |                                      | 1   |                           |      |

|                       |                              | Gain = 2x                                           |                                      | 2   |                           |      |

|                       |                              | Gain = 4x                                           |                                      | 4   |                           |      |

| ٨                     | Differential amplifier gain  | Gain = $8x$ , $V_{DAxP} = V_{DAxN} = 0V$ , $T_A =$  |                                      | 8   |                           |      |

| $A_{VZI;DA}$          | (zero ohm source impedance)  | 25°C                                                | -2                                   |     | 2                         | %    |

|                       |                              | Gain = 16x                                          |                                      | 16  |                           |      |

|                       |                              | Gain = 32x                                          |                                      | 32  |                           |      |

|                       |                              | Gain = 48x                                          |                                      | 48  |                           |      |

| k <sub>CMRR;DA</sub>  | Common mode rejection ratio  | Gain = 8x, $V_{DAxP}=V_{DAxN}=0V$ , $T_A=25$ °C     | $D_{DAXP} = V_{DAXN} = 0V, T_A = 55$ |     |                           | dB   |

| R <sub>INDIF;DA</sub> | Differential input impedance | 27                                                  |                                      |     | kΩ                        |      |

|                       | Slew rate <sup>6</sup>       | Gain = 8x 7 10                                      |                                      |     | V/μs                      |      |

| t <sub>ST;DA</sub>    | Settling time <sup>6</sup>   | To 1% of final value                                |                                      | 200 | 400                       | ns   |

<sup>&</sup>lt;sup>6</sup> Guaranteed by design

#### Table 11-2 Single-Ended Programmable Gain Amplifier (AMP) Electrical Characteristics

( $V_{SYS} = 5V$ ,  $V_{CCIO} = 3.3V$  and  $T_A = -40$ °C to 125°C unless otherwise specified.)

| SYMBOL               | PARAMETER                  | CONDITIONS                                                 | MIN | TYP | MAX                    | UNIT |

|----------------------|----------------------------|------------------------------------------------------------|-----|-----|------------------------|------|

| I <sub>CC;AMP</sub>  | Operating supply current   | Each enabled amplifier                                     |     | 80  | 140                    | μΑ   |

| V <sub>ICMR;DA</sub> | Input common mode range    |                                                            | 0   |     | V <sub>SYS</sub>       | V    |

| $V_{OLR;DA}$         | Output linear range        |                                                            | 0.1 |     | V <sub>SYS</sub> _ 0.1 | V    |

| V <sub>OS;AMP</sub>  | Input offset voltage       | Gain = 1x, T <sub>A</sub> =25°C, V <sub>AMPX</sub> =2.5V   | -10 |     | 10                     | mV   |

|                      |                            | Gain = 1x                                                  |     | 1   |                        |      |

|                      |                            | Gain = 2x                                                  |     | 2   |                        |      |