# PERICOM®

## **PI2EQX5964**

### 5.0Gbps 4-Lane PCIe<sup>®</sup> 2.0 ReDriver<sup>™</sup> with Equalization, Emphasis, & I<sup>2</sup>C Control

### Features

- → Up to 5.0Gbps PCI Express<sup>®</sup> 2.0 Serial ReDriver

- → Supporting 8 differential channels or 4 lanes of PCIe Interface

- $\rightarrow$  I<sup>2</sup>C configuration controls (3.3V tolerant)

- → Adjustable receiver equalization and transmitter deemphasis and output levels

- → Variable input an output termination

- → 1:2 channel broadcast

- → Channel loop-back/Mux and Demux Mode

- → Electrical Idle fully supported

- → Receiver detect and individual output control

- $\rightarrow$  Fine adjustment of electrical idle threshold via I<sup>2</sup>C

- → Single supply voltage,  $1.2V \pm 0.05V$

- ➔ Power down modes

- → Industrial Temp support, -40°C ~ +85°C

- → Packaging: 56-contact TQFN, Pb-free & Green

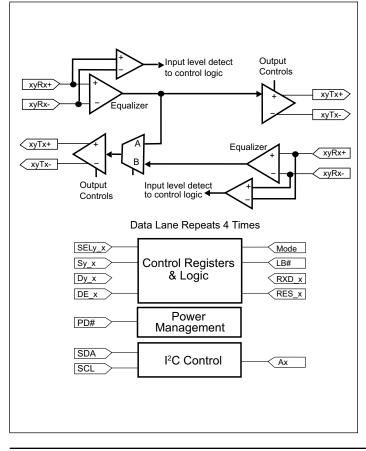

### **Block Diagram**

### Description

Pericom Semiconductor's PI2EQX5964 is a low power, PCIe® compliant signal redriver. The device provides programmable equalization, amplification, and de-emphasis by using 8 select bits, to optimize performance over a variety of physical mediums by reducing Inter-symbol interference.

PI2EQX5964 supports eight 100-Ohm Differential CML data I/O's between the Protocol ASIC to a switch fabric, across a backplane, or extends the signals across other distant data pathways on the user's platform.

The integrated equalization circuitry provides flexibility with signal integrity of the PCI Express signal before the ReDriver™, whereas the integrated de-emphasis circuitry provides flexibility with signal integrity of the signal after the redriver.

In addition to providing signal re-conditioning, Pericom's PI2EQX5964 also provides power management Stand-by mode operated by a Bus Enable pin.

1

PS-0.5

### Figure1

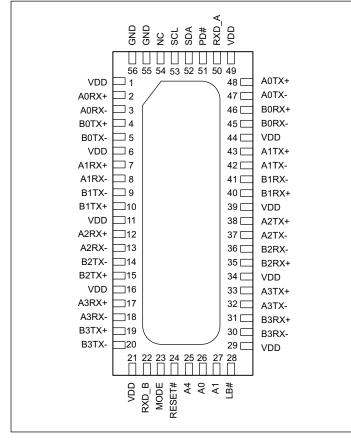

### **Pin Configuration**

### **Pin Description**

| Pin #           | Pin Name   | Туре | Description                                                                                                                                                                       |

|-----------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Signals    |            |      |                                                                                                                                                                                   |

| 2               | A0RX+,     | Ι    | CML inputs for Channel A0, with internal 50-Ohm pull down during normal                                                                                                           |

| 3               | A0RX-      | I    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 48              | A0TX+,     | 0    | CML outputs for Channel A0, with internal 50-Ohm pull up during normal                                                                                                            |

| 47              | A0TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 7               | A1RX+,     | Ι    | CML inputs for Channel A1, with internal 50-Ohm pull down during normal                                                                                                           |

| 8               | A1RX-      | Ι    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 43              | A1TX+,     | 0    | CML outputs for Channel A1, with internal 50-Ohm pull up during normal                                                                                                            |

| 42              | A1TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 12              | A2RX+,     | Ι    | CML inputs for Channel A2, with internal 50-Ohm pull down during normal                                                                                                           |

| 13              | A2RX-      | Ι    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 38              | A2TX+,     | 0    | CML outputs for Channel A2, with internal 50-Ohm pull up during normal                                                                                                            |

| 37              | A2TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 17              | A3RX+,     | Ι    | CML inputs for Channel A3 with internal 50-Ohm pull down during normal                                                                                                            |

| 18              | A3RX-      | Ι    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 33              | A3TX+,     | 0    | CML outputs for Channel A3, with internal 50-Ohm pull up during normal                                                                                                            |

| 32              | A3TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 46              | BORX+,     | Ι    | CML inputs for Channel B0, with internal 50-Ohm pull down during normal                                                                                                           |

| 45              | BORX-      | Ι    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 4               | В0ТХ+,     | 0    | CML outputs for Channel B0, with internal 50-Ohm pull up during normal                                                                                                            |

| 5               | B0TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 41              | B1RX-,     | Ι    | CML inputs for Channel B1, with internal 50-Ohm pull down during normal                                                                                                           |

| 40              | B1RX+      | Ι    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 9               | B1TX-,     | 0    | CML outputs for Channel B1, with internal 50-Ohm pull up during normal                                                                                                            |

| 10              | B1TX+      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 36              | B2RX-,     | Ι    | CML inputs for Channel B2, with internal 50-Ohm pull down during normal                                                                                                           |

| 35              | B2RX+      | I    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 14              | В2ТХ-,     | 0    | CML outputs for Channel B2, with internal 50-Ohm pull up during normal                                                                                                            |

| 15              | B2TX+      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| 31              | B3RX+,     | Ι    | CML inputs for Channel B3, with internal 50-Ohm pull down during normal                                                                                                           |

| 30              | B3RX-      | I    | operation, and >200K-Ohm otherwise.                                                                                                                                               |

| 19              | ВЗТХ+,     | 0    | CML outputs for Channel B3, with internal 50-Ohm pull up during normal                                                                                                            |

| 20              | B3TX-      | 0    | operation and 2K-Ohm pull up otherwise.                                                                                                                                           |

| Control Signals | 8          |      |                                                                                                                                                                                   |

| 26, 27, 25      | A0, A1, A4 | Ι    | I <sup>2</sup> C programmable address bit A0, A1 and A4.                                                                                                                          |

| 28              | LB#        | Ι    | Loopback control input. Input with internal 100K-Ohm pull-up resistor. LB#<br>= High or open for normal operation. LB# = Low for loopback connection of<br>A_RX to A_TX and B_TX. |

(Continued on Next Page)

| Pin #                                   | Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23                                      | Mode     | Ι    | Enables I <sup>2</sup> C control when LOW. Has internal 100K-Ohm pull-up resistor. A LVCMOS high level selects input pins control, and disables I <sup>2</sup> C operation. Note, during startup, input status of the control pin (LB#, RES_A/B#, RXD_A/B, RESET#) will be latched to set the initial register state. |

| 51                                      | PD#      | Ι    | Input with 100K-Ohm pull-up resistor, PD# = High or open is normal operation, PD# = Low disables the IC and sets the IC into Power Down mode. Both inputs and outputs go to Hi-Z.                                                                                                                                     |

| 54                                      | NC       |      | No Connect                                                                                                                                                                                                                                                                                                            |

| 24                                      | RESET#   | Ι    | RESET# is an active low channel reset input for Channel A0, B0, A1, B1, A2, B2, A3 and B3 with internal 100K-Ohm pull-up resistor. When low, receiver detection cycle is reset, and normal detection cycle is carry on after the pin goes high.                                                                       |

| 50                                      | RXD_A    | I    | Receiver detect enable input for Channel A0, A1, A2 and A3 with internal 100K-<br>Ohm pull-up resistor.                                                                                                                                                                                                               |

| 22                                      | RXD_B    | Ι    | Receiver detect enable input for Channel B0, B1, B2 and B3 with internal 100K-<br>Ohm pull-up resistor.                                                                                                                                                                                                               |

| 53                                      | SCL      | I/O  | I <sup>2</sup> C SCL clock input.                                                                                                                                                                                                                                                                                     |

| 52                                      | SDA      | I/O  | I <sup>2</sup> C SDA data input.                                                                                                                                                                                                                                                                                      |

| 55, 56, Center Pad                      | GND      | PWR  | Supply Ground                                                                                                                                                                                                                                                                                                         |

| 1, 6, 11, 16, 21, 29,<br>34, 39, 44, 49 | VDD      | PWR  | 1.2V Supply Voltage                                                                                                                                                                                                                                                                                                   |

### **Description of Operation:**

### **Configuration Modes**

Device configuration can be performed in two ways depending on the state of the MODE input. MODE determines whether IC configuration status is from the input pins or via  $I^2C$  control. When MODE is set high, the configuration input pins set the configuration operating state as stored in configuration registers. While MODE is set high, changes to these control registers are disabled and the initial condition is protected from any changes to insuring a known operating state. When the MODE pin is low, reprogramming of these control registers via  $I^2C$  is allowed. Note that the MODE pin is not latched, and is always active to enable or disable  $I^2C$  access.

During initial power-on, the value at the configuration input pins: LB#, RESET#,RXD\_A and RXD\_B, will be latched to the configuration registers as initial startup states.

### **Equalizer Configuration**

The PI2EQX5964 input equalizer compensates for signal attenuation and Inter-Symbol Interference (ISI) resulting from long signal traces or cables, vias, signal crosstalk and other factors, by boosting the gain of high-frequency signal components. Because either too little, or too much, signal compensation may be non-optimal eight levels are provided to adjust for any application. Equalizer configuration can be programmed via  $I^2C$  when the mode pin is low. Each group of four channels, A and B, has separate equalization control, and all four channels within the group are assigned the same configuration state. The Equalizer Selection table below describes the register state and associated operation of the equalizer.

| SEL2_[A:B] | SEL1_[A:B] | SEL0_[A:B] | @1.25GHz | @2.5GHz |

|------------|------------|------------|----------|---------|

| 0          | 0          | 0          | 0.5dB    | 1.2dB   |

| 0          | 0          | 1          | 0.6dB    | 1.5dB   |

| 0          | 1          | 0          | 1.0dB    | 2.6dB   |

| 0          | 1          | 1          | 1.9dB    | 4.3dB   |

| 1          | 0          | 0          | 2.8dB    | 5.8dB   |

| 1          | 0          | 1          | 3.6dB    | 7.1dB   |

| 1          | 1          | 0          | 5.0dB    | 9.0dB   |

| 1          | 1          | 1          | 7.7dB    | 12.3dB  |

### **Equalizer Selection**

### **Output Configuration**

The PI2EQX5964 provides flexible output strength and emphasis controls to provide the optimum signal to pre-compensate for losses across long trace or noisy environments so that the receiver gets a clean with good eye opening. Control of output configuration is grouped for the A and B channels, so that each channel within the group has the same setting.

Output configuration can be set via I<sup>2</sup>C when the mode pin is LOW. The Output Swing Control table shows available configuration settings for output level control, as specified by the SELx\_y registers.

### **Output Swing Control**

| S1_[A:B] | S0_[A:B] | Swing (Diff. VPP) |  |

|----------|----------|-------------------|--|

| 0        | 0        | 1.1V              |  |

| 0        | 1        | 0.5V              |  |

| 1        | 0        | 0.8V              |  |

| 1        | 1        | 1.0V              |  |

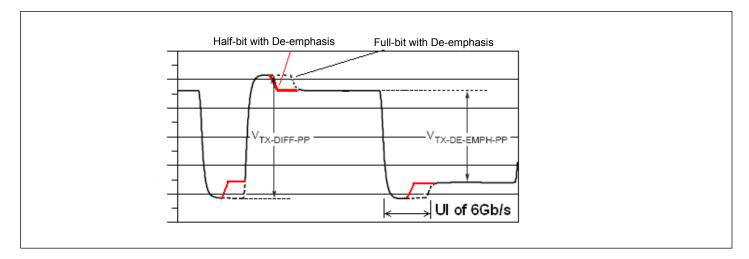

### **Output De-Emphasis Adjustment**

De-emphasis settings are determined by the state of the DEx\_y input pins and configuration registers, as shown in the Output De-emphasis table below. Half-bit-de-emphasis is selected as the default power-on mode, but can be changed to full-bit-de-emphasis via reprogramming the Loopback and De-emphasis Control register using the I<sup>2</sup>C interface. Output de-emphasis settings are independent of the data rate.

| D2_[A:B] | D1_[A:B] | D0_[A:B] | De-emphasis |

|----------|----------|----------|-------------|

| 0        | 0        | 0        | 0dB         |

| 0        | 0        | 1        | -2.5dB      |

| 0        | 1        | 0        | -3.5dB      |

| 0        | 1        | 1        | -4.5dB      |

| 1        | 0        | 0        | -5.5dB      |

| 1        | 0        | 1        | -6.5dB      |

| 1        | 1        | 0        | -7.5dB      |

| 1        | 1        | 1        | -8.5dB      |

### **Input Level Detect**

An input level detect and output squelch function is provided on each channel to eliminate re-transmission of input noise. A continuous signal level below the Vth- threshold causes the output driver to go to a high-impredance state, so that both the positive and negative output signal are pulled to  $V_{DD}$  by the internal pull-up resistors. This feature supports LOS PCI Express Electrical Idle state.

### **Receiver Detect**

Automatic Receiver Detection is a feature that can set the number of active channels. By sensing the presence of a load device on the output, the channel can be automatically enabled for operation. This allows the PI2EQX5964 to configure itself properly depending on the devices it is communicating with, whether it is a 4-lane, 3-lane, 2-lane or just 1-lane device or adapter card.

Receiver Detect is enabled by the RXD\_A, or RXD\_B pins, or alternatively via I<sup>2</sup>C programming. When RXD\_A or RXD\_B is set to low, the Receiver Detect operation for that group of channels is disabled, and those channels go directly to 50-Ohm input termination to ground and 50-Ohm output termination to VDD (for a valid differential channel input level) or to 2K-Ohm (if the signal level is less than the threshold level).

The RESET# input is used to reset the receiver detect state machine to its initial state. The start of the receiver detect cycle starts when RESET# transitions from low to high.

When a Receiver Detect cycle begins the differential channel pins are enabled with a 2K-Ohm pull-up to  $V_{DD}$ . A 50-Ohm Receiver termination will change the pin level. This pin level is evaluated after a fixed time-out, and the channel is then set into the proper operating state. The register bits RX50\_Ax and RX50\_Bx represent the receiver detect result for their specific channels.

The I/O operation table summarizes the relationships and operation of receiver detect and other signals involved with I/O control.

| Cont | rol Input | \$     | Detection<br>States |       | on<br>Data Channel I/O |                    |                                                                                                              |

|------|-----------|--------|---------------------|-------|------------------------|--------------------|--------------------------------------------------------------------------------------------------------------|

| PD#  | RXD_x     | RESET# | RX50                | SIG_x | Input Termination      | Output Termination | Mode                                                                                                         |

| 0    | X         | X      | X                   | Х     | Hi-Z                   | Hi-Z               | Full IC power down, all channels disabled                                                                    |

| 1    | 0         | 0      | X                   | X     | Hi-Z                   | 2K-Ohm pull-up     | Channel disabled, output pulls to V <sub>DD</sub> . Receiver detect reset                                    |

| 1    | 0         | 1      | X                   | 0     | 50-Ohm pull-down       | 2K-Ohm pull-up     | Channel enabled, no input signal, output pulls to $\mathrm{V}_{\mathrm{DD}}.$ Receiver detect disabled       |

| 1    | 0         | 1      | X                   | 1     | 50-Ohm pull-down       | 50-Ohm pull-up     | Channel enabled, valid input signal<br>detected, output driving. Receiver<br>detect disabled.                |

| 1    | 1         | 0      | X                   | х     | Hi-Z                   | 2K-Ohm pull-up     | Channel disabled. Receiver detect reset.                                                                     |

| 1    | 1         | 1      | 0                   | X     | Hi-Z                   | 2K-Ohm pull-up     | Channel disabled, output pulls to $V_{\rm DD}$ . Receiver detect enabled, no receiver detected.              |

| 1    | 1         | 1      | 1                   | 0     | 50-Ohm pull-down       | 2K-Ohm pull-up     | Channel inactive, output pulls to $V_{DD}$ . Receiver detect enabled, receiver detected. No input signal     |

| 1    | 1         | 1      | 1                   | 1     | 50-Ohm pull-down       | 50-Ohm pull-up     | Channel active, valid input signal de-<br>tected, output driving. Receiver detect<br>enabled, load detected. |

### I/O Operation Control

### **Loopback Operation**

| Loopback Modes |                                                                                       | CONDITIONS                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | NORMAL MODE<br>A0Rx to A0Tx, B0Rx to B0Tx                                             | LB_A0B0# = 1<br>INDIS_A0 = 0<br>OUTDIS_A0 = 0<br>INDIS_B0 = 0<br>OUTDIS_B0 = 0                                                                                   |

|                | BROADCAST MODE<br>A0Rx to A0Tx and B0Tx                                               | LB_A0B0# = 0<br>INDIS_A0 =0<br>INDIS_B0 = 1<br>OUTDIS_B0 = 0                                                                                                     |

|                | LOOPBACK MODE<br>A0Rx to B0Tx                                                         | LB_A0B0# = 0<br>INDIS_A0 = 0<br>OUT_DIS_A0 = 1<br>INDIS_B0 = 1<br>OUTDIS_B0 = 0                                                                                  |

|                | DEMUX MODE<br>Solid Line<br>A0Rx to A0Tx<br>DEMUX MODE<br>Dashed Line<br>A0Rx to B0Tx | LB_A0B0# = 1<br>INDIS_A0 = 0<br>OUTDIS_A0 = 0<br>INDIS_B0 = 1<br>OUTDIS_B0 = 0<br>LB_A0B0# = 0<br>INDIS_A0 = 0<br>OUTDIS_A0 = 0<br>INDIS_B0 = 1<br>OUTDIS_B0 = 0 |

|                | MUX MODE<br>Solid Line<br>B0Rx to B0Tx<br>MUX MODE<br>Dasked Line<br>A0Rx to B0Tx     | LB_A0B0# = 1<br>INDIS_A0 = 0<br>OUTDIS_A0 = 1<br>INDIS_B0 = 0<br>OUTDIS_B0 = 0<br>LB_A0B0# = 0<br>INDIS_A0 = 0<br>OUTDIS_A0 = 1<br>INDIS_B0 = 0<br>OUTDIS_B0 = 0 |

Each lane of provides a loopback mode for test purposes which is controlled by a strapping pin and  $I^2C$  register bit. The LB# pin controls all lanes together. When this pin is high normal data mode is enabled. When LB# is low the loopfeature mode is enabled. The adjacent figure diagrams this operation. Loopback is not intended to be dynamically switched, and the normal system application is to initialize to one configuration or the other.

The Loopback mode can also support mux/ demux operation. Using I<sup>2</sup>C configuration, unused inputs and outputs can be disabled to minimize power and noise.

PS-0.5

## I<sup>2</sup>C Operation

The PI2EQX5964 I<sup>2</sup>C controller operates as a slave device, supporting standard rate operation of 100Kbps, with 7-bit addressing mode. The data byte format is 8 bit bytes. The bytes must be accessed in sequential order from the lowest to the highest byte with the ability to stop after any complete byte has been transferred. Address bits A4, A1 and A0 are programmable to support multiple chips environment. The data is loaded until a Stop sequence is issued.

| Byte | Mnemonic | Function                                                                                                                         |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| 0    | SIG      | Signal Detect, indicates valid input signal level                                                                                |

| 1    | RX50     | Receiver Detect Output, indicates whether a receiver load was detected                                                           |

| 2    | LBEC     | Loopback and Emphasis Control, provides for control of the loopback function and emphasis mode (pre-<br>emphasis or de-emphasis) |

| 3    | INDIS    | Channel Input Disable, controls whether a channels input buffer is enabled or disabled                                           |

| 4    | OUTDIS   | Channel Output Disable: Controls whether a channels output buffer is enabled or disabled                                         |

| 5    | RESET    | Channel Reset                                                                                                                    |

| 6    | PWR      | Power Down Control, enables power down for each channel individually                                                             |

| 7    | RXDE     | Receiver Detect Enable, controls the receiver detect operation                                                                   |

| 8    | AEOC     | A-Channels Equalizer and Output Control                                                                                          |

| 9    | BEOC     | B-Channels Equalizer and Output Control                                                                                          |

| 10   | RSVD     | Reserved                                                                                                                         |

| 11   | VTH      | Idle detect threshold control                                                                                                    |

### **Configuration Register Summary**

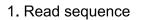

### **Transferring Data**

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I<sup>2</sup>C Data Transfer diagram). The PI2EQX5964 will never hold the clock line SCL LOW to force the master into a wait state.

Note: Byte-write and byte-read transfers have a fixed offset of 0x00, because of the very small number of configuration bytes. An offset byte presented by a host to the PI2EQX5964 is not used.

### Addressing

Up to eight PI2EQX5964 devices can be connected to a single  $I^2C$  bus. The PI2EQX5964 supports 7-bit addressing, with the LSB indicating either a read or write operation. The address for a specific device is determined by the A0, A1 and A4 input pins.

| Address Assignment |    |         |    |    |              |    |          |

|--------------------|----|---------|----|----|--------------|----|----------|

| A6                 | A5 | A4      | A3 | A2 | A1           | A0 | R/W      |

| 1                  | 1  | Program | 0  | 0  | Programmable |    | 1=R, 0=W |

### Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, the PI2EQX5964 will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I2C Data Transfer diagram. The PI2EQX5964 will generate an acknowledge after each byte has been received.

### Data Transfer

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, the PI2EQX5964 will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit. For a write cycle, the first data byte following the address byte is a dummy or fill byte that is not used by the PI2EQX5964. This byte is provided to provided compatibility with systems implementing 10-bit addressing. Data is transferred with the most significant bit (MSB) first. After each block write, address pointer will reset to byte 0.

### **Register Description**

#### BYTE 0 - Signal Detect (SIG)

SIG\_xy=0=low input signal, SIG\_xy=1=valid input signal

| Bit               | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name              | SIG_A0 | SIG_B0 | SIG_A1 | SIG_B1 | SIG_A2 | SIG_B2 | SIG_A3 | SIG_B3 |

| Туре              | R      | R      | R      | R      | R      | R      | R      | R      |

| Power-on<br>State | X      | Х      | X      | X      | Х      | X      | X      | Х      |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Signal Detect register provides information on the instantaneous status of the channel input from the Input Level Threshold Detect circuit. If the input level falls below the Vth- level the relevant SIG\_xy bit will be 0, indicating a low-level noise or electrical idle input, resulting in the outputs going to the high-impedance off state or squelch mode. If the input level is above Vth-, then SIG\_xy is 1, indicating a valid input signal, and active signal recovery operation.

BYTE 1 - Receiver Detect Output Register (RX50)

| Bit               | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Name              | RX50_A0 | RX50_B0 | RX50_A1 | RX50_B1 | RX50_A2 | RX50_B2 | RX50_A3 | RX50_B3 |

| Туре              | R       | R       | R       | R       | R       | R       | R       | R       |

| Power-on<br>State | Х       | Х       | Х       | X       | Х       | Х       | Х       | Х       |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The RX50\_xy bits report the result of a receiver detection cycle. One bit is assigned for each channel of the device. RX50\_xy is at a logic 1 level indicating a load and receiver was detected. When RX50\_xy is 0 then a load device was not detected. The RX50 register is read-only, and is undefined after power-up until a Receiver Detection cycle completes.

#### BYTE 2 - Loopback and Emphasis Control Register (LBEC)

LB\_xyxy#=0=loopback mode, LB\_xyxy#=1=normal mode, DE\_x=0=Full-bit de-emphasis, DE\_x=1=Half-bit de-emphasis

| Bit               | 7        | 6        | 5        | 4        | 3    | 2    | 1    | 0    |

|-------------------|----------|----------|----------|----------|------|------|------|------|

| Name              | LB_A0B0# | LB_A1B1# | LB_A2B2# | LB_A3B3# | DE_A | DE_B | rsvd | rsvd |

| Туре              | R/W      | R/W      | R/W      | R/W      | R/W  | R/W  | R    | R    |

| Power-on<br>State | LB#      | LB#      | LB#      | LB#      | 1    | 1    | X    | X    |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

Individual control for each lane is provided for the loopback function via this register.

#### BYTE 3 - Channel Input Disable (INDIS)

| Bit               | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|-------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Name              | INDIS_A0 | INDIS_B0 | INDIS_A1 | INDIS_B1 | INDIS_A2 | INDIS_B2 | INDIS_A3 | INDIS_B3 |

| Туре              | R/W      |

| Power-on<br>State | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

INDIS xy=0=enable input, INDIS xy=1=disable input

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Channel Input Disable register, provides control over the input buffer of each channel independently. When and INDIS\_xy bit is logic 1, then the input buffer is switched off and the input termination is high impedance. This feature can be used for PCB testing, and when only one input is used during Loopback as a demux function. When INDIS\_xy is at a logic 0 state then the input buffer is enabled (normal operating mode).

#### BYTE 4 - Channel Output Disable (OUTDIS)

ODIS\_xy=0=enable output, ODIS\_xy=1=disable output

| Bit               | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Name              | ODIS_A0 | ODIS_B0 | ODIS_A1 | ODIS_B1 | ODIS_A2 | ODIS_B2 | ODIS_A3 | ODIS_B3 |

| Туре              | R/W     |

| Power-on<br>State | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Channel Output Disable register, allows control over the output buffer of each channel independently. When and OUTDIS\_xy bit is logic 1, then the output buffer is switched off and the termination is high impedance. This feature can be used for PCB testing, and when only one output is used during Loopback as a mux function. When INDIS\_xy is at a logic 0 state then the input buffer is enabled (normal operating mode).

#### BYTE 5 - Channel Reset (RESET)

| Bit               | 7                                   | 6             | 5             | 4             | 3             | 2             | 1             | 0             |  |

|-------------------|-------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--|

| Name              | RESET_<br>A0#                       | RESET_<br>B0# | RESET_<br>A1# | RESET_<br>B1# | RESET_<br>A2# | RESET_<br>B2# | RESET_<br>A3# | RESET_<br>B3# |  |

| Туре              | R/W                                 | R/W           | R/W           | R/W           | R/W           | R/W           | R/W           | R/W           |  |

| Power-on<br>State | Latch from RESET# inputs at startup |               |               |               |               |               |               |               |  |

RESET# =0=reset, RESET# =1=normal operation. Latch from RESET# input at startup

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Channel Reset register allows for restart of an individual channels Receiver Detect function. A transition from 0 to 1 initiates a new Receiver Detect cycle (if the channel is enabled and receiver detect is enabled). While static at 0 or 1, the RESET# bit will have no effect on operation. The Channel Reset bits are read/write allowing the current state to be checked.

#### BYTE 6 - Power Down Control (PWR)

PD\_xy# =0=channel off/power down, PD\_xy# =1=normal operation, Latch from PD# input at startup

| Bit               | 7                               | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------------------|---------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| Name              | PD_A0#                          | PD_B0# | PD_A1# | PD_B1# | PD_A2# | PD_B2# | PD_A3# | PD_B3# |  |

| Туре              | R/W                             | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Power-on<br>State | Latch from PD# input at startup |        |        |        |        |        |        |        |  |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Power Down Control register allows for individual control over each channel for power savings. When PD\_xy# is logic 0 the channel is turned off. When PD\_xy# is 1 then the channel is enabled for normal operation.

#### BYTE 7 - Receiver Detect Enable (RXDETEN)

RXD\_xy =0=channel off/power down, RXD\_xy =1=normal operation, Latch from PD# input at startup

| Bit               | 7                                          | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------------------|--------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Name              | RXDE-<br>TEN_A0                            | RXDE-<br>TEN_B0 | RXDE-<br>TEN_A1 | RXDE-<br>TEN_B1 | RXDE-<br>TEN_A2 | RXDE-<br>TEN_B2 | RXDE-<br>TEN_A3 | RXDE-<br>TEN_B3 |

| Туре              | R/W                                        | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             |

| Power-on<br>State | Latch from RXD_A & RXD_B inputs at startup |                 |                 |                 |                 |                 |                 |                 |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The Receiver Detect Enable register allows for control of the receiver detect state machine for each individual channel. When RXD\_xy is set to 0, then the receiver detect function is disabled. When RXD\_xy is logic 1, then the receiver detect state machine is enabled for operation. The initial state of the register bits are determined by the RXD\_A and RXD\_B input pins during power-up.

#### BYTE 8 - A-Channels Equalizer and Output Control (AEOC)

SELx\_A: Equalizer configuration, Dx\_A: Emphasis control, Sx\_A: Output level control (see Configuration Table)

| Bit               | 7      | 6      | 5      | 4    | 3    | 2    | 1    | 0    |

|-------------------|--------|--------|--------|------|------|------|------|------|

| Name              | SELO_A | SEL1_A | SEL2_A | D0_A | D1_A | D2_A | S0_A | S1_A |

| Туре              | R/W    | R/W    | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  |

| Power-on<br>State | 1      | 1      | 1      | 1    | 1    | 1    | 1    | 1    |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The A-Channels Equalizer and Output Control register is used to control the configuration of the input equalizer and output emphasis and levels of the four A channels. These register bits are loaded from the input configuration pins of the same name at power-on. These bits may be changed if the MODE# input is set to allow I<sup>2</sup>C configuration. Please refer to the tables (1) Equalizer Configuration, (2) Output Swing Configuration and (3) Output Emphasis Configuration earlier in this document for setting information. All four A channels get the same configuration settings.

#### BYTE 9 - B-Channels Equalizer and Output Control (BEOC)

SELx\_B: Equalizer configuration, Dx\_B: Emphasis control, Sx\_B: Output level control (see Configuration Table)

| Bit               | 7      | 6      | 5      | 4    | 3    | 2    | 1    | 0    |

|-------------------|--------|--------|--------|------|------|------|------|------|

| Name              | SELO_B | SEL1_B | SEL2_B | D0_B | D1_B | D2_B | S0_B | S1_B |

| Туре              | R/W    | R/W    | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  |

| Power-on<br>State | 1      | 1      | 1      | 1    | 1    | 1    | 1    | 1    |

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use

The B-Channels Equalizer and Output Control register is used to control the configuration of the input equalizer and output emphasis and levels of the four B channels. These register bits are loaded from the input configuration pins of the same name at power-on. These bits may be changed if the MODE# input is set to allow I<sup>2</sup>C configuration. Please refer to the tables (1) Equalizer Configuration, (2) Output Swing Configuration and (3) Output Emphasis Configuration earlier in this document for setting information. All four B channels get the same configuration settings.

#### BYTE 10 - Reserved

Reserved Byte 10 is also visible via the I<sup>2</sup>C interface. This byte is R/W, is initialized to 0 at power up, is used for IC manufacturing test purposes and should not be changed for normal operation.

| Bit               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|------|------|------|------|------|------|------|------|

| Name              | VTH7 | VTH6 | VTH5 | VTH4 | VTH3 | VTH2 | VTH1 | VTH0 |

| Туре              | R/W  |

| Power-on<br>State | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    |

#### BYTE 11 - Idle Detect Threshold Control

Note: R=Read only, W=Write only, R/W=Read and Write, X=Undefined, rsvd=reserved for future use 0 = enable Only 1 bit can be enabled at a time

All trademarks are property of their respective owners.

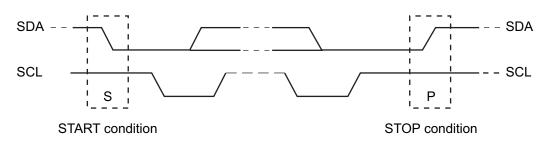

### **Start & Stop Conditions**

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition, as shown in the figure below.

I<sup>2</sup>C START and STOP conditions.

### I<sup>2</sup>C Data Transfer

#### Notes:

1. only block read and block write from the lowest byte are supported for this application.

2. for some I2C application, an offset address byte will be presented at the second byte in write command, which is called dummy byte here and will be simply ignored in this application for correct interoperation.

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                                                  |

|------------------------------------------------------------------------------------|

| Supply Voltage to Ground Potential0.5V to +2.5V                                    |

| DC SIG Voltage $\ldots \ldots \ldots \ldots \ldots \ldots -0.5V$ to $V_{DD}$ +0.5V |

| I <sup>2</sup> C DC SIG Voltage0.5V to +3.6V                                       |

| Current Output                                                                     |

| Power Dissipation Continuous1W                                                     |

| Operating Temperature40°C to +85°C                                                 |

| ESD, HBM: I <sup>2</sup> C pins –1kV to +1kV                                       |

| ESD, HBM: All other pins2kV to +2kV                                                |

|                                                                                    |

Note:

Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### AC/DC Electrical Characteristics

### Power Supply Characteristics (V\_{DD} = 1.2 $\pm 0.05$ V, T<sub>A</sub> = -40°C ~ +85°C)

| Symbol                  | Parameters                                    | Conditions             | Min. | Тур. | Max. | Units |

|-------------------------|-----------------------------------------------|------------------------|------|------|------|-------|

| I <sub>DDactive</sub>   | Power supply current - active                 | All channels switching |      |      | 800  |       |

| I <sub>DDstandby</sub>  | Power supply current - standby                | PD_xy# all 0           |      | 1    | 5    | mA    |

| I <sub>DD-channel</sub> | Power supply current - per<br>channel, Active |                        |      | 50   |      |       |

### AC Performance Characteristics ( $V_{DD} = 1.2 \pm 0.05V$ , $T_A = -40^{\circ}C \sim +85^{\circ}C$ )

| Symbol          | Parameters                           | Conditions | Min. | Тур. | Max. | Units |

|-----------------|--------------------------------------|------------|------|------|------|-------|

| T <sub>pd</sub> | Channel latency from input to output |            |      | 750  |      | ps    |

| Symbol                   | Parameters                              | Conditions | Min.  | Тур. | Max.  | Units |

|--------------------------|-----------------------------------------|------------|-------|------|-------|-------|

| ZRX-DIFF-DC              | DC Differential Input Impedance         |            | 80    | 100  | 120   | Ohma  |

| ZRX-DC                   | DC Input Impedance                      |            | 40    | 50   | 60    | Ohms  |

| VRX-DIFFP-P              | Differential Input Peak-to-peak Voltage |            | 0.175 |      | 1.200 | V     |

| VRX-CM-ACP               | AC Peak Common Mode Input Voltage       |            |       |      | 150   |       |

| Vth- <sub>DIFF p-p</sub> | Signal detect threshold voltage         |            | 65    |      | 175   | mV    |

#### **CML Receiver Input** ( $V_{DD} = 1.2 \pm 0.05V$ , $T_A = -40^{\circ}C \sim +85^{\circ}C$ )

### Equalizer

| Symbol            | Parameters      | Conditions    | Min. | Тур. | Max. | Units |

|-------------------|-----------------|---------------|------|------|------|-------|

| J <sub>RS-T</sub> | Residual jitter | Total         |      |      | 0.3  | Ulp-p |

| J <sub>RS-D</sub> | Residual jitter | Deterministic |      |      | 0.2  | Ulp-p |

| J <sub>RM</sub>   | Random jitter   | Note 2        |      | 1.5  |      | psrms |

Notes

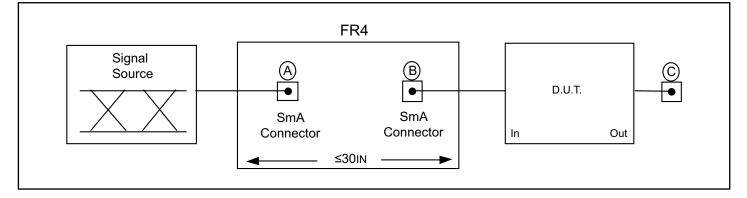

1. K28.7 pattern is applied differentially at point A as shown in AC test circuit (see figure).

2. Total jitter does not include the signal source jitter. Total jitter (TJ) = (14.1 × RJ + DJ) where RJ is random RMS jitter and DJ is maximum deterministic jitter. Signal source is a K28.5 ± pattern (00 1111 1010 11 0000 0101) for the deterministic jitter test and K28.7 (0011111000) or equivalent for random jitter test. Residual jitter is that which remains after equalizing media-induced losses of the environment of Figure 1 or its equivalent. The deterministic jitter at point B must be from media-induced loss, and not from clock source modulation. Jitter is measured at 0V at point C of the AC test circuit (see figure).

### **CML Transmitter Output** (V<sub>DD</sub> = 1.2 $\pm 0.05$ V, T<sub>A</sub> = -40°C ~ +85°C)

| Symbol                          | Parameters                                 | Conditions                             | Min. | Тур.                  | Max. | Units  |  |

|---------------------------------|--------------------------------------------|----------------------------------------|------|-----------------------|------|--------|--|

| Z <sub>OUT</sub>                | Output resistance                          | Single ended                           | 40   | 50                    | 60   |        |  |

| Z <sub>TX-DIFF-DC</sub>         | DC Differential TX Imped-<br>ance          |                                        | 80   | 100                   | 120  | – Ohms |  |

| V <sub>DIFFP</sub>              | Output Voltage Swing, Dif-<br>ferential    | VTX-D+ - VTX-D-                        | 200  |                       | 800  | mVp-p  |  |

| V <sub>TX-DIFFP-P</sub>         | Differential Peak-to-peak<br>Ouput Voltage | VTX-DIFFP-P = 2 *   VTX-D+ -<br>VTX-D- | 0.4  |                       | 1.6  | V      |  |

| V <sub>TX-C</sub>               | Common-Mode Voltage                        | VTX-D+ + VTX-D-   / 2                  |      | V <sub>DD</sub> - 0.3 |      |        |  |

| t <sub>F</sub> , t <sub>R</sub> | Transition Time                            | 20% to 80%                             |      |                       | 150  | ps     |  |

| C <sub>TX</sub> ( <sup>1)</sup> | AC Coupling Capacitor                      |                                        | 75   |                       | 200  | nF     |  |

#### Notes:

1. Recommended external coupling capacitor.

## Digital I/O DC Specifications (V\_{DD} = 1.2 $\pm 0.05 V,\, T_A = -40^{\circ}C \sim +85^{\circ}C)$

| Symbol               | Parameters                          | Conditions     | Min.                 | Тур. | Max.                    | Units |

|----------------------|-------------------------------------|----------------|----------------------|------|-------------------------|-------|

| V <sub>IH</sub>      | DC input logic high                 |                | $V_{DD}/2 + 0.2$     |      | V <sub>DD</sub> +0.3    |       |

| V <sub>IL</sub>      | DC input logic low                  |                | -0.3                 |      | V <sub>DD</sub> /2 -0.2 |       |

| V <sub>OH</sub>      | DC output logic high                | $I_{OH} = 4mA$ | V <sub>DD</sub> -0.4 |      |                         | V     |

| V <sub>OL</sub>      | DC output logic low                 | $I_{OL} = 4mA$ |                      |      | 0.4                     |       |

| V <sub>hys</sub>     | Hysteresis of Schmitt trigger input |                | 0.2                  |      |                         |       |

| $I_{IH}(1)$          | Input high current                  |                |                      |      | 100                     |       |

| $I_{IL1}(2)$         | Input low current                   |                | -20                  |      |                         | μA    |

| I <sub>IL2</sub> (3) | Input low current                   |                | -20                  |      |                         |       |

#### Notes:

1. Includes input signals A1, A2, A4, LB#, MODE#, RESET#, RXD\_[A:B], SCL, SDA

2. For control inputs without pullups: SCL, SDA

3. Control inputs with pull-ups include: LB#, MODE#, RESET#, RXD\_[A:B], A1, A2, A4

|                  |                                     | - //           | ,             |      |                    |       |

|------------------|-------------------------------------|----------------|---------------|------|--------------------|-------|

| Symbol           | Parameters                          | Conditions     | Min.          | Тур. | Max.               | Units |

| V <sub>IH</sub>  | DC input logic high                 |                | $0.85 V_{DD}$ |      | 3.6                |       |

| V <sub>IL</sub>  | DC input logic low                  |                | -0.3          |      | 0.3V <sub>DD</sub> | V     |

| V <sub>OL</sub>  | DC output logic low                 | $I_{OL} = 3mA$ |               |      | 0.4                | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger input |                | 0.2           |      |                    |       |

## SDA and SCL I/O for I<sup>2</sup>C-bus ( $V_{DD} = 1.2 \pm 0.05V$ , $T_A = -40^{\circ}C \sim +85^{\circ}C$ )

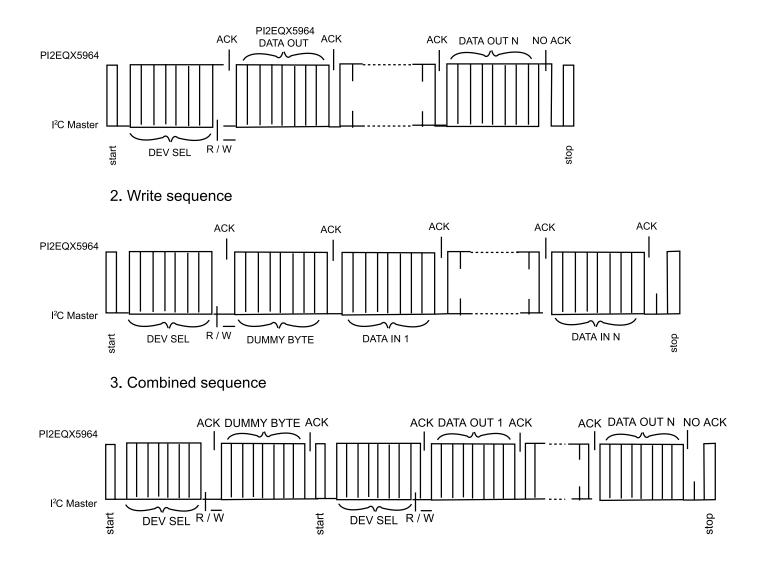

## Characteristics of the SDA and SCL bus lines for Standard Mode $I^2$ C-bus devices<sup>(1)</sup>

| Symbol              | Parameter                                                                                   | Conditions | Min. | Тур. | Max. | Unit |  |

|---------------------|---------------------------------------------------------------------------------------------|------------|------|------|------|------|--|

| f <sub>SCL</sub>    | SCL clock frequency                                                                         |            | 0    |      | 100  | kHz  |  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated |            | 4.0  |      | -    |      |  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                 |            | 4.7  |      | -    | μs   |  |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                |            | 4.0  |      | -    |      |  |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition                                                  |            | 4.7  |      | -    |      |  |

| t <sub>HD;DAT</sub> | Data hold time                                                                              |            | 10   |      | -    | ns   |  |

| t <sub>SU;DAT</sub> | Data set-up time                                                                            |            | 250  |      | -    |      |  |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                       |            | -    |      | 1000 | ns   |  |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                       |            |      |      | 300  |      |  |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                                                              |            | 4.0  |      | _    | μs   |  |

| t <sub>BUF</sub>    | Buss free time between a STOP and STOP condition                                            |            | 4.7  |      | -    |      |  |

| C <sub>b</sub>      | Capacitive load for each bus line                                                           |            | -    |      | 400  | pF   |  |

#### Notes:

1. All values referred to VIHmin and VILmax levels.

### I<sup>2</sup>C Timing

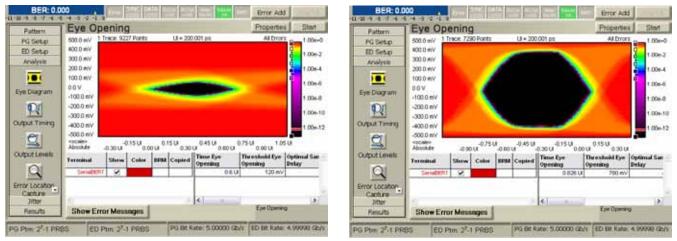

Eye Diagrams 5.0Gbps (input left, output right)

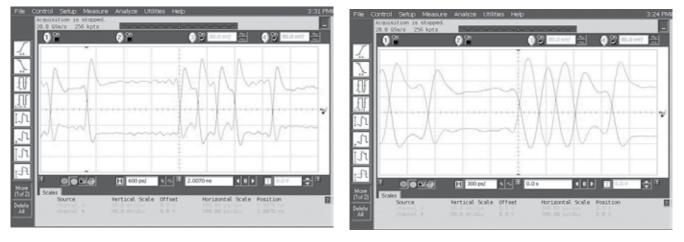

Data Waveforms, 2.5Gbps (left) & 5.0Gbps (right)

#### AC Test Circuit Referenced in the Electrical Characteristic Table

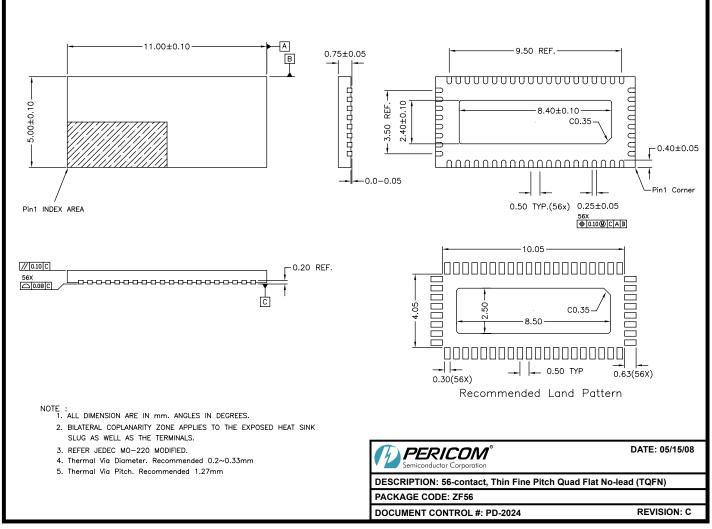

### **Packaging Information**

08-0208

Note:

For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

### **Ordering Information**

| Ordering Number | Package Code | Package Description             |

|-----------------|--------------|---------------------------------|

| PI2EQX5964ZFE   | ZF           | Pb-free & Green 56-Contact TQFN |

Notes:

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• X suffix = Tape/Reel