# **AUTOMATION**

User manual

# **IBS SUPI 3 OPC UM E**

Order No.: —

INTERBUS IBS SUPI 3 OPC protocol chip

# AUTOMATION

# User manual IBS SUPI 3 OPC INTERBUS protocol chip

| 04/2009 |

|---------|

|---------|

| Designation: | IBS SUPI 3 OPC UM E |

|--------------|---------------------|

|--------------|---------------------|

- Revision: 05

- Order No.: —

This user manual is valid for:

| Designation        | Order No. |

|--------------------|-----------|

| IBS SUPI 3 LS      | 2746977   |

| IBS SUPI 3 OPC     | 2746980   |

| IBS SUPI 3 OPC T&R | 2746964   |

# Please observe the following notes

In order to ensure the safe use of the product described, you have to read and understand this manual. The following notes provide information on how to use this manual.

#### User group of this manual

The use of products described in this manual is oriented exclusively to qualified electricians or persons instructed by them, who are familiar with applicable standards and other regulations regarding electrical engineering and, in particular, the relevant safety concepts.

Phoenix Contact accepts no liability for erroneous handling or damage to products from Phoenix Contact or third-party products resulting from disregard of information contained in this manual.

#### Explanation of symbols used and signal words

This is the safety alert symbol. It is used to alert you to potential personal injury hazards. Obey all safety messages that follow this symbol to avoid possible injury or death.

#### DANGER

This indicates a hazardous situation which, if not avoided, will result in death or serious injury.

#### WARNING

This indicates a hazardous situation which, if not avoided, could result in death or serious injury.

#### CAUTION

This indicates a hazardous situation which, if not avoided, could result in minor or moderate injury.

The following types of messages provide information about possible property damage and general information concerning proper operation and ease-of-use.

i

#### NOTE

This symbol and the accompanying text alerts the reader to a situation which may cause damage or malfunction to the device, either hardware or software, or surrounding property.

This symbol and the accompanying text provides additional information to the reader. It is also used as a reference to other sources of information (manuals, data sheets, literature) on the subject matter, product, etc.

#### General terms and conditions of use for technical documentation

Phoenix Contact reserves the right to alter, correct, and/or improve the technical documentation and the products described in the technical documentation at its own discretion and without giving prior notice, insofar as this is reasonable for the user. The same applies to any technical changes that serve the purpose of technical progress.

The receipt of technical documentation (in particular data sheets, installation instructions, manuals, etc.) does not constitute any further duty on the part of Phoenix Contact to furnish information on alterations to products and/or technical documentation. Any other agreement shall only apply if expressly confirmed in writing by Phoenix Contact. Please note that the supplied documentation is product-specific documentation only and that you are responsible for checking the suitability and intended use of the products in your specific application, in particular with regard to observing the applicable standards and regulations. Although Phoenix Contact makes every effort to ensure that the information content is accurate, up-to-date, and state-of-the-art, technical inaccuracies and/or printing errors in the information cannot be ruled out. Phoenix Contact does not offer any guarantees as to the reliability, accuracy or completeness of the information. All information made available in the technical data is supplied without any accompanying guarantee, whether expressly mentioned, implied or tacitly assumed. This information does not include any guarantees regarding quality, does not describe any fair marketable quality, and does not make any claims as to quality guarantees or guarantees regarding the suitability for a special purpose.

Phoenix Contact accepts no liability or responsibility for errors or omissions in the content of the technical documentation (in particular data sheets, installation instructions, manuals, etc.).

The aforementioned limitations of liability and exemptions from liability do not apply, in so far as liability must be assumed, e.g., according to product liability law, in cases of premeditation, gross negligence, on account of loss of life, physical injury or damage to health or on account of the violation of important contractual obligations. Claims for damages for the violation of important contractual obligations are, however, limited to contract-typical, predictable damages, provided there is no premeditation or gross negligence, or that liability is assumed on account of loss of life, physical injury or damage to health. This ruling does not imply a change in the burden of proof to the detriment of the user.

# Statement of legal authority

|              | manual by any third party is forbidden. Repro<br>well as electronic and photographic archivin                                                        | This manual, including all illustrations contained herein, is copyright protected. Use of this manual by any third party is forbidden. Reproduction, translation, and public disclosure, as well as electronic and photographic archiving or alteration requires the express written consent of Phoenix Contact. Violators are liable for damages. |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|              | Phoenix Contact reserves all rights in the ca<br>design. Third-party products are always nan<br>existence of such rights shall not be exclude        | ned without reference to patent rights. The                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|              | How to contact us                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Internet     | Up-to-date information on Phoenix Contact p<br>found on the Internet at:                                                                             | products and our Terms and Conditions can be                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|              | www.phoenixcontact.com.                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|              | Make sure you always use the latest docume<br>It can be downloaded at:                                                                               | entation.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|              | www.phoenixcontact.net/download.                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Subsidiaries | If there are any problems that cannot be solv<br>your Phoenix Contact subsidiary.<br>Subsidiary contact information is available a                   | ved using the documentation, please contact                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Published by |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| rubiished by | PHOENIX CONTACT GmbH & Co. KG<br>Flachsmarktstraße 8<br>32825 Blomberg<br>Germany<br>Phone +49 - (0) 52 35 - 3-00<br>Fax +49 - (0) 52 35 - 3-4 12 00 | PHOENIX CONTACT<br>P.O. Box 4100<br>Harrisburg, PA 17111-0100<br>USA<br>Phone +1-717-944-1300                                                                                                                                                                                                                                                      |  |  |  |  |  |

|              | Should you have any suggestions or recomm layout of our manuals, please send your con                                                                | endations for improvement of the contents and nments to                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|              | tecdoc@phoenixcontact.com.                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

# Table of contents

| 1 | General functions     |     |                                                          | 1-1  |

|---|-----------------------|-----|----------------------------------------------------------|------|

|   |                       | 1.1 | Introduction                                             | 1-1  |

|   |                       | 1.2 | SUPI 3 OPC protocol chip                                 | 1-1  |

|   |                       | 1.3 | Basic structure                                          | 1-2  |

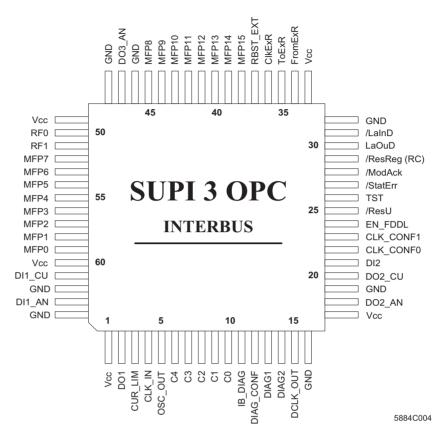

|   |                       | 1.4 | Housing type                                             | 1-3  |

|   |                       |     | 1.4.1 TQFP 64 housing (Thin Quad Flat Pack)              |      |

|   |                       |     | 1.4.2 Cooling surface (slug)                             | 1-4  |

|   |                       |     | 1.4.3 TQFP 44 housing (Thin Quad Flat Pack)              | 1-5  |

|   |                       |     | 1.4.4 Pin boards                                         | 1-6  |

|   |                       | 1.5 | Pin description                                          | 1-8  |

|   |                       | 1.6 | Optical regulation (SUPI 3 OPC (T&R) only)               | 1-10 |

|   |                       |     | 1.6.1 Initializing optical regulation                    | 1-11 |

|   |                       |     | 1.6.2 Online regulation                                  | 1-13 |

|   |                       |     | 1.6.3 MAU warnings                                       | 1-16 |

|   |                       | 1.7 | Basic wiring                                             | 1-17 |

|   |                       |     | 1.7.1 Clock supply                                       |      |

|   |                       |     | 1.7.2 Initializing the chip                              | 1-19 |

| 2 | INTERBUS interface    | s   |                                                          | 2-1  |

|   |                       | 2.1 | Overview                                                 | 2-1  |

|   |                       |     | 2.1.1 Bus connector recognition and regulation function  | 2-2  |

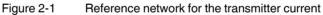

|   |                       |     | 2.1.2 Setting the optical fiber transmitter current      | 2-2  |

|   |                       | 2.2 | Local bus devices                                        | 2-4  |

|   |                       |     | 2.2.1 Local bus without device-oriented diagnostics      | 2-4  |

|   |                       |     | 2.2.2 Local bus with device-oriented diagnostics         | 2-6  |

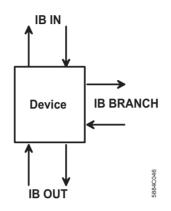

|   |                       | 2.3 | Remote bus devices                                       | 2-8  |

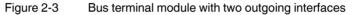

|   |                       | 2.4 | Bus terminal module                                      | 2-9  |

| 3 | Application interface |     |                                                          | 3-1  |

|   |                       | 3.1 | Overview                                                 | 3-1  |

|   |                       | 3.2 | Binary I/O operating mode                                | 3-2  |

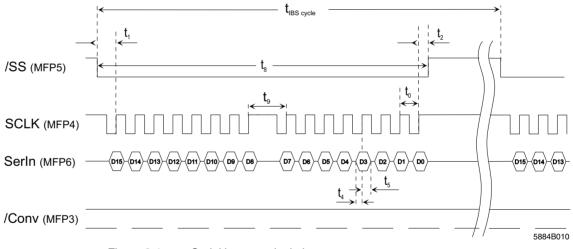

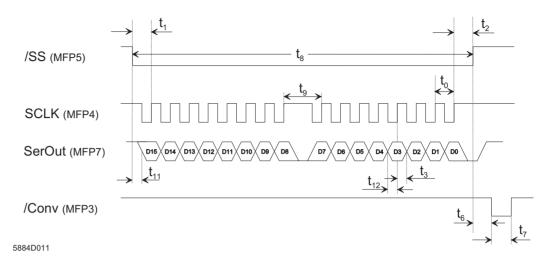

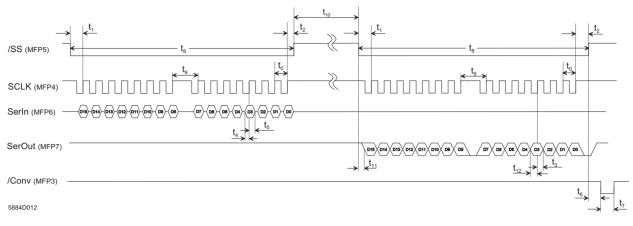

|   |                       | 3.3 | Serial I/O (SPI master mode) operating mode              | 3-3  |

|   |                       |     | 3.3.1 General                                            | 3-3  |

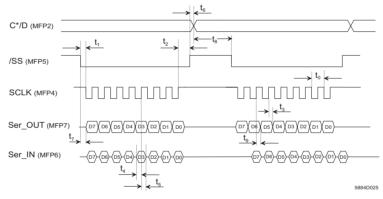

|   |                       |     | 3.3.2 Timing of the SPI interface                        | 3-4  |

|   |                       | 3.4 | Serial $\mu P$ interface (SPI slave mode) operating mode | 3-7  |

|   |                       |     | 3.4.1 General                                            | 3-7  |

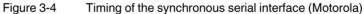

|   |                       |     | 3.4.2 Serial interface timing                            |      |

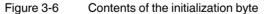

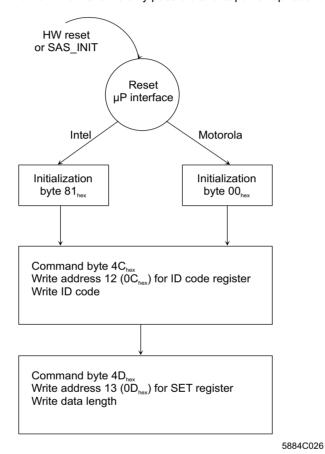

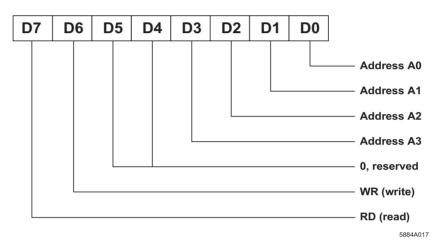

|   |                       |     | 3.4.3 Initializing the microprocessor interface          |      |

|   |                       |     | 3.4.4 Data transmission to the SUPI 3 OPC/SUPI 3 LS      |      |

|   |                       |     | 3.4.5 Initialization sequence - example                  |      |

|   |                       |     | 3.4.6 Block transfer                                     |      |

|   |                       |     | 3.4.7 Address area assignment                            | 3-19 |

|   |                     |     | 3.4.8      | INTERBUS data registers                                 | 3-20 |

|---|---------------------|-----|------------|---------------------------------------------------------|------|

|   |                     |     | 3.4.9      | Processor alarm register and processor command register | 3-20 |

|   |                     |     | 3.4.10     | ID code register                                        | 3-20 |

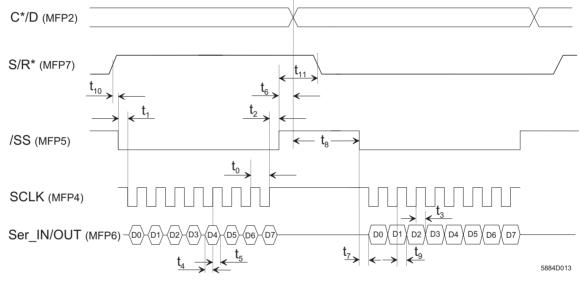

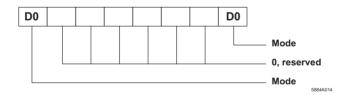

|   |                     |     | 3.4.11     | SET register                                            | 3-20 |

|   |                     |     | 3.4.12     | Optical data register                                   | 3-23 |

|   |                     |     | 3.4.13     | Optical status register                                 | 3-24 |

|   |                     |     | 3.4.14     | Synchronizing the application                           | 3-25 |

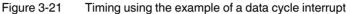

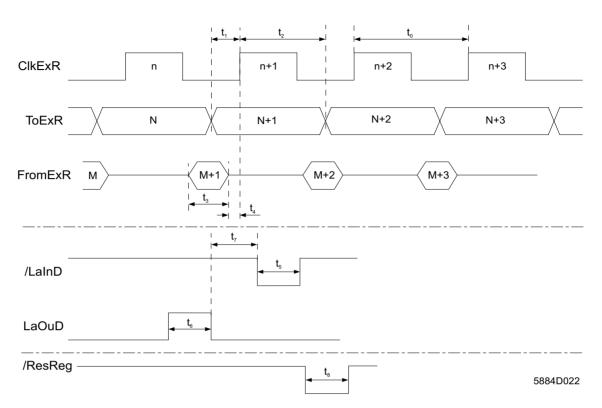

|   |                     | 3.5 | Serial re  | egister expansion                                       | 3-30 |

|   |                     | 3.6 | Diagno     | stics                                                   | 3-34 |

|   |                     |     | 3.6.1      | Diagnostic inputs/outputs                               | 3-34 |

|   |                     |     | 3.6.2      | Input/output module error                               | 3-36 |

| А | Technical appendix. |     |            |                                                         | A-1  |

|   |                     | A 1 | ID code    | specification (extract)                                 | A-2  |

|   |                     | A 2 | Genera     | I processing information                                | A-5  |

|   |                     |     | A 2.1      | Storage                                                 | A-5  |

|   |                     |     | A 2.2      | Processing time                                         | A-5  |

|   |                     |     | A 2.3      | Soldering                                               | A-5  |

|   |                     | АЗ  | Length     | code specification                                      | A-6  |

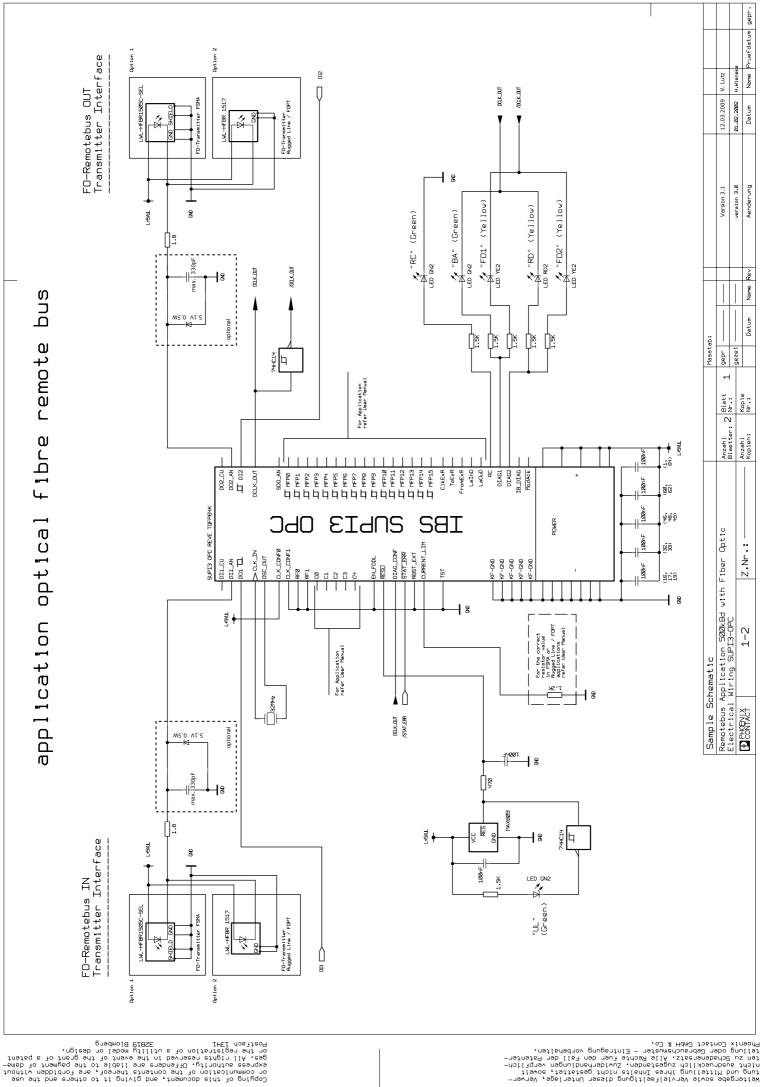

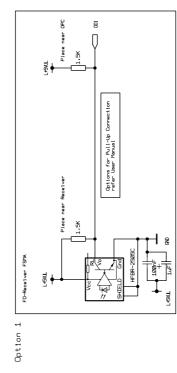

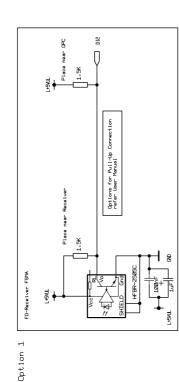

| в | Wiring examples     |     |            |                                                         | B-1  |

| С | Appendix            |     |            |                                                         | C-1  |

|   |                     | C 1 | List of fi | gures                                                   | C-1  |

|   |                     | C 2 |            | ables                                                   |      |

|   |                     |     |            |                                                         |      |

# **1** General functions

# 1.1 Introduction

The SUPI 3 OPC/SUPI 3 OPC (T&R) (referred to in the following as: SUPI 3 OPC; OPC =  $\mathbf{O}$ ptical **P**rotocol **C**hip) is another INTERBUS slave protocol chip of the SUPI 3 family. It can be used to develop all device classes such as digital modules, bus terminal modules (BK), and intelligent I/O devices.

This user manual describes the SUPI 3 OPC in detail and illustrates its most common applications.

The SUPI 3 OPC offers a high level of operational safety and diagnostic capability for optical signal transmission. The control systems and procedures required are described in this user manual.

On the basis of this description you may implement your own INTERBUS devices within a very short time. With the end user in mind, subject the devices to the INTERBUS conformance test.

In addition to this document you will find the INTERBUS Club guideline "Conformity Test and Certification" as a reference work on the Internet at <u>www.interbusclub.com</u>.

Current hardware and software information for the device manufacturer as well as further product documents from Phoenix Contact can be found on the Internet at <u>www.phoenixcontact.net/download</u>.

# 1.2 SUPI 3 OPC protocol chip

The SUPI 3 OPC protocol chip is an ASIC in 0.6  $\mu$ m CMOS technology with approximately 15,000 gate equivalents. It can be used to implement 2-wire remote bus and 2-wire local bus devices.

The SUPI 3 OPC differs from the IBS SUPI 3 in particular through its support of optical transmission methods. These include:

- Optical power regulation for fiber optic transmitters

- Optical transmission diagnostics

- Automatic bus connector recognition (RBST/LBST<sup>1</sup>) for copper and fiber optic transmission

- Automatic recognition of the control function on other units or devices

<sup>&</sup>lt;sup>1</sup> Signal, which indicates that another device follows.

The SUPI 3 OPC can be used for I/O applications, bus terminal modules, and intelligent slave devices. It has a parallel I/O interface (similar to the multi-function pins (MFPs) on SUPI 3), a voltage monitor, an SPI master and slave interface, and device-oriented local bus diagnostics for devices with and without data return.

| Table 1-1 | Housing versions   |

|-----------|--------------------|

|           | riouoling voiolono |

| Order designation  | Order No. | Housing |

|--------------------|-----------|---------|

| IBS SUPI 3 LS      | 2746977   | TQFP44  |

| IBS SUPI 3 OPC     | 2746980   | TQFP64  |

| IBS SUPI 3 OPC T&R | 2746964   | TQFP64  |

1

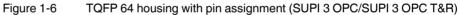

The SUPI 3 LS (TQFP 44) is a version of the SUPI 3 OPC with a smaller housing. Therefore it has less pins. This means that the SUPI 3 LS **cannot** be extended by additional data registers and is only suitable for copper interfaces. Therefore, SUPI 3 LS does **not** support optical signal transmission.

# 1.3 Basic structure

The device processes layer 2 of the ISO/OSI reference model independently according to IEC 61158.

i

All interfaces are designed for the **2-wire protocol only**. The following block diagram shows the chip structure.

Figure 1-1 Block diagram of the SUPI 3 OPC

# 1.4 Housing type

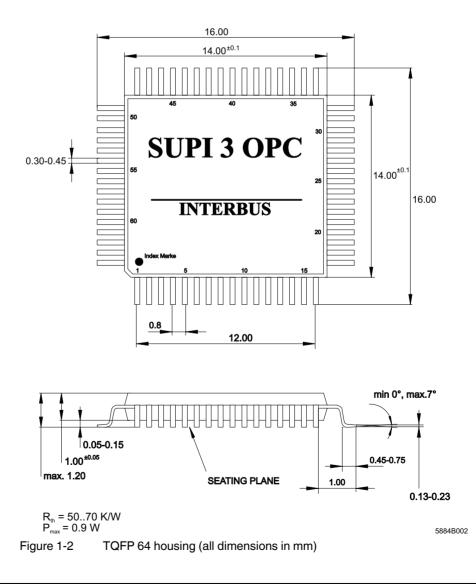

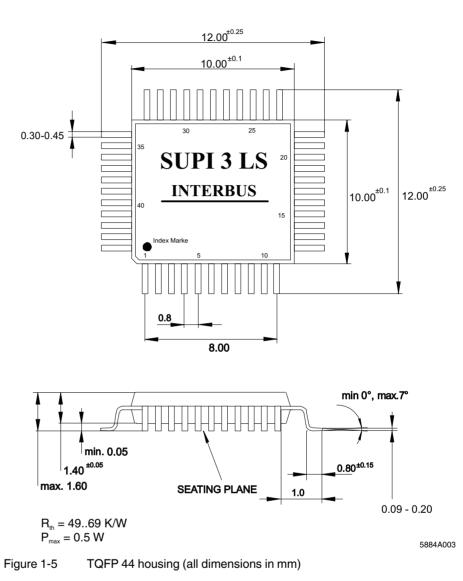

The SUPI 3 OPC is available in housing versions TQFP 64 and TQFP 44.

For optical power regulation, SUPI 3 OPC/SUPI 3 OPC T&R (both housing type TQFP 64 (with slug)) must be used, because the power drivers for optical regulation are integrated into this housing. Because the SUPI 3 LS (housing type TQFP 44) has a reduced number of pins it **cannot** be expanded with additional data registers and is **only** suitable for copper interfaces.

The TQFP 64 housing should be connected to the printed circuit board for the removal of heat. Layout notes can be found in Section 1.4.2 "Cooling surface (slug)".

# 1.4.1 TQFP 64 housing (Thin Quad Flat Pack)

## 1.4.2 Cooling surface (slug)

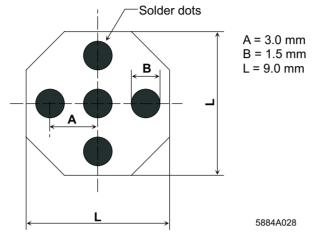

The TQFP 64 housing has a metal cooling surface on the back to improve its thermal properties. To ensure the optimum removal of heat, the cooling surface must be connected to a grounding surface. The contacts should be made according to the diagrams below.

Figure 1-3 Contacts for the cooling surface

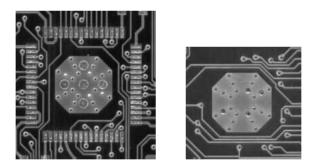

If a printed circuit board with grounding layer is used, it is recommended to provide approximately 15-20 through-contacts on the copper surface. An example is given in Figure 1-4.

Figure 1-4 Layout example for TQFP 64 with cooling surface

1.4.3 TQFP 44 housing (Thin Quad Flat Pack)

#### 1.4.4 Pin boards

TQFP 64 pin board

#### Table 1-2 TQFP 64 pin table

| Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        |

|------------|-----------------|------------|-----------------|------------|-----------------|

| 1          | V <sub>cc</sub> | 23         | CLK_CONF1       | 45         | MFP8            |

| 2          | DO1             | 24         | EN_FDDL         | 46         | GND             |

| 3          | CUR_LIM         | 25         | /ResU           | 47         | DO3_AN          |

| 4          | CLK_IN          | 26         | TST             | 48         | GND             |

| 5          | OSC_OUT         | 27         | /StatErr        | 49         | V <sub>cc</sub> |

| 6          | C4              | 28         | /ModAck         | 50         | RF0             |

| 7          | C3              | 29         | /ResReg (RC)    | 51         | RF1             |

| 8          | C2              | 30         | LaOuD           | 52         | MFP7            |

| 9          | C1              | 31         | /LaInD          | 53         | MFP6            |

| 10         | C0              | 32         | GND             | 54         | MFP5            |

| 11         | IB_DIAG         | 33         | V <sub>cc</sub> | 55         | MFP4            |

| Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name | Pin<br>No. | Pin Name        |

|------------|-----------------|------------|----------|------------|-----------------|

| 12         | DIAG_CONF       | 34         | FromExR  | 56         | MFP3            |

| 13         | DIAG1           | 35         | ToExR    | 57         | MFP2            |

| 14         | DIAG2           | 36         | ClkExR   | 58         | MFP1            |

| 15         | DCLK_OUT        | 37         | RBST_EXT | 59         | MFP0            |

| 16         | GND             | 38         | MFP15    | 60         | V <sub>cc</sub> |

| 17         | V <sub>cc</sub> | 39         | MFP14    | 61         | DI1_CU          |

| 18         | DO2_AN          | 40         | MFP13    | 62         | GND             |

| 19         | GND             | 41         | MFP12    | 63         | DI1_AN          |

| 20         | DO2_CU          | 42         | MFP11    | 64         | GND             |

| 21         | DI2             | 43         | MFP10    |            |                 |

| 22         | CLK_CONF0       | 44         | MFP9     |            |                 |

Table 1-2TQFP 64 pin table (continued)

#### TQFP 44 pin board

Figure 1-7 TQFP 44 housing with pin assignment (SUPI 3 LS)

| Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        |

|------------|-----------------|------------|-----------------|------------|-----------------|

| 1          | V <sub>cc</sub> | 16         | CLK_CONF1       | 31         | MFP9            |

| 2          | DO1             | 17         | GND             | 32         | MFP8            |

| 3          | CLK_IN          | 18         | /ResU           | 33         | GND             |

| 4          | OSC_OUT         | 19         | TST             | 34         | V <sub>cc</sub> |

| 5          | C3              | 20         | /StatErr        | 35         | MFP7            |

| 6          | C2              | 21         | /ModAck         | 36         | MFP6            |

| 7          | C1              | 22         | GND             | 37         | MFP5            |

| 8          | C0              | 23         | V <sub>cc</sub> | 38         | MFP4            |

| 9          | IB_DIAG         | 24         | RBST_EXT        | 39         | MFP3            |

| 10         | DCLK_OUT        | 25         | MFP15           | 40         | MFP2            |

| 11         | GND             | 26         | MFP14           | 41         | MFP1            |

| 12         | V <sub>cc</sub> | 27         | MFP13           | 42         | MFP0            |

| 13         | DO2_CU          | 28         | MFP12           | 43         | DI1_CU          |

| 14         | DI2             | 29         | MFP11           | 44         | GND             |

| 15         | CLK_CONF0       | 30         | MFP10           |            |                 |

Table 1-3TQFP 44 pin table

# 1.5 Pin description

# Table 1-4 Pin description (SUPI 3 OPC (T&R)/SUPI 3 LS)

| Designation  | Meaning                                                                            | Туре | TQFP 64 | TQFP 44 |

|--------------|------------------------------------------------------------------------------------|------|---------|---------|

| CLK_IN       | Oscillator input                                                                   | CI   | Х       | Х       |

| OSC_OUT      | Oscillator output                                                                  | OSC  | Х       | Х       |

| DCLK_OUT     | Data clock output (500 kbps/2 Mbps)                                                | B8   | Х       | Х       |

| CLK_CONF[10] | PLL/clock cell configuration                                                       | CI   | Х       | Х       |

| C4           | Operating mode configuration                                                       | Clp  | Х       | -       |

| C[30]        | Operating mode configuration                                                       | CI   | Х       | Х       |

| RF[10]       | Optical regulation configuration                                                   | Clp  | Х       | -       |

| RBST_EXT     | Optical regulation configuration (or alarm input if an outgoing interface is used) | STC  | Х       | Х       |

| MFP[150]     | Multi-function pins                                                                | BD4  | Х       | Х       |

|              | INTERBUS ring data line                                                            |      |         |         |

| DO1          | Input: Data line OUT forward                                                       | STC  | Х       | Х       |

| Designation     | Meaning                                                                              | Туре | TQFP 64 | TQFP 44 |

|-----------------|--------------------------------------------------------------------------------------|------|---------|---------|

| DI1_CU          | Output: Data line OUT digital return for copper                                      | B4   | Х       | Х       |

| DI1_AN          | Output: Data line OUT analog return for optical fiber                                | AN60 | Х       | -       |

| DI2             | Input: Data line IN return                                                           | STC  | Х       | Х       |

| DO2_CU          | Output: Data line OUT digital forward for copper                                     | B4   | Х       | Х       |

| DO2_AN          | Output: Data line OUT analog forward for optical fiber                               | AN60 | Х       | -       |

| DO3_AN          | Output: Data line OUT analog forward branch for optical fiber                        | AN60 | Х       | -       |

|                 | Signals for external register expansion                                              |      |         |         |

| /LaInD          | Latch signal for input data                                                          | B4   | Х       | -       |

| LaOuD           | Latch signal for output data                                                         | B4   | Х       | -       |

| ClkExR          | Clock for external data registers                                                    | B4   | Х       | -       |

| ToExR           | Data output for external data registers <b>without</b> internal SUPI 3 OPC registers | B2   | Х       | _       |

| FromExR         | Data input for external data registers                                               | STC  | Х       | -       |

|                 | Diagnostics                                                                          |      |         |         |

| /StatErr        | "Module error" alarm input                                                           | STCp | Х       | Х       |

| /ModAck         | Acknowledgment output for detected module error                                      | B2   | Х       | Х       |

| /ResReg (RC)    | Reset external register (or RC LED)                                                  | B4   | Х       | -       |

| DIAG_CONF       | Configuration of diagnostic outputs                                                  | Clp  | Х       | -       |

| DIAG1           | "BA" or "FO1 IN" alarm output                                                        | B4   | Х       | -       |

| DIAG2           | "RBDA" or "FO2 OUT" alarm output                                                     | B4   | Х       | -       |

| IB_DIAG         | Diagnostic output (limited)                                                          | B4   | Х       | Х       |

|                 |                                                                                      |      |         |         |

| CUR_LIM         | Control current setting                                                              | PAS  | Х       | -       |

| TST             | Test input, hard-wire to GND                                                         | CI   | Х       | Х       |

| EN_FDDL         | Reserved, hard-wire to GND                                                           | CI   | Х       | -       |

| /ResU           | Initialization reset (input and output)                                              | OD8  | Х       | Х       |

| V <sub>cc</sub> | Voltage supply +5 V                                                                  |      | Х       | Х       |

| GND             | Ground                                                                               |      | Х       | Х       |

# Table 1-4 Pin description (SUPI 3 OPC (T&R)/SUPI 3 LS) (continued)

# Cell types

| CI:   | CMOS input                              |

|-------|-----------------------------------------|

| Clp:  | CMOS input with pull-up                 |

| STC:  | CMOS Schmitt trigger input              |

| STCp: | CMOS Schmitt trigger input with pull-up |

|       |                                         |

| B2:   | Driver output 2 mA                                                                  |

|-------|-------------------------------------------------------------------------------------|

| B4:   | Driver output 4 mA                                                                  |

| B8:   | Driver output 8 mA                                                                  |

| BD4:  | Bidirectional with TTL Schmitt trigger input without pull-up and 4 mA driver output |

| AN60: | DAC current output 60 mA                                                            |

| OD8:  | 8 mA open drain output                                                              |

| OSC:  | Oscillator cell output                                                              |

| PAS:  | Passive external components                                                         |

|       |                                                                                     |

#### Optical regulation (SUPI 3 OPC (T&R) only) 1.6

SUPI 3 LS does not support optical regulation.

The SUPI 3 OPC offers a high level of operational safety and diagnostic capability for optical signal transmission compared with the IBS SUPI 3. The control systems and procedures required are described in the following section.

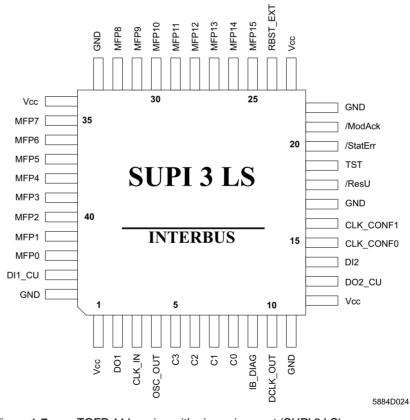

The scope of functions for "optical regulation" includes automatic interface recognition, initialization, and online regulation.

Parameter variations in the fiber optic transmitters are automatically corrected in certain areas. This improves the performance of the system (longer distances) because it adapts to the actual (typical) and not the worst case component characteristics. To simplify configuration and diagnostics, the measured distances, the current power level and the enable status of the regulation can be transmitted to the master via the internal diagnostics and report manager in the SUPI 3 OPC.

Transmission power of the fiber optic components is adjusted to a set value by the device manufacturer to ensure compatibility with earlier SUPI 3 devices, and in no circumstances should the receiver be overcontrolled.

**Online regulation** Online regulation adapts the transmission power to modifications in the transmission characteristics and ensures an adjustable system reserve of 3dB. The transmission characteristics may change during operation due to aging and temperature change in the transmission/reception element and fibers, and due to mechanical load (bending, tensile load) on the fibers.

#### Behavior on a reset

An INTERBUS reset it detected in the ASIC core. When a reset is detected, regulation is reset for the reset period. Once the INTERBUS reset has been canceled, automatic interface recognition is carried out. Initialization then starts in optical power regulation mode. During interface recognition and initialization the protocol core remains the reset state. Automatic interface recognition is always carried out at the end of an INTERBUS reset if *RF[1..0]* ≠ "10".

## 1.6.1 Initializing optical regulation

During initialization (6 ms, maximum), the transmission power of the optical interface is adapted to the characteristics of the transmission path present in the application (transmitter  $\rightarrow$  fiber optic  $\rightarrow$  receiver). In addition, the initialization determines whether the subsequent device also supports the optical regulation or diagnostic function. If the initialization sequence fails, the device is operated as a device without optical regulation, i.e., via an adjusted transmitter with maximum power for fiber optic transmission.

The following section details the mechanisms used to evaluate the signal received (which also apply for online regulation), and describes the initialization sequence. The path is only initialized if optical regulation operating mode is selected using *RF[1..0]* and the corresponding interface is a remote bus interface. The initialization result can be illustrated by a diagnostic LED for each interface if the diagnostic outputs are configured correspondingly (see Table 3-17 on page 3-34).

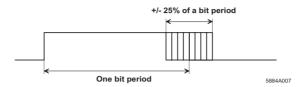

The SUPI 3 OPC can correctly decode a bit using the signal distortion<sup>1</sup> shown in Figure 1-9. Clock deviation over 13 bits must be within the range 500 kbps  $\pm 0.1\%$  or 2 Mbps  $\pm 0.1\%$ .

#### Initialization control

After a reset (power-up or INTERBUS reset) and automatic interface recognition, initialization automatically determines whether the corresponding interface is connected to a regulated or unregulated interface in the subsequent device (device detection without optical regulation).

If the interface is connected to a regulated interface, optical power of the interface is set to a power minimum with a defined reserve and distortion is checked. A regulation pattern is retransmitted, the regulation response from the other device is evaluated and, if necessary, transmission power is reduced.

Initialization is terminated:

- If the maximum number of regulation procedures is reached (13) or

- If the critical power level is only just ensured on a permissible distortion

The maximum possible number of regulations procedures is determined by the number of power levels. The maximum possible number of regulations procedures is determined by the precision of initialization. Initialization has 15 power levels.

After power-up or an INTERBUS reset, the transmitter for the incoming interface transmits the "Light on" signal and thus starts the initialization process in the outgoing interface of the previous device. Due to its location the outgoing interface is always the first transmitter. Transmission power for the outgoing interface is then reduced until the receiver for the outgoing interface receives the first negative regulation response. Transmission power is then increased by one and started up.

The "Light off" signal corresponds to the regulation response "Pattern detected", and the "Light on" signal corresponds to the regulation response "Pattern not detected". After successful initialization of the outgoing interface, the regulation direction changes, i.e. the transmitter for the incoming interface on the subsequent device is regulated in the same way.

Initialization starts once the end of the INTERBUS reset has been detected on the incoming interface. It leads to the cancellation of the INTERBUS reset on the outgoing interface or on the branch through telegrams. INTERBUS devices can only be switched off by the master after the maximum initialization period (6 ms) i.e., transmission power is adapted to the path characteristics.

- <sup>1</sup> All amounts which are caused by sampling errors, distortions due to time recovery components, pulse width distortions due to optical components (transmitter, receiver, and fiber), distortions due to electronics, jitter, etc.

- <sup>2</sup> Medium Dependent Sublayer

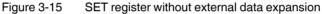

In addition, during initialization the length of the optical path is determined by a runtime measurement. This enables the detection of fiber optic cables, which are too long. During initialization, the time from the transmission of the first status telegram to the receipt of a positive response (logical 0 level) is measured using a timer. Using the clock frequency and the known runtime of the light in the medium, the distance can be calculated from the timer result using the following formula:

$$L = n \cdot \frac{1}{f \cdot t}$$

Where:

L: Length (forward and return)

n: Timer result

f: Clock at e.g., 500 kB (= 8 MHz)

t: 5 ns/m (runtime constant)

Table 1-5Length of the transmission path

| Path length    | Resolution           | Value range | INTERBUS  |

|----------------|----------------------|-------------|-----------|

| 0 m to 400 m   | 24 m (48 m), typical | 0 to 62     | 500 kbaud |

| 400 m to 20 km | -                    | 63          | 500 kbaud |

| 0 m to 400 m   | 6 m (12 m), typical  | 0 to 62     | 2 Mbytes  |

| 400 m to 20 km | -                    | 63          | 2 Mbytes  |

The typical resolution of the cable length for the fibers used at a transmission speed of 500 kbaud is 24 m (the worst case is 48 m) for fiber distances of up to 400 m (in each direction). For greater fiber distances (HCS and glass systems) the indicator is > 400 m. The worst case resolution of 48 m occurs in systems with a synchronous clock, where the clock system has no phase shift. The INTERBUS master can read the cable lengths from the chip.

If the interface cannot be initialized in optical regulation mode, all regulation mechanisms are deactivated.

## 1.6.2 Online regulation

After successful initialization (power set, distortion OK) online regulation is enabled. During initialization, the distance is determined for the outgoing interface or for the branch and this information is made available in the internal diagnostics and report manager. The enable status of the regulation function for each interface is also given in the chip for the master.

Optical fiber path regulation is used as the "optical power regulation" for the transmitter. Additional information for optical fiber path regulation is transmitted during data transmission within the INTERBUS protocol.

#### **Optical power regulation**

During data transmission, the path characteristics are monitored and, if necessary, the power is adapted to the modified path characteristics (online regulation).

If the system reserves are too low, this is signaled by an MAU warning, which prompts you to check the path or the cable **prior to** a system failure. Additional information can be found in Section 3.6, "Diagnostics". Errors are indicated centrally through the transmission of the error message to the INTERBUS protocol using the diagnostics and report manager and through diagnostic LEDs *FO1* and *FO2*.

| 🗱 IBS CMD G4 c:\cmd451e\PROJ          |                                           |                    |                    |                         |            |              |             | _ 8      |

|---------------------------------------|-------------------------------------------|--------------------|--------------------|-------------------------|------------|--------------|-------------|----------|

| Eile Edit View Configuration Moni-    | or Disconstine Dation                     | . 2                |                    |                         |            |              |             |          |

| 🗅 🍃 🖶 😂 🕰 🕷                           | Optical diagnostic<br>File Edit Read In O |                    | URM                |                         |            |              |             |          |

| Project                               |                                           |                    |                    | I                       |            |              | 1           |          |

|                                       | Date                                      | Forward path       | Return path        | PFor                    | PReturn    | Dist.Counter | Dist.       | LWL-Type |

| <u>_</u>                              | ■ 13.6.2001 10:46:33<br>−1.0<->2.0        | optimal            | optimal            | 11 (of 15)              | 0.000      |              | 150m        |          |

| PLC/PC                                | 2.0<->3.0                                 | optimal            | optimal            | 7 (of 15)               |            |              | 75m         |          |

|                                       | 3.0<->4.0                                 | optimal            | optimal            | 3 (of 15)               |            |              | 112m        |          |

|                                       | -2.0<->5.0                                | optimal            | optimal            | 9 (of 15)               |            |              |             |          |

| Controller Board Parameterization Men | -5.0<->6.0                                | optimal            | optimal            | 7 (of 15)               |            |              | 112m        |          |

|                                       | -6.0«->8.0                                | optimal            | optimal            | 6 (of 15)               |            |              | 87m         | POF      |

|                                       |                                           | optimal            | optimal            | 11 (of 15)              | 10 (of 15) | 14           | 150m        |          |

|                                       |                                           | optimal            | optimal            | 7 (of 15)               |            |              | 75m         |          |

| 1                                     | -10.0<->11.0                              | optimal            | optimal            | 8 (of 15)               |            |              | 125m        |          |

| 1.0                                   | -11.0<->12.0                              | optimal            | optimal            | 12 (of 15)              |            |              | 275m        |          |

|                                       | -9.0<->13.0                               | optimal            | optimal            | 10 (of 15)              |            |              | 150m        |          |

| BK                                    |                                           |                    | optimal            | 10 (of 15)<br>6 (of 15) |            |              | 75m<br>62m  |          |

|                                       | -15.0<->16.0                              |                    | optimal            | 3 (of 15)               |            |              |             | POF      |

|                                       | -14.0«->17.0                              |                    | optimal            | 9 (of 15)               |            |              | 75m         | POF      |

|                                       |                                           | optimal            | optimal            | 7 (of 15)               |            |              | 62m         | POF      |

| ID:8 (8h)                             | -18.0<->19.0                              |                    | optimal            | 11 (of 15)              |            |              | 75m         | POF      |

|                                       | -17.0«->20.0                              |                    | optimal            | 7 (of 15)               |            |              | 75m         | POF      |

|                                       |                                           | optimal            | optimal            | 7 (of 15)               | 8 (of 15)  | 9            | 87m         | POF      |

| 2<br>20                               |                                           | optimal            | optimal            | 10 (of 15)              |            |              | 87m         | POF      |

|                                       | -20.0<->24.0                              |                    | optimal            | 9 (of 15)               |            |              | 75m         | POF      |

| BK                                    |                                           | optimal            | optimal            | 8 (of 15)               |            |              | 75m         | POF      |

|                                       | -25.0<->26.0                              |                    | optimal            | 6 (of 15)               |            |              | 75m         | POF      |

|                                       |                                           | optimal            | optimal<br>optimal | 9 (of 15)<br>6 (of 15)  |            |              | 87m<br>75m  | POF      |

|                                       | 28.0<->29.0                               |                    | optimal            | 6 (of 15)               |            |              | 75m<br>87m  | POF      |

| ID:12 (Ch)                            | 29.0 - 29.0 - 30.0                        |                    | optimal            | 11 (of 15)              |            |              | 200m        |          |

|                                       | -30.0<->31.0                              |                    | optimal            | 7 (of 15)               |            |              | 62m         | POF      |

|                                       | -31.0<->32.0                              |                    | optimal            | 6 (of 15)               |            |              | 87m         |          |

| 3 4                                   | 13.6.2001 10.46:20                        |                    |                    |                         |            |              |             |          |

| 3.0 3.1                               | -1.0<->2.0                                | optimal            | optimal            | 11 (of 15)              | 9 (of 15)  | 14           | 150m        |          |

| вк 👼                                  | -2.0<->3.0                                | optimal            | optimal            | 7 (of 15)               |            |              | 75m         |          |

|                                       |                                           | optimal            | optimal            | 3 (of 15)               |            |              | 112m        |          |

|                                       | -2.0<->5.0                                | optimal            | optimal            | 9 (of 15)               |            |              |             |          |

|                                       |                                           | optimal            | optimal            | 8 (of 15)               |            |              | 112m        |          |

| ID:8 (8h) ID:189 (8D                  |                                           | optimal<br>optimal | optimal<br>optimal | 6 (of 15)<br>11 (of 15) |            |              | 87m<br>150m |          |

|                                       | 9.0~>10.0                                 | optimal            | optimal            | 7 (of 15)               |            |              | 75m         |          |

|                                       | 10.0 -11.0                                | optimal            | optimal            | 8 (of 15)               |            |              | 125m        |          |

| 6 7                                   |                                           | optimal            | optimal            | 12 (of 15)              |            |              | 275m        |          |

| 4.0 4.1                               | -9.0<->13.0                               | optimal            | optimal            | 10 (of 15)              |            |              | 150m        |          |

| ВК 👼                                  | Time comme                                | nt:                |                    |                         |            |              |             |          |

|                                       | Path comme                                | nt:                |                    |                         |            |              |             |          |

| -                                     |                                           |                    |                    |                         |            |              |             |          |

| Status: Bus is running                |                                           |                    | State:             | Diagnostic              | s Ext      | ended        |             |          |

Figure 1-10 Optical path diagnostics (e.g., in CMD 4.50)

| Communication Path FL NP PND, Platz<br>View INTERBUS Diagnostic<br>slution   Device Diagnostic   History   Bus Architecture<br>Veference Value |                                              |                                |          | Dis  | connect |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|----------|------|---------|

|                                                                                                                                                |                                              |                                | -        | -    |         |

|                                                                                                                                                | Bus Info Optical Diagnost                    | C Statistic Sett               | ings     |      |         |

| tererence value                                                                                                                                | 1 Northeast Contraction                      |                                | ~ 1      |      |         |

| Time: 23.03.2009 13:51:37                                                                                                                      |                                              |                                | -        |      | Set     |

| Comment:                                                                                                                                       |                                              |                                | •        | D    | elete   |

| Read Current Values                                                                                                                            |                                              | Export                         |          |      |         |

| Path                                                                                                                                           |                                              | →                              | Δ        | +    | Δ       |

| 0 <=> 2.0                                                                                                                                      |                                              | 3                              | (0)      | 3    | (0)     |

| 0 <=> 4.0                                                                                                                                      |                                              | 5                              | (+4)     | 7    | (0)     |

|                                                                                                                                                |                                              |                                |          |      |         |

|                                                                                                                                                |                                              |                                |          |      |         |

|                                                                                                                                                | Current                                      | Refu                           | erence V | alue |         |

| eceiving quality (forward path)<br>eceiving quality (return path)<br>ength<br>ontrol stage (return path)                                       | Current<br>normal<br>norma<br>4 6m<br>5<br>7 | Refr<br>norr<br>norr<br>5<br>7 | nal      | alue |         |

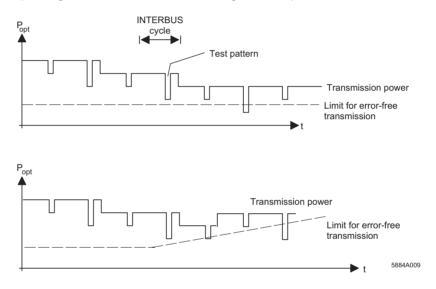

The aim of online regulation is to set the power to a minimum value. At this value transmission with the defined system reserve is ensured. This also applies to short-term modifications in path characteristics with permissible distortions.

Online regulation has 15 power levels. The test over two levels can offer a higher level of system safety because it provides an additional reserve for short-term modifications. The reduction for the second test is one power level higher. The set reduction for the first test corresponds to the system reserve for online regulation.

Online regulation operates as 3-point regulation, i.e, when the minimum permissible transmission power is reached, it remains constant. Transmission power is increased as soon as a negative acknowledgment is received on a reduction of one power level. If a reduction by one power level is acknowledged positively and a reduction by two power levels is acknowledged negatively, the power remains unchanged. If the acknowledgment is positive for both reduction levels, the power is reduced by one level.

Operating behavior can be illustrated using two examples.

Figure 1-12 Example sequence for the transmission power

The upper diagram shows the transmission power sequence with a constant power limit. Once the power limit is reached, the power is constant.

The lower diagram shows the transmission power sequence with a modification to the power limit. The minimum rise time for the transmission power is given by the repeat frequency of the regulation. This largely depends on the number of devices on the bus and corresponds to twice the cycle time. Due to the repeat frequency, the regulation can only compensate for gradual modifications to the path characteristics, e.g., temperature drift and aging effects on the components.

It can be seen that a power increase when transmission quality deteriorates is faster than the power reduction when transmission quality improves.

#### **Optical diagnostics**

Alternatively, the SUPI 3 OPC can be operated with optical power diagnostics. With optical power diagnostics only the characteristics of the transmission medium are tested. The principle for power reduction is only used with a set transmission power to detect the point at which the power reserve falls below the limit. In this case an MAU warning is generated, which is assigned to the incoming interface of the corresponding device.

#### 1.6.3 MAU warnings

There are three active high MAU<sup>1</sup> inputs, however, they are not available as pins to the user (automatic internal detection):

- MAUWH Incoming INTERBUS interface

- MAUWR Outgoing INTERBUS interface

- MAUWS Branch interface (for bus terminal modules only)

The protocol chip can use these inputs to indicate to the master that the transmission quality of, for example, optical paths has fallen to a critical but still operational level. The SUPI 3 OPC is able to evaluate the reception quality of the MAU for the corresponding interface (incoming, outgoing or branch) and to make this available to the appropriate input as a digital signal. Setting this input generates an appropriate message at the bus master. This function is supported by firmware version 4.0.x or later.

During optical power regulation, a critical power reserve, at which transmission is still errorfree but may be with damaged system reserves, is indicated in the MAU warning bits. Basically this means that transmission power cannot be increased any further. An appropriate hysteresis is implemented to ensure that the MAU warning bit does not change constantly at the threshold.

If only one reduced power reserve is available for the online regulation of the highest possible output power, i.e., at "MAX" power level the set reserve is not ensured, the diagnostic status MAU\_WARNING is generated. An appropriate message is triggered on the INTERBUS master by the chip. When the MAU\_WARNING status is activated on the transition of the transmission power MAX-1  $\rightarrow$  MAX and deactivated on the transition MAX-1  $\rightarrow$  MAX-2, a hysteresis occurs which prevents the repeated display of a MAU\_WARNING without the return of the power to the saved operating range.

The current power value is made available by the chip in its registers. In optical power regulation mode the MAU\_WARNING diagnostic status and the MAU\_WARNING\_EVENT diagnostic event are assigned to the transmitting interface. The MAU\_WARNING state is reported to the INTERBUS master by the protocol chip.

<sup>1</sup> Medium Attachment Unit

# 1.7 Basic wiring

# 1.7.1 Clock supply

i

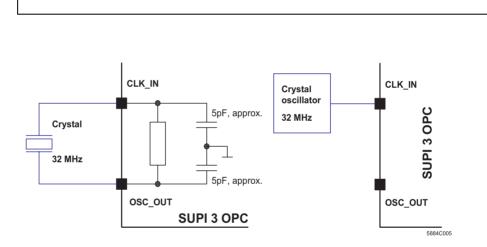

The SUPI 3 OPC/SUPI 3 LS has an internal clock generator. It provides a simple means of implementing the required clock supply. All that is required is a 32 MHz quartz crystal for a quartz oscillator.

The clock signal is generated by the oscillator cell. The clock frequency depends on the frequency of the external quartz crystal. A quartz crystal or a quartz oscillator can be used, as shown in Figure 1-13. A quartz oscillator should be connected to *CLK\_IN*, which acts as a CMOS input buffer. An alternative solution is to directly connect a 32 MHz quartz crystal, without additional external components, to *CLK\_IN* and *OSC\_OUT* (see Table 1-8). The  $\Pi$  filter network required for clock generation is already present in the ASIC.

With this clock no other components can be operated when a quartz crystal is used.

Figure 1-13 Clock supply for the SUPI 3 OPC/SUPI 3 LS

The tolerance of the quartz crystal or the oscillator must not exceed  $f = 32 MHz \pm 100 ppm$ . The following applies for the clock supply: Pulse duty factor: 50% ±10% duty cycles. The permissible deviation applies to both the short-time as well as the long-time stability.

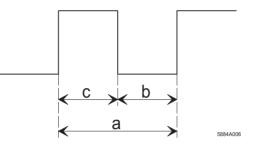

#### Pulse duty factor for the clock supply of INTERBUS protocol chips

Figure 1-14 Pulse duty factor

| Designation | Name                | Symbol          | Min.   | Туре   | Max.   | Unit |

|-------------|---------------------|-----------------|--------|--------|--------|------|

| а           | Clock period        | t <sub>c</sub>  | 31.25  | 31.25  | 31.25  | ns   |

|             |                     |                 | -3.125 |        | +3.125 | ps   |

| b           | Pulse width<br>high | t <sub>pH</sub> | 12.5   | 15.625 | 18.75  | ns   |

| С           | Pulse width low     | t <sub>pL</sub> | 12.5   | 15.625 | 18.75  | ns   |

The clock supply and INTERBUS transmission speed are configured using pins *CLK\_CONF[1..0]*, as shown in the following table.

| Table 1-7 | Configuration of the transmissior | n speed |

|-----------|-----------------------------------|---------|

|           |                                   |         |

| CLK_CONF1 | CLK_CONF0 | Clock source   | Data rate |

|-----------|-----------|----------------|-----------|

| 0         | 1         | Quartz, 32 MHz | 500 kbps  |

| 1         | 1         | Quartz, 32 MHz | 2 Mbps    |

| Х         | 0         | Reserved       |           |

The following table lists suitable quartz crystals and quartz oscillators.

Table 1-8Clock supply components

| Manufacturer      | Туре     | f      | Temperature    |

|-------------------|----------|--------|----------------|

| Quartz            |          |        |                |

| Nippon            | SXN-A    | 32 MHz | -40°C to +85°C |

| Hokuriku          | SX-6B    | 32 MHz | -40°C to +85°C |

| Quartz oscillator |          |        |                |

| Nippon            | NMSOHR   | 32 MHz | -40°C to +85°C |

| Kinseki           | FXO-31FH | 32 MHz | -40°C to +85°C |

|                   | FXO-31FT | 32 MHz | -40°C to +85°C |

| Hokuriku          | KCO-765  | 32 MHz | -40°C to +85°C |

## 1.7.2 Initializing the chip

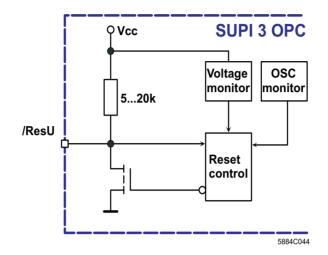

The SUPI 3 OPC/SUPI 3 LS has an internal reset unit (Figure 1-15), which contains a voltage monitor and a clock monitor.

The voltage monitor is directly connected to the ASIC power supply. The internal voltage monitor generates a high signal if the voltage exceeds 4.5 V and a low signal if the voltage falls below 3.9 V. The reset time generated is at least 4  $\mu$ s. If just the internal reset monitor is to be activated, only a 10 k $\Omega$  pull-up needs to be connected at */ResU*.

**NOTE:** The rise time for the supply voltage 0 through +5 V must be less than 100  $\mu$ s, as this could otherwise damage the analog data outputs of the SUPI 3 OPC.

Externally, the active low bidirectional reset pin /*ResU* is brought out. As long as the pin is at a low potential, the internal reset is active. The internal reset only becomes active if the lower voltage threshold is passed **and** the clock supply is stable. The /*ResU* signal can also be used to reset other components with the same potential. The output has a current sink of up to a maximum of 8 mA. Internally, the pin has a pull-up resistor (5 to 20 k $\Omega$ ) and filtering against malfunctions (spikes).

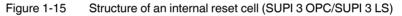

If the reset pin is used as an input, a current of 1 mA is required in the ASIC. In the SUPI 3 OPC/SUPI 3 LS it acts as an "open collector" output stage so that an external voltage monitor must either have an "open collector" output or a resistor for current limitation in the reset path. An application example is given in Figure 1-16.

Figure 1-16 SUPI 3 OPC/SUPI 3 LS with external reset block

# 2 INTERBUS interfaces

# 2.1 Overview

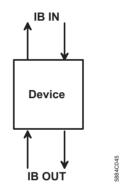

The SUPI 3 OPC chip features three INTERBUS interfaces which can be used simultaneously. They are divided into one incoming and two outgoing interfaces. Each interface has a receive data line and a send data line. In the case of an outgoing interface there is also an alarm input, which indicates the assignment of this interface (RBST\_EXT for the first, LBST (= MFP11) for the second interface).

The SUPI 3 LS chip features two INTERBUS interfaces which can be used simultaneously. They are divided into one incoming and one outgoing interface. Each interface has a receive data line and a send data line. In the case of an outgoing interface there is also an alarm input, which indicates the assignment of this interface (RBST\_EXT).

The interfaces can be set using configuration pins RF[1..0] and C[4..0]. Further details on possible configurations can be found in this section.

INTERBUS interfaces and the application interface for the SUPI 3 OPC are configured using pins C[4..0] and MFP[15..12]. The following operating modes can be set:

| INTERBUS interface                 |  |  |  |  |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|--|--|--|--|

| Remote bus (RB)                    |  |  |  |  |  |  |  |  |  |

| Local bus (LB) with return (MR)    |  |  |  |  |  |  |  |  |  |

| Local bus (LB) without return (OR) |  |  |  |  |  |  |  |  |  |

| MFP interface                      |  |  |  |  |  |  |  |  |  |

| Bus terminal module                |  |  |  |  |  |  |  |  |  |

| Digital I/O                        |  |  |  |  |  |  |  |  |  |

| Serial µP interface                |  |  |  |  |  |  |  |  |  |

| Serial SPI interface               |  |  |  |  |  |  |  |  |  |

| Serial register expansion          |  |  |  |  |  |  |  |  |  |

The Multi-Function Pin interface (*MFP*[15..0]) has 16 bidirectional I/O pins which are statically set to the IN or OUT direction depending on the MFP mode.

The MFP interface is the configurable user interface for the protocol chip. It is set using signals C[4..0]. A detailed overview of possible configurations is given in Section 3, "Application interface".

**NOTE:** MFP pins, which are not assigned any function (no signal) during configuration are connected as **inputs**. They should therefore be connected to GND.

In order to reduce the pins required for the ID code, configurations pins C[4..0] must be mapped internally to the complete 16-bit ID code (see also the SUPI 3 user manual IBS SUPI 3 UM E).

#### 2.1.1 Bus connector recognition and regulation function

The SUPI 3 OPC/SUPI 3 LS supports automatic bus connector recognition (BST). Configuration pins RF[1..0] can be used to set various operating modes. The external input signals RBST ( $RBST\_EXT$ ) and LBST (MPF11) recognized by SUPI 3 are only required in RF[1..0]=10 mode (copper, no automatic recognition). In all other operating modes the interfaces are recognized automatically by internal monitoring, i.e., the control signal required is automatically generated. The setting is made using the signals given in the table.

Table 2-2Bus connector recognition and regulation function

| RF1 | RF0 | RBST_EXT   | Function                                                                                                                                      |

|-----|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0   | Controlled | Bus connector recognition via pin                                                                                                             |

| 1   | 1   | 0          | Automatic bus connector recognition, only copper interface; bit distortion monitoring                                                         |

| 0   | 0   | 0          | Automatic bus connector recognition, regulation<br>function with 3 dB power reserve,<br>fiber optic interface only; bit distortion monitoring |

1

Automatic bus connector recognition (*RF1*=1, *RF0*=1) should always be selected for new copper interface developments.

Automatic bus connector recognition works with all INTERBUS devices that have an INTERBUS protocol chip SUPI 2 or later, when they follow after the SUPI 3 OPC/SUPI 3 LS in the INTERBUS topology.

### 2.1.2 Setting the optical fiber transmitter current

1

Not supported by SUPI 3 LS.

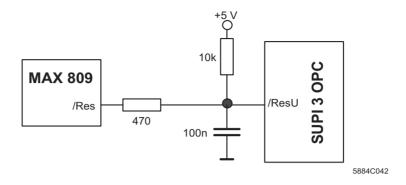

The SUPI 3 OPC can be used to limit or preset all implemented fiber optic transmitters with a reference resistor at pin *CUR\_LIM*. This means that the SUPI 3 OPC can counteract any fiber optic transmission modifications caused by aging and temperature fluctuations using its regulation functions.

The reference resistor can be designed in various forms: For example as a discrete potentiometer, a programmable resistor array, an individual resistor or a resistor network with solder bridges. The reference resistor must have a maximum resistor value of 2.4 K $\Omega$  and a minimum resistor value of 1.2 K $\Omega$ . The voltage at this pin is 1.2 V.

The value to be set is determined during transmitter compensation. The procedure for compensation is detailed in the document "Optical\_Transmission\_Technology\_V2.pdf". This document can be found on the Internet at <a href="http://www.interbusclub.com">www.interbusclub.com</a>.

A suitable increment is required when increasing or decreasing the light output. A compromise must be found between the lowest possible light output increment and low effort on the resistor network. Because the maximum resistor value of 2.4 k $\Omega$  must not be exceeded, 2.4 k $\Omega$  is hard-wired as the first resistor value. All additional resistors for reducing the value are connected in parallel using soldering bridges (LB 1..5).

One possible implementation provides a network with a total of six resistors and a maximum light output increment of 0.3 dB. The resistor values can be found in Table 2-3.

Table 2-3

Resistor values for the reference network to CUR\_LIM

| Resistor | Value          |

|----------|----------------|

| Hesistoi | Value          |

| R1       | <b>2.4 k</b> Ω |

| R2       | <b>3.9 k</b> Ω |

| R3       | <b>7.5 k</b> Ω |

| R4       | <b>15 k</b> Ω  |

| R5       | <b>33 k</b> Ω  |

| R6       | <b>56 k</b> Ω  |

1

With copper applications, a resistor of 1 k $\Omega$  after +5 V should be connected to CUR\_LIM.

# 2.2 Local bus devices

Local bus devices are units within a limited space, which are often supplied with power centrally from a bus terminal module. Several local bus devices can be grouped together to form logical groups. These groups can only be isolated and disconnected from the remote bus as a unit. They differ from remote bus devices in their interface switching behavior. The SUPI 3 OPC/SUPI 3 LS chip divides the local bus operating modes into the number of active interfaces and support of device-oriented local bus diagnostics.

Local bus devices with SUPI 3 OPC or SUPI 3 LS include versions with/without deviceoriented local bus diagnostics. Mixed operation is not permitted. A distinction is also made between devices with (MR; e.g., IBS Inline) and without return (OR; e.g., IBS Loop 2). In the event of an error, devices with device-orientated local bus diagnostics can send diagnostic information to the SUPI 3 OPC of the previous bus terminal module. The INTERBUS master can then retrieve this data.

Figure 2-2 INTERBUS device with two interfaces (MR)

#### 2.2.1 Local bus without device-oriented diagnostics

This operating mode corresponds to the function of the IBS SUPI 3. It is used to implement INTERBUS devices with return (MR). This mode should no longer be used for new developments.

Table 2-4 Local bus operating modes without device-oriented diagnostics

| C4 <sup>*</sup> | C3 | C2 | C1 | C0 |    | M      | FP      |    | Data length <sup>†</sup> | ID code | Function        |

|-----------------|----|----|----|----|----|--------|---------|----|--------------------------|---------|-----------------|

|                 |    |    |    |    | 15 | 14     | 13      | 12 | (ID 128)                 | (Hex)   |                 |

| 0               | 1  | 0  | 0  | 0  |    | See Ta | ble 3-2 |    | 01001                    | BF      | LB-MR, 8 IN/OUT |

| 0               | 1  | 0  | 0  | 1  |    | See Ta | ble 3-2 |    | 00001                    | BE      | LB-MR, 16 IN    |

| 0               | 1  | 0  | 1  | 0  |    | See Ta | ble 3-2 |    | 00001                    | BD      | LB-MR, 16 OUT   |

| 0               | 1  | 0  | 1  | 1  | 0  | 0      | 0       | 0  | 01101                    | BF      | LB-MR, 2 IN/OUT |

| 0               | 1  | 0  | 1  | 1  | 0  | 0      | 0       | 1  | 01101                    | BE      | LB-MR, 2 IN     |

| 0               | 1  | 0  | 1  | 1  | 0  | 0      | 1       | 0  | 01101                    | BD      | LB-MR, 2 OUT    |

| 0               | 1  | 0  | 1  | 1  | 0  | 0      | 1       | 1  | 01000                    | BF      | LB-MR, 4 IN/OUT |

| 0               | 1  | 0  | 1  | 1  | 0  | 1      | 0       | 0  | 01000                    | BE      | LB-MR, 4 IN     |

| 0               | 1  | 0  | 1  | 1  | 0  | 1      | 0       | 1  | 01000                    | BD      | LB-MR, 4 OUT    |

| C4 <sup>*</sup> | C3                                                   | C2 | C1 | C0 |    | M  | FP |    | Data length <sup>†</sup> | ID code | Function             |  |

|-----------------|------------------------------------------------------|----|----|----|----|----|----|----|--------------------------|---------|----------------------|--|

|                 |                                                      |    |    |    | 15 | 14 | 13 | 12 | (ID 128)                 | (Hex)   |                      |  |

| 0               | 1                                                    | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 01001                    | BE      | LB-MR, 8 IN          |  |

| 0               | 1                                                    | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 01001                    | BD      | LB-MR, 8 OUT         |  |

| 0               | 1                                                    | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 00001                    | 7F      | LB-MR, SPI 16 IN/OUT |  |

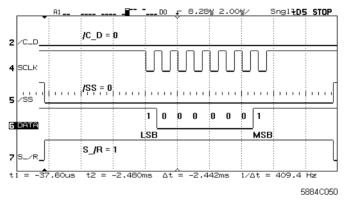

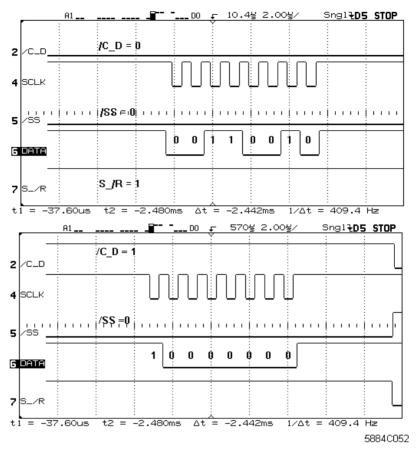

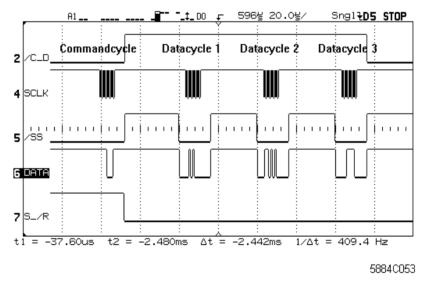

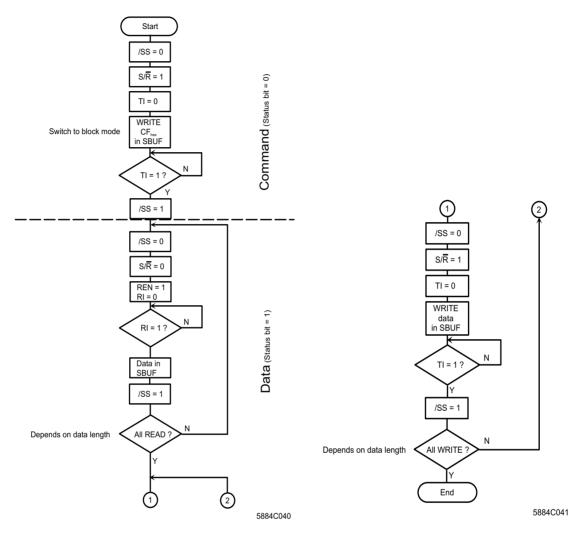

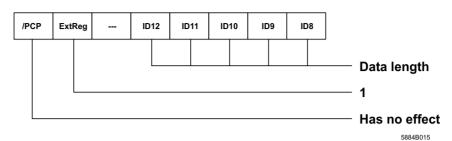

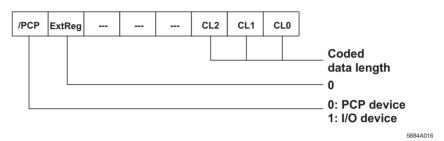

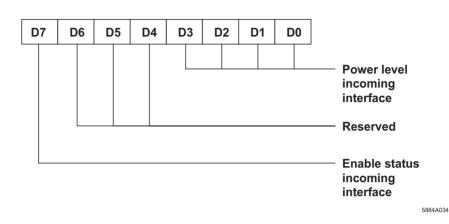

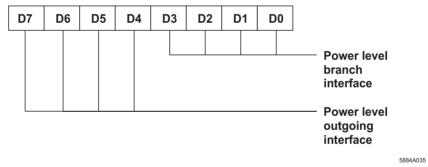

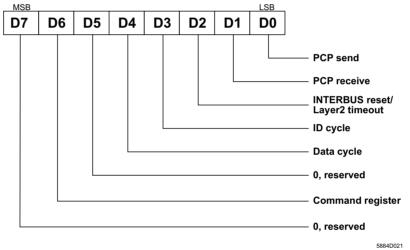

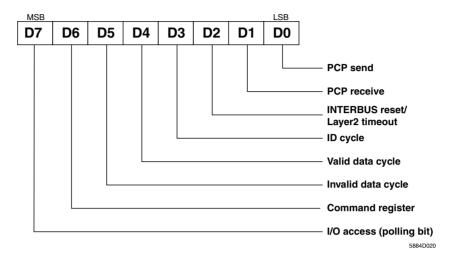

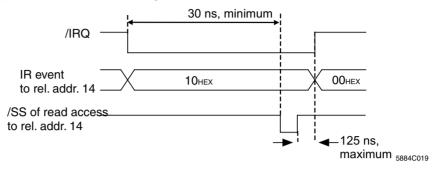

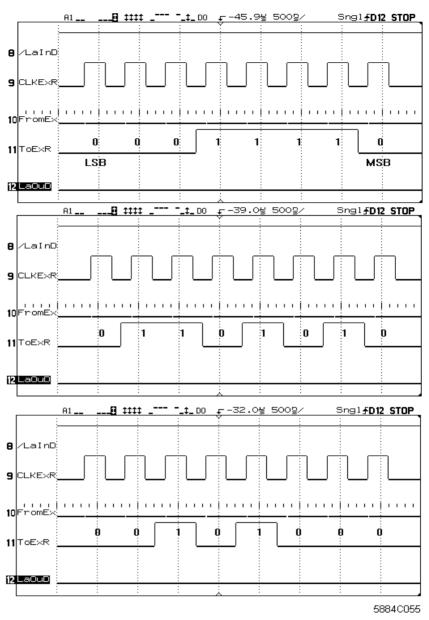

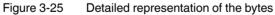

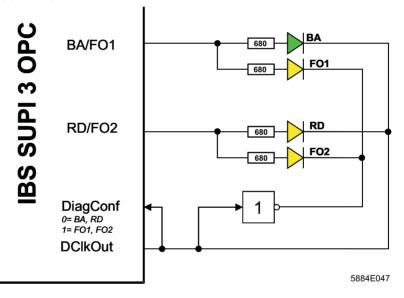

| 0               | 1                                                    | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 00001                    | 7D      | LB-MR, SPI 16 OUT    |  |