# Monolithic Linear IC

http://onsemi.com

## 16ch LED Driver

#### Overview

The LV5232VH is a semiconductor integrated circuit that incorporates a serial input and serial or parallel output 16-stage shift register that features a CMOS structure based on Bi-CMOS process technology. The LV5232VH also contains an n-channel CMOS construction high-withstand-voltage, large-current drive 16-stage parallel output driver. The protection circuit of the output malfunction is built into.

#### **Function**

- Serial input and serial or parallel output

- Enable input for output control

- Serial output enables cascade connection

- Low supply current (30μA typ. during standby ICC≤40μA)

- Serial input/output levels compatible with typical CMOS devices

- High-withstand-voltage LED driver with open drain output

High withstand voltage (VDS < 42V)

High-current drive ( $I_{O} max = 100 mA$ )

- Operating temperature range Ta = -25 to  $75^{\circ}C$

- Output malfunction protection circuit

Reset input pin , V<sub>CC</sub> decrease voltage confirmation

#### **Specifications**

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol              | Conditions          | Ratings     | Unit |

|-----------------------------|---------------------|---------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max | sv <sub>CC</sub>    | 6           | V    |

| Output voltage              | V <sub>O</sub> max  | LEDO1 to LEDO16 off | 42          | V    |

| Output current              | I <sub>O</sub> max  |                     | 100         | mA   |

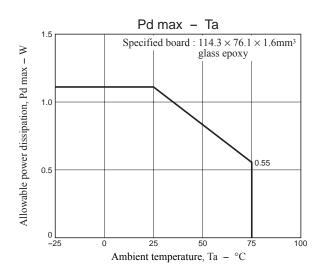

| Allowable power dissipation | Pd max              | Ta ≤ 25°C *         | 1100        | mW   |

| Operating temperature       | Topr                |                     | -25 to +75  | °C   |

| Storage temperature         | Tstg                |                     | -40 to +125 | °C   |

<sup>\*</sup> Specified board : 114.3mm × 76.1mm × 1.6mm, glass epoxy board.

Caution 1) Absolute maximum ratings represent the values which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                      | Symbol             | Conditions        | Ratings    | Unit |

|--------------------------------|--------------------|-------------------|------------|------|

| Recommended supply voltage     | VCC                | sv <sub>CC</sub>  | 5.0        | V    |

| Operating supply voltage range | V <sub>CC</sub> op | sv <sub>CC</sub>  | 3.0 to 5.5 | V    |

| Output applied voltage         | VO                 |                   | 42         | V    |

| Output current                 | I <sub>O</sub>     | Duty = 45% to 55% | 100        | mA   |

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 8 of this data sheet.

## **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 5.0$ V

| Danasatas                                    | Complete and        | One distance              |                      | Unit |                       |      |

|----------------------------------------------|---------------------|---------------------------|----------------------|------|-----------------------|------|

| Parameter                                    | Symbol              | Conditions                | min                  | typ  | max                   | Unit |

| Quiescent current drain                      | I <sub>CC</sub> 1   | LEDO driver off (standby) |                      | 30   | 40                    | μА   |

| LEDO output on resistance                    | Ron                 | I <sub>O</sub> = 30mA     |                      | 5    |                       | Ω    |

| OFF leak current                             | lleak               | V <sub>O</sub> = 42V      |                      | 0    | 10                    | μА   |

| Driver output malfunction prevention voltage | Vt                  |                           | 2.58                 | 2.70 | 2.82                  | V    |

| Control circuit block                        | 1                   |                           |                      |      |                       |      |

| H level 1                                    | V <sub>IN</sub> H1  | Input H level             | $V_{CC} \times 0.8$  |      |                       | V    |

| L level 1                                    | V <sub>IN</sub> L1  | Input L level             | 0                    |      | V <sub>CC</sub> × 0.2 | V    |

| H level 2                                    | V <sub>O</sub> UTH1 | SOUT IO = -1mA            | V <sub>CC</sub> -0.3 |      |                       | ٧    |

| L level 2                                    | V <sub>O</sub> UTL1 | SOUT IO = 1mA             | 0                    |      | 0.3                   | ٧    |

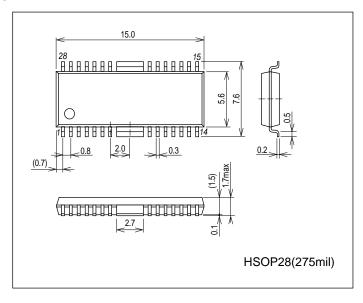

## **Package Dimensions**

unit: mm (typ)

3222A

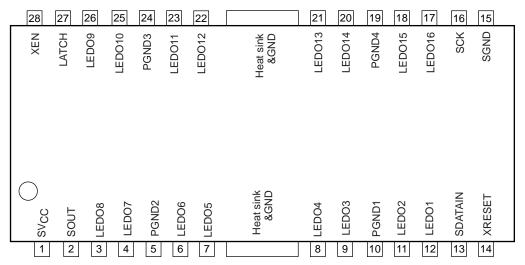

## **Pin Assignment**

Top view

## **Pin Descriptions**

| Pin No.   | Pin name         | I/O | Description                                                                                                                                                                           |

|-----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | sv <sub>cc</sub> |     | Power supply                                                                                                                                                                          |

| 2         | SOUT             | 0   | shift register output (final-stage shift register)                                                                                                                                    |

| 3         | LEDO8            | 0   | LEDO8 Latch output (LEDO8 of shift register)                                                                                                                                          |

| 4         | LEDO7            | 0   | LEDO7 Latch output (LEDO7 of shift register)                                                                                                                                          |

| 5         | PGND2            |     | GND                                                                                                                                                                                   |

| 6         | LEDO6            | 0   | LEDO6 Latch output (LEDO6 of shift register)                                                                                                                                          |

| 7         | LEDO5            | 0   | LEDO5 Latch output (LEDO5 of shift register)                                                                                                                                          |

| Heat sink |                  |     |                                                                                                                                                                                       |

| 8         | LEDO4            | 0   | LEDO4 Latch output (LEDO4 of shift register)                                                                                                                                          |

| 9         | LEDO3            | 0   | LEDO3 Latch output (LEDO3 of shift register)                                                                                                                                          |

| 10        | PGND1            |     | GND                                                                                                                                                                                   |

| 11        | LEDO2            | 0   | LEDO2 Latch output (LEDO2 of shift register)                                                                                                                                          |

| 12        | LEDO1            | 0   | LEDO1 Latch output (LEDO1 of shift register)                                                                                                                                          |

| 13        | SDATAIN          | 1   | Serial Input                                                                                                                                                                          |

| 14        | XRESET           | I   | Reset input (shift register and latch)                                                                                                                                                |

| 15        | SGND             |     | GND                                                                                                                                                                                   |

| 16        | SCK              | I   | Clock input (for shift register)                                                                                                                                                      |

| 17        | LEDO16           | 0   | LEDO16 Latch output (LEDO16 of shift register)                                                                                                                                        |

| 18        | LEDO15           | 0   | LEDO15 Latch output (LEDO15 of shift register)                                                                                                                                        |

| 19        | PGND4            |     | GND                                                                                                                                                                                   |

| 20        | LEDO14           | 0   | LEDO14 Latch output (LEDO14 of shift register)                                                                                                                                        |

| 21        | LEDO13           | 0   | LEDO13 Latch output (LEDO13 of shift register)                                                                                                                                        |

| Heat sink |                  |     |                                                                                                                                                                                       |

| 22        | LEDO12           | 0   | LEDO12 Latch output (LEDO12 of shift register)                                                                                                                                        |

| 23        | LEDO11           | 0   | LEDO11 Latch output (LEDO11 of shift register)                                                                                                                                        |

| 24        | PGND3            |     | GND                                                                                                                                                                                   |

| 25        | PGND10           | 0   | LEDO10 Latch output (LEDO10 of shift register)                                                                                                                                        |

| 26        | PGND9            | 0   | LEDO9 Latch output (LEDO9 of shift register)                                                                                                                                          |

| 27        | LATCH            | I   | Latch input  When the latch input is held low, the LED0 output status is retained.  When a high-level is input, the LED0 outputs change when the status of the shift register changes |

| 28        | XEN              | I   | Enable inputs (LEDO1 to LEDO16)  When a high-level is input, all the LED0 outputs are turned off.  When a low-level is input, the shift register data is output to LED0.              |

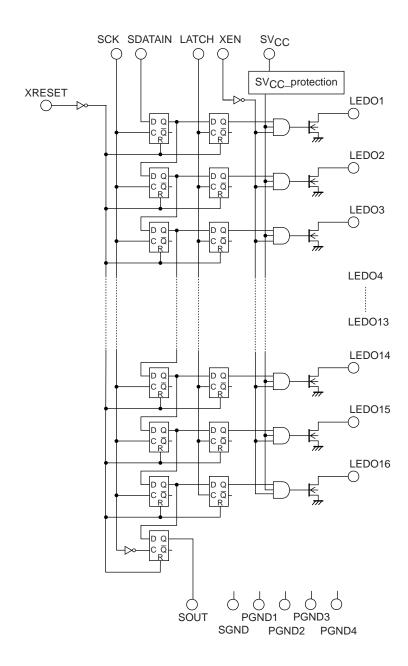

#### **Block Diagram**

#### **Function**

The LV5232VH consists of 1) an 16-stage D-type flip-flop and 2) an 16-stage D-type flip-flop connected to the output of 1). When data is supplied to the serial data input (SDATAIN) and the clock pulse is supplied to the clock input (SCK), the serial data input signal is input to the internal shift register and the data already in the shift register shifted sequentially when the clock changes from low to high.

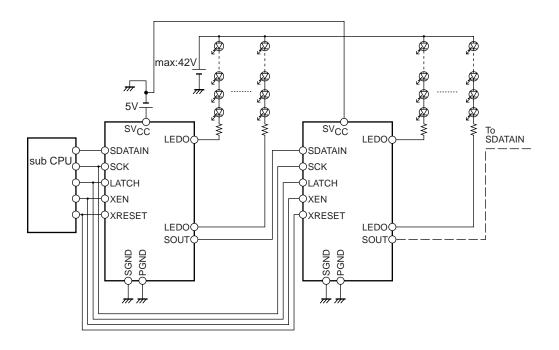

The serial output (SOUT) is used to connect multiple LV5232VH to expand the number of bits and is connected to the SDATAIN of the next stage. (Cascade connection supported.)

For parallel output, when the output control enable input (XEN) is low, the latch input (LATCH) changes from low to high and the clock pulse input changes from low to high, the serial data input signal is output to LEDO1, and the output is shifted sequentially. For parallel outputs (LEDO2 to LEDO16), the signals whose polarities inverted from those of the serial data input (SDATAIN) are output.

When the EN input is high, outputs LEDO1 through LEDO16 all turn off.

When the reset input is low, outputs LEDO1 through LEDO16 and SOUT outputs all turn off. The power must be turned on after checking that the reset input is low.

To prevent the malfunction, the output load protection circuit is built into. The output of LEDO1 to LEDO16 is compulsorily turned off when becoming below the voltage with a constant there is  $V_{CC}$ .

#### **Pin Functions**

| Pin No.                                                                                | Pin Name                                                                                               | Pin function                 | Equivalent Circuit |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------|--------------------|

| 13<br>16                                                                               | SDATAIN<br>SCK                                                                                         | Pull-down input              | SGND               |

| 14<br>27<br>28                                                                         | XRESET<br>LATCH<br>XEN                                                                                 | Pull-up input                | SGND               |

| 2                                                                                      | SOUT                                                                                                   | SOUT output                  | SVCC               |

| 3<br>4<br>6<br>7<br>8<br>9<br>11<br>12<br>17<br>18<br>20<br>21<br>22<br>23<br>25<br>26 | LEDO8 LEDO7 LEDO6 LEDO5 LEDO4 LEDO3 LEDO2 LEDO1 LEDO16 LEDO15 LEDO14 LEDO13 LEDO12 LEDO11 LEDO10 LEDO9 | LEDO outputs LEDO1 to LEDO16 | SVCC<br>SGND PGND  |

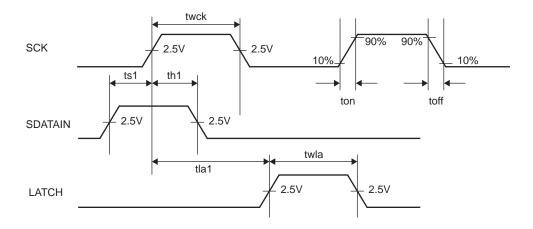

## **Timing conditions**

| Parameter          | symbol | Conditions                                         | min | typ | max | unit |

|--------------------|--------|----------------------------------------------------|-----|-----|-----|------|

| Clock frequency    | fs1    | SCK Duty = 50%                                     |     |     | 10  | MHz  |

| Clock pulse width  | twck   | SCK                                                | 50  |     |     | ns   |

| Latch pulse width  | twla   | LATCH                                              | 50  |     |     | ns   |

| Data set up time   | ts1    | SDATAIN setup time relative to the rise of SCK     | 25  |     |     | ns   |

| Data hold time     | th1    | SDATAIN data hold time relative to the rise of SCK | 25  |     |     | ns   |

| Clock latch time   | tla1   |                                                    | 100 |     |     | ns   |

| Input conditions 1 | ton    | SCK and SDATAIN rise time                          |     |     | 100 | ns   |

| Input conditions 2 | toff   | SCL and SDATAIN fall time                          |     |     | 100 | ns   |

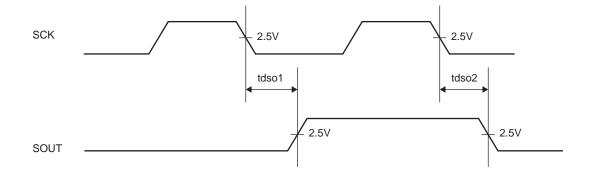

## **SOUT output timings**

| Parameter         | symbol | Conditions                                            | min | typ | max | unit |

|-------------------|--------|-------------------------------------------------------|-----|-----|-----|------|

| SOUT delay time 1 | tdso1  | The time from a SCK falling edge to SOUT rising edge  |     |     | 50  | MHz  |

| SOUT delay time 2 | tdso2  | The time from a SCK falling edge to SOUT falling edge |     |     | 50  | ns   |

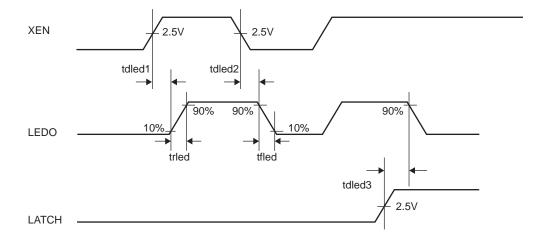

#### **LEDO** output timings

| Parameter         | symbol | Conditions                                                                                               | min | typ | max | unit |

|-------------------|--------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| LEDO delay time 1 | tdled1 | The time from an XEN rising edge to LEDO rising edge $CL = 30pF$ , $I_O = 100mA$ , $V_O = 42V$           |     | 100 |     | ns   |

| LEDO delay time 2 | tdled2 | The time from an XEN falling edge to LEDO falling edge CL = 30pF, $I_O$ = 100mA, $V_O$ = 42V             |     | 100 |     | ns   |

| LEDO rise time    | trled  | LEDO rise time $CL = 30pF$ , $I_O = 100mA$ , $V_O = 42V$                                                 |     | 200 |     | ns   |

| LEDO fall time    | tfled  | LEDO fall time<br>CL = 30pF, $I_O$ = 100mA, $V_O$ = 42V                                                  |     | 200 |     | ns   |

| LEDO delay time 3 | tdled3 | The time from a LATCH rising edge to LEDO falling edge CL = 30pF, $I_{\rm O}$ = 100mA, $V_{\rm O}$ = 42V |     | 200 |     | ns   |

## **Application Circuit Example**

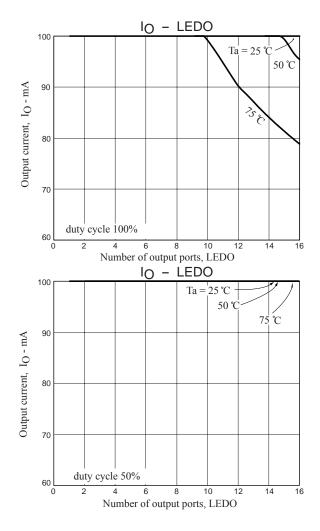

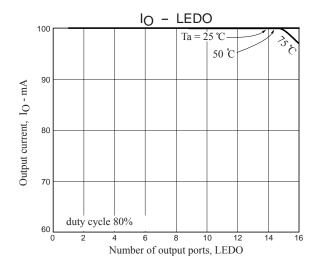

## Temperature properties graph

#### **ORDERING INFORMATION**

| Device          | Package                                     | Shipping (Qty / Packing) |

|-----------------|---------------------------------------------|--------------------------|

| LV5232VH-TLM-H  | HSOP28 (275mil)<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |

| LV5232VHZ-TLM-H | HSOP28 (275mil)<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |

| LV5232VH-MPB-H  | HSOP28 (275mil)<br>(Pb-Free / Halogen Free) | 30 / Fan-Fold            |

| LV5232VHZ-MPB-H | HSOP28 (275mil)<br>(Pb-Free / Halogen Free) | 30 / Fan-Fold            |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa