# 5.0 V, 500 mA Linear Regulator with ENABLE, RESET, and Watchdog

The CS8140 and CS8141 are linear regulators suited for microprocessor applications in automotive environments.

These ON Semiconductor parts provide the power for the microprocessors along with many of the control functions needed in today's computer based systems. Incorporating all of these features saves both cost, and board space.

Packages are available for surface mounting as well as through hole mounting.

The CS8141 has the same feature set as the CS8140 with the exception of the response to the watchdog signals (WDI). The CS8141 only responds to input signals (WDI) which are below the preset watchdog frequency threshold.

## Features

- 5.0 V ±4.0%, 500 mA Output Voltage

- µP Compatible Control Functions

- Watchdog

- RESET

- ENABLE

- Low Dropout Voltage (1.25 V @ 500 mA)

- Low Quiescent Current (7.0 mA @ 500 mA)

- Low Noise, Low Drift

- Low Current SLEEP Mode ( $I_Q = 250 \mu A$ )

- Fault Protection

- Thermal Shutdown

- Short Circuit

- 60 V Peak Transient Voltage

# **ON Semiconductor®**

http://onsemi.com

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.

#### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 14 of this data sheet.

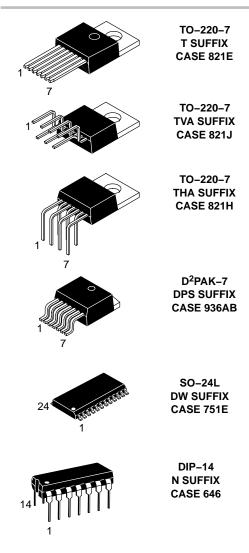

## **PIN CONNECTIONS**

## **MAXIMUM RATINGS\***

| Rating                                                                                                                          |                                                                                    | Value                   | Unit         |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------|--------------|

| Input Operating Range                                                                                                           |                                                                                    | -0.5 to 26              | V            |

| Peak Transient Voltage (46 V Load Dump @ 14 V V <sub>BAT</sub> )                                                                |                                                                                    | 60                      | V            |

| Electrostatic Discharge (Human Body Model)                                                                                      |                                                                                    | 4.0                     | kV           |

| WDI Input Signal Range                                                                                                          |                                                                                    | -0.3 to 7.0             | V            |

| Internal Power Dissipation                                                                                                      |                                                                                    | Internally Limited      | -            |

| Junction Temperature Range (T <sub>J</sub> )                                                                                    |                                                                                    | -40 to +150             | °C           |

| Storage Temperature Range                                                                                                       |                                                                                    | -65 to +150             | °C           |

| ENABLE                                                                                                                          |                                                                                    | –0.3 to V <sub>IN</sub> | V            |

| Package Thermal Resistance, TO–220–7<br>Junction–to–Case, R <sub>θJC</sub><br>Junction–to–Ambient, R <sub>θJA</sub>             |                                                                                    | 1.6<br>50               | °C/W<br>°C/W |

| Package Thermal Resistance, D <sup>2</sup> PAK–7<br>Junction–to–Case, R <sub>θJC</sub><br>Junction–to–Ambient, R <sub>θJA</sub> |                                                                                    | 1.5<br>10–50†           | °C/W<br>°C/W |

| Package Thermal Resistance, SO–24L Junction–to–Case, $R_{\theta JC}$ Junction–to–Ambient, $R_{\theta JA}$                       |                                                                                    | 16<br>80                | °C/W<br>°C/W |

| Package Thermal Resistance, DIP–14<br>Junction–to–Case, $R_{\theta JC}$<br>Junction–to–Ambient, $R_{\theta JA}$                 |                                                                                    | 48<br>85                | °C/W<br>°C/W |

| Lead Temperature Soldering: Way                                                                                                 | ve Solder (through hole styles only) (Note 1)<br>Reflow (SMD styles only) (Note 2) | 260 peak<br>230 peak    | °C           |

\*The maximum package power dissipation must be observed.

†Depending on thermal properties of substrate  $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$ .

1. 10 second maximum.

2. 60 seconds max above 183°C.

# $\label{eq:electrical characteristics} \textbf{ELECTRICAL CHARACTERISTICS} \quad (7.0 \leq V_{IN} \leq 26 \text{ V}, \ 5.0 \text{ mA} \leq I_{OUT} \leq 500 \text{ mA}, \ -40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}, \ 10^{\circ}\text{C} \leq 10^{\circ}\text{C}, \ 10^{\circ}\text{C} \approx 10^{\circ}\text{C} \approx 10^{\circ}\text{C}, \ 10^{\circ}\text{C} \approx 10^{\circ$

–40°C  $\leq$  T\_A  $\leq$  125°C, unless otherwise noted.) Note 3.

| Characteristic                                                    | Test Conditions                                                                                                   | Min | Тур         | Max        | Unit     |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|------------|----------|

| Output Stage (V <sub>OUT</sub> )                                  |                                                                                                                   |     |             |            |          |

| Output Voltage, V <sub>OUT</sub>                                  | 7.0 V $\leq$ V $_{IN}$ $\leq$ 26 V, 5.0 mA < I $_{OUT}$ < 500 mA                                                  | 4.8 | 5.0         | 5.2        | V        |

| Dropout Voltage (V <sub>IN</sub> – V <sub>OUT</sub> )             | I <sub>OUT</sub> = 500 mA                                                                                         | -   | 1.25        | 1.50       | V        |

| Line Regulation                                                   | $I_{OUT} = 50 \text{ mA}, 7.0 \text{ V} \leq \text{V}_{\text{IN}} \leq 26 \text{ V},$                             | -   | 5.0         | 25         | mV       |

| Load Regulation                                                   | $V_{IN}$ = 14 V, 50 mA $\leq I_{OUT} \leq$ 500 mA                                                                 | -   | 5.0         | 80         | mV       |

| Output Impedance, R <sub>OUT</sub>                                | 500 mA DC and 10 mA AC, 100 Hz $\leq$ f $\leq$ 10 kHz                                                             | -   | 200         | -          | mΩ       |

| Quiescent Current, (I <sub>Q</sub> )<br>Active Mode<br>Sleep Mode | $0 \le I_{OUT} \le 500$ mA, 7.0 V $\le V_{IN} \le 26$ V<br>$I_{OUT} = 0$ mA, V <sub>IN</sub> = 13 V, ENABLE = 0 V |     | 7.0<br>0.25 | 15<br>0.50 | mA<br>mA |

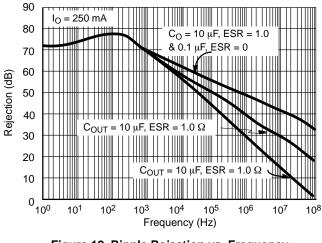

| Ripple Rejection                                                  | 7.0 V $\leq$ V $_{IN}$ $\leq$ 17 V, I $_{OUT}$ = 250 mA, f = 120 Hz                                               | 60  | 75          | -          | dB       |

| Current Limit                                                     | _                                                                                                                 | 700 | 1200        | 2000       | mA       |

| Thermal Shutdown                                                  | -                                                                                                                 | 150 | 180         | -          | °C       |

| Overvoltage Shutdown                                              | V <sub>OUT</sub> < 1.0 V                                                                                          | 30  | 34          | 38         | V        |

3. To observe safe operating junction temperatures, low duty cycle pulse testing is used in tests where applicable.

# $\textbf{ELECTRICAL CHARACTERISTICS (continued)} (7.0 \leq V_{\text{IN}} \leq 26 \text{ V}, 5.0 \text{ mA} \leq I_{\text{OUT}} \leq 500 \text{ mA}, -40^{\circ}\text{C} \leq T_{\text{J}} \leq 150^{\circ}\text{C}, \text{ massless} = 100^{\circ}\text{C} \text{ m}, 1$

| $-40^{\circ}C \le T_A \le 125^{\circ}C$ , unless otherwise | e noted.) Note 4. |

|------------------------------------------------------------|-------------------|

|------------------------------------------------------------|-------------------|

| Characteristic                            | Test Conditions                                                                                                                                          | Min      | Тур          | Max                     | Unit   |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-------------------------|--------|

| ENABLE                                    | · · · · · · · · · · · · · · · · · · ·                                                                                                                    |          |              |                         |        |

| Threshold<br>HIGH<br>LOW                  | $\label{eq:Vout} \begin{split} V_{OUT} &\geq 0.5 \text{ V}, \left(V_{OUT(ON)}\right) \\ V_{OUT} &< 0.5 \text{ V}, \left(V_{OUT(OFF)}\right) \end{split}$ | _<br>3.5 | 4.05<br>3.95 | 4.50                    | V<br>V |

| Threshold Hysteresis                      | (HIGH – LOW)                                                                                                                                             | -        | 100          | -                       | mV     |

| RESET                                     | · · · ·                                                                                                                                                  |          |              |                         |        |

| Threshold HIGH V <sub>R(HI)</sub>         | V <sub>OUT</sub> Increasing                                                                                                                              | 4.65     | 4.90         | V <sub>OUT</sub> – 0.05 | V      |

| Threshold LOW V <sub>R(LOW)</sub>         | N) V <sub>OUT</sub> Decreasing                                                                                                                           |          | 4.70         | 4.90                    | V      |

| Threshold Hysteresis (V <sub>RH</sub> )   | (HIGH – LOW)                                                                                                                                             | 150      | 200          | 250                     | mV     |

| RESET Output Leakage<br>RESET = HIGH      | $V_{OUT} \ge V_{R(HI)}$                                                                                                                                  | -        | -            | 25                      | μΑ     |

| Output Voltage Low (V <sub>L(LOW)</sub> ) | 1.0 V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>R(LOW)</sub> , R <sub>P</sub> = 2.7 kΩ, Note 5.                                                              | -        | 0.1          | 0.4                     | V      |

| Output Voltage Low (V <sub>Rpeak</sub> )  | V <sub>OUT</sub> , Power up, Power down                                                                                                                  | -        | 0.6          | 1.0                     | V      |

| Delay Times t <sub>POR</sub>              | C <sub>DELAY</sub> = 0.1 μF                                                                                                                              | 30       | 47.5         | 65                      | ms     |

| Delay Times t <sub>WDI(RESET)</sub>       | C <sub>DELAY</sub> = 0.1 μF                                                                                                                              | 0.5      | 1.0          | 1.5                     | ms     |

| Watchdog                                  |                                                                                                                                                          |          |              |                         |        |

| Input Voltage High                        | -                                                                                                                                                        | 2.0      | -            | -                       | V      |

| Input Voltage Low                         | -                                                                                                                                                        | -        | -            | 0.8                     | V      |

| Input Current                             | $WDI \leq V_{OUT}$                                                                                                                                       | -        | 0            | 10                      | μA     |

| Input Current                                            | $WDI \le V_{OUT}$         | -   | 0   | 10  | μΑ |

|----------------------------------------------------------|---------------------------|-----|-----|-----|----|

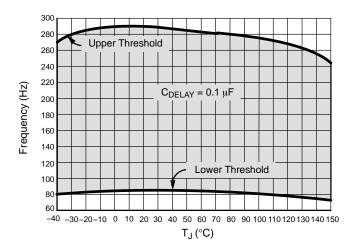

| Threshold Frequency f <sub>WDI(LOWER)</sub>              | $C_{DELAY} = 0.1 \ \mu F$ | 64  | 77  | 96  | Hz |

| Threshold Frequency f <sub>WDI(UPPER)</sub><br>(Note 6.) | $C_{DELAY} = 0.1 \ \mu F$ | 218 | 262 | 326 | Hz |

To observe safe operating junction temperatures, low duty cycle pulse testing is used in tests where applicable.

R<sub>P</sub> is connected to RESET and V<sub>OUT</sub>.

CS8140 only.

# PACKAGE LEAD DESCRIPTION

|          | PACKAG               | E LEAD #              |            | LEAD SYMBOL      |                                                                                                                                                                                      |

|----------|----------------------|-----------------------|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO-220-7 | D <sup>2</sup> PAK-7 | SO-24L                | DIP-14     | LEAD SYMBOL      | FUNCTION                                                                                                                                                                             |

| 1        | 1                    | 21                    | 12         | V <sub>IN</sub>  | Supply voltage to IC, usually direct from the battery.                                                                                                                               |

| 2        | 2                    | 23                    | 13         | ENABLE           | CMOS compatible logical input. V <sub>OUT</sub> is disabled when ENABLE is LOW and WDI is beyond its preset limits.                                                                  |

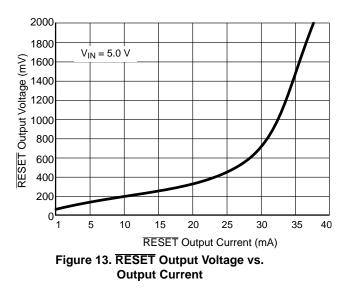

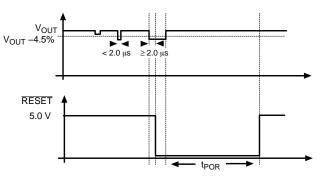

| 3        | 3                    | 24                    | 14         | RESET            | CMOS compatible output lead. RESET goes low whenever $V_{OUT}$ drops below 4.5% of it's typical value for more than 2.0 $\mu$ s or WDI signal falls outside it's window limits.      |

| 4        | 4                    | 12, 20                | 8, 11      | GND              | Ground Connection.                                                                                                                                                                   |

| 5        | 5                    | 2                     | 1          | Delay            | Timing capacitor for Watchdog and RESET functions.                                                                                                                                   |

| 6        | 6                    | 3                     | 2          | WDI              | CMOS compatible input lead. The Watchdog function monitors<br>the falling edge of the incoming digital pulse train. The signal is<br>usually generated by the system microprocessor. |

| 7        | 7                    | 4                     | 3          | V <sub>OUT</sub> | Regulated output voltage, 5.0 V (Typ).                                                                                                                                               |

| -        | -                    | 1, 6–11,<br>13–19, 22 | 5–7, 9, 10 | NC               | No connection.                                                                                                                                                                       |

| -        | -                    | 5                     | 4          | Sense            | Kelvin connection which allows remote sensing of output volt-<br>age for improved regulation.                                                                                        |

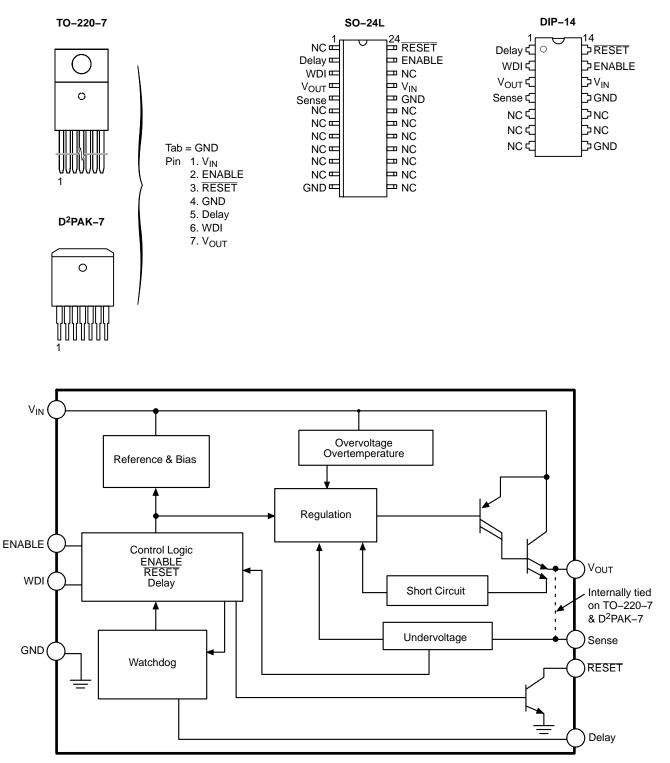

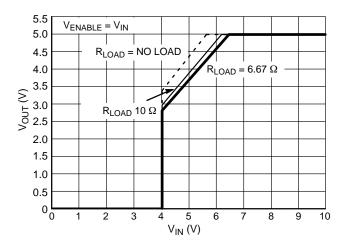

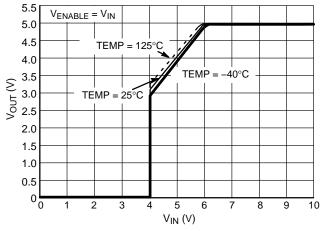

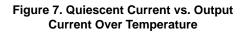

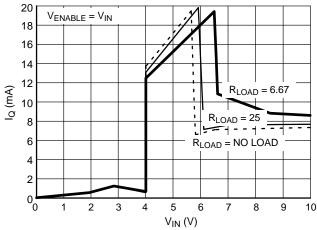

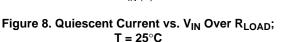

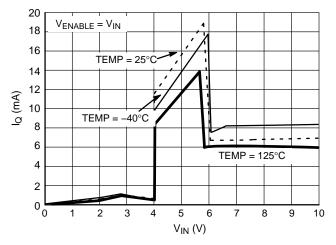

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. V<sub>OUT</sub> vs. V<sub>IN</sub> Over Temperature; R<sub>LOAD</sub> = 25  $\Omega$

Figure 2. V<sub>OUT</sub> vs. V<sub>IN</sub> over R<sub>LOAD</sub>; T = 25°C

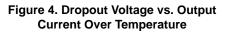

Figure 6. Line Regulation vs. Output Current Over Temperature

3.5 -40°C 0 25°C -3.5 -7  $V_{IN} = 14 V$ -10.5 -14 -17.5 -21 125°C -24.5 -28 -31.5 -35 0 100 300 400 500 200 600 700 800 I<sub>OUT</sub> (mV)

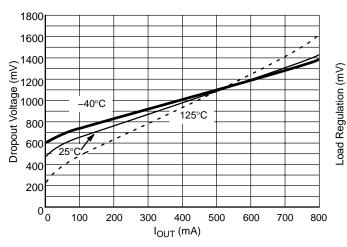

Figure 5. Load Regulation vs. Output Current Over Temperature

# **TYPICAL PERFORMANCE CHARACTERISTICS**

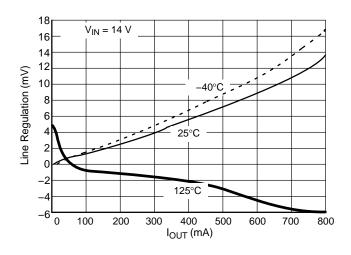

Figure 9. Quiescent Current vs. V<sub>IN</sub> Over Temperature; R<sub>LOAD</sub> = 25  $\Omega$

107 106 105 WDI Threshold Upper Threshold 104 10<sup>3</sup> Lower Threshold 10<sup>2</sup> 101 H Т 100 101 10<sup>2</sup> 10<sup>3</sup> 104 10<sup>5</sup> 10<sup>6</sup> 1( Capacitance (pF)

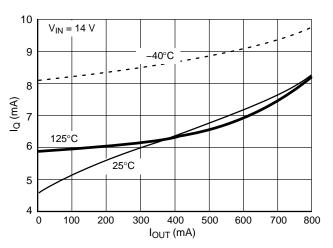

Figure 11. Watchdog Frequency Threshold vs. C<sub>DELAY</sub>

#### **DEFINITION OF TERMS**

affected.

output.

**Dropout Voltage:** The input–output voltage differential at which the circuit ceases to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100 mV from the nominal value obtained at 14 V input, dropout voltage is dependent upon load current and junction temperature.

**Input Voltage:** The DC voltage applied to the input terminals with respect to ground.

**Line Regulation:** The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques

#### **CIRCUIT DESCRIPTION**

1 VOLTAGE REFERENCE AND OUTPUT CIRCUITRY

regulator ground lead current.

### Precision Voltage Reference

The regulated output voltage depends on the precision band gap voltage reference in the IC. By adding an error amplifier into the feedback loop, the output voltage is maintained within  $\pm 4.0\%$  over temperature and supply variation.

such that the average chip temperature is not significantly

Load Regulation: The change in output voltage for a

Quiescent Current: The part of the positive input current

**Ripple Rejection:** The ratio of the peak-to-peak input

ripple voltage to the peak–to–peak output ripple voltage. **Current Limit:** Peak current that can be delivered to the

that does not contribute to the positive load current. The

change in load current at constant chip temperature.

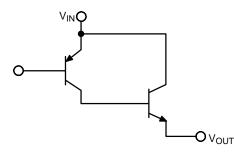

#### **Output Stage**

The composite PNP–NPN output structure (Figure 14) provides 500 mA (min) of output current while maintaining a low drop out voltage (1.25 V) and drawing little quiescent current (7.0 mA).

Figure 14. Composite Output Stage of the CS8140/1

The NPN pass device prevents deep saturation of the output stage which in turn improves the IC's efficiency by preventing excess current from being used and dissipated by the IC.

#### **Output Stage Protection**

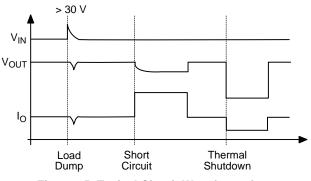

The output stage is protected against overvoltage, short circuit and thermal runaway conditions (Figure 15).

If the input voltage rises above 30 V (e.g. load dump), the output shuts down. This response protects the internal circuitry and enables the IC to survive unexpected voltage transients.

Using an emitter sense scheme, the amount of current through the NPN pass transistor is monitored. Feedback

The CS8140 is a 5.0 V Watchdog Regulator with protection circuitry and three logic control functions that allow a microprocessor to control its own power supply. The CS8140 is designed for use in automotive, switch mode power supply post regulator, and battery powered systems.

Basic regulator performance characteristics include a low noise, low drift, 5.0 V  $\pm$ 4.0% precision output voltage with low dropout voltage (1.25 V @ I<sub>OUT</sub> = 500 mA) and low quiescent current (7.0 mA @ I<sub>OUT</sub> = 500 mA). On board short circuit, thermal, and overvoltage protection make it possible to use this regulator in particularly harsh operating environments.

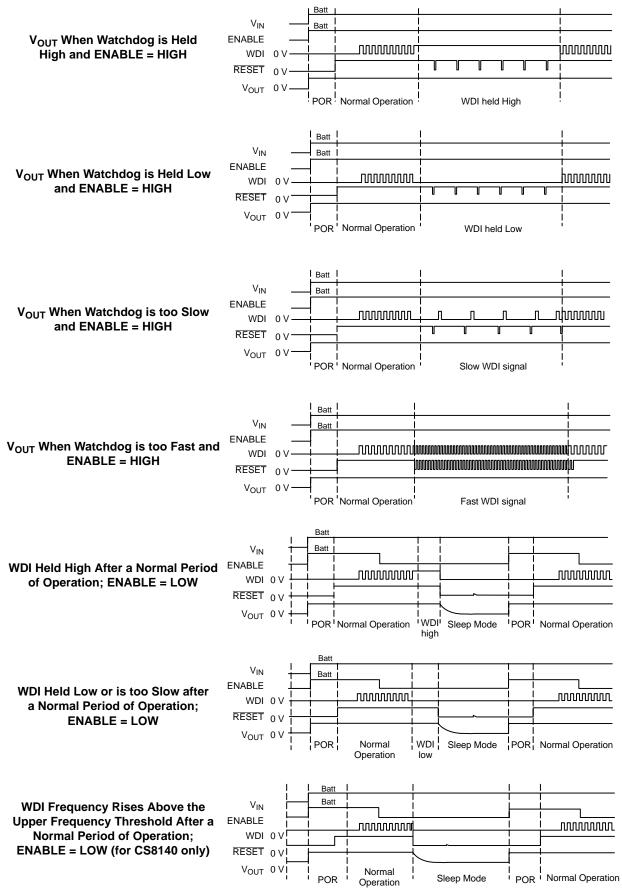

The Watchdog logic function monitors an input signal (WDI) from the microprocessor or other signal source. When the signal frequency moves outside externally programmable window limits, a  $\overline{\text{RESET}}$  signal is generated ( $\overline{\text{RESET}}$ ). An external capacitor ( $C_{\text{DELAY}}$ ) programs the watchdog window frequency limits as well as the power on reset (POR) and  $\overline{\text{RESET}}$  delay.

The RESET function is activated by any of three conditions: the watchdog signal moves outside of its preset limits; the output voltage drops out of regulation by more than 4.5%; or the IC is in its power up sequence. The RESET signal is independent of  $V_{IN}$  and reliable down to  $V_{OUT} = 1.0$  V.

In conjunction with the Watchdog, the ENABLE function controls the regulator's power consumption. The CS8140's output stage and its attendant circuitry are enabled by setting the ENABLE lead high. The regulator goes into sleep mode when the ENABLE lead goes low and the watchdog signal moves outside its preset window limits. This unique combination of control functions in the CS8140 gives the microprocessor control over its own power down sequence: i.e. it gives the microprocessor the flexibility to perform housekeeping functions before it powers down.

The CS8141 has the same features as the CS8140, except that the CS8141 only responds to input signals (WDI) which are below the preset watchdog frequency threshold.

circuitry insures that the output current never exceeds a preset limit.

Figure 15. Typical Circuit Waveforms for Output Stage Protection

Should the junction temperature of the power device exceed 180°C (Typ), the power transistor is turned off. Thermal shutdown is an effective means to prevent die overheating since the power transistor is the principle heat source in the IC.

#### **REGULATOR CONTROL FUNCTIONS**

The CS8140 differs from all other linear regulators in its unique combination of control features.

#### Watchdog and ENABLE Function

V<sub>OUT</sub> is controlled by the logic functions ENABLE and Watchdog (Table 1).

| Table 1. | Table 1. V <sub>OUT</sub> as a Function of ENABLE and Watchdog |  |  |  |  |

|----------|----------------------------------------------------------------|--|--|--|--|

|          | V <sub>OUT</sub> (V)                                           |  |  |  |  |

|          | WDI                                                            |  |  |  |  |

|        | WDI  |        |      |      |     |

|--------|------|--------|------|------|-----|

| ENABLE | Slow | Normal | Fast | High | Low |

| Н      | 5    | 5      | 5    | 5    | 5   |

| L      | 0    | 5      | 0    | 0    | 0   |

|        |      |        |      |      |     |

As long as ENABLE is high or ENABLE is low and the Watchdog signal is normal,  $V_{OUT}$  will be at 5.0 V (Typ). If ENABLE is low and the Watchdog signal moves outside programmable limits, the output transistor turns off and the IC goes into SLEEP mode. Only the ENABLE circuitry in the IC remains powered up, drawing a quiescent current of 250  $\mu$ A.

The Watchdog monitors the frequency of an incoming WDI signal. If the signal falls outside of the WDI window, a frequency programmable pulse train is generated at the **RESET** lead (Figure 16) until the correct Watchdog input signal reappears at the lead (ENABLE = HIGH).

The lower and upper window threshold limits of the watchdog function are set by the value of  $C_{DELAY}$ . The limits are determined according to the following equations for the CS8140:

(a)  $tWDI(LOWER) = (1.3 \times 10^5)CDELAY$  or

$fWDI(LOWER) = (7.69 \times 10^{-6})CDELAY^{-1}$

**(b)**  $t_{WDI(UPPER)} = (3.82 \times 10^{-4})C_{DELAY}$  or

$fWDI(UPPER) = (2.62 \times 10^{-5})CDELAY^{-1}$

For the CS8141 the lower limit is determined by the equations in (a) above.

The capacitor  $C_{DELAY}$  also determines the frequency of the RESET signal and the POWER-ON-RESET (POR) delay period.

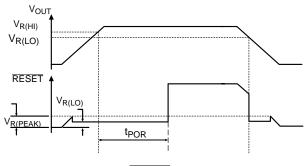

#### **RESET** Function

The  $\overline{\text{RESET}}$  function is activated when the Watchdog signal is outside of its preset window (Figure 16), when the regulator is in its power up state (Figure 17) or when V<sub>OUT</sub> drops below V<sub>OUT</sub> -4.5% for more than 2.0 µs (Figure 18)

If the Watchdog signal falls outside of the preset voltage and frequency window, a frequency programmable pulse train is generated at the RESET lead (Figure 16) until the correct Watchdog input signal reappears at the lead. The duration of the RESET pulse is determined by  $C_{DELAY}$ according to the following equation:

$tWDI(\overline{RESET}) = (1.0 \times 10^4)CDELAY$

#### RESET CIRCUIT WAVEFORMS WITH DELAYS INDICATED

If an undervoltage condition exists, the voltage on the  $\overline{\text{RESET}}$  lead goes low and the delay capacitor,  $C_{\text{DELAY}}$ , is discharged.  $\overline{\text{RESET}}$  remains low until output is in regulation, the voltage on  $C_{\text{DELAY}}$  exceeds the upper switching threshold and the Watchdog input signal is within its set window limits (Figures 17 and 18). The delay after the output is in regulation is:

## $tPOR(typ) = (4.75 \times 10^5)CDELAY$

The  $\overline{\text{RESET}}$  delay circuit is also programmed with the external cap  $C_{\text{DELAY}}$ .

The output of the reset circuit is an open collector NPN. **RESET** is operational down to  $V_{OUT} = 1.0$  V. Both **RESET** and its delay are governed by comparators with hysteresis to avoid undesirable oscillations.

Figure 16. Timing Diagrams for Watchdog and ENABLE Functions

Figure 17. Power RESET and Power Down

## **APPLICATION NOTES**

## **CS8140 DESIGN EXAMPLE**

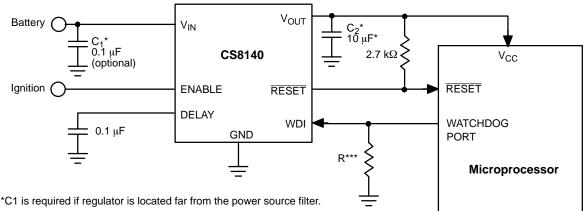

The CS8140 with its unique integration of linear regulator and control features:  $\overline{\text{RESET}}$ , ENABLE and WATCHDOG, provides a single IC solution for a microprocessor power supply. The reset delay, reset duration and watchdog frequency limits are all determined by a single capacitor. For a particular microprocessor the overriding requirement is usually the reset delay (also known as power on reset). The capacitor is chosen to meet this requirement and the reset duration and watchdog frequency follow.

The reset delay is given by:

Assume that the reset delay must be 200 ms minimum. From the CS8140 data sheet the reset delay has a  $\pm 37\%$  tolerance due to the regulator.

Assume the capacitor tolerance is  $\pm 10\%$ .

$t_{POR}(min) = (4.75 \times 10^5 \times 0.63) \times C_{DELAY} \times 0.9$

$$C_{DELAY}(min) = \frac{t_{POR}(min)}{2.69 \times 10^5}$$

$$C_{DELAY}(min) = 0.743 \,\mu F$$

Closest standard value is 0.82 µF.

Minimum and maximum delays using 0.82  $\mu F$  are 220 ms and 586 ms.

The duration of the reset pulse is given by:

$TWDI(\overline{RESET})(typ) = (1.0 \times 10^4) \times CDELAY$

This has a tolerance of  $\pm 50\%$  due to the IC, and  $\pm 10\%$  due to the capacitor.

The duration of the reset pulse ranges from 3.69 ms to 13.5 ms.

The watchdog signal can be expressed as a frequency or time. From a programmers point of view, time is more useful since they must ensure that a watchdog signal is issued consistently several times per second. The maximum and minimum watchdog times are given by:

$tWDI(LOWER) = (1.3 \times 10^5)CDELAY$

$t_{WDI(UPPER)} = (3.82 \times 10^4)C_{DELAY}$

There is a tolerance of  $\pm 20\%$  due to the CS8140. With a capacitor tolerance of  $\pm 10\%$ :

tWDI(LOWER) =  $(1.3 \times 10^5) \times 1.2 \times 1.1 \times C_{Delay}$

tWDI(UPPER) =  $(3.82 \times 10^4) \times 0.8 \times 0.9 \times C_{Delay}$

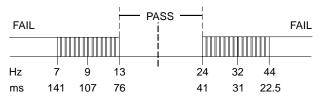

tWDI(LOWER) = 141 ms (max)

tWDI(UPPER) = 22.5 ms (max)

$t_{WDI(LOWER)} = (1.3 \times 10^5) \times 0.8 \times 0.9 \times C_{DELAY}$

twdi(upper) =  $(3.82 \times 10^4) \times 1.2 \times 1.1 \times CDELAY$

tWDI(LOWER) = 76 ms (min)

tWDI(UPPER) = 41 ms (min)

The software must be written so that a watchdog signal arrives at least every 76 ms but not faster than every 41 ms (Figure 19).

$C=0.1~\mu F~\pm 10\%$

# Figure 19. WDI Signal for C\_{Delay} = 0.82 $\mu\text{F}$ using CS8140

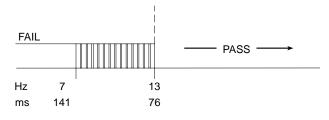

The CS8141 is identical to the CS8140 except that the CS8141 only has a lower watchdog frequency threshold.

The designer using this part need only be concerned with  $t_{WDI(LOWER)}$  as shown in Figure 20.

Figure 20. WDI Signal for C<sub>Delay</sub> = 0.82  $\mu$ F using CS8141

### ENERGY CONSERVATION AND SMART FEATURES

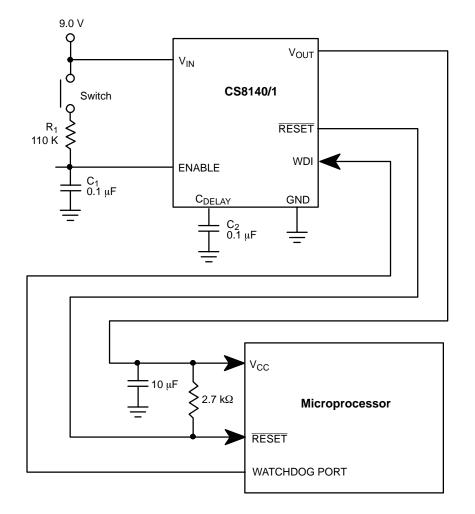

Energy conservation is another benefit of using a regulator with integrated microprocessor control features. Using the CS8140 or CS8141 as indicated in Figure 21, the microprocessor can control its own power down sequence.

The momentary contact switch quickly charges C1 through R1.

When the voltage across C1 reaches 3.95 V ( the enable threshold), the output switches on and  $V_{OUT}$  rises to 5.0 V. After a delay period determined by  $C_{Delay}$ , a frequency programmable reset pulse train is generated at the reset output. The pulse train continues until the correct watchdog signal appears at the WDI lead. C1 is now left to discharge through the input impedance of the enable lead (approximately 150 k $\Omega$ ) and the enable signal disappears. The output voltage remains at 5.0 V as long as the CS8140 continues to receive the correct watchdog signal.

The microprocessor can power itself down by terminating its watchdog signal. When the microprocessor finishes its housekeeping or power down software routine, it stops sending a watchdog signal. In response, the regulator generates a reset signal and goes into a sleep mode where  $V_{OUT}$  drops to 0 V, shutting down the microprocessor.

\*\*C2 is required for stability.

\*\*\*R ≤ 80 kΩ.

#### Figure 22. Application Diagram

#### STABILITY CONSIDERATIONS

The output or compensation capacitor  $C_2$  in Figure 22 helps determine three main characteristics of a linear regulator: start-up delay, load transient response and loop stability.

The capacitor value and type should be based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR can cause instability. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures ( $-25^{\circ}$ C to  $-40^{\circ}$ C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturers data sheet usually provides this information.

The value for the output capacitor  $C_2$  shown in Figure 22 should work for most applications, however it is not necessarily the optimized solution.

To determine an acceptable value for  $C_2$  for a particular application, start with a tantalum capacitor of the recommended value and work towards a less expensive alternative part.

**Step 1:** Place the completed circuit with a tantalum capacitor of the recommended value in an environmental chamber at the lowest specified operating temperature and monitor the outputs with an oscilloscope. A decade box connected in series with the capacitor will simulate the higher ESR of an aluminum capacitor. Leave the decade box outside the chamber, the small resistance added by the longer leads is negligible.

**Step 2:** With the input voltage at its maximum value, increase the load current slowly from zero to full load while observing the output for any oscillations. If no oscillations are observed, the capacitor is large enough to ensure a stable design under steady state conditions.

**Step 3:** Increase the ESR of the capacitor from zero using the decade box and vary the load current until oscillations appear. Record the values of load current and ESR that cause the greatest oscillation. This represents the worst case load conditions for the regulator at low temperature. **Step 4:** Maintain the worst case load conditions set in step 3 and vary the input voltage until the oscillations increase. This point represents the worst case input voltage conditions.

**Step 5:** If the capacitor is adequate, repeat steps 3 and 4 with the next smaller valued capacitor. A smaller capacitor will usually cost less and occupy less board space. If the output oscillates within the range of expected operating conditions, repeat steps 3 and 4 with the next larger standard capacitor value.

**Step 6:** Test the load transient response by switching in various loads at several frequencies to simulate its real working environment. Vary the ESR to reduce ringing.

**Step 7:** Increase the temperature to the highest specified operating temperature. Vary the load current as instructed in step 5 to test for any oscillations.

Once the minimum capacitor value with the maximum ESR is found, a safety factor should be added to allow for the tolerance of the capacitor and any variations in regulator performance. Most good quality aluminum electrolytic capacitors have a tolerance of  $\pm$  20% so the minimum value found should be increased by at least 50% to allow for this tolerance plus the variation which will occur at low temperatures. The ESR of the capacitor should be less than 50% of the maximum allowable ESR found in step 3 above.

#### CALCULATING POWER DISSIPATION IN A SINGLE OUTPUT LINEAR REGULATOR

The maximum power dissipation for a single output regulator (Figure 23) is:

PD(max) = [VIN(max) - VOUT(min)]IOUT(max) + VIN(max)IQ(1)

where:

- $V_{IN(max)}$  is the maximum input voltage,

- V<sub>OUT(min)</sub> is the minimum output voltage,

- I<sub>OUT(max)</sub> is the maximum output current for the application, and

- $I_Q$  is the quiescent current the regulator consumes at  $I_{OUT(max)}$ .

#### Figure 23. Single Output Regulator With Key Performance Parameters Labeled

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{\theta JA}$  can be calculated:

$$R_{\Theta JA} = \frac{150^{\circ}C - T_{A}}{P_{D}}$$

(2)

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

## HEAT SINKS

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\theta JA}$ .

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CS} + R_{\Theta SA}$$

(3)

where:

$R_{\Theta JC}$  = the junction-to-case thermal resistance,

$R_{\theta CS}$  = the case–to–heatsink thermal resistance, and

$R_{\theta SA}$  = the heatsink-to-ambient thermal resistance.

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta JA}$ , it too is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

## MARKING DIAGRAMS

TO-220-7

#### D<sup>2</sup>PAK-7 936AB

#### SO-24L

$\begin{array}{lll} x & = 0 \text{ or } 1 \\ A & = \text{Assembly Location} \\ WL, L & = Wafer Lot \\ YY, Y & = Year \\ WW, W & = Work Week \end{array}$

## **DEVICE ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| CS8140YT7    | TO-220-7, Straight   | 50 Units/Rail         |

| CS8140YTVA7  | TO-220-7, Vertical   | 50 Units/Rail         |

| CS8140YTHA7  | TO-220-7, Horizontal | 50 Units/Rail         |

| CS8140YDW24  | SO-24L               | 31 Units/Rail         |

| CS8140YDWR24 | SO-24L               | 1000 Tape & Reel      |

| CS8140YN14   | DIP-14               | 25 Units/Rail         |

| CS8141YT7    | TO-220-7, Straight   | 50 Units/Rail         |

| CS8141YTVA7  | TO–220–7, Vertical   | 50 Units/Rail         |

| CS8141YTHA7  | TO-220-7, Horizontal | 50 Units/Rail         |

| CS8141YDPS7  | D <sup>2</sup> PAK–7 | 50 Units/Rail         |

| CS8141YDPSR7 | D <sup>2</sup> PAK–7 | 750 Tape & Reel       |

| CS8141YDW24  | SO-24L               | 31 Units/Rail         |

| CS8141YDWR24 | SO-24L               | 1000 Tape & Reel      |

| CS8141YN14   | DIP-14               | 25 Units/Rail         |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## PACKAGE DIMENSIONS

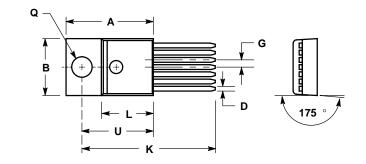

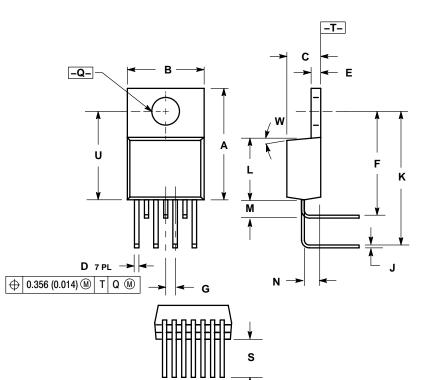

TO-220-7 **T SUFFIX** CASE 821E-04 ISSUE D

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.003 (0.076) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. 4. 821E-01 THRU 821-03 OBSOLETE, NEW STANDARD 821E-04.

|     | INCHES |       | MILLIN | IETERS |

|-----|--------|-------|--------|--------|

| DIM | MIN    | MAX   | MIN    | MAX    |

| Α   | 0.600  | 0.610 | 15.24  | 15.49  |

| В   | 0.386  | 0.403 | 9.80   | 10.23  |

| С   | 0.170  | 0.180 | 4.32   | 4.56   |

| D   | 0.028  | 0.037 | 0.71   | 0.94   |

| G   | 0.045  | 0.055 | 1.15   | 1.39   |

| Η   | 0.088  | 0.102 | 2.24   | 2.59   |

| J   | 0.018  | 0.026 | 0.46   | 0.66   |

| K   | 1.028  | 1.042 | 26.11  | 26.47  |

| L   | 0.355  | 0.365 | 9.02   | 9.27   |

| Μ   | 5°1    | NOM   | 5 ° N  | MON    |

| Q   | 0.142  | 0.148 | 3.61   | 3.75   |

| U   | 0.490  | 0.501 | 12.45  | 12.72  |

| V   | 0.045  | 0.055 | 1.15   | 1.39   |

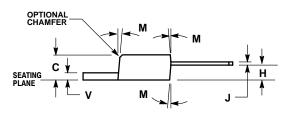

TO-220-7 **TVA SUFFIX** CASE 821J-02 **ISSUE A**

NOTES:

ITES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 10.92 (0.043) MAXIMUM.

|     | INC       | HES   | MILLIN | IETERS |

|-----|-----------|-------|--------|--------|

| DIM | MIN       | MAX   | MIN    | MAX    |

| Α   | 0.560     | 0.590 | 14.22  | 14.99  |

| В   | 0.385     | 0.415 | 9.77   | 10.54  |

| C   | 0.160     | 0.190 | 4.06   | 4.82   |

| D   | 0.023     | 0.037 | 0.58   | 0.94   |

| E   | 0.045     | 0.055 | 1.14   | 1.40   |

| F   | 0.540     | 0.555 | 13.72  | 14.10  |

| G   | 0.050 BSC |       | 1.27   | BSC    |

| Н   | 0.570     | 0.595 | 14.48  | 15.11  |

| J   | 0.014     | 0.022 | 0.36   | 0.56   |

| K   | 0.785     | 0.800 | 19.94  | 20.32  |

| L   | 0.322     | 0.337 | 8.18   | 8.56   |

| Μ   | 0.073     | 0.088 | 1.85   | 2.24   |

| Ν   | 0.090     | 0.115 | 2.28   | 2.91   |

| Q   | 0.146     | 0.156 | 3.70   | 3.95   |

| R   | 0.289     | 0.304 | 7.34   | 7.72   |

| S   | 0.164     | 0.179 | 4.17   | 4.55   |

| U   | 0.460     | 0.475 | 11.68  | 12.07  |

| W   | 3         | 0     | 3      | °      |

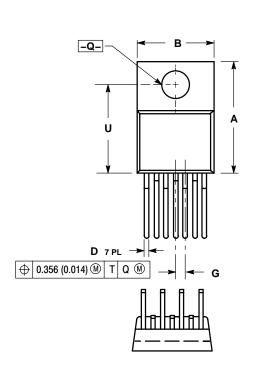

# PACKAGE DIMENSIONS

TO-220-7 THA SUFFIX CASE 821H-02 **ISSUE A**

NOTES:

DIMENSIONING AND TOLERANCING PER ANSI 1. DIMENSIO Y14.5M, 1982.

- 2. 3.

Y 14.3M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL

NOT EXCEED 10.92 (0.043) MAXIMUM. 1. LEADS MAINTAIN A RIGHT ANGLE WITH RESPECT TO THE PACKAGE BODY TO WITH

$\pm 0.020$ "

|     | INC   | HES   | MILLIN   | IETERS |

|-----|-------|-------|----------|--------|

| DIM | MIN   | MAX   | MIN      | MAX    |

| Α   | 0.560 | 0.590 | 14.22    | 14.99  |

| В   | 0.385 | 0.415 | 9.77     | 10.54  |

| С   | 0.160 | 0.190 | 4.06     | 4.82   |

| D   | 0.023 | 0.037 | 0.58     | 0.94   |

| Е   | 0.045 | 0.055 | 1.14     | 1.40   |

| F   | 0.568 | 0.583 | 14.43    | 14.81  |

| G   | 0.050 | BSC   | 1.27 BSC |        |

| ſ   | 0.015 | 0.022 | 0.38     | 0.56   |

| Κ   | 0.728 | 0.743 | 18.49    | 18.87  |

| L   | 0.322 | 0.337 | 8.18     | 8.56   |

| Μ   | 0.101 | 0.116 | 2.57     | 2.95   |

| Ν   | 0.090 | 0.115 | 2.28     | 2.91   |

| Q   | 0.146 | 0.156 | 3.70     | 3.95   |

| S   | 0.150 | 0.200 | 3.81     | 5.08   |

| U   | 0.460 | 0.475 | 11.68    | 12.07  |

| W   | 3     | 0     | 3        | ۰<br>۱ |

D<sup>2</sup>PAK-7 **DPS SUFFIX** CASE 936AB-01 ISSUE O

# For D<sup>2</sup>PAK Outline and **Dimensions – Contact Factory**

## PACKAGE DIMENSIONS

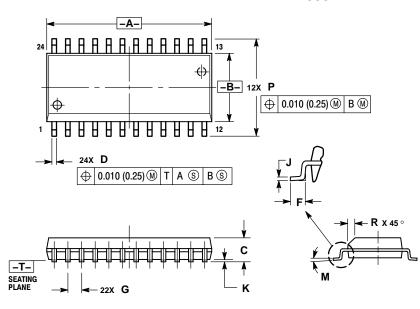

SO-24L **DW SUFFIX** CASE 751E-04 ISSUE E

NOTES:

- DIESS: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- PEH SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 15.25       | 15.54 | 0.601     | 0.612 |

| В   | 7.40        | 7.60  | 0.292     | 0.299 |

| С   | 2.35        | 2.65  | 0.093     | 0.104 |

| D   | 0.35        | 0.49  | 0.014     | 0.019 |

| F   | 0.41        | 0.90  | 0.016     | 0.035 |

| G   | 1.27 BSC    |       | 0.050 BSC |       |

| J   | 0.23        | 0.32  | 0.009     | 0.013 |

| K   | 0.13        | 0.29  | 0.005     | 0.011 |

| М   | 0 °         | 8°    | 0 °       | 8°    |

| Ρ   | 10.05       | 10.55 | 0.395     | 0.415 |

| R   | 0.25        | 0.75  | 0.010     | 0.029 |

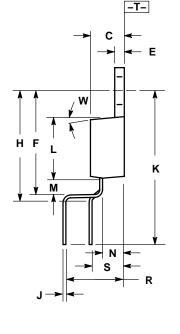

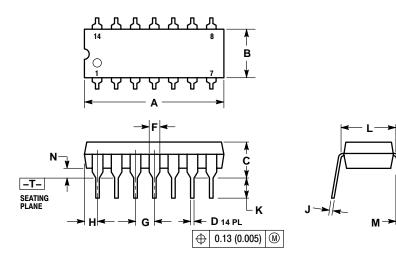

DIP-14 **N SUFFIX** CASE 646-04 **ISSUE M**

NOTES:

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION LTO CENTER OF LEADS WHEN FORMED PARALLEL 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH. 5. ROUNDED CORNERS OPTIONAL.

|     | INCHES    |       | MILLIMETERS |       |

|-----|-----------|-------|-------------|-------|

| DIM | MIN       | MAX   | MIN         | MAX   |

| Α   | 0.715     | 0.740 | 18.16       | 18.80 |

| В   | 0.240     | 0.260 | 6.10        | 6.60  |

| С   | 0.160     | 0.180 | 4.06        | 4.57  |

| D   | 0.015     | 0.020 | 0.38        | 0.51  |

| F   | 0.040     | 0.060 | 1.02        | 1.52  |

| G   | 0.100 BSC |       | 2.54 BSC    |       |

| н   | 0.052     | 0.072 | 1.32        | 1.83  |

| J   | 0.008     | 0.012 | 0.20        | 0.30  |

| K   | 0.115     | 0.135 | 2.92        | 3.43  |

| L   | 0.290     | 0.310 | 7.37        | 7.87  |

| Μ   |           | 10 °  |             | 10 °  |

| N   | 0.020     | 0.040 | 0.51        | 1.02  |

SMART REGULATOR is a registered trademark of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.