# Quad Analog Switch/ Quad Multiplexer

The MC14016B quad bilateral switch is constructed with MOS P-channel and N-channel enhancement mode devices in a single monolithic structure. Each MC14016B consists of four independent switches capable of controlling either digital or analog signals. The quad bilateral switch is used in signal gating, chopper, modulator, demodulator and CMOS logic implementation.

- Diode Protection on All Inputs

- Supply Voltage Range = 3.0 Vdc to 18 Vdc

- Linearized Transfer Characteristics

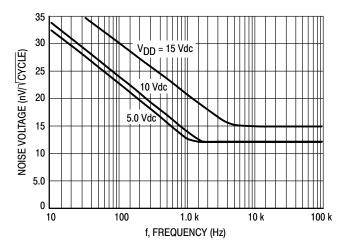

- Low Noise  $12 \text{ nV/}\sqrt{\text{Cycle}}$ ,  $f \ge 1.0 \text{ kHz typical}$

- Pin-for-Pin Replacements for CD4016B, CD4066B (Note improved transfer characteristic design causes more parasitic coupling capacitance than CD4016)

- For Lower R<sub>ON</sub>, Use The HC4016 High-Speed CMOS Device or The MC14066B

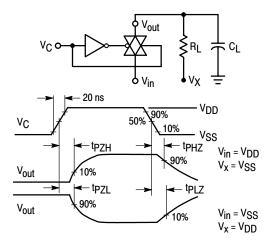

- This Device Has Inputs and Outputs Which Do Not Have ESD Protection. Antistatic Precautions Must Be Taken.

#### MAXIMUM RATINGS (Voltages Referenced to VSS) (Note 2.)

| Symbol                             | Parameter                                       | Value                         | Unit |

|------------------------------------|-------------------------------------------------|-------------------------------|------|

| $V_{DD}$                           | DC Supply Voltage Range                         | -0.5 to +18.0                 | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage Range (DC or Transient) | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub>                    | Input Current (DC or Transient) per Control Pin | ±10                           | mA   |

| Isw                                | Switch Through Current                          | ±25                           | mA   |

| PD                                 | Power Dissipation,<br>per Package (Note 3.)     | 500                           | mW   |

| TA                                 | Ambient Temperature Range                       | -55 to +125                   | °C   |

| T <sub>stg</sub>                   | Storage Temperature Range                       | -65 to +150                   | °C   |

| TL                                 | Lead Temperature<br>(8–Second Soldering)        | 260                           | °C   |

- Maximum Ratings are those values beyond which damage to the device may occur.

- Temperature Derating: Plastic "P and D/DW" Packages: – 7.0 mW/°C From 65°C To 125°C

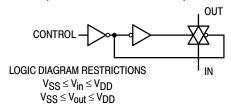

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \mbox{ or } V_{out}) \leq V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD). Unused outputs must be left open.

# ON Semiconductor

http://onsemi.com

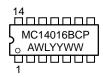

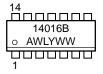

#### MARKING DIAGRAMS

PDIP-14 P SUFFIX CASE 646

SOIC-14 D SUFFIX CASE 751A

SOEIAJ-14 F SUFFIX CASE 965

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week

#### **ORDERING INFORMATION**

| Device      | Package   | Shipping         |  |  |  |

|-------------|-----------|------------------|--|--|--|

| MC14016BCP  | PDIP-14   | 2000/Box         |  |  |  |

| MC14016BD   | SOIC-14   | 55/Rail          |  |  |  |

| MC14016BDR2 | SOIC-14   | 2500/Tape & Reel |  |  |  |

| MC14016BF   | SOEIAJ-14 | See Note 1.      |  |  |  |

| MC14016BFEL | SOEIAJ-14 | See Note 1.      |  |  |  |

For ordering information on the EIAJ version of the SOIC packages, please contact your local ON Semiconductor representative.

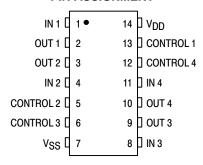

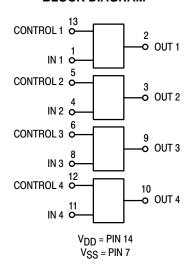

# **PIN ASSIGNMENT**

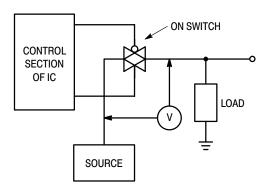

#### **BLOCK DIAGRAM**

| Control             | Switch |

|---------------------|--------|

| 0 = V <sub>SS</sub> | Off    |

| 1 = V <sub>DD</sub> | On     |

#### **LOGIC DIAGRAM**

(1/4 OF DEVICE SHOWN)

#### **ELECTRICAL CHARACTERISTICS** (Voltages Referenced to V<sub>SS</sub>)

|                                                                                                                                                                                                                                                                                                                                                                           |        |                  | V <sub>DD</sub> − 55°C |                       | 5°C                                    | 25°C             |                                               |                                        | 125°C            |                                               |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|------------------------|-----------------------|----------------------------------------|------------------|-----------------------------------------------|----------------------------------------|------------------|-----------------------------------------------|------|

| Characteristic                                                                                                                                                                                                                                                                                                                                                            | Figure | Symbol           | Vdc                    | Min                   | Max                                    | Min              | Тур (4.)                                      | Max                                    | Min              | Max                                           | Unit |

| Input Voltage<br>Control Input                                                                                                                                                                                                                                                                                                                                            | 1      | VIL              | 5.0<br>10<br>15        | _<br>_<br>_           | _<br>_<br>_                            | _<br>_<br>_      | 1.5<br>1.5<br>1.5                             | 0.9<br>0.9<br>0.9                      | _<br>_<br>_      | _<br>_<br>_                                   | Vdc  |

|                                                                                                                                                                                                                                                                                                                                                                           |        | VIH              | 5.0<br>10<br>15        |                       | _<br>_<br>_                            | 3.0<br>8.0<br>13 | 2.0<br>6.0<br>11                              | _<br>_<br>_                            | _<br>_<br>_      | _<br>_<br>_                                   | Vdc  |

| Input Current Control                                                                                                                                                                                                                                                                                                                                                     | _      | l <sub>in</sub>  | 15                     | _                     | ±0.1                                   | _                | ±0.00001                                      | ±0.1                                   | _                | ± 1.0                                         | μAdc |

| Input Capacitance Control Switch Input Switch Output Feed Through                                                                                                                                                                                                                                                                                                         | _      | C <sub>in</sub>  | _<br>_<br>_<br>_       | _<br>_<br>_<br>_      | _<br>_<br>_<br>_                       | _<br>_<br>_      | 5.0<br>5.0<br>5.0<br>0.2                      | _<br>_<br>_<br>_                       | _<br>_<br>_      | _<br>_<br>_<br>_                              | pF   |

| Quiescent Current<br>(Per Package) (5.)                                                                                                                                                                                                                                                                                                                                   | 2,3    | I <sub>DD</sub>  | 5.0<br>10<br>15        | _<br>                 | 0.25<br>0.5<br>1.0                     | _<br>_<br>_      | 0.0005<br>0.0010<br>0.0015                    | 0.25<br>0.5<br>1.0                     | _<br>_<br>_      | 7.5<br>15<br>30                               | μAdc |

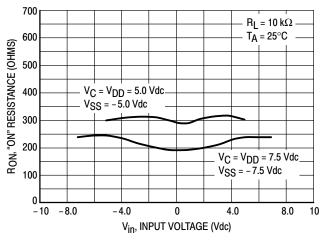

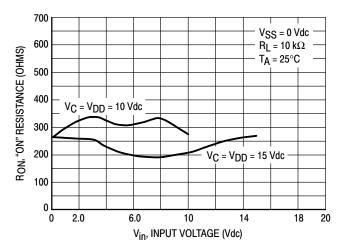

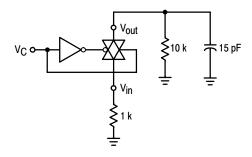

| "ON" Resistance $ (V_C = V_{DD}, R_L = 10 \text{ k}\Omega) $ $ (V_{in} = +5.0 \text{ Vdc}) $ $ (V_{in} = +5.0 \text{ Vdc}) $ $ (V_{in} = -5.0 \text{ Vdc}) $ $ (V_{in} = \pm 0.25 \text{ Vdc}) $ $ (V_{in} = \pm 7.5 \text{ Vdc}) $ $ (V_{in} = +7.5 \text{ Vdc}) $ $ (V_{in} = -7.5 \text{ Vdc}) $ $ (V_{in} = \pm 0.25 \text{ Vdc}) $ $ (V_{in} = \pm 10 \text{ Vdc}) $ | 4,5,6  | RON              | 5.0<br>7.5             | _<br>_<br>_<br>_<br>_ | 600<br>600<br>600<br>360<br>360<br>360 |                  | 300<br>300<br>280<br>240<br>240<br>180<br>260 | 660<br>660<br>660<br>400<br>400<br>400 |                  | 840<br>840<br>840<br>520<br>520<br>520<br>840 | Ohms |

| $(V_{in} = + 0.25 \text{ Vdc}) V_{SS} = 0 \text{ Vdc}$<br>$(V_{in} = + 5.6 \text{ Vdc})$<br>$(V_{in} = + 15 \text{ Vdc})$<br>$(V_{in} = + 0.25 \text{ Vdc}) V_{SS} = 0 \text{ Vdc}$<br>$(V_{in} = + 9.3 \text{ Vdc})$                                                                                                                                                     |        |                  | 10<br>15               | _<br>_<br>_<br>_      | 600<br>600<br>360<br>360<br>360        | _<br>_<br>_<br>_ | 310<br>310<br>260<br>260<br>300               | 660<br>660<br>400<br>400<br>400        | _<br>_<br>_<br>_ | 840<br>840<br>520<br>520<br>520               |      |

| $\Delta$ "ON" Resistance Between any 2 circuits in a common package $(V_{C} = V_{DD}) \\ (V_{in} = \pm 5.0 \text{ Vdc}, V_{SS} = -5.0 \text{ Vdc}) \\ (V_{in} = \pm 7.5 \text{ Vdc}, V_{SS} = -7.5 \text{ Vdc})$                                                                                                                                                          | _      | ΔR <sub>ON</sub> | 5.0<br>7.5             |                       |                                        |                  | 15<br>10                                      |                                        |                  | _<br>                                         | Ohms |

| Input/Output Leakage Current ( $V_C = V_SS$ ) ( $V_{in} = +7.5$ , $V_{out} = -7.5$ Vdc) ( $V_{in} = -7.5$ , $V_{out} = +7.5$ Vdc)                                                                                                                                                                                                                                         | _      | _                | 7.5<br>7.5             |                       | ±0.1<br>±0.1                           | _                | ±0.0015<br>±0.0015                            | ±0.1<br>±0.1                           | _                | ± 1.0<br>± 1.0                                | μAdc |

NOTE: All unused inputs must be returned to V<sub>DD</sub> or V<sub>SS</sub> as appropriate for the circuit application.

Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

For voltage drops across the switch (ΔV<sub>switch</sub>) > 600 mV ( > 300 mV at high temperature), excessive V<sub>DD</sub> current may be drawn; i.e., the current out of the switch may contain both V<sub>DD</sub> and switch input components. The reliability of the device will be unaffected unless the Maximum Ratings are exceeded. (See first page of this data sheet.) Reference Figure 14.

# **ELECTRICAL CHARACTERISTICS (6.)** ( $C_L = 50 \text{ pF}, T_A = 25^{\circ}\text{C}$ )

| Characteristic                                                                                                                                                                                                                                                                                                                                                            | Figure | Symbol                                                                                      | V <sub>DD</sub><br>Vdc | Min                | Typ (7.)                   | Max              | Unit      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------|------------------------|--------------------|----------------------------|------------------|-----------|

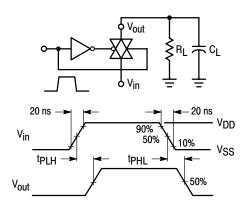

| Propagation Delay Time (V <sub>SS</sub> = 0 Vdc) V <sub>in</sub> to V <sub>out</sub> (V <sub>C</sub> = V <sub>DD</sub> , R <sub>L</sub> = 10 kΩ)                                                                                                                                                                                                                          | 7      | t <sub>PLH</sub> ,<br>t <sub>PHL</sub>                                                      | 5.0<br>10<br>15        | _<br>_<br>_        | 15<br>7.0<br>6.0           | 45<br>15<br>12   | ns        |

| Control to Output $(V_{in} \le 10 \text{ Vdc}, R_L = 10 \text{ k}\Omega)$                                                                                                                                                                                                                                                                                                 | 8      | <sup>†</sup> PHZ <sup>,</sup><br>†PLZ <sup>,</sup><br>†PZH <sup>,</sup><br><sup>†</sup> PZL | 5.0<br>10<br>15        | _<br>_<br>_        | 34<br>20<br>15             | 90<br>45<br>35   | ns        |

| Crosstalk, Control to Output ( $V_{SS}$ = 0 Vdc)<br>( $V_{C}$ = $V_{DD}$ , $R_{in}$ = 10 k $\Omega$ , $R_{out}$ = 10 k $\Omega$ ,<br>f = 1.0 kHz)                                                                                                                                                                                                                         | 9      | _                                                                                           | 5.0<br>10<br>15        | _<br>_<br>_        | 30<br>50<br>100            |                  | mV        |

| Crosstalk between any two switches (V <sub>SS</sub> = 0 Vdc)<br>(R <sub>L</sub> = 1.0 k $\Omega$ , f = 1.0 MHz,<br>crosstalk = $20 \log_{10} \frac{V_{out1}}{V_{out2}}$ )                                                                                                                                                                                                 | _      | _                                                                                           | 5.0                    | _                  | - 80                       | _                | dB        |

| Noise Voltage ( $V_{SS} = 0 \text{ Vdc}$ )<br>( $V_C = V_{DD}$ , $f = 100 \text{ Hz}$ )<br>( $V_C = V_{DD}$ , $f = 100 \text{ kHz}$ )                                                                                                                                                                                                                                     | 10,11  | _                                                                                           | 5.0<br>10<br>15<br>5.0 | <br> -<br> -<br> - | 24<br>25<br>30<br>12<br>12 | _<br>_<br>_<br>_ | nV/√Cycle |

| Second Harmonic Distortion (VSS = $-5.0$ Vdc)<br>(Vin = 1.77 Vdc, RMS Centered @ 0.0 Vdc,<br>RL = $10 \text{ k}\Omega$ , f = $1.0 \text{ kHz}$ )                                                                                                                                                                                                                          | _      | _                                                                                           | 15<br>5.0              | _                  | 0.16                       | _                | %         |

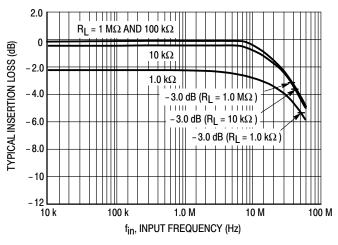

| $\begin{split} &\text{Insertion Loss (V_C = V_{DD}, V_{in} = 1.77 \ Vdc,} \\ &\text{V}_{SS} = -5.0 \ Vdc, \ \text{RMS centered} = 0.0 \ Vdc, \ f = 1.0 \ \text{MHz)} \\ &\text{I}_{IOSS} = 20 \log_{10} \frac{V_{out}}{V_{in}}) \\ &(R_L = 1.0 \ k\Omega) \\ &(R_L = 10 \ k\Omega) \\ &(R_L = 100 \ k\Omega) \\ &(R_L = 1.0 \ M\Omega) \end{split}$                       | 12     | _                                                                                           | 5.0                    |                    | 2.3<br>0.2<br>0.1<br>0.05  | _<br>_<br>_<br>_ | dB        |

| $\label{eq:bandwidth} \begin{array}{l} \text{Bandwidth } (-3.0 \text{ dB}) \\ \text{($^{\prime}$C} = \text{V}_{DD}, \text{V}_{in} = 1.77 \text{ Vdc}, \text{V}_{SS} = -5.0 \text{ Vdc}, \\ \text{RMS centered @ 0.0 Vdc}) \\ \text{($R_{L} = 1.0 k\Omega)} \\ \text{($R_{L} = 10 k\Omega)} \\ \text{($R_{L} = 100 k\Omega)} \\ \text{($R_{L} = 1.0 M\Omega)} \end{array}$ | 12,13  | BW                                                                                          | 5.0                    | <br> -<br> -       | 54<br>40<br>38<br>37       | _<br>_<br>_<br>_ | MHz       |

| OFF Channel Feedthrough Attenuation $ \begin{array}{l} (V_{SS} = -5.0 \text{ Vdc}) \\ (V_{C} = V_{SS}, 20 \log_{10} \frac{V_{out}}{V_{in}} = -50  \text{dB}) \\ (R_{L} = 1.0  \text{k}\Omega) \\ (R_{L} = 10  \text{k}\Omega) \\ (R_{L} = 100  \text{k}\Omega) \\ (R_{L} = 1.0  \text{M}\Omega) \end{array} $                                                             | _      | _                                                                                           | 5.0                    | <br> -<br> -       | 1250<br>140<br>18<br>2.0   | _<br>_<br>_<br>_ | kHz       |

<sup>6.</sup> The formulas given are for typical characteristics only at 25°C.

7. Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

$\begin{array}{l} V_{IL} \colon V_{C} \text{ is raised from V}_{SS} \text{ until } V_{C} = V_{IL}. \\ \text{at } V_{C} = V_{IL} \colon I_{S} = \pm 10 \ \mu\text{A} \text{ with } V_{in} = V_{SS}, V_{out} = V_{DD} \text{ or } V_{in} = V_{DD}, V_{out} = V_{SS}. \\ \end{array}$

$V_{IH}$ : When  $V_C = V_{IH}$  to  $V_{DD}$ , the switch is ON and the  $R_{ON}$  specifications are met.

Figure 1. Input Voltage Test Circuit

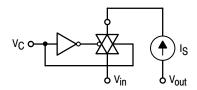

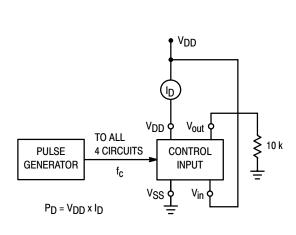

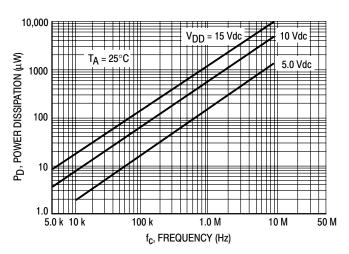

Figure 2. Quiescent Power Dissipation

Test Circuit

Figure 3. Typical Power Dissipation per Circuit (1/4 of device shown)

# **TYPICAL RON versus INPUT VOLTAGE**

Figure 4.  $V_{SS} = -5.0 \text{ V}$  and -7.5 V

Figure 5. Vss = 0 V

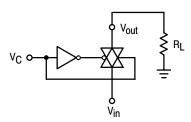

Figure 6. R<sub>ON</sub> Characteristics Test Circuit

Figure 8. Turn-On Delay Time Test Circuit and Waveforms

Figure 10. Noise Voltage Test Circuit

Figure 7. Propagation Delay Test Circuit and Waveforms

Figure 9. Crosstalk Test Circuit

Figure 11. Typical Noise Characteristics

Figure 12. Typical Insertion Loss/Bandwidth Characteristics

Figure 13. Frequency Response Test Circuit

Figure 14.  $\Delta V$  Across Switch

#### **APPLICATIONS INFORMATION**

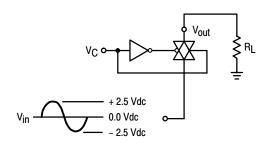

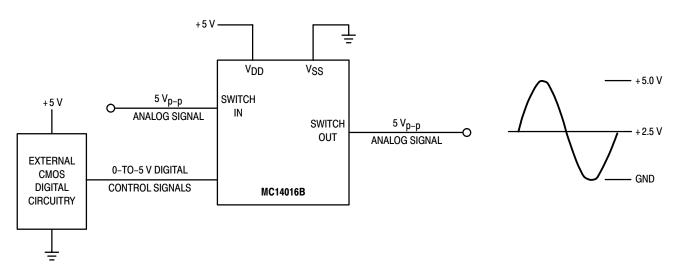

Figure A illustrates use of the Analog Switch. The 0–to–5 V Digital Control signal is used to directly control a 5  $\rm V_{p-p}$  analog signal.

The digital control logic levels are determined by  $V_{DD}$  and  $V_{SS}$ . The  $V_{DD}$  voltage is the logic high voltage; the  $V_{SS}$  voltage is logic low. For the example,  $V_{DD}$  =+5 V logic high at the control inputs;  $V_{SS}$  = GND = 0 V logic low.

The maximum analog signal level is determined by  $V_{DD}$  and  $V_{SS}$ . The analog voltage must not swing higher than  $V_{DD}$  or lower than  $V_{SS}$ .

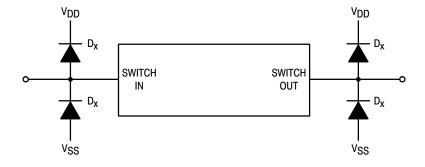

The example shows a 5  $V_{p-p}$  signal which allows no margin at either peak. If voltage transients above  $V_{DD}$  and/or below  $V_{SS}$  are anticipated on the analog channels, external diodes ( $D_x$ ) are recommended as shown in Figure B. These diodes should be small signal types able to absorb the maximum anticipated current surges during clipping.

The *absolute* maximum potential difference between  $V_{DD}$  and  $V_{SS}$  is 18.0 V. Most parameters are specified up to 15 V which is the *recommended* maximum difference between  $V_{DD}$  and  $V_{SS}$ .

Figure A. Application Example

Figure B. External Germanium or Schottky Clipping Diodes