# Secondary Side SMPS OFF Mode Controller for Low Standby Power

The NCP4353/4 is a secondary side SMPS controller designed for use in applications which require extremely low no load power consumption. The device is capable of detecting "no load" conditions and entering the power supply into a low consumption OFF mode. During OFF mode, the primary side controller is turned off and energy is provided by the output capacitors thus eliminating the power consumption required to maintain regulation. During OFF mode, the output voltage relaxes and is allowed to decrease to an adjustable level. Once more energy is required, the NCP4353/4 automatically restarts the primary side controller. The NCP4353/4 controls the primary side controller with an "Active OFF" signal, meaning that it drives optocoupler current during OFF mode to pull–down the FB pin of the primary controller.

During normal power supply operation, the NCP4353/4 provides integrated voltage feedback regulation, replacing the need for a shunt regulator. The A versions include a current regulation loop in addition to voltage regulation. Feedback control as well as ON/OFF signal can be provided with only one optocoupler.

The NCP4354 includes a LED driver pin implemented with an open drain MOSFET driven by a 1 kHz square wave with a 12.5% duty cycle when primary side is in regulation for indication purpose.

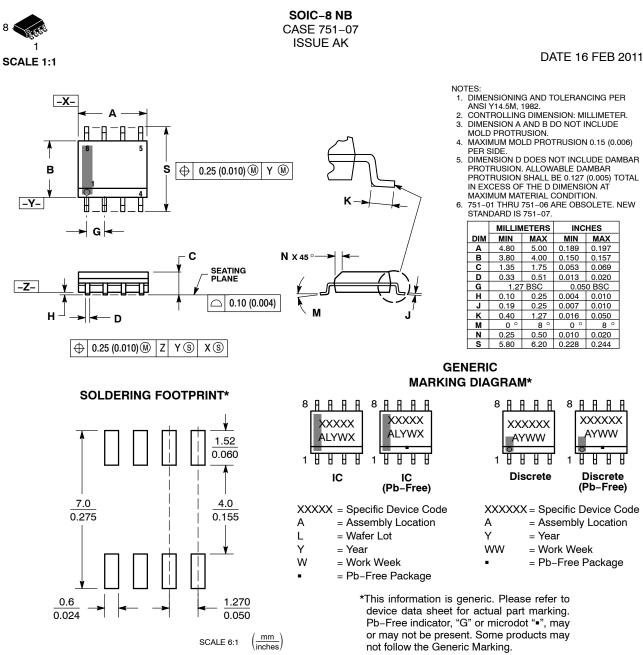

The NCP4353 is available in TSOP–6 package while the NCP4354 is available in SOIC–8 package.

#### Features

- Operating Input Voltage Range: 2.5 V to 36.0 V

- Supply Current < 100 μA

- $\pm 0.5\%$  Reference Voltage Accuracy (T<sub>J</sub> = 25°C)

- Constant Voltage and Constant Current (A versions) Control Loop

- Indication LED PWM Modulated Driver (NCP4354x)

- Designed for use with NCP1246 Fixed Frequency PWM Controller

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- Offline Adapters for Notebooks, Game Stations and Printers

- High Power AC-DC Converters for TVs, Set-Top Boxes, Monitors, etc.

|                                | NCP4353A | NCP4353B | NCP4354A | NCP4354B |  |  |

|--------------------------------|----------|----------|----------|----------|--|--|

| Adjustable<br>V <sub>min</sub> | No       | Yes      | Yes      | Yes      |  |  |

| Current<br>Regulation          | Yes      | No       | Yes      | No       |  |  |

| LED Driver                     | No       | No       | Yes      | Yes      |  |  |

| Package                        | TSOP-6   | TSOP-6   | SOIC-8   | SOIC-8   |  |  |

# **ON Semiconductor®**

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information in the package dimensions section on page 15 of this data sheet.

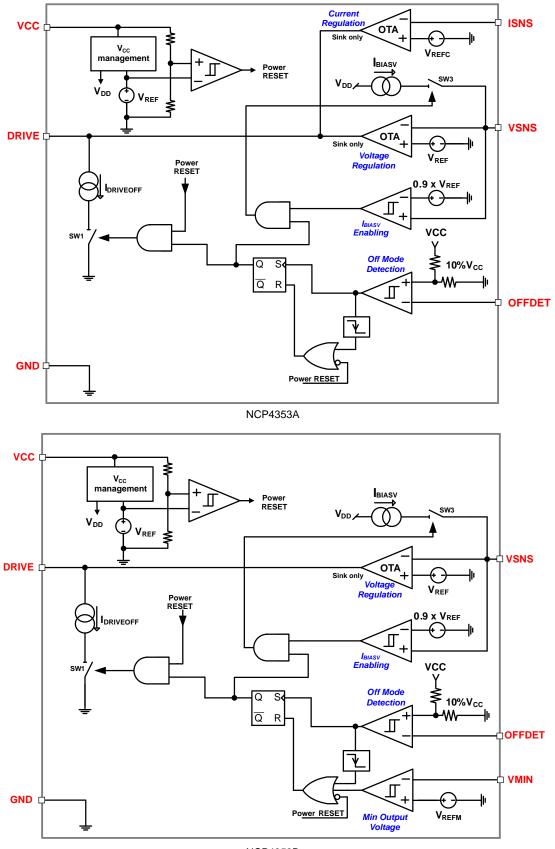

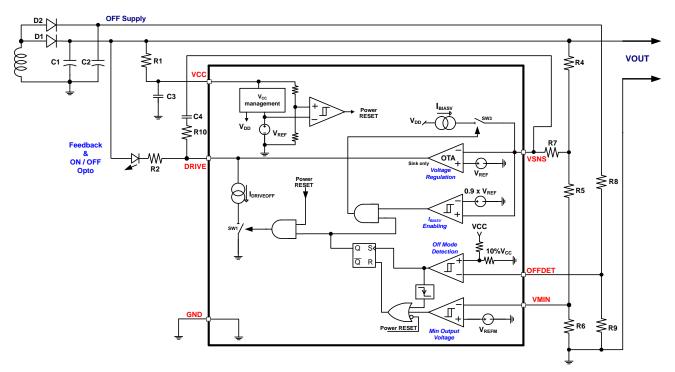

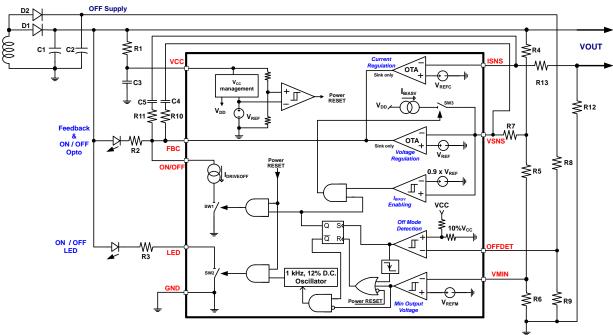

NCP4353B Figure 1. Simplified Block Diagrams NCP4353A and NCP4353B

Figure 2. Simplified Block Diagrams NCP4354A and NCP4354B

#### **PIN FUNCTION DESCRIPTION**

| NCP4353A | NCP4353B | NCP4354A | NCP4354B | Pin Name | Description                                                                                                                                     |

|----------|----------|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 1        | 8        | 8        | VCC      | Supply voltage pin                                                                                                                              |

| 2        | 2        | 7        | 7        | GND      | Ground                                                                                                                                          |

| 6        | 6        | 1        | 1        | VSNS     | Output voltage sensing pin, connected to output voltage divider                                                                                 |

| 5        | 5        | 2        | 2        | OFFDET   | OFF mode detection input. Voltage divider pro-<br>vides adjustable off mode detection threshold                                                 |

| -        | 4        | 3        | 3        | VMIN     | Minimum output voltage adjustment                                                                                                               |

| 4        | -        | 4        | _        | ISNS     | Current sensing input for output current regulation, connect it to shunt resistor in ground branch.                                             |

| -        | -        | 5        | 4        | LED      | PWM LED driver output. Connected to LED cath-<br>ode with current define by external serial resist-<br>ance                                     |

| -        | _        | -        | 6        | FBC      | Output of current sinking OTA amplifier or amplifiers driving feedback optocoupler's LED. Connect here compensation network (networks) as well. |

| -        | _        | -        | 5        | ON/OFF   | OFF mode current sink. This output keeps primary control pin at low level in off mode.                                                          |

| 3        | 3        | 6        | -        | DRIVE    | Combination of FBC and ON/OFF pins                                                                                                              |

## **ABSOLUTE MAXIMUM RATINGS**

| Rating                                        |                                              | Symbol                                                                           | Value                         | Unit |

|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|-------------------------------|------|

| Input Voltage                                 |                                              | V <sub>CC</sub>                                                                  | -0.3 to 40                    | V    |

| DRIVE, ON/OFF, FBC, LED Voltage               |                                              | V <sub>DRIVE</sub> , V <sub>ONOFF</sub> ,<br>V <sub>FBC</sub> , V <sub>LED</sub> | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| VSNS, ISNS, OFFDET, VMIN Voltage              |                                              | V <sub>SNS</sub> , V <sub>ISNS</sub> ,<br>Voffdet, V <sub>MIN</sub>              | -0.3 to 10                    | V    |

| LED Current                                   |                                              | I <sub>LED</sub>                                                                 | 10                            | mA   |

| Thermal Resistance – Junction-to-Air (Note 1) | NCP4353A<br>NCP4353B<br>NCP4354A<br>NCP4354B | R <sub>θJA</sub>                                                                 | 315<br>324<br>260<br>277      | °C/W |

| Junction Temperature                          |                                              | Т <sub>Ј</sub>                                                                   | -40 to 150                    | °C   |

| Storage Temperature                           |                                              | T <sub>STG</sub>                                                                 | -60 to 150                    | °C   |

| ESD Capability, Human Body Model (Note 2)     |                                              | ESD <sub>HBM</sub>                                                               | 2000                          | V    |

| ESD Capability, Machine Model (Note 2)        |                                              | ESD <sub>MM</sub>                                                                | 250                           | V    |

| ESD Capability, Charged Device Model (Note 2) |                                              | ESD <sub>CDM</sub>                                                               | 1000                          | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

50 mm<sup>2</sup>, 1.0 oz. Copper spreader.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per JESD22–A114F

ESD Machine Model tested per JESD22–A114F

ESD Charged Device Model tested per JESD22–C101F

Latchup Current Maximum Rating tested per JESD22–C101F

Latchup Current Maximum Rating tested per JEDEC standard: JESD78D.

#### **ELECTRICAL CHARACTERISTICS**

$0^{\circ}C \leq T_J \leq 125^{\circ}C; \ V_{CC}$  = 15 V; unless otherwise noted. Typical values are at  $T_J$  = +25^{\circ}C.

| Parameter                                 | Test Conditions                                                                                       | Symbol                  | Min   | Тур                 | Max   | Unit |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------|-------|---------------------|-------|------|

| Maximum Operating Input Volt-<br>age      |                                                                                                       | Vcc                     |       |                     | 36.0  | V    |

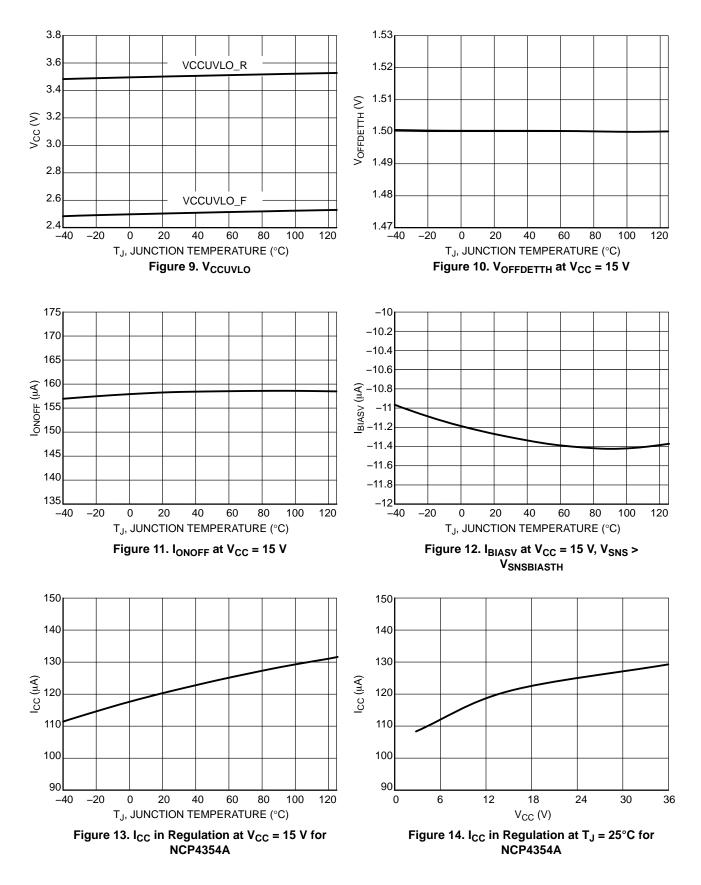

| VCC UVLO                                  | V <sub>CC</sub> rising                                                                                | V <sub>CCUVLO</sub>     | 3.3   | 3.5                 | 3.7   | V    |

|                                           | V <sub>CC</sub> falling                                                                               | -                       | 2.3   | 2.5                 | 2.7   |      |

| VCC UVLO Hysteresis                       |                                                                                                       | V <sub>CCUVLOHYS</sub>  | 0.8   | 1.0                 |       | V    |

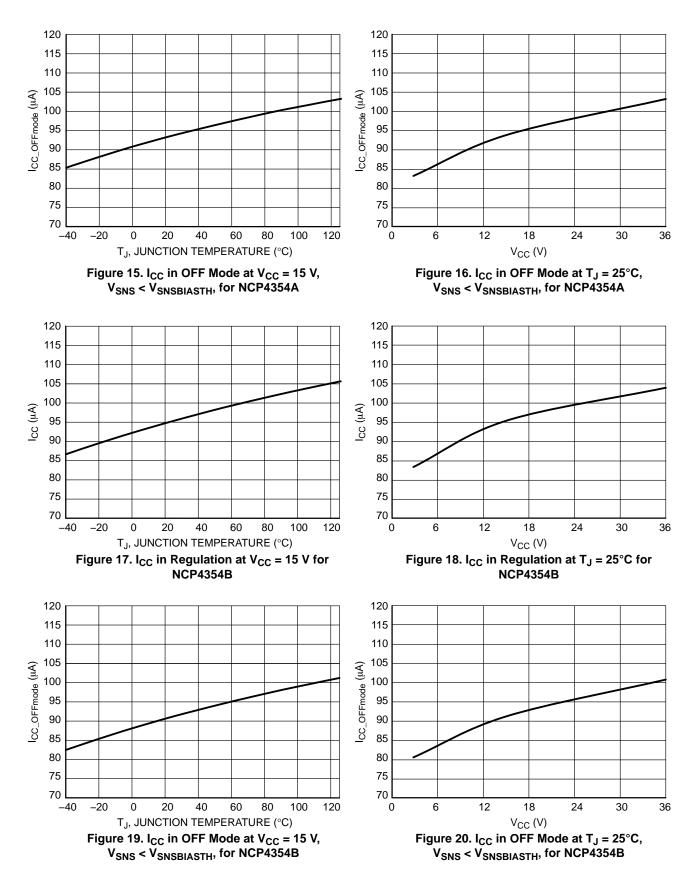

|                                           | NCP4353A                                                                                              | I <sub>CC</sub>         |       | 101                 | 125   | μΑ   |

|                                           | NCP4353B                                                                                              |                         |       | 82                  | 105   |      |

| Quiescent Current in Regulation           | NCP4354A                                                                                              |                         |       | 118                 | 145   |      |

|                                           | NCP4354B                                                                                              |                         |       | 95                  | 120   |      |

| Quiescent Current in OFF Mode             | V <sub>SNS</sub> < 1.12 V                                                                             | I <sub>CC,OFFmode</sub> |       | 90                  | 110   | μA   |

| VOLTAGE CONTROL LOOP OT                   | A                                                                                                     |                         |       |                     |       |      |

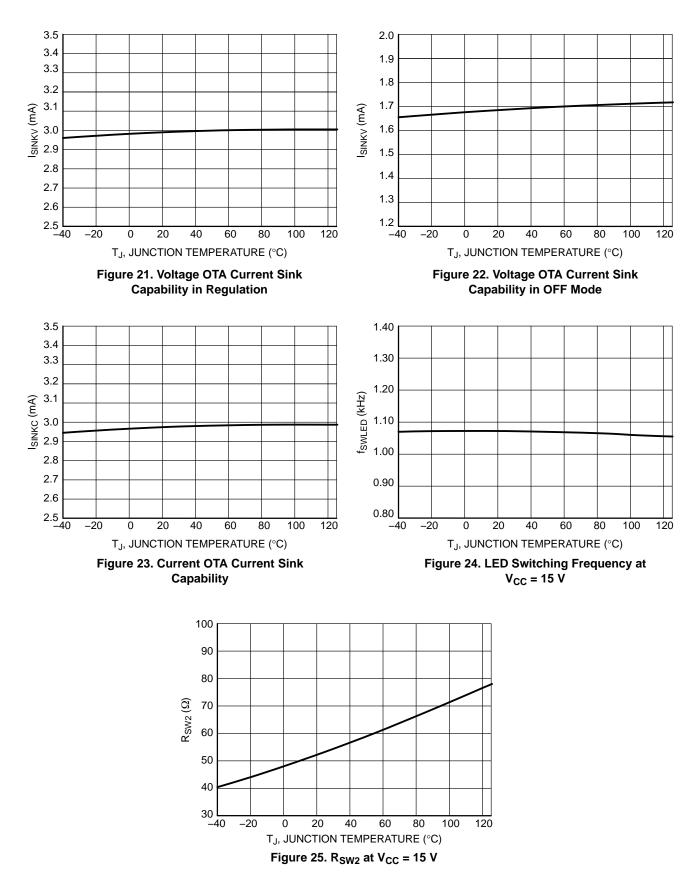

| Transconductance                          | Sink current only                                                                                     | gm <sub>V</sub>         |       | 1                   |       | S    |

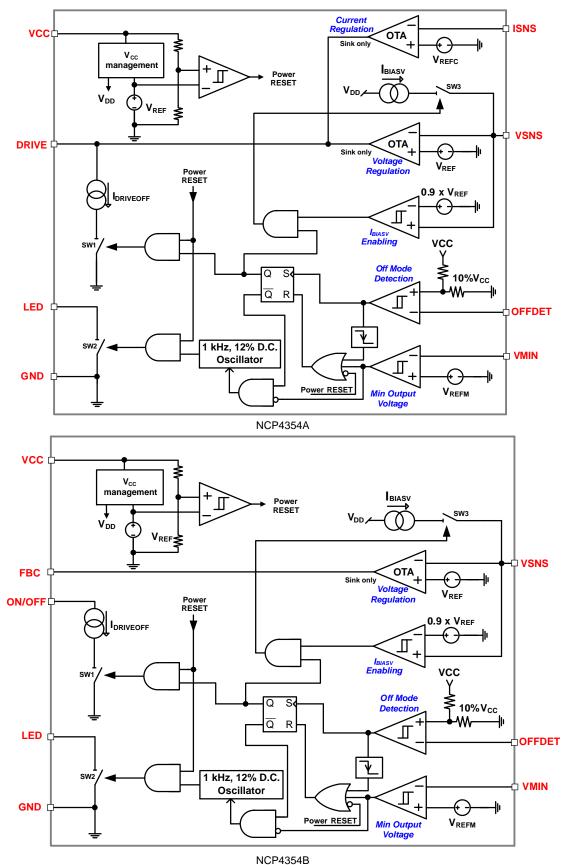

| Reference Voltage                         | 2.8 V $\leq$ V_{CC} $\leq$ 36.0 V, T_J = 25°C                                                         | V <sub>REF</sub>        | 1.244 | 1.250               | 1.256 | V    |

|                                           | $2.8 \text{ V} \leq \text{V}_{CC} \leq 36.0 \text{ V}, \text{ T}_{\text{J}} = 0 - 85^{\circ}\text{C}$ |                         | 1.240 | 1.250               | 1.264 |      |

|                                           | $2.8 \text{ V} \le \text{V}_{CC} \le 36.0 \text{ V}, \text{T}_{J} = 0 - 125^{\circ}\text{C}$          |                         | 1.230 | 1.250               | 1.270 |      |

| Sink Current Capability                   | In regulation, $V_{DRIVE}$ or $V_{FBC} > 1.5 V$                                                       | I <sub>SINKV</sub>      | 2.5   |                     |       | mA   |

|                                           | In OFF mode, $V_{DRIVE}$ or $V_{FBC}$ > 1.5 V                                                         |                         | 1.2   | 1.5                 | 2.0   | mA   |

| Inverting Input Bias Current              | In regulation, V <sub>SNS</sub> = V <sub>REF</sub>                                                    | I <sub>BIASV</sub>      | -100  |                     | 100   | nA   |

|                                           | In OFF mode, V <sub>SNS</sub> > 1.12 V                                                                |                         | -13   | -11                 | -10   | μA   |

| Inverting Input Bias Current<br>Threshold | In OFF mode                                                                                           | V <sub>SNSBIASTH</sub>  | 1.07  | 1.12                | 1.17  | V    |

| CURRENT CONTROL LOOP OT                   | A (NCP435xA only)                                                                                     |                         |       |                     |       |      |

| Transconductance                          | Sink current only                                                                                     | gm <sub>C</sub>         |       | 3                   |       | S    |

| Reference Voltage                         |                                                                                                       | V <sub>REFC</sub>       | 60    | 62.5                | 65    | mV   |

| Sink Current Capability                   | $V_{DRIVE}$ or $V_{FBC} > 1.5 V$                                                                      | I <sub>SINKC</sub>      | 2.5   |                     |       | mA   |

| Inverting Input Bias Current              | I <sub>SNS</sub> = V <sub>REFC</sub>                                                                  | I <sub>BIASC</sub>      | -100  |                     | 100   | nA   |

| MINIMUM VOLTAGE COMPARA                   | TOR (except NCP4353A)                                                                                 |                         |       |                     |       |      |

| Threshold Voltage                         |                                                                                                       | V <sub>REFM</sub>       | 355   | 377                 | 400   | mV   |

| Hysteresis                                | Output change from logic high to logic low                                                            | V <sub>MINH</sub>       |       | 40                  |       | mV   |

| OFF MODE DETECTION COMPA                  | ARATOR                                                                                                |                         |       |                     |       |      |

| Threshold Value                           | $2.5~\textrm{V} \leq \textrm{V}_{\textrm{CC}} \leq 36.0~\textrm{V}$                                   | V <sub>OFFDETTH</sub>   |       | 10% V <sub>CC</sub> |       | V    |

|                                           | V <sub>CC</sub> = 15 V                                                                                |                         | 1.47  | 1.50                | 1.53  | 1    |

| Hysteresis                                | Output change from logic high to logic low                                                            | V <sub>OFFDETH</sub>    |       | 40                  |       | mV   |

| LED DRIVER (NCP4354x only)                |                                                                                                       |                         |       |                     |       |      |

| Switching Frequency                       |                                                                                                       | f <sub>SWLED</sub>      |       | 1                   |       | kHz  |

| Duty Cycle                                |                                                                                                       | D <sub>LED</sub>        | 10.0  | 12.5                | 15.0  | %    |

| Switch Resistance                         | I <sub>LED</sub> = 5 mA                                                                               | R <sub>SW2</sub>        |       | 50                  |       | Ω    |

| OFF MODE CONTROL                          |                                                                                                       |                         |       |                     |       |      |

| Sink Current                              | In OFF mode, V <sub>DRIVE</sub> or V <sub>ONOFF</sub> > 0.6 V                                         | IDRIVEOFF               | 140   | 160                 | 180   | μA   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### APPLICATION INFORMATION

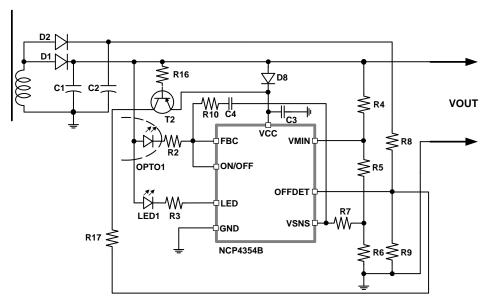

A typical application circuit for NCP435x series is shown in Figure 28, done with an imaginary IC with all features in one. Pin functions are available in pin description table.

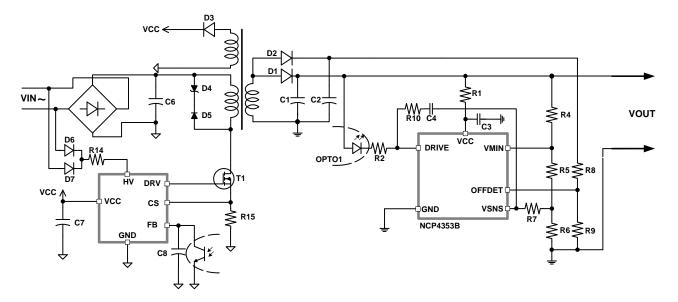

Simplified typical application circuit for NCP4353B that shows only available features in this IC is shown in Figure 27. Figure 29 shows possible connection of the NCP4353B to flyback primary controller.

IC will be derived in multiple versions with different features for each of them.

#### **Power Supply**

The NCP435x is designed to operate from a single supply up to 36 V. It starts to operate when VCC voltage reaches 3.5 V and stops when VCC voltage drops below 2.5 V.  $V_{CC}$ can be supplied by direct connection to the VOUT voltage of the power supply. It is highly recommended to add a RC filter (R1 and C3) in series from VOUT to VCC pin to reduce voltage spikes and drops that are produced at the converter's output capacitors. Recommended values for this filter are 220  $\Omega$  and 1  $\mu$ F.

#### **Voltage Regulation Path**

The output voltage is detected on the VSNS pin by the R4, R5 and R6 voltage divider. This voltage is compared with the internal precise voltage reference. The voltage difference is amplified by  $gm_V$  of the transconductance amplifier. The amplifier output current is connected to the FBC or DRIVE pin. The compensation network is also connected to this pin to provide frequency compensation for the voltage regulation path. This FBC (DRIVE) pin drives regulation optocoupler that provides regulation of primary side. The optocoupler is supplied via direct connection to VOUT line through resistor R2.

Regulation information is transferred through the optocoupler to the primary side controller where its FB pin is usually pulled down to reduce energy transferred to secondary output.

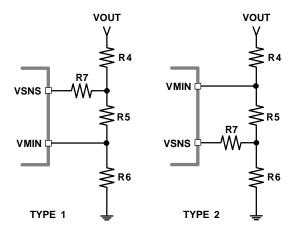

The VSNS voltage divider is shared with VMIN voltage divider. The shared voltage divider can be connected in two ways as shown in Figure 26. The divider type is selected based on the ratio between  $V_{\rm MIN}$  and  $V_{\rm OUT}$ . When the condition of Equation 1 is true, divider type 1 should be used.

$$V_{MIN} > \frac{V_{OUT} \times V_{REFM}}{V_{REF}}$$

(eq. 1)

Output voltage for divider type 1 can be computed by Equation 2

$$V_{OUT} = V_{REF} \times \frac{R4 + R5 + R6}{R5 + R6}$$

(eq. 2)

and for type 2 by Equation 3.

$$V_{OUT} = V_{REF} \times \frac{R4 + R5 + R6}{R6} \qquad (eq. 3)$$

Figure 26. Shared Dividers Type

#### **Current Regulation Path (A versions only)**

The output current is sensed by the shunt resistor R12 in series with the load. Voltage drop on R12 is compared with internal precise voltage reference  $V_{REFC}$  at  $I_{SNS}$  transconductance amplifier input.

Voltage difference is amplified by  $gm_C$  to output current of amplifier, connected to FBC or DRIVE pin. Compensation network is connected between this pin and ISNS input to provide frequency compensation for current regulation path. Resistor R13 separates compensation network from sense resistor. Compensation network works into low impedance without this resistor that significantly decreases compensation network impact.

Current regulation point is set to current given by Equation 4.

$$I_{OUTLIM} = \frac{V_{REFC}}{R12}$$

(eq. 4)

#### **OFF Mode Detection**

OFF mode operation is advantageous for ultra low or zero output current condition. The very long off time and the ultra low power mode of the whole regulation system greatly reduces the overall consumption.

The output voltage is varying between nominal and minimal in OFF mode. When output voltage decreases below set (except NCP4353A) minimum level, primary controller is switched on until output capacitor C1 is charged again to the nominal voltage.

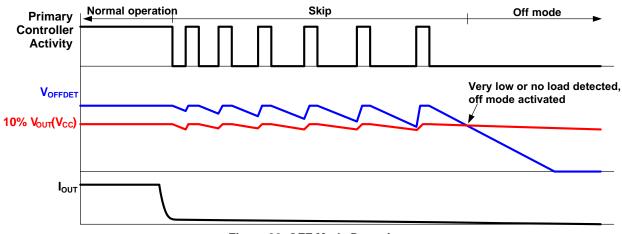

The OFF mode detection is based on comparison of output voltage and voltage loaded with fixed resistances (D2, C2, R8 and R9). Figure 30 shows detection waveforms. When output voltage is loaded with very low current, primary controller goes into skip mode (primary controller stops switching for some time). While output capacitor C1 is discharged very slowly (no load condition), the capacitor C2

is discharged through a fixed load, by R8 and R9 faster than output voltage on C1.

Once OFFDET pin voltage is lower than  $V_{OFFDETTH}$  (this threshold is derived from  $V_{OUT}$ ), OFF mode is detected. In OFF mode SW1 is switched on to allow  $I_{DRIVEOFF}$  current, going through ON/OFF pin (NCP4354B) or DRIVE pin, to keep switch off primary controller.

A higher sink current on primary FB pin is needed to keep primary controller FB below the skip level until the OFF mode is detected on primary side.

Despite output voltage on C1 may go down, the current  $I_{BIASV}$  injected into VSNS pin provides the requested offset (VSNS voltage is higher than  $V_{REF}$ ). Primary IC should detect OFF mode before VSNS is lower than 90% of  $V_{REF}$  while  $I_{BIASV}$  is switched off to reduce consumption.

This offset, defined by R7 and the internal current source, should be large enough to secure off mode detection of the primary controller and avoid restart when  $V_{SNS} < V_{REF}$ .

# Minimum Output Voltage Detection (Except NCP4353A)

Minimum output voltage level defines primary controller restart from OFF mode. It can be set by shared voltage divider with voltage regulation loop. When VMIN voltage drops below  $V_{REFM}$ , OFF mode is ended and primary controller restarts.

Minimum voltage level is given by Equation 5 for divider type 1

$$V_{MIN} = V_{REF} \times \frac{R4 + R5 + R6}{R6} \qquad (eq. 5)$$

and for type 2 by Equation 6.

$$V_{MIN} = V_{REF} \times \frac{R4 + R5 + R6}{R5 + R6}$$

(eq. 6)

NCP4353A has no external adjustment and uses the internal minimum voltage level specified by minimum falling operation supply voltage.

#### LED Driver (NCP4354x only)

LED driver is active when VCC is higher than  $V_{CCMIN}$  and output voltage is in regulation (driver is off in OFF mode). LED driver consists of an internal power switch controlled by a PWM modulated logic signal and an external current limiting resistor R3. LED current can be computed by Equation 7.

$$I_{LED} = \frac{V_{OUT} - V_{F\_LED}}{R3}$$

(eq. 7)

PWM modulation is used to increase efficiency of LED.

#### **Operation in OFF Mode Description**

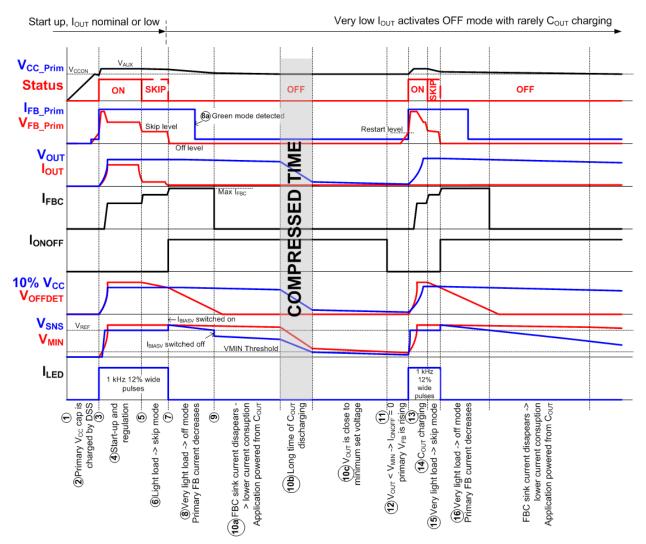

Operation waveforms in off mode and transition into OFF mode with NCP1246 primary controller are shown in Figure 31.

Figure shows waveforms from the first start (1) of the convertor. At first, primary controller's DSS charges VCC capacitor over the UVLO level (2). When primary  $V_{CC}$  is

over UVLO level (3), primary controller starts to operate. VCC capacitor is charged above DSS level from auxiliary winding,  $V_{OUT}$  is slowly rising according to primary controller start up ramp to nominal voltage (4).

Primary FB pin voltage is above regulation range until  $V_{OUT}$  is at set level. Once  $V_{OUT}$  is at set level, the secondary controller starts to sink current from optocoupler LED's and primary FB voltage is stabilized in regulation region. With nominal output power (without skip mode) OFFDET pin voltage is higher than  $V_{OFFDETTH}$  (typically 10% of  $V_{CC}$ ).

After some time, the load current decreases to low level (5) and primary convertor uses skip mode (6) to keep regulation of output voltage at set level. The skip mode consists of few switching cycles followed by missing ones to provide limited energy by light load. The number of missing cycles allows regulation for any output power.

While both C1 and C2 are discharged during the missing cycles, C2 discharge will be faster than C1 without output current, VOFFDET drops below VOFFDETTH and OFF mode is detected (7). This situation is shown in Figure 30 in detail. When OFF mode is detected, internal pull-up current IBIASV is switch on (7), VSNS voltage increases (due to IBIASV) and voltage amplifier sinks full current to keep primary FB voltage below skip level until OFF mode is detected by the primary side controller (8). Current into ONOFF pin or DRIVE pin begins to flow at the same time, when entering into OFF mode (7). When OFF mode is detected by primary side controller (8a), primary FB injected current decreases to a lower level to reduce overall power consumption. Optocoupler current, can also be reduced from that time to keep the level below restart level. Secondary side controller decreases optocoupler current (voltage transconductance amplifier stops to sink current) when VSNS voltage drops below VREF (9) and IBIASV is also switch off when  $V_{SNS}$  is lower than 90% of  $V_{REF}$  to reduce overall consumption. This point is defined by IBIASV current, R6, R4 and R5 resistors and discharging time of output capacitor C1. Discharging of C1 continues (10) until output voltage drops below level set by voltage divider at VMIN pin (except NCP4353A where minimum V<sub>OUT</sub> is defined only by VCC UVLO) (11). ONOFF current stops and thanks to internal pull-up, the primary FB voltage rises above restart level (12) and primary controller starts switching (13). Output capacitor C1 is recharged (14) to set voltage. If there is still light load condition primary controller goes to skip mode (15) again and after some time secondary controller detects OFF mode by very light or no load condition (16) and whole cycle is repeated.

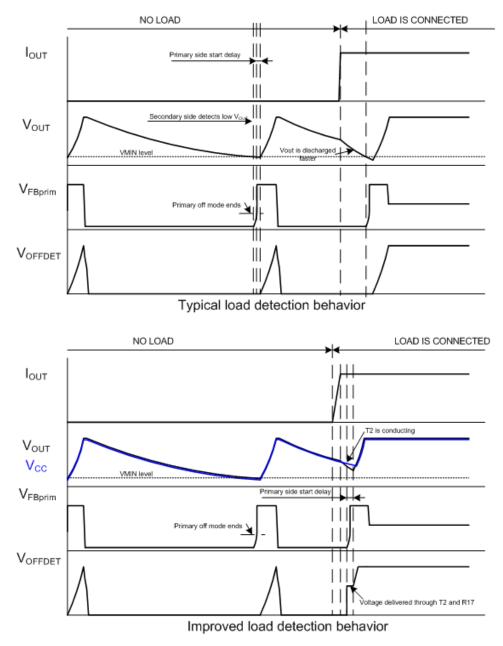

#### Fast Restart From OFF Mode

The IC ends OFF mode when a load is connected to the output and  $V_{OUT}$  is discharged to  $V_{MIN}$  level. There exists another connection that allows transition to normal mode faster without waiting some time for  $V_{OUT}$  to discharge to  $V_{MIN}$ . This schematic is shown at Figure 32. The basic idea is that C3 is discharged by the IC faster than C1 by output

load in OFF mode. When an output load is applied, capacitor C1 is discharged faster and this creates a voltage drop at D8. When there is enough voltage at D8, T2 is opened and current is injected into the OFFDET divider through R17. OFFDET voltage higher than 10% of  $V_{CC}$  ends OFF mode and ON/OFF current stops. Primary controller leaves OFF

mode because voltage at its FB pin rises above OFF mode end level and switching resumes.

Normal operation waveforms for typical load detection connection and improved load detection waveforms are shown in Figure 33.

Figure 27. Typical Application Schematic for NCP4353B

Figure 28. Typical Application Schematic for All Features

Figure 29. Typical Application Schematic for NCP4353B with Flyback

Figure 30. OFF Mode Detection

Figure 31. Typical Application States and Waveforms in OFF Mode with NCP1246 Primary Controller

Figure 32. Improved Load Detection Connection

Figure 33. Typical and Improved Load Detection Comparison Waveforms

#### **ORDERING INFORMATION**

| Device        | Marking  | Adjustable<br>V <sub>min</sub> | Current<br>Regulation | LED<br>Driver | Package             | Shipping <sup>†</sup> |

|---------------|----------|--------------------------------|-----------------------|---------------|---------------------|-----------------------|

| NCP4353ASNT1G | A53      | No                             | Yes                   | No            | TSOP–6<br>(Pb–Free) | 3000 / Tape & Reel    |

| NCP4353BSNT1G | B53      | Yes                            | No                    | No            | TSOP–6<br>(Pb–Free) | 3000 / Tape & Reel    |

| NCP4354ADR2G  | NCP4354A | Yes                            | Yes                   | Yes           | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP4354BDR2G  | NCP4354B | Yes                            | No                    | Yes           | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# onsemi

TSOP-6 CASE 318G-02 ISSUE V DATE 12 JUN 2012 SCALE 2:1 NOTES: D 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. 2 Η MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM З. LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D 4 ¥ 12 4 GAUGE E1 Е AND E1 ARE DETERMINED AT DATUM H. 5. PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE. 2 4 MILLIMETERS М NOTE 5 b DIM MIN NOM MAX 0.90 1.10 DETAIL Z Α 1.00 A1 0.01 0.06 0.10 b 0.25 0.38 0.50 с 0.10 0 18 0.26 D 2.90 3.00 3.10 С Е 2.50 2.75 Α 3.00  $|\cap$ 0.05 E1 1.30 1.50 1.70 e L 0.85 0.95 1.05 0.40 0.20 0.60 Δ1 L2 M 0.25 BSC DETAIL Z 10° 0 STYLE 2: PIN 1. EMITTER 2 2. BASE 1 STYLE 3: PIN 1. ENABLE 2. N/C STYLE 4: PIN 1. N/C 2. V in STYLE 5: PIN 1. EMITTER 2 2. BASE 2 STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR STYLE 1: PIN 1. DRAIN 2. DRAIN COLLECTOR 1 EMITTER 1 3. GATE 4. SOURCE З. 3. R BOOST 4. Vz 3. NOT USED 4. GROUND 3. COLLECTOR 1 4. EMITTER 1 3. BASE 4. EMITTER 4. 5. ENABLE 6. LOAD 5. COLLECTOR 6. COLLECTOR 5. DRAIN 5. BASE 2 5. V in 5. BASE 1 6. V out 6. COLLECTOR 2 6. COLLECTOR 2 6. DRAIN STYLE 10: STYLE 11: STYLE 8: STYLE 9: STYLE 12: STYLE 7 PIN 1. COLLECTOR PIN 1. Vbus PIN 1. LOW VOLTAGE GATE PIN 1. D(OUT)+ PIN 1. SOURCE 1 PIN 1. I/O 2. DRAIN 2 2. GROUND 2. COLLECTOR 2. D(in) 2. DRAIN 2. GND 3. D(in)+ 4. D(out)+ 3. SOURCE 4. DRAIN 3. D(OUT)-4. D(IN)-3. BASE DRAIN 2 3. I/O З. 4 N/C 4 I/O 4 SOURCE 2 5. COLLECTOR 5. D(out) 6. GND 5. 5. VBUS 6. D(IN)+ 5. GATE 1 6. DRAIN 1/GATE 2 5. VCC 6. I/O DRAIN 6. HIGH VOLTAGE GATE 6. EMITTER STYLE 13: PIN 1. GATE 1 STYLE 14: PIN 1. ANODE STYLE 15: PIN 1. ANODE STYLE 16: PIN 1. ANODE/CATHODE STYLE 17: PIN 1. EMITTER 2. SOURCE 2 2. SOURCE 2. SOURCE 2. BASE 2. BASE 3 EMITTER 3 ANODE/CATHODE 3. GATE 2 3 GATE 3 GATE 4. DRAIN 2 4. CATHODE/DRAIN 4. DRAIN 4 COLLECTOR ANODE 5. CATHODE/DRAIN CATHODE 5. SOURCE 1 5. N/C 5. ANODE 5. DRAIN 1 6. CATHODE/DRAIN 6. CATHODE CATHODE COLLECTOR 6. 6. 6. GENERIC RECOMMENDED **MARKING DIAGRAM\*** SOLDERING FOOTPRINT\* 0.60 XXXAYW= XXX M= 0 o 1LI 6X 3.20 IC STANDARD 0.95 XXX = Specific Device Code XXX = Specific Device Code А =Assembly Location Μ = Date Code Y = Pb-Free Package = Year W = Work Week 0.95 = Pb-Free Package PITCH DIMENSIONS: MILLIMETERS \*This information is generic. Please refer to device data \*For additional information on our Pb-Free strategy and soldering sheet for actual part marking. Pb-Free indicator, "G" details, please download the ON Semiconductor Soldering and or microdot "•", may or may not be present. Some Mounting Techniques Reference Manual, SOLDERRM/D. products may not follow the Generic Marking. Electronic versions are uncontrolled except when accessed directly from the Document Repository. DOCUMENT NUMBER: 98ASB14888C Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

TSOP-6

PAGE 1 OF 1

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular

purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation

special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

© Semiconductor Components Industries, LLC, 2019

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                     | 98ASB42564B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B42564B Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DESCRIPTION: SOIC-8 NB PAGE 1 OF 2                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                           |  |  |  |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume ar | onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                                                                                                                                                                                           |  |  |  |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |  |  |  |

|                  |                                                                                                                                                                                                 |  |             |  |  |  |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>