# onsemi

# Current Mode PWM Controller

# NCP12711

The NCP12711 is a fixed-frequency peak-current-mode PWM controller containing all of the features necessary for implementing single-ended power converter topologies. The device operates from 4 V to 45 V without auxiliary winding and within its thermal capabilities. The controller contains a programmable oscillator capable of operating from 100 kHz to 1 MHz and integrates slope compensation to prevent subharmonic oscillations. The controller includes a programmable soft-start, input voltage UVLO protection, and an over-power protection (OPP) circuit which limits the total power capability of the circuit as the input voltage increases. The UVLO pin also features a shutdown comparator which allows for an external signal to disable switching and brings the controller into a low quiescent state. An onboard op-amp allows the implementation of primary-side regulated converters or non-isolated dc-dc converters.

The NCP12711 contains a suite of protection features including cycle-by-cycle peak-current limiting with smooth frequency increase and a timer-based overload protection. All protection features place the device into a low quiescent fault mode with a 1-s auto-recovery period to allow for system recovery if the fault condition is removed.

#### **Common General Features**

- Wide V<sub>cc</sub> Input Range (4 45 V)

- Internal 7.5–V Regulator

- Current–Mode Control with Adjustable Slope Compensation

- 0% Duty Ratio Operation in No-Load Condition

- Internal Over Power Protection

- Single Resistor Programmable Oscillator 100 kHz to 1 MHz

- Adjustable Soft-Start on Peak Current and Frequency

- Programmable Input Voltage UVLO with Hysteresis

- Shutdown Threshold for External Disable

- Overload Protection with 30 ms Overload Timer

- Internal Operational Amplifier

- Fault Auto-recovery Mode with 1-s Auto-recovery Period

- ±1 A Source / Sink Gate Driver

#### **Typical Applications**

- Single–ended Flyback and Forward Converters for Electric Vehicles

- 4 45 V Input DC/DC Controller for Auxiliary Power

MSOP10, 3x3 CASE 846AE

#### **ORDERING INFORMATION**

| Device         | Package                  | Shipping <sup>†</sup>  |

|----------------|--------------------------|------------------------|

| NCP12711ADNR2G | MSOP10, 3x3<br>(Pb–Free) | 2,500 / Tape<br>& Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

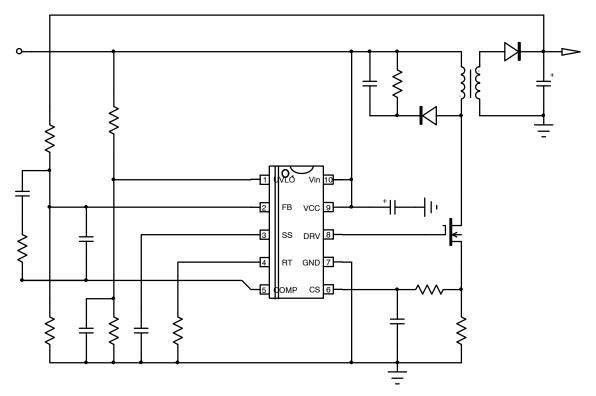

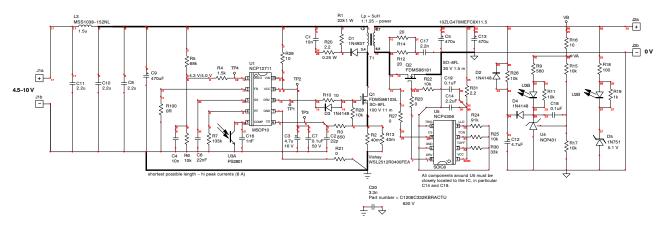

Figure 1. Low-Dissipation Wide-Range Application Non-Isolated Converter

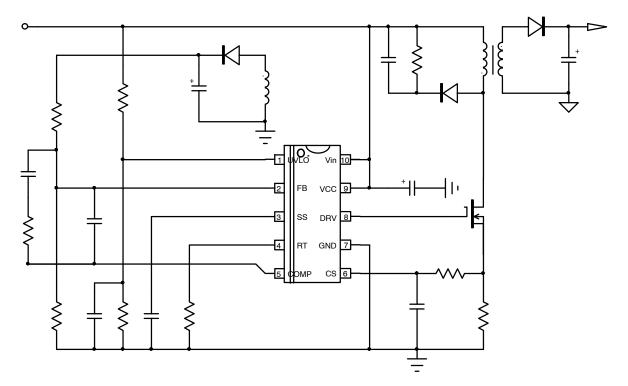

Figure 2. Primary–Side–Regulated Wide–Range–Application Isolated Converter

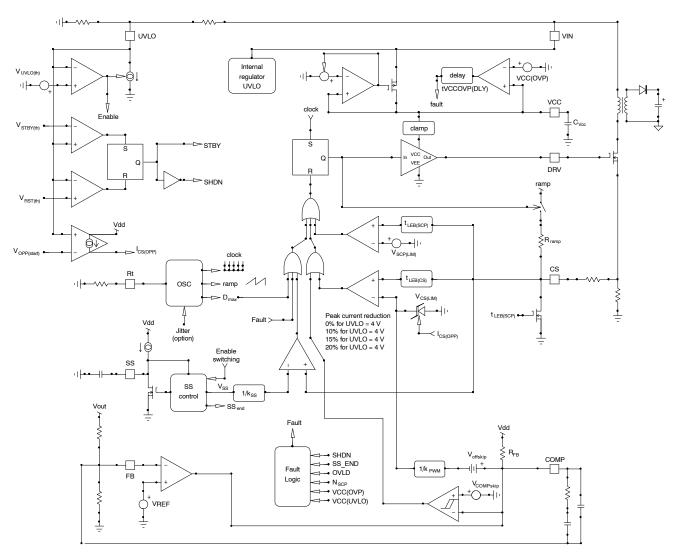

Figure 3. Block Diagram

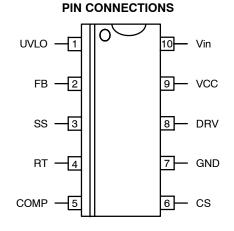

#### **PIN DESCRIPTION**

| DFNW10 | Pin Name | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | UVLO     | The UVLO pin is the input to the standby and UVLO comparators. A resistor divider between the power supply input voltage and ground is connected to the UVLO pin to set the input voltage level at which the controller will be enabled. UVLO hysteresis is set by a 5-µA pull-down current source. An externally-supplied pull-down signal can also be used to disable the controller. The UVLO pin is also used to determine the over-power protection amount. |

| 2      | FB       | The FB pin senses the voltage to be regulated via a resistive divider. A passive network connected between this pin and COMP allows to set poles and zeroes as suggested by the compensation strategy.                                                                                                                                                                                                                                                           |

| 3      | SS       | A capacitor on this pin sets the soft-start sequence during which the peak current setpoint is gradually increased as well as the switching frequency.                                                                                                                                                                                                                                                                                                           |

| 4      | RT       | The RT pin sets the oscillator frequency in the controller. This pin requires a resistor to ground closely located to the controller. Typical $R_T$ resistor values are in the range of 10 k $\Omega$ – 150 k $\Omega$ .                                                                                                                                                                                                                                         |

| 5      | COMP     | This is the op-amp output pin, loaded by the R <sub>FB</sub> resistance.                                                                                                                                                                                                                                                                                                                                                                                         |

| 6      | CS       | The CS pin is the current sense input for the PWM and current limit comparators. An external low-pass filter is recommended for improved noise immunity. The external filter resistor is also used to determine the amount of compensation ramp added to the current sense information.                                                                                                                                                                          |

| 7      | GND      | This pin is the controller ground.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8      | DRV      | The DRV pin is a high current output used to drive the external MOSFET gate. DRV has source and sink capability of 1 A.                                                                                                                                                                                                                                                                                                                                          |

| 9      | VCC      | The VCC pin provides bias to the controller via a linear regulator. An external decoupling capacitor to ground in the range of 1 – 10 $\mu$ F is recommended. An auxiliary winding can help turn off the regulator and improve power dissipation in wide input range applications.                                                                                                                                                                               |

| 10     | VIN      | This is the controller supply input. If kept below $V_{CC(OVP)}$ it can be safely connected to VCC.                                                                                                                                                                                                                                                                                                                                                              |

#### **MAXIMUM RATINGS**

| Symbol                | Rating                                                                                                                                   | Value                                   | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| V <sub>in(MAX)</sub>  | Supply Voltage (Continuous)                                                                                                              | -0.3 to 45                              | V    |

| I <sub>CC(MAX)</sub>  | Supply Current<br>V <sub>in</sub> = 12 V<br>V <sub>in</sub> = 45 V                                                                       | 35<br>10                                | mA   |

| V <sub>CC(MAX)</sub>  | VCC pin                                                                                                                                  | -0.3 to 30                              | V    |

| V <sub>DRV(MAX)</sub> | DRV Voltage (Note 1)                                                                                                                     | –0.3 V to V <sub>DRV(high)</sub>        | V    |

| I <sub>DRV(MAX)</sub> | DRV Current (Peak)                                                                                                                       | 1.25                                    | А    |

| V <sub>SIG(MAX)</sub> | Max Voltage on Signal Pins $V_{Vcc} > 5.5 V$<br>$V_{Vcc} < 5.5 V$                                                                        | –0.3 to 5.5<br>–0.3 to V <sub>Vcc</sub> | V    |

| I <sub>SIG(MAX)</sub> | Max Current on Signal Pins                                                                                                               | 10                                      | mA   |

| $R_{\theta J-A}$      | Thermal Resistance Junction-to-Air                                                                                                       | 139                                     | °C/W |

| $\Psi_{\theta J-T}$   | Junction-to-Top Thermal Characterization Parameter                                                                                       | 5.5                                     | °C/W |

| $\Psi_{\theta J-B}$   | Junction-to-Board Thermal Characterization Parameter                                                                                     | 68.4                                    | °C/W |

| T <sub>JMAX</sub>     | Maximum Junction Temperature                                                                                                             | 150                                     | °C   |

| T <sub>STG</sub>      | Storage Temperature Range                                                                                                                | -55 to 150                              | °C   |

| TJ                    | Operating Temperature Range                                                                                                              | -40 to 125                              | °C   |

|                       | ESD Capability (Notes 2, 3)<br>Human Body Model per JEDEC Standard JESD22-A114E.<br>Charge Device Model per JEDEC Standard JESD22-C101E. | 2000<br>1000                            | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Maximum driver voltage is limited by the driver clamp voltage, V<sub>DRV(high)</sub>, when V<sub>CC</sub> exceeds the driver clamp voltage. Otherwise, the maximum driver voltage is V<sub>CC</sub>.

This device series contains ESD protection and exceeds the following tests: Human Body Model 2000 V per JEDEC Standard JESD22-A114E

Charge Device Model 1000 V per JEDEC Standard JESD22-C101E

3. This device contains latch-up protection and has been tested per JEDEC JESD78D, Class I and exceeds ±100 mA.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Rating                      | Value      | Unit |

|-----------------|-----------------------------|------------|------|

| V <sub>in</sub> | Supply Voltage              | 4.5 – 40   | V    |

| TJ              | Operating Temperature Range | -40 to 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>IN</sub> = 12 V, V <sub>CC</sub> = 12 V, V <sub>COMP</sub> = open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = 0 V, V <sub>S</sub> | pen, |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $V_{UVLO} = 1.2 V$ , $V_{FB} = 0 V$ , for typical values $T_J = 25^{\circ}$ C, for min/max values, $T_J$ is $-40^{\circ}$ C to $125^{\circ}$ C, unless otherwise noted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Symbol                                                                                         | Characteristics                                                                                                                                       | Test Condition                                                                                                          | Min                      | Тур                               | Max                                  | Unit                       |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|--------------------------------------|----------------------------|

| SUPPLY CIRC                                                                                    | UIT                                                                                                                                                   |                                                                                                                         |                          |                                   |                                      |                            |

| V <sub>CC(reg)</sub><br>V <sub>in(STR)</sub><br>V <sub>in(MIN)</sub><br>V <sub>CC(reset)</sub> | Supply Voltage<br>V <sub>cc</sub> Regulation Level<br>Start-up Level (Part Switches)<br>Minimum Operating Voltage<br>Reset Voltage (All Faults Clear) | $I_{CC} = -5 \text{ mA}$<br>$V_{in}$ increasing<br>$V_{in}$ decreasing<br>$V_{CC}$ decreasing                           | 7.0<br>3.5<br>3.3<br>3.0 | 7.5<br>3.7<br>3.5<br>3.3          | 8.0<br>3.95<br>3.75<br>3.6           | ><br>><br>><br>>           |

| V <sub>IN(hys)</sub>                                                                           | Hysteresis between $V_{in(STR)}$ and $V_{in(MIN)}$                                                                                                    |                                                                                                                         | -                        | 200                               | -                                    | mV                         |

| I <sub>start</sub>                                                                             | Start-up Current                                                                                                                                      | $V_{CC} = V_{CC(reg)} - 0.2 V$                                                                                          | 15                       | 20                                | -                                    | mA                         |

| I <sub>VIN(LIM)</sub>                                                                          | Start-up Current with V <sub>cc</sub> = 0 V                                                                                                           | $V_{cc}$ pin shorted to ground                                                                                          | -                        | 2.5                               | -                                    | mA                         |

| V <sub>CC(SC)</sub>                                                                            | V <sub>CC</sub> Threshold for Non–Short Circuit Detection                                                                                             |                                                                                                                         | -                        | 0.2                               | -                                    | V                          |

| I <sub>Vin(off)</sub>                                                                          | Start-up Circuit Off-State Leakage Current                                                                                                            | V <sub>in</sub> = 45 V                                                                                                  | -                        | -                                 | 95                                   | μA                         |

| V <sub>CC(OVP)</sub>                                                                           | Supply Over-Voltage Protection                                                                                                                        |                                                                                                                         | 25                       | 27                                | 29                                   | V                          |

| V <sub>CC(OVP_HYS)</sub>                                                                       | Hysteresis on Supply OVP                                                                                                                              |                                                                                                                         | -                        | 100                               | -                                    | mV                         |

| t <sub>VCCOVP(DLY)</sub>                                                                       | VCC OVP Detection Filter Delay                                                                                                                        |                                                                                                                         | -                        | 7                                 | -                                    | μs                         |

| ICC(SHDN)<br>ICC(STBY)<br>ICC(SHDNVI)<br>ICC(STBYVI)<br>ICC(EN)<br>ICC(FLT)                    | Supply Current<br>SHDN (VCC Pin)<br>STBY (VCC Pin)<br>SHDN (VIN and VCC Pins Shorted)<br>STBY (VIN and VCC Pins Shorted)<br>Enable<br>Fault           | $V_{UVLO} = 0 V$ $V_{UVLO} = 0.4 V$ $V_{UVLO} = 0 V$ $V_{UVLO} = 0.4 V$ $C_{DRV} = Open, V_{COMP} = 2 V$ $V_{CS} = 0 V$ | -<br>-<br>-<br>-         | 60<br>340<br>104<br>380<br>-<br>- | 120<br>650<br>170<br>700<br>4<br>500 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

#### **CURRENT SENSE**

| V <sub>CS(LIM)</sub>  | Current Limit Comparator Threshold                     |                                               | 237  | 250  | 263  | mV |

|-----------------------|--------------------------------------------------------|-----------------------------------------------|------|------|------|----|

| t <sub>CS(DLY)</sub>  | Propagation Delay From Current Sense Limit to DRV Low  | Step $V_{CS}$ from 0 – 0.35 V                 | -    | 25   | 75   | ns |

| V <sub>SCP(LIM)</sub> | Short Circuit Protection (SCP) Current Limit Threshold |                                               | -    | 325  | -    | mV |

| t <sub>SCP(DLY)</sub> | Propagation Delay From Short Circuit Limit to DRV Low  | Step $V_{CS}$ from 0 – 0.44 V                 | -    | 25   | 75   | ns |

| t <sub>on,min</sub>   | Minimum On-time Duration                               |                                               | -    | 135  | 170  | ns |

| N <sub>SCP</sub>      | Short Circuit Counter                                  | V <sub>CS</sub> = 1 V                         | -    | 4    | -    |    |

| t <sub>LEB(CS)</sub>  | CS Leading Edge Blanking (LEB)                         |                                               | 60   | 110  | 155  | ns |

| t <sub>LEB(SCP)</sub> | SCP Leading Edge Blanking                              |                                               | 35   | 60   | 90   | ns |

| R <sub>PD(LEB)</sub>  | CS LEB Pull-down Resistance                            |                                               | -    | 27   | 55   | Ω  |

| t <sub>CS(OVLD)</sub> | Overload Timer Duration                                | V <sub>CS</sub> > 0.25 V                      | 22.5 | 28.5 | 34.5 | ms |

| V <sub>CS(skip)</sub> | CS Skip Threshold in % of the Max CS Level             | 0% duty ratio –<br>V <sub>COMP</sub> < 325 mV | -    | 0    | -    | %  |

| V <sub>ramp</sub>     | Compensation Ramp Peak Level                           |                                               | 1.55 | 1.8  | 2.05 | V  |

| R <sub>ramp</sub>     | Internal Ramp Resistance to CS Pin                     |                                               | 15   | 21   | 27   | kΩ |

| <b>ELECTRICAL CHARACTERISTICS</b> ( $V_{IN} = 12 V$ , $V_{CC} = 12 V$ , $V_{COMP} = open$ , $C_{DRV} = 1 nF$ , $R_T = 53.6 k\Omega$ , $V_{CS} = 0 V$ , $V_{SS} = Open$ , $V_{UVLO} = 1.2 V$ , $V_{FB} = 0 V$ , for typical values $T_J = 25^{\circ}$ C, for min/max values, $T_J is - 40^{\circ}$ C to 125°C, unless otherwise noted) (continued) |                 |                |     |     |     |      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-----|-----|-----|------|--|--|--|

| Symbol                                                                                                                                                                                                                                                                                                                                            | Characteristics | Test Condition | Min | Тур | Max | Unit |  |  |  |

| COMP SECTIO                                                                                                                                                                                                                                                                                                                                       | COMP SECTION    |                |     |     |     |      |  |  |  |

| K <sub>PWM</sub>                     | PWM to COMP Gain Through Resistor Divider                   | V <sub>COMP</sub> = 1.25 V / 2.9 V                            | 7.6          | 8.0         | 8.4          |        |

|--------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------|--------------|-------------|--------------|--------|

| t <sub>PWM(Dly)</sub>                | Propagation Delay to DRV Low (Note 6)                       | $V_{COMP}$ = 2 V,<br>Step V <sub>CS</sub> 0 – 0.35 V          | -            | 25          | 75           | ns     |

| V <sub>offskip</sub>                 | Internal Feedback Offset                                    |                                                               | 0.3          | 0.64        | 0.91         | V      |

| V <sub>COMP(skip)</sub>              | 0% Duty Ratio Level – 0–A Setpoint and No DRV               | V <sub>COMP</sub> is decreasing                               | -            | 325         | -            | mV     |

| COMP(skip_hys)                       | Voltage Hysteresis between Skip and Skip_out Level          | V <sub>COMP</sub> is increasing                               | _            | 5           | -            | mV     |

| R <sub>FB</sub>                      | Internal Pull-Up Resistance                                 |                                                               | 4            | 5           | 6            | kΩ     |

| V <sub>COMP(open)</sub>              | COMP Open Pin Voltage                                       | V <sub>cc</sub> = 3.6 V                                       | 3.15         | 3.45        | -            | V      |

| ICOMP                                | COMP Output Current                                         | V <sub>COMP</sub> = 0                                         | 0.84         | 1           | 1.2          | mA     |

| D <sub>MAX</sub>                     | Maximum Duty Ratio Limit (Note 6)                           | V <sub>COMP</sub> = Open                                      | 86           | 90          | 94           | %      |

| D <sub>MIN</sub>                     | Minimum Duty Ratio (Note 6)                                 | V <sub>COMP</sub> = 0                                         | -            | -           | 0            | %      |

| OPERATIONA                           | L AMPLIFIER SECTION                                         |                                                               |              |             |              |        |

| V <sub>ref</sub>                     | Voltage Feedback Input                                      | $T_J = 25^{\circ}C$<br>-40°C < $T_J < 125^{\circ}C$           | 2.45<br>2.42 | 2.5<br>2.5  | 2.55<br>2.58 | V      |

| I <sub>IB</sub>                      | Input Bias Current                                          | V <sub>FB</sub> = 3 V                                         | -            | 0.01        | -            | μA     |

| A <sub>OL</sub>                      | Open-Loop Voltage Gain                                      | V <sub>COMP</sub> = 2 to 4 V                                  | -            | 90          | -            | dB     |

| BW                                   | Unity Gain Bandwidth ( $T_j = 25^{\circ}C$ )                |                                                               | -            | 1           | -            | MHz    |

| PSRR                                 | Power Supply Rejection Ratio                                |                                                               | -            | 60          | -            | dB     |

| I <sub>OPS</sub>                     | Output Current (Output Resistance is R <sub>FB</sub> ) Sink | $(V_{COMP} = 0.35 \text{ V}, V_{FB} = 2.7 \text{ V})$         | -            | 10          | -            | mA     |

| V <sub>OTH</sub><br>V <sub>OTL</sub> | Output Voltage Swing<br>High State<br>Low State             | COMP is open, $V_{FB}$ = 2.3 V COMP is open, $V_{FB}$ = 2.7 V | -            | 4.8<br>0.03 | _<br>0.15    | v<br>v |

| SOFT START                           | •                                                           |                                                               |              |             |              |        |

| V <sub>SS(open)</sub>                | Soft-Start Open Pin Voltage                                 | V <sub>cc</sub> = 3.6 V                                       | 2.80         | 3.35        | -            | V      |

| V <sub>SS(end)</sub>                 | Soft-Start End Threshold                                    |                                                               | 1.85         | 2.00        | 2.15         | V      |

| I <sub>SS</sub>                      | Soft-Start Current                                          | $0 < V_{SS} < V_{SS(end)}$                                    | 12           | 15          | 18           | μA     |

| K <sub>SS</sub>                      | Soft-Start to CS Divider                                    |                                                               | -            | 8           | -            |        |

| R <sub>SS(DIS)</sub>                 | Soft-Start Discharge Resistance                             |                                                               | -            | -           | 100          | Ω      |

| f <sub>SW(SS)</sub>                  | Minimum Frequency for $V_{SS} = 0 V$                        | Clamp frequency                                               | 20           | 30          | -            | kHz    |

| OSCILLATOR                           |                                                             |                                                               |              |             |              |        |

| f <sub>OSC1</sub>                    | Oscillator Frequency 1                                      | R <sub>T</sub> = 53.6 kΩ                                      | 185          | 200         | 215          | kHz    |

| f <sub>OSC2</sub>                    | Oscillator Frequency 2                                      | R <sub>T</sub> = 130 kΩ                                       | 90           | 100         | 110          | kHz    |

| f <sub>OSC3</sub>                    | Oscillator Frequency 3                                      | R <sub>T</sub> = 18.7 kΩ                                      | 450          | 500         | 550          | kHz    |

| f <sub>OSC4</sub>                    | Oscillator Frequency 4                                      | R <sub>T</sub> = 8.66 kΩ                                      | _            | 1000        | -            | kHz    |

| UNDER-VOLT                           | AGE LOCKOUT                                                 |                                                               |              |             |              |        |

| V <sub>STBY(th)</sub>                | Standby Threshold                                           | V <sub>UVLO</sub> increasing                                  | 0.3          | 0.35        | 0.4          | V      |

| V <sub>RST(th)</sub>                 | Reset Threshold                                             | V <sub>UVLO</sub> decreasing                                  | 0.25         | 0.3         | 0.35         | V      |

| V <sub>STBY(HYS)</sub>               | Standby Hysteresis                                          | V <sub>UVLO</sub> decreasing                                  | -            | 50          | _            | mV     |

| t <sub>STBY(DLY)</sub>               | Standby Detection RC Filter                                 |                                                               | -            | 7           | _            | μs     |

| V <sub>UVLO(th)</sub>                | UVLO Threshold                                              | V <sub>UVLO</sub> increasing                                  | 0.49         | 0.5         | 0.51         | V      |

| I <sub>UVLO(HYS)</sub>               | UVLO Hysteresis Current                                     |                                                               | 4.5          | 5           | 5.5          | μA     |

| t <sub>UVLO(DLY)</sub>               | UVLO Detection Delay Filter                                 | V <sub>UVLO</sub> = V <sub>UVLO(th)</sub> – 50 mV             | -            | 1.1         | -            | μs     |

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>IN</sub> = 12 V, V <sub>CC</sub> = 12 V, V <sub>COMP</sub> = open, C <sub>DRV</sub> = 1 nF, R <sub>T</sub> = 53.6 k $\Omega$ , V <sub>CS</sub> = 0 V, V <sub>SS</sub> = Open, |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{UVLO} = 1.2 V$ , $V_{FB} = 0 V$ , for typical values $T_J = 25^{\circ}$ C, for min/max values, $T_J$ is $-40^{\circ}$ C to $125^{\circ}$ C, unless otherwise noted) (continued)                                     |  |

| Symbol                  | Characteristics                                   | Test Condition                                                                                                       | Min | Тур | Max | Unit |

|-------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| UNDER-VOLT              | AGE LOCKOUT                                       |                                                                                                                      |     |     |     |      |

| t <sub>UVLO(EN)</sub>   | Enable Filter Delay                               | V <sub>UVLO</sub> increasing                                                                                         | _   | 5   | _   | μs   |

| OVER-POWE               | R PROTECTION                                      |                                                                                                                      |     |     |     |      |

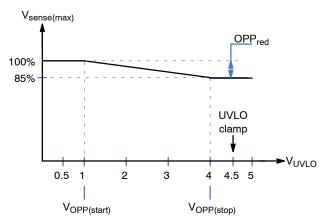

| V <sub>OPP(START)</sub> | UVLO Voltage Above Which OPP Applied              |                                                                                                                      | -   | 1   |     | V    |

| OPP <sub>red</sub>      | Maximum Peak Current Reduction                    | V <sub>UVLO</sub> = 4 V                                                                                              | -   | 15  | -   | %    |

| OPP <sub>clp</sub>      | Internal Peak Reduction Clamp on UVLO             | $V_{CS} = V_{CS(LIM)} (1 - OPP_{red})$                                                                               | -   | 4   | -   | V    |

| V <sub>OPP(0%)</sub>    | COMP Threshold Voltage Above Which OPP is Applied |                                                                                                                      | -   | 1.4 | -   | V    |

| V <sub>OPP(100%)</sub>  | COMP Threshold Voltage for 100% OPP               |                                                                                                                      | -   | 2.6 | -   | V    |

| GATE DRIVE              |                                                   |                                                                                                                      |     |     |     |      |

| t <sub>DRV(rise)</sub>  | DRV Rise Time                                     | $V_{DRV}$ = 1.2 V to 10.8 V, $C_{DRV}$ = 1 nF                                                                        | 6   | 10  | 16  | ns   |

| t <sub>DRV(fall)</sub>  | DRV Fall Time                                     | $V_{DRV}$ = 10.8 V to 1.2 V, $C_{DRV}$ = 1 nF                                                                        | 6   | 10  | 16  | ns   |

| I <sub>DRV(SRC)</sub>   | DRV Source Current                                | V <sub>DRV</sub> = 6 V, Note 8                                                                                       | -   | 0.9 | -   | Α    |

| I <sub>DRV(SNK)</sub>   | DRV Sink Current                                  | V <sub>DRV</sub> = 6 V, Note 8                                                                                       | -   | 1.0 | -   | Α    |

| V <sub>DRV(clamp)</sub> | DRV Clamp Voltage                                 | $V_{CC}$ = 20 V, $R_{DRV}$ = 10 k $\Omega$                                                                           | 8   | 10  | 12  | V    |

| V <sub>DRV(MIN)</sub>   | Minimum DRV Voltage                               | $\label{eq:VCC} \begin{split} V_{CC} &= V_{CC(reg)} + 100 \text{ mV}, \\ R_{DRV} &= 10 \text{ k} \Omega \end{split}$ | 6   | -   | -   | V    |

t<sub>AR</sub> Auto-recovery Timer

THERMAL SHUTDOWN

| T <sub>SHDN</sub>      | Thermal Shutdown            | 150 | 165 | 180 | °C |

|------------------------|-----------------------------|-----|-----|-----|----|

| T <sub>SHDN(hys)</sub> | Thermal Shutdown Hysteresis | -   | 25  | -   | °C |

0.8

1

1.2

s

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions. 4. Disabling of overload timer refers to not acknowledging overload as a fault. The device will continue to switch indefinitely without going to fault mode.

5. Disabling Slope compensation means that no compensation ramp is applied.

6. Electrical characteristics apply to both COMP Architectures

7. OPP Current Gain disabled means that no OPP current is injected out of the CS pin

8. Guaranteed by design

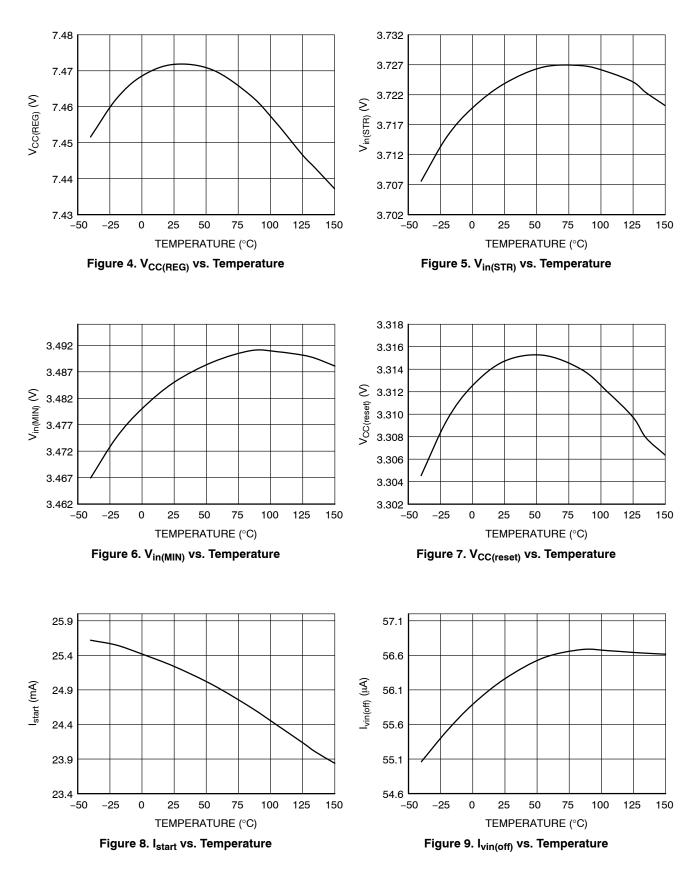

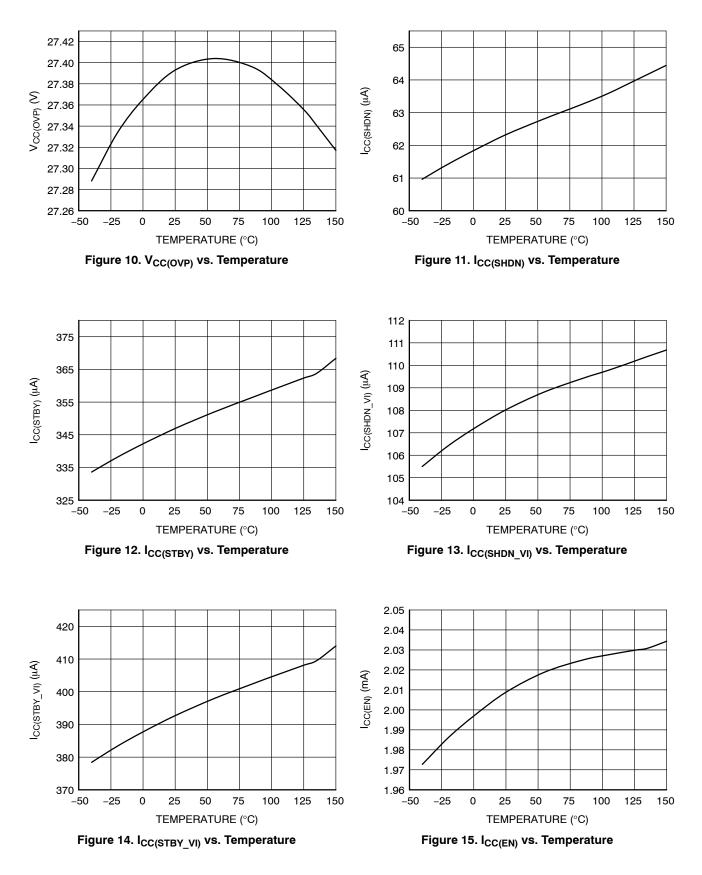

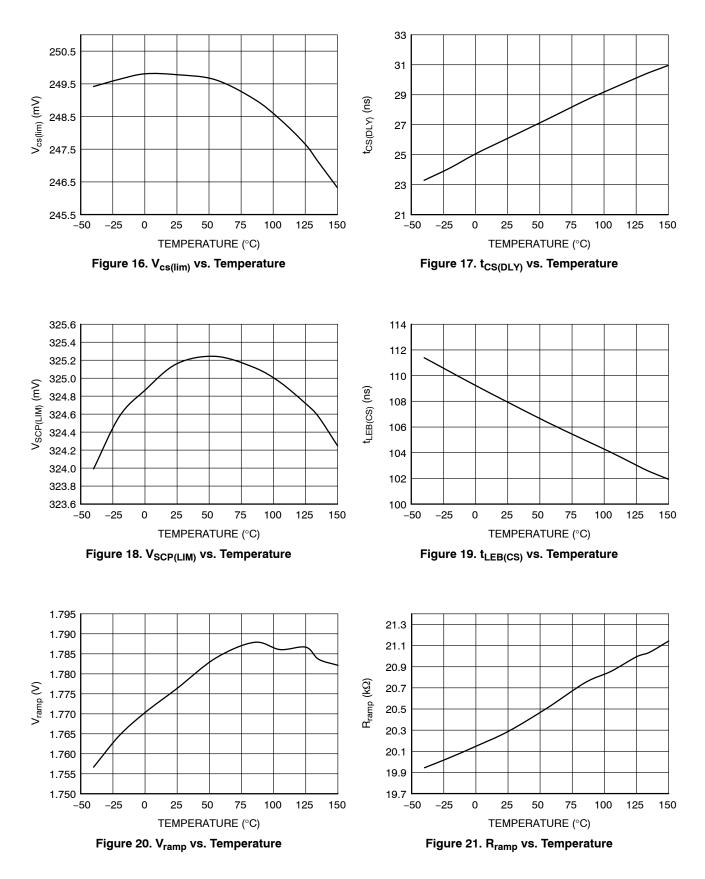

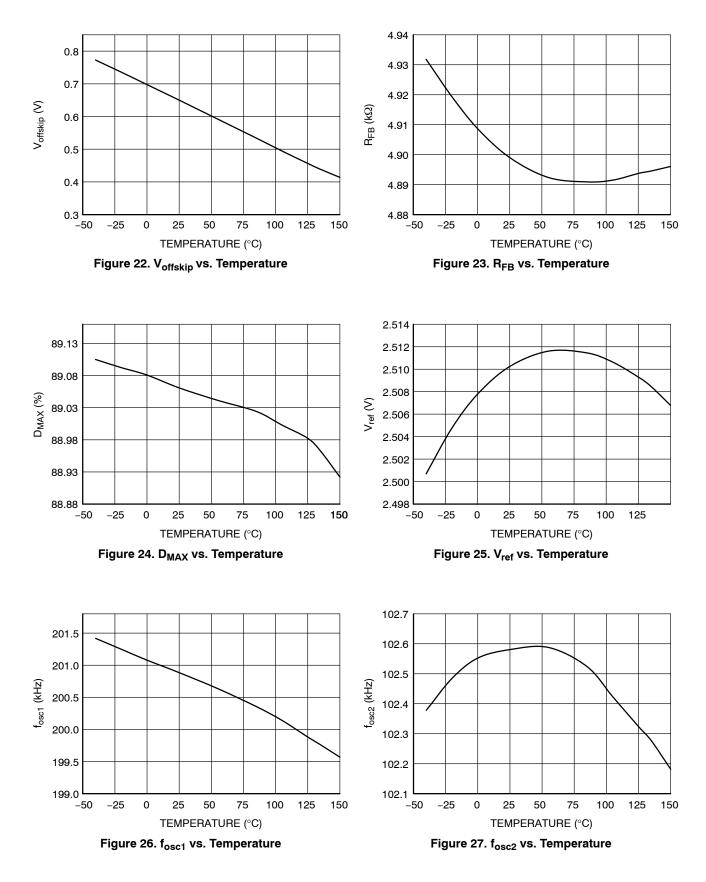

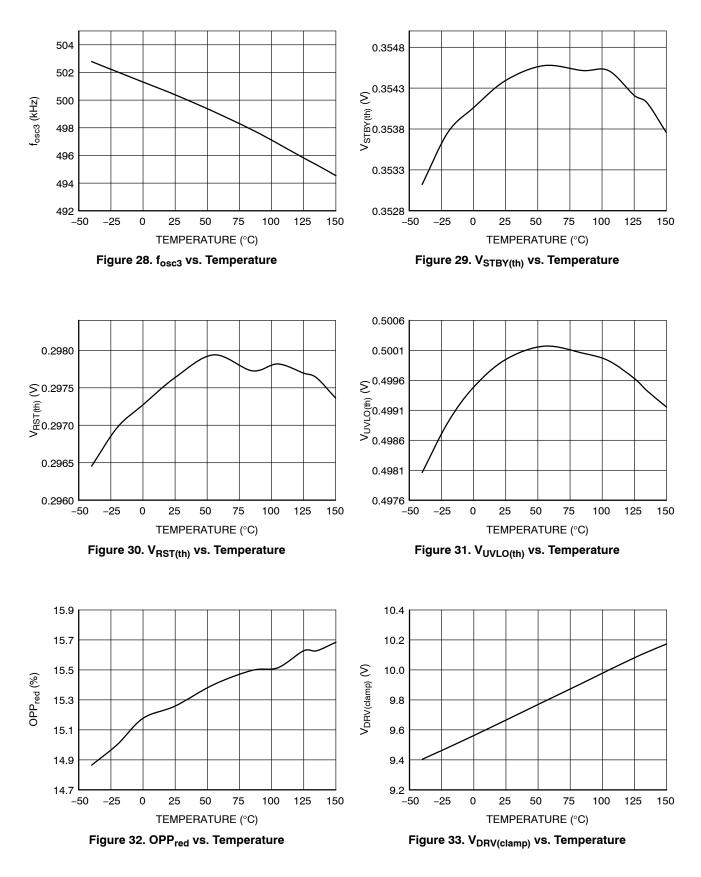

### **TYPICAL CHARACTERISTICS**

#### APPLICATION INFORMATION

NCP12711 implements a standard current-mode architecture where the switch-off event is dictated by the peak current setpoint. This component represents the ideal candidate where low part-count and cost effectiveness are key design parameters, particularly in dc-dc converters modules and open-frame power supplies. NCP12711 brings all the necessary components normally needed in today modern power supply designs.

- *Current-mode operation with internal slope compensation:* implementing peak current mode control at a fixed operating frequency, the NCP12711 includes an externally-adjustable slope compensation scheme. By sizing a single resistance connected in series with the CS pin, the designer has the ability to tailor the compensation level exactly to his needs.

- 0% duty ratio operation: the loop can program a 0-A peak current setpoint when it imposes 640 mV on the error amplifier COMP pin. It means, the width of the DRV pulse is a minimum  $t_{on}$  (LEB + propagation delay). If  $V_{out}$  keeps increasing in this situation, the regulation is lost and the IC goes to skip mode with no DRV pulse. It ensures that the IC will safely skip cycles at minimum  $t_{on}$  during light load, preventing output runaway while keeping output ripple at a minimum.

- *Internal regulator:* the part includes an internal regulator powering the device from 4 to 45 V without the need to resort to an auxiliary winding. When power dissipation is at stake, it is possible to lift the VCC pin up via an auxiliary winding and permanently disable the regulator.

- *Input voltage monitoring:* the UVLO pin observes the input voltage through a resistive divider. This pin serves two purposes: a) it ensures the converter operates within the range it has been designed for and b) it routes this information to a power-limiting path for over-power protection (OPP).

- *Internal OPP:* the part internally buffers the UVLO voltage and reduces the maximum peak current setpoint at high input line. Please note that the OPP current starts from 0% when the UVLO voltage is 1.0 V, a low-line condition. It helps pass maximum power at the lowest input voltage despite some compensation at high line. OPP is also disabled during the start-up sequence or in light-load operation.

- Internal soft-start: a soft-start precludes the main power switch from being stressed upon start up and it reduces output voltage overshoots. In this controller, the soft-start can be adjusted by a simple capacitor to ground. Beside peak current smooth increase brought by this mechanism, the switching frequency starts from a low 30-kHz value

and increases along the soft-start sequence. Soft-start is activated when a new startup sequence occurs or during an auto-recovery hiccup.

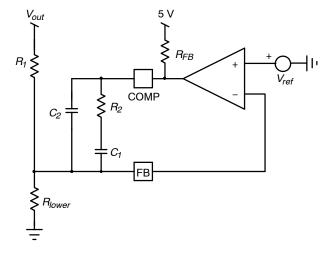

- On-board op-amp: an op-amp allows the implementation of non-isolated dc-dc converters but also isolated versions in which the rectified auxiliary voltage is used for regulation.

- $V_{cc}$  OVP: an OVP protects the circuit against  $V_{cc}$  runaways. The fault must be present at least 7 µs to be validated. This OVP is auto-recovery.

- Short-circuit protection: short-circuit and especially over-load protections are difficult to implement when a strong leakage inductance between auxiliary and power windings affects the transformer (the auxiliary winding level does not properly collapse in presence of an output short). In this controller, every time the internal 0.25-V maximum peak current limit is activated (or less when OPP is active), an error flag is asserted and a time period starts, thanks to the programmable timer. When the timer has elapsed, the controller enters an auto-recovery mode with a 1-s recurrence.

- Winding or diode short circuit protection: in case the secondary-side winding (or even the rectifying diode) is shorted, the primary-side current can grow very quickly with possibly-lethal conditions in the converter. An extra comparator with a smaller LEB monitors if the peak current exceeds 25% of the maximum value (250 mV/R<sub>sense</sub>) four consecutive times. At the end of this sequence, the converter enters auto-recovery mode.

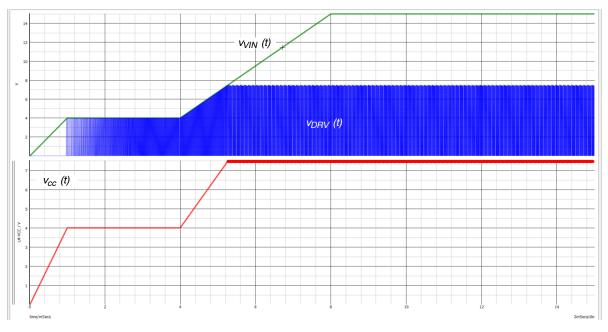

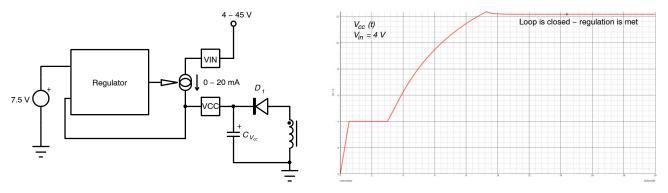

#### Supplying the Controller

The component integrates a start-up current source supplied from the VIN pin and capable of sourcing up to 20 mA typically to the VCC pin. When  $V_{cc}$  reaches the regulation level of 7.5 V, the startup is a linear regulator which can continue to supply and regulate  $V_{cc}$  at 7.5 V. The recommended VCC capacitance to ensure stability of the regulator is  $1 - 10 \mu$ F. This source is a dual-current type meaning that if for any reason the  $V_{cc}$  is shorted to ground, the current is safely limited to 2.5 mA, preventing any lethal runaway at a high input voltage. When the short circuit is released and Vcc exceeds a certain voltage level (200 mV typical), the source is back to its 20-mA setpoint. The 20-mA are typically specified for a 12-V level on the VIN pin but the part will deliver current as soon as a bias appears on the part. Figure 34 shows a simulated start-up sequence with VIN plateauing at 4 V for some time before taking off towards 15 V. The driving pulses follow the voltage and are clamped at the 7.5-V voltage later on.

Figure 34. The LDO is Activated During the Start-up Sequence and Powers the Controller

As the LDO supplies the controller, it sees the average current absorbed by the controller. This current is approximately made of  $I_{CC(EN)}$  plus the MOSFET driving current leading to a total current equal to:

$$I_{LDO} \approx I_{CC(EN)} + I_{DRV} \approx I_{CC(EN)} + f_{sw}Q_{G}$$

(eq. 1)

Assume you have selected a MOSFET featuring a 35–nC total gate charge  $Q_G$  and operate it at 250 kHz. The average current flowing in the LDO will be:

$$I_{LDO} \approx 4 \text{ m} + 250 \text{ k} \cdot 35 \text{ n} \approx 12.8 \text{ mA} \tag{eq. 2}$$

This current multiplied by the maximum voltage at the VIN pin will define the controller average power dissipation:

$$P_{LDO} = I_{LDO} V_{VIN}$$

(eq. 3)

If we assume a  $R_{\theta J-A}$  of 130°C/W when the part is soldered on a wide copper area, then the maximum VIN voltage at a 50°C ambient temperature will be:

$$V_{in,max} < \frac{T_j - T_A}{R_{\theta J - A}I_{LDO}}$$

(eq. 4)

Assume a junction temperature limit of 110°C and a maximum ambient of 60°C, then the maximum bias voltage for this circuit *while the LDO is permanently activated* would be:

$$V_{in,max} < \frac{110 - 60}{130 \times 12.8 \text{ m}} \approx 30 \text{ V} \tag{eq. 5}$$

Beyond this value, risks exist to damage the die by excessive power dissipation. To benefit from the full voltage range up to 45 V, it is recommended to a) reduce the dissipated power by lowering  $f_{sw}$  and adopting a low- $Q_G$  power MOSFET and/or b) add an auxiliary winding to the transformer and use the LDO as a simple one-shot start-up source (Figure 35).

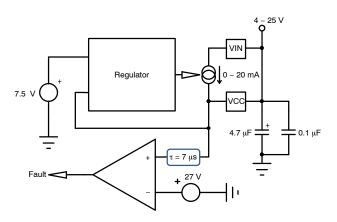

Figure 35. The LDO Can Be Associated with an Auxiliary Winding and Be Turned Off in Normal Operation

#### Protecting the VCC Pin

The VCC pin is protected by an over–voltage detection circuitry which immediately reacts as soon as the bias on this pin exceeds 27 V typically (25 V minimum). When the fault happens and lasts more than 7  $\mu$ s, all pulses are immediately stopped and the circuit remains silent for 1 s. It resumes operation via a soft–start sequence and goes back to normal mode if the fault has gone. This function is there to protect the controller in case you would accidentally supply it with a large voltage on the auxiliary winding for instance if the control loop fails. In some low–voltage applications, you can directly supply the controller from the input rail by shorting the VIN and VCC pins together (Figure 36).

Figure 36. For Low-voltage Applications, it is Possible to Connect the VIN and VCC Pins Together. The OVP on the VCC Pin Remains Active and will Stop Pulses if the Input Rail Exceeds 27 V.

The short circuit between the pins bypasses the LDO and the whole circuit is fed by the input rail. Make sure the input rail voltage always remain below the OVP voltage otherwise the controller will stop working. In the example, the 25–V limit corresponds to the minimum of the OVP specification.

#### Monitoring the Input Voltage

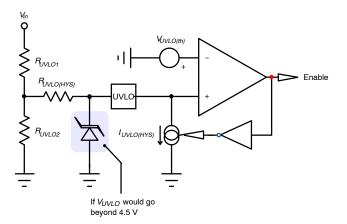

It is important to check that the converter operates within an authorized input voltage range. For that purpose, the UVLO pin permanently monitors a scaled–down image of the input rail and turns the IC on or off accordingly. A simplified view of the internal circuitry is shown in Figure 37.

#### Figure 37. A Comparator Turns The IC On or Off Depending the VIN Pin Bias Level

The turn-on and -off voltages can be obtained using the following formulas:

$$V_{on} = [V_{UV(th)} + (R_{UVLO1} || R_{UVLO2} + R_{HYS}) I_{UV(HYS)}] \frac{R_{UVLO1} + R_{UVLO2}}{R_{UVLO2}}$$

(eq. 6)

$$V_{off} = (V_{UVLO(th)} - V_{UVLO(HYS)}) \frac{R_{UVLO1} + R_{UVLO2}}{R_{UVLO2}}$$

(eq. 7)

From these expressions, resistors setting the turn-on and –off levels are determined with the below equations in which  $R_{UVLO2}$  is arbitrarily fixed:

$$R_{UVLO(HYS)} = \frac{(V_{UVLO(th)} - V_{UVLO(HYS)}) V_{on} + I_{UVLO(HYS)} R_{UVLO2} (V_{UVLO(th)} - V_{UVLO(hys)}) - V_{off} (V_{UVLO(th)} + I_{UVLO(HYS)} R_{UVLO2})}{I_{UVLO(HYS)} V_{off}}$$

(eq. 8)

$$R_{UVLO1} = \frac{R_{UVLO2} \left(V_{off} - V_{UVLO(th)} + V_{UVLO(HYS)}\right)}{V_{UVLO(th)} - V_{UVLO(HYS)}}$$

(eq. 9)

As an example, if  $R_{UVLO2} = 10 \text{ k}\Omega$  and you select an 8–V turn–on voltage with a 6–V turn–off level, then  $R_{HYS} = 20 \text{ k}\Omega$  and  $R_{UVLO1} = 114 \text{ k}\Omega$ . The Excel sheet posted on the NCP12711 landing page automates the calculation of these resistors. As a final note, once the resistive divider is determined, it is important to verify that the maximum voltage on the UVLO pin does not approach or exceed its 5.5–V maximum rating at the maximum input voltage. Should it be the case, you will have to install a 4.7–V Zener diode at the UVLO pin to keep the pin voltage within its safe operating area.

#### Limiting the Power Excursion at High Input Voltage

It is a well-known phenomenon that the maximum power delivered by a flyback converter varies with the input voltage. Assuming a wide input range design, your converter can potentially exhibit more current for the output diode at high line than at low line with detrimental effects for reliability. This is because the converter is designed to deliver its nominal power at the lowest input voltage. Transition to DCM and propagation delays are the reason why the power capability changes with the input voltage.

NCP12711 embarks an over-power protection (OPP) scheme which reduces the maximum peak current setpoint when the UVLO voltage varies from 1 V (low line) to 4 V where the OPP is no longer active. The peak setpoint will reduce by 15% when the UVLO hits 4 V (Figure 38). An option exists to turn OPP permanently off, please contact sales for that purpose.

#### Soft-Start Sequence

. .

...

To limit the stress on primary– and secondary–sides, the NCP12711 incorporates a soft–start circuitry which smoothly increases the peak current setpoint cycle–by–cycle but also sweeps the switching frequency. The converter starts with an almost 0–A setpoint at a 30–kHz frequency and increases this value up to the nominal selection. A capacitor is charged by a 15– $\mu$ A current source up to 2 V where the sequence has ended. The capacitor is thus selected based on the wanted soft–start duration:

$$C_{SS} = \frac{I_{SS}I_{SS}}{V_{SS(end)}} = \frac{15\,\mu \times 10\,\text{m}}{2} = 75\,\text{nF}$$

(eq. 10)

. . .

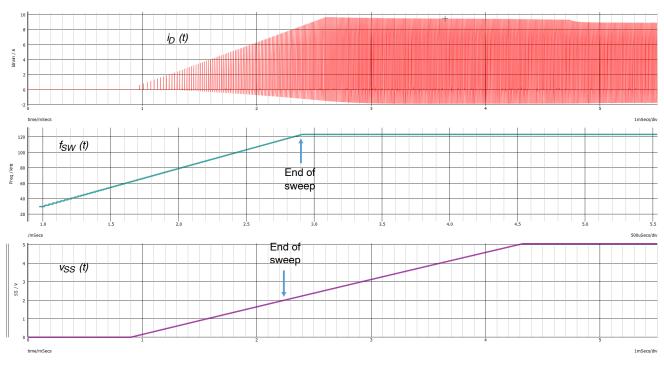

Figure 39. The Peak Current is Smoothly Ramped Up as Well as the Switching Frequency Which Starts from a Low 30 kHz

Figure 39 shows a typical start–up sequence highlighting current and frequency variations during this sequence. Please note the different time scale for the frequency plot.

The frequency sweep ensures the lowest possible stress at power up and is especially interesting when secondary-side synchronous rectification is used: in absence of output voltage, the MOSFET body diode plays the rectifier role until the control circuit takes the lead when sufficiently powered. In absence of a smooth frequency ramp-up, violent voltage spikes can appear across the synchronous MOSFET and may destroy it. A slow frequency increase ensures a limited stress until the synchronous circuit is fully operational.

#### Feedback and Current Sense

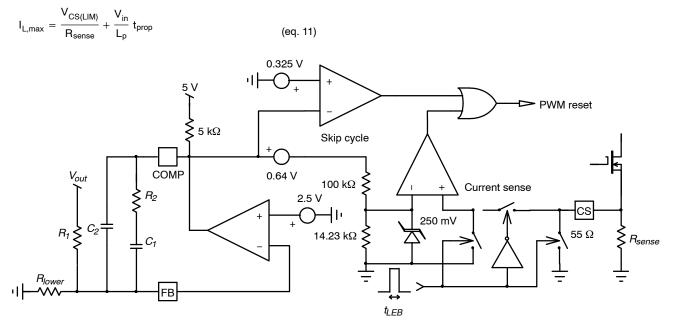

The controller hosts an operational amplifier (op-amp) useful for either non-isolated dc-dc or primary-side-operated isolated flyback converters. The

output of this op-amp controls the peak current setpoint via a resistive divider associated with a series diode as shown in Figure 40. The voltage-to-peak-current-setpoint division ratio is 8 with a maximum value  $V_{CS(LIM)}$  clamped at 250 mV. The maximum inductor current without active OPP is therefore defined as:

In which  $t_{prop}$  represents the maximum propagation delay from the detection of the over-current event to the effective MOSFET gate pulldown. The IC contributes up to 75 ns to this figure but if you add a gate resistance, this number can grow significantly.

Figure 40. The Series Diode Introduces an Offset Making Sure Skip Cycle Occurs at a 0% Duty Ratio

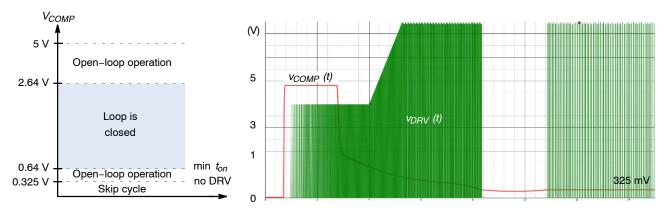

In a current-mode controller, the minimum on-time duration is set by the propagation delay and the leading-edge blanking duration. The sum of both variables gives the minimum  $t_{on}$ . When the load current is getting lighter, the op-amp pulls the COMP pin down in an attempt to reduce the peak current setpoint. The voltage on the COMP decreases until the minimum on-time is reached. With the NCP12711, this minimum ton is around 135 ns and despite a COMP pin going further down, it cannot be reduced. Thus, there is always a little bit of energy that is transmitted cycle by cycle from the primary to the secondary side. An output voltage runaway in a flyback converter is therefore possible in a no-load condition. To avoid this situation, a diode drop ( $\approx 640$  mV) is inserted with the feedback voltage setting the peak current. For the maximum peak value, the COMP pin will be biased at the following level:

$$V_{COMP} = V_{CS(LIM)} \times k_{PWM} + V_{f} = 0.25 \times 8 + 0.64 = 2.64 V$$

(eq. 12)

On the opposite, the minimum current will be reached when  $V_{COMP}$  falls below 0.64 V. The dynamic on the COMP pin can therefore be depicted by the graph shown in Figure 41 with simulation data. At power up, the loop asks for the maximum peak current and regulates when the target is met. Considering a light–load condition, the loop will reduce the setpoint to a minimum so as to keep  $V_{out}$  in regulation. The output pulses can reduce down to the smallest possible ones and equal LEB plus propagation delay, including the MOSFET turn-off time. If the loop asks for less than this value, the peak current is frozen to this minimum value:

$$I_{p,min} = \frac{V_{in}}{L_p} (t_{LEB} + t_{prop})$$

(eq. 13)

Assuming a 5- $\mu$ H primary inductance  $L_p$  with a 40-V input voltage and a 150-ns pulse duration, the peak current cannot be below 1.2 A. If the load keeps decreasing, an output voltage runaway can happen as peak current can no longer be reduced: regulation is lost. To avoid an over-voltage situation, the controller hosts a skip cycle comparator which shuts pulses off when the feedback is out of its normal dynamic range. When V<sub>COMP</sub> keeps going down in an attempt to regulate (with no action of course), it reaches 325 mV and all pulses are stopped. As Vout is now falling in lack of pulses, the COMP pin slightly goes up again and authorizes pulses until COMP goes low. This is skip cycle operation. Unlike other controller where skip is programmed at 10 - 15% peak current, here it only activates when the regulation is lost. Thus, if you do not want to see skip cycle in your application, either install a dummy output load (a bleeder) or reduce the output resistance of the feedback divider so that it draws enough current to maintain V<sub>COMP</sub> above 640 mV.

Figure 41. The COMP Pin Swings between 2.64 V and 0.64 V for a 0–A Peak Setpoint. Skip Cycle Operation Happens when the Loop Fails to Regulate at the Lowest Possible Peak Current Setpoint.

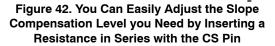

#### **Slope Compensation**

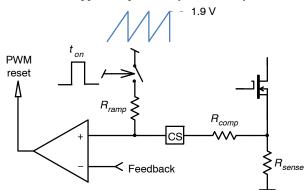

Current-mode power supplies are prone to sub-harmonic oscillations. This is because the inner current-loop gain crossover frequency is too high and there is no phase margin at this point. The condition happens when the converter operates in continuous conduction mode (CCM) with a duty ratio approaching 50%. A simple cure for these sub-harmonic oscillations is to inject a compensation ramp  $S_e$  which will reduce the current-loop gain. It can be done in several ways but the simplest one is to sum the ramp with the current sense information. NCP12711 integrates an artificial ramp derived from the oscillator. Once buffered, it biases the CS pin via a 20-k $\Omega$  resistor (Figure 42) only during the on-time. Inserting a resistance in series with the sensed voltage offers a simple means to adjust the compensation effort. If you do not want compensation, simply reduce this resistance or suppress it provided your PCB layout is clean.

To determine the value of  $R_{comp}$ , you first need to determine the primary–side inductor current downslope  $S_f$ . Once scaled to volts per second via the sense resistance, we have:

$$S_{f} = \frac{V_{out} + V_{f}}{NL_{p}} R_{sense}$$

(eq. 14)

In which  $V_f$  is the secondary-side rectifier drop, N is the 1:N transformer turns ratio,  $L_p$  the primary-side inductance and  $R_{sense}$  the current sensing resistance. The compensation slope is given in the data-sheet and depends on the selected switching period:

$$S_{e} = \frac{V_{ramp}}{D_{max}T_{sw}}$$

(eq. 15)

Now, compute the division ratio value between  $S_e$ , the existing ramp level and what you want to inject. If we select a compensation level equal to 50% of the inductor downslope current, then the division ratio equals:

$$\text{divratio} = \frac{0.5 \times S_{\text{f}}}{S_{\text{e}}} = \frac{0.5 \cdot D_{\text{max}} R_{\text{sence}} T_{\text{sw}} \left(V_{\text{out}} + V_{\text{f}}\right)}{L_{\text{p}} N V_{\text{ramp}}} \tag{eq. 16}$$

Then, the resistance to add in series with the CS pin is simply:

$$R_{comp} = divratio \times R_{ramp}$$

(eq. 17)

Assume the following data:  $L_p = 5 \ \mu H$ ,  $R_{sense} = 0.03 \ \Omega$ ,  $D_{max} = 90\%$ ,  $F_{sw} = 100 \ \text{kHz}$ ,  $R_{ramp} = 20 \ \text{k}\Omega$ ,  $N = 1.25 \ \text{and}$  $V_{ramp} = 1.9 \ \text{V}$ . Applying the above formulas to a 5–V converter leads to a compensation resistance value of 1.4 k $\Omega$ :

$$\begin{split} &\mathsf{V}_{out} := 5 \,\mathsf{V} &\mathsf{N}_{turns} := 1.25 \;\; \mathsf{R}_{ramp} := 20 \,\mathsf{k}\Omega \;\; \mathsf{R}_{sense} := 0.03 \,\Omega \\ &\mathsf{L}_p := 5 \,\mu\mathsf{H} &\mathsf{D}_{max} := 90\% \;\; \mathsf{F}_{sw} := 100 \;\mathsf{kHz} \;\; \mathsf{k}_{comp} := 50\% \\ &\mathsf{V}_{ramp} := 1.9 \,\mathsf{V} \;\; \mathsf{T}_{sw} := \frac{1}{\mathsf{F}_{sw}} \;\; \mathsf{V}_f := 0.5 \,\mathsf{V} \\ &\mathsf{S}_e := \frac{\mathsf{V}_{ramp}}{\mathsf{T}_{sw}} = 0.19 \;\frac{\mathsf{V}}{\mu s} \;\; \mathsf{S}_f := \frac{\mathsf{V}_{out} + \mathsf{V}_f}{\mathsf{N}_{turns} \cdot \mathsf{L}_p} \cdot \mathsf{R}_{sense} = 0.026 \;\frac{\mathsf{V}}{\mu s} \\ &\mathsf{divratio} := \frac{\mathsf{k}_{comp} \cdot \mathsf{S}_f}{\mathsf{S}_e} = 0.069 \end{split}$$

$R_{comp}:=~R_{ramp}~\cdot~divratio~=~1.389~\times~10^3~\Omega$

$$\frac{k_{comp} \cdot R_{sense} \cdot T_{sw} \cdot (V_{out} + V_{f})}{L_{p} \cdot N_{turns} \cdot V_{ramp}} \cdot R_{ramp} = 1.389 \text{ k}\Omega$$

#### Figure 43. The Compensation Resistance is Easily Determined with a few Calculation Steps

#### **Short Circuit Protection**

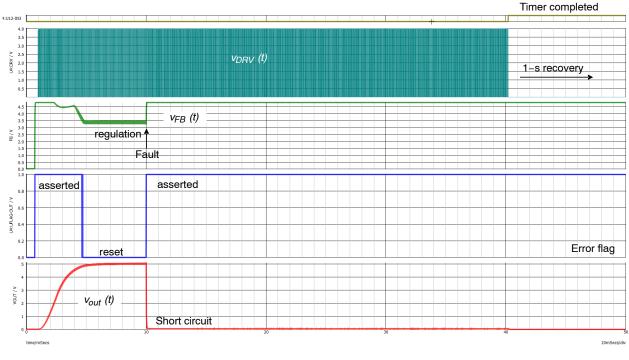

If the loop asks for the maximum power, the peak-current setpoint is clamped to 250 mV (no OPP). When this happens, the controller arms an error flag signaling a fault condition. This naturally occurs during the start-up sequence until the converter regulates and resets the flag. A fault timer of 30 ms starts every time the error flag is asserted. When the timer reaches completion, all pulses are stopped and the part remains silent for 1 s. If the auxiliary winding disappears during the 1–s off–mode, the LDO takes over and supplies the part. At the end of the 1–s period, a fresh start–up sequence takes place with soft–start and frequency sweep. If the fault has disappeared, the converter

recovers and resumes operation. If the fault is still present, a new 1-s off-mode takes place and the converter keeps ticking as long as the fault remains. Figure 44 describes a start-up sequence leading to a regulated output and suddenly followed by an output short circuit. The error flag is asserted immediately and the timer starts counting. During this time, the peak current is pushed to the maximum value. When the timer has elapsed, all pulses stop and the 1-s off-time period starts. Then the power supply attempts to resume operations (not shown). The overload timer is set to 30 ms but longer periods of time are available upon request to the factory. Please contact your sales person for more information.

Figure 44. The Circuit Auto-recovers from a Short Circuit or an Overload Situation

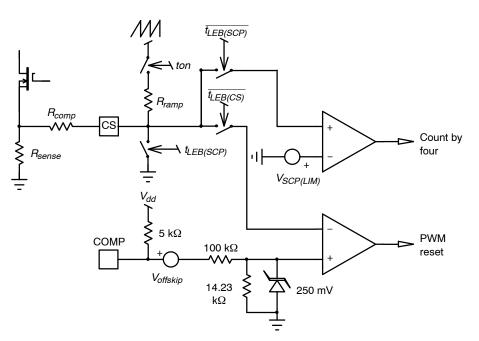

In case the peak current measured at the CS pin largely exceeds the 250-mV voltage setpoint, a second over-current comparator trips. This second comparator benefits from a smaller LEB duration (60 ns versus 110 ns) and reacts in case the sensed voltage exceeds the 250-mV

limit by 25%:  $V_{SCP(LIM)}$ . When such an event occurs, e.g. when the secondary diode fails shorted, the controller counts 4 consecutive events and stops all pulses immediately. The part then waits 1 s before attempting to restart. The internal circuitry appears in Figure 45.

Figure 45. If the Current Sense Pin Exceeds the Maximum Cycle-by-cycle Limit by 25%, a Counter Records the Event and Stops All Pulses after 4 Consecutive Events

#### **Operational Amplifier**

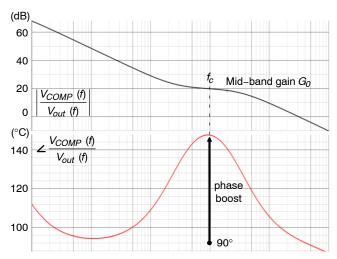

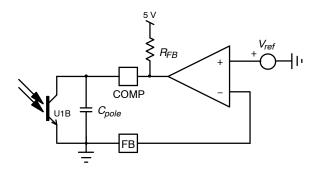

The on-board op-amp exhibits a gain-bandwidth product (GBW) of 1.4 MHz with a low-frequency pole located at 53 Hz. It features an open-drain configuration loaded by the internal 5-k $\Omega$  pull-up resistor. With this circuit, it is possible to implement a type 2 compensator hosting a pole at the origin, one zero and one pole. Such configuration is shown in Figure 46 with its typical ac response in the right side. The type 2 lends itself well to stabilizing current-mode dc-dc converters. The characteristics of such compensator are described by the following transfer functions:

$$G(s) = -G_0 \frac{1 + \frac{\omega_z}{s}}{1 + \frac{s}{\omega_p}}$$

(eq. 18)

In which:

$$G_0 = \frac{R_2}{R_1} \frac{C_1}{C_1 + c_2} \approx \frac{R_2}{R_1}$$

(eq. 19)

$$\omega_z = \frac{1}{R_2 C_1}$$

(eq. 20)

$$\omega_{p} = \frac{1}{R_{2} \frac{C_{1}C_{2}}{C_{1} + C_{2}}} \approx \frac{1}{R_{2}C_{1}}$$

(eq. 21)

Approximated formulas are valid when we have  $C_2 \ll C_1$ .

Figure 46. The On-board op-amp Lets you Realize a Type 2 Compensator which is Adequate for Stabilizing Current-mode dc-dc Converters

The op-amp own characteristic can be neglected if the selected crossover frequency is moderate, around the kHz for instance. However, if you plan to extend crossover at 10 kHz or so, then it is important to verify the compensator response once the op-amp characteristic is accounted for especially if a high gain is required at crossover. A separate application note covers a compensation exercise in details.

NCP12711 lends itself well to opto–isolated applications also. Just ground the feedback pin and connect the opto–coupler collector to the COMP pin with a capacitor for the pole generation together with  $R_{FB}$ .

Figure 47. If you Tie the FB Pin to Ground, then an Opto-isolator Can Pull the COMP Pin Down for Regulation Purposes

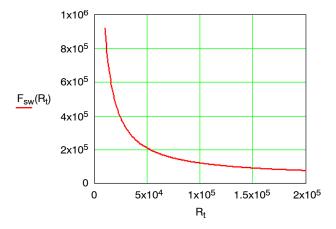

#### Oscillator

The oscillator lets you select a switching frequency from 100 kHz up to 1 MHz. By pulling the  $R_t$  pin to ground via a resistance, it is possible to select the switching frequency. The curve from Figure 48 links the switching frequency with the resistance value. An approximate formula lets you also determine the resistance as follows:

$$R_{t} \approx \frac{8.9 \cdot 10^{9}}{F_{sw} - 30 \,k}$$

(eq. 22)

Assuming a wanted 100-kHz operation, you would select a resistance of

$$R_{t} = \frac{8.9 \cdot 10^{9}}{100 \text{ k} - 30 \text{ k}} \approx 127 \text{ k}\Omega$$

(eq. 23)

A quick experiment on the prototype will let you know if you need to keep or slightly adjust this value. The following array suggest values for some typical switching frequencies:

#### Table 1.

| Frequency (kHz) | R <sub>t</sub> (kΩ) |

|-----------------|---------------------|

| 100             | 127                 |

| 150             | 74.2                |

| 200             | 52.4                |

| 250             | 40.5                |

| 300             | 33                  |

| 350             | 27.8                |

| 400             | 24                  |

For stability reasons, it is usually not recommended to decouple the  $R_t$  pin with a capacitor.

Figure 48. You Can Extract the  $R_t$  Resistance Value from the Graph or Compute it with the Approximate Expression

#### **Application Circuits**

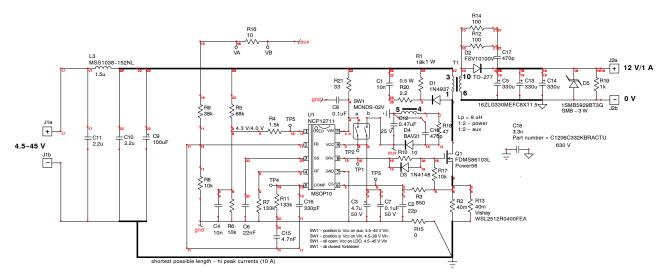

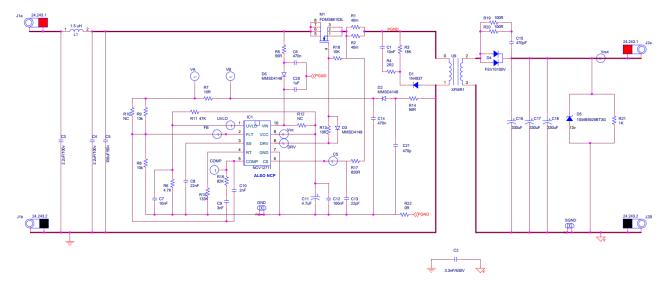

The NCP12711 can be used in a variety of applications. Figure 49 represents a 100-kHz flyback converter

regulating the auxiliary winding at 12 V. This is a wide-range application since the board operates from a 4-V input voltage up to 45 V. the precision

Figure 49. 4.5 – 45 V Input Voltage Isolated Flyback Converter Delivering 12 V/1 A

Figure 50 represents a 5-V/2-A application circuit operated from a 4.5-to-10-V input source, a typical industrial board-mounted module. A synchronous rectifier

ensures a good overall efficiency. There is no auxiliary winding on this board.

Figure 50. 4.5 - 10 V 5-V/2-A Opto-isolated dc-dc Flyback Module

Considering NCP12711 for a non-isolated dc-dc converter such as a SEPIC or a boost is an option as shown in the below figure:

Figure 51. Here an Example of a 250-kHz-operated 12-W Boost Converterc delivers 12 V

Finally, it is also possible to use the NCP12711 as a high-side controller, for instance to build a

primary-side-regulated flyback converter operated without an auxiliary winding:

Figure 52. A 100-kHz-operated 12-W Flyback Converter Delivering 12 V without Auxiliary Winding

With a 12–V output, the reflected voltage imposes a maximum input voltage limited to 38 V. It can be increased if  $V_{out}$  takes on a lower value.

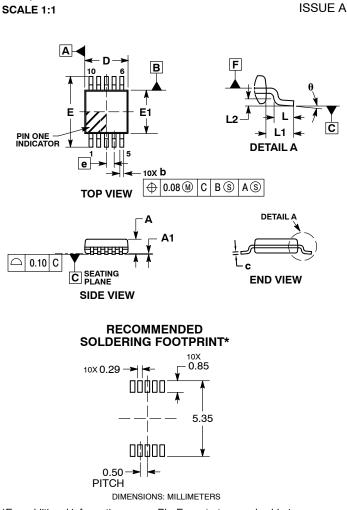

DATE 20 JUN 2017

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

NOTES:

MSOP10, 3x3 CASE 846AE

- IES: DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSIONS: MILLIMETERS. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.10 MM IN 1. 2. 3

- 4

- ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.10 MM IN EXCESS OF MAXIMUM MATERIAL CONDITION. DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. DIMENSION E DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 MM PER SIDE. DIMENSIONS D AND E ADE DETERMINED AT DATIME DIMENSIONS D AND E ARE DETERMINED AT DATUM F. DATUMS A AND B TO BE DETERMINED AT DATUM F.

- 5.

- A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE 6 BODY.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   |             |      | 1.10 |  |

| A1  | 0.00        | 0.05 | 0.15 |  |

| A2  | 0.75        | 0.85 | 0.95 |  |

| b   | 0.17        |      | 0.27 |  |

| С   | 0.13        |      | 0.23 |  |

| D   | 2.90        | 3.00 | 3.10 |  |

| Е   | 4.75        | 4.90 | 5.05 |  |

| E1  | 2.90        | 3.00 | 3.10 |  |

| е   | 0.50 BSC    |      |      |  |

| L   | 0.40        | 0.70 | 0.80 |  |

| L1  | 0.95 REF    |      |      |  |

| L2  | 0.25 BSC    |      |      |  |

| θ   | 0°          |      | 8°   |  |

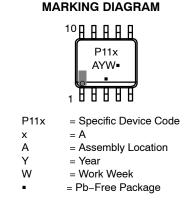

#### GENERIC **MARKING DIAGRAM\***

А

Y

W

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present and may be in either location. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98AON34098E | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|