# 3A Ultra-Small Controlled **Load Switch with Auto-Discharge Path**

The NCP436 and NCP437 are very low Ron MOSFET controlled by external logic pin, allowing optimization of battery life, and portable device autonomy.

Indeed, due to a current consumption optimization with PMOS structure, leakage currents are eliminated by isolating connected IC on the battery when not used.

Output discharge path is also embedded to eliminate residual voltages on the output rail for the NCP437 part only.

Proposed in a wide input voltage range from 1.0 V to 3.6 V, in a small 1 x 1.5 mm WLCSP6, pitch 0.5 mm.

#### **Features**

- 1.0 V 3.6 V Operating Range

- $20 \text{ m}\Omega \text{ P MOSFET}$  at 3.6 V

- DC Current Up to 3 A

- Output Auto-discharge

- Active High EN Pin

- WLCSP6 1 x 1.5 mm

- These are Pb-Free Devices

## **Typical Applications**

- Mobile Phones

- Tablets

- Digital Cameras

- GPS

- Portable Devices

#### ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM**

#### WLCSP6 CASE 567FH

= Assembly Location

= Year

= Work Week

= Pb-Free Package

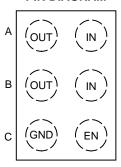

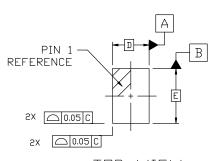

#### **PIN DIAGRAM**

(Top View)

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information in the package dimensions section on page 6 of this data sheet.

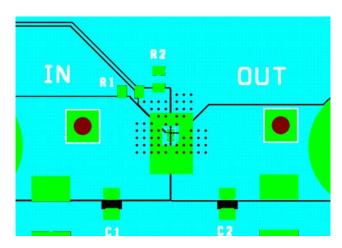

**Figure 1. Typical Application Circuit**

## PIN FUNCTION DESCRIPTION

| Pin Name | Pin Number | Туре   | Description                                                                                                                      |  |

|----------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------|--|

| IN       | A2, B2     | POWER  | Load–switch input voltage; connect a 1 $\mu\text{F}$ or greater ceramic capacitor from IN to GND as close as possible to the IC. |  |

| GND      | C1         | POWER  | Ground connection.                                                                                                               |  |

| EN       | C2         | INPUT  | Enable input, logic high turns on power switch.                                                                                  |  |

| OUT      | A1, B1     | OUTPUT | Load–switch output; connect a 1 $\mu\text{F}$ ceramic capacitor from OUT to GND as close as possible to the IC is recommended.   |  |

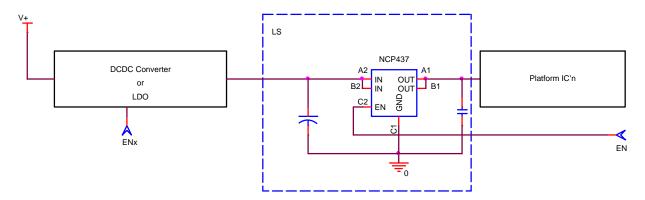

## **BLOCK DIAGRAM**

#### **MAXIMUM RATINGS**

| Symbol                                                                                     | Rating                                                   | Value        | Unit |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|------|

| $V_{\mbox{\footnotesize EN}}, V_{\mbox{\footnotesize IN}}, \ V_{\mbox{\footnotesize OUT}}$ | IN, OUT, EN, Pins: (Note 1)                              | -0.3 to + 4  | V    |

| V <sub>IN</sub> ,<br>V <sub>OUT</sub>                                                      | From IN to OUT Pins: Input/Output (Note 1)               | 0 to + 4     | V    |

| TJ                                                                                         | Maximum Junction Temperature                             | -40 to + 125 | °C   |

| ESD<br>HBM                                                                                 | Human Body Model (HBM) ESD Rating are (Notes 2 and 3)    | 8000         | V    |

| ESD MM                                                                                     | Machine Model (MM) ESD Rating are (Notes 2 and 3)        | 250          | V    |

| ESD<br>CDM                                                                                 | Charge Device Model (CDM) ESD Rating are (Notes 2 and 3) | 2000         | V    |

| LU                                                                                         | Latch-up Protection (Note ) - Pins IN, OUT, EN           | 100          | mA   |

| T <sub>STG</sub>                                                                           | Storage Temperature Range                                | -40 to + 150 | °C   |

| MSL                                                                                        | Moisture Sensitivity (Note 2)                            | Level 1      |      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. According to JEDEC standard JESD22-A108.

- 2. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020.

- 3. This device series contains ESD protection and passes the following tests Human Body Model (HBM) ±8.0 kV per JEDEC standard: JESD22–A114 for all pins. Machine Model (MM) ±250 V per JEDEC standard: JESD22–A115 for all pins. Charge Device Model (CDM) ±2.0 kV per JEDEC standard: JESD22–C101 for all pins.

- 4. Latch-up Current Maximum Rating: ±100 mA per JEDEC standard: JESD78 Class II.

#### **OPERATING CONDITIONS**

| Symbol           | Parameter                          | Conditions             |               | Min | Тур  | Max  | Unit |

|------------------|------------------------------------|------------------------|---------------|-----|------|------|------|

| V <sub>IN</sub>  | Operational Power Supply           |                        | 1.0           |     | 3.6  | V    |      |

| V <sub>EN</sub>  | Enable Voltage                     |                        |               | 0   |      | 3.6  |      |

| T <sub>A</sub>   | Ambient Temperature Range          |                        |               | -40 | 25   | +85  | °C   |

| TJ               | Junction Temperature Range         |                        |               | -40 | 25   | +125 | °C   |

| C <sub>IN</sub>  | Decoupling input capacitor         |                        |               | 1   |      |      | μF   |

| C <sub>OUT</sub> | Decoupling output capacitor        |                        |               | 1   |      |      | μF   |

| $R_{\theta JA}$  | Thermal Resistance Junction to Air | WLCSP package (Note 5) |               |     | 100  |      | °C/W |

| l <sub>OUT</sub> | Maximum DC current                 |                        |               |     |      | 3    | Α    |

| P <sub>D</sub>   | Power Dissipation Rating (Note 6)  | $T_A \le 25^{\circ}C$  | WLCSP package |     | 0.66 |      | W    |

|                  |                                    | T <sub>A</sub> = 85°C  | WLCSP package |     | 0.26 |      | W    |

- 5. The  $R_{\theta JA}$  is dependent of the PCB heat dissipation and thermal via.

- 6. The maximum power dissipation (PD) is given by the following formula:

$$P_D = \frac{T_{JMAX} - T_A}{R_{\theta JA}}$$

ELECTRICAL CHARACTERISTICS Min and Max Limits apply for T<sub>A</sub> between -40°C to +85°C for VIN between 1.0 V to 3.6 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 3.3 \text{ V}$  (Unless otherwise noted).

| Symbol              | Parameter                                  |                         | Conditions                                      |     | Тур  | Max | Unit |

|---------------------|--------------------------------------------|-------------------------|-------------------------------------------------|-----|------|-----|------|

| POWER S             | WITCH                                      |                         |                                                 |     |      |     |      |

|                     |                                            |                         | I = 200 mA, 25°C                                |     | 15   | 26  | mΩ   |

|                     |                                            | V <sub>IN</sub> = 3.6 V | I = 200 mA, T <sub>A</sub> = 85°C               |     |      | 28  |      |

|                     |                                            |                         | T <sub>J</sub> = 125°C                          |     |      | 29  |      |

|                     |                                            |                         | I = 200 mA, 25°C                                |     | 18   | 30  |      |

|                     |                                            | V <sub>IN</sub> = 2.5 V | I = 200 mA, T <sub>A</sub> = 85°C               |     |      | 32  |      |

|                     |                                            |                         | T <sub>J</sub> = 125°C                          |     |      | 35  |      |

| R <sub>DS(on)</sub> | Static drain–source on–state resistance    |                         | I = 200 mA, 25°C                                |     | 23   | 40  |      |

|                     | resistance                                 | V <sub>IN</sub> = 1.8 V | I = 200 mA, Full Ta                             |     |      | 42  |      |

|                     |                                            |                         | T <sub>J</sub> = 125°C                          |     |      | 44  |      |

|                     |                                            |                         | I = 200 mA, 25°C                                |     | 45   | 80  |      |

|                     |                                            | V <sub>IN</sub> = 1.2 V | I = 200 mA, Full Ta                             |     |      | 84  |      |

|                     |                                            |                         | T <sub>J</sub> = 125°C                          |     |      | 85  |      |

|                     |                                            | V <sub>IN</sub> = 1.1 V | I = 200 mA, 25°C                                |     | 62   |     |      |

| R <sub>dis</sub>    | Output discharge path                      | V <sub>IN</sub> = 3.3 V | EN = low                                        | 50  | 65   | 90  | Ω    |

| V <sub>IH</sub>     | High-level input voltage                   |                         |                                                 | 1.1 |      |     | .,   |

| V <sub>IL</sub>     | Low-level input voltage                    |                         |                                                 |     |      | 0.5 | V    |

| QUIESCEN            | IT CURRENT                                 |                         |                                                 |     |      |     |      |

| I <sub>std</sub>    | Standby current                            | V <sub>IN</sub> = 3.3 V | EN = low, No load                               |     | 0.01 | 0.6 |      |

| Iq                  | Quiescent current                          | V <sub>IN</sub> = 3.3 V | EN = high, No load                              |     | 0.2  | 0.6 | μΑ   |

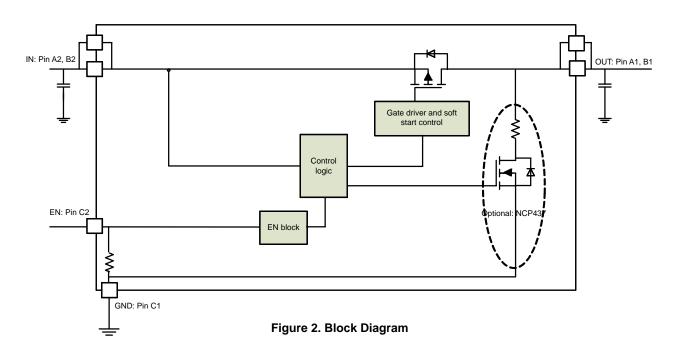

| TIMINGS             |                                            |                         |                                                 |     |      |     |      |

| T <sub>EN</sub>     | Enable time                                |                         | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                  | 20  | 39   | 55  |      |

| T <sub>R</sub>      | Output rise time                           |                         | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                  | 10  | 25   | 40  | μς   |

| T <sub>ON</sub>     | ON time (T <sub>EN+</sub> T <sub>R</sub> ) | V <sub>IN</sub> = 3.6 V | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                  | 30  | 64   | 95  |      |

| T <sub>DIS</sub>    | Disable time                               | (Note 8)                | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                  |     | 20   |     | _ μο |

| T <sub>F</sub>      | Output fall time                           | 7                       | NCP437. $R_L = 25 \Omega$ , $C_{OUT} = 1 \mu F$ | 20  | 55   | 80  |      |

|                     | -                                          | •                       |                                                 |     |      |     |      |

<sup>7.</sup> Guaranteed by design and characterization

8. Parameters are guaranteed for C<sub>LOAD</sub> and R<sub>LOAD</sub> connected to the OUT pin with respect to the ground

#### **TIMINGS**

Figure 3. Enable, Rise and Fall Time

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The NCP437 is a high side P channel MOSFET power distribution switch designed to isolate ICs connected on the battery in order to save energy. The part can be turned on, with a wide range of battery from 1.0 V to 3.6 V.

#### **Enable Input**

Enable pin is an active high. The path is opened when EN pin is tied low (disable), forcing P MOS switch off.

The IN/OUT path is activated with a minimum of  $V_{IN}$  of 1.2 V and EN forced to high level.

#### **Auto Discharge**

NMOS FET is placed between the output pin and GND, in order to discharge the application capacitor connected on OUT pin.

The auto-discharge is activated when EN pin is set to low level (disable state).

The discharge path (Pull down NMOS) stays activated as long as EN pin is set at low level and  $V_{\rm IN} > 1.2$  V.

In order to limit the current across the internal discharge N–MOSFET, the typical value is set at 65  $\Omega$ .

## $C_{IN}$ and $C_{OUT}$ Capacitors

IN and OUT, 1  $\mu$ F, at least, capacitors must be placed as close as possible the part to for stability improvement.

#### APPLICATION INFORMATION

#### **Power Dissipation**

Main contributor in term of junction temperature is the power dissipation of the power MOSFET. Assuming this, the power dissipation and the junction temperature in normal mode can be calculated with the following equations:

$$P_D = R_{DS(on)} \times (I_{OUT})^2$$

$P_D$  = Power dissipation (W)

$R_{DS(on)}$  = Power MOSFET on resistance ( $\Omega$ )

$I_{OUT}$  = Output current (A)

$$T_{.J} = R_D \times R_{0.JA} + T_A$$

$T_J$  = Junction temperature (°C)

$R_{\theta JA}$  = Package thermal resistance (°C/W)

$T_A$  = Ambient temperature (°C)

#### **PCB Recommendations**

The NCP437 integrates an up to 3 A rated PMOS FET, and the PCB design rules must be respected to properly evacuate the heat out of the silicon. By increasing PCB area, especially around IN and OUT pins, the  $R_{\theta JA}$  of the package can be decreased, allowing higher power dissipation.

Routing example: 2 oz, 4 layers with vias across two internal inners.

Figure 4.

Example of application definition.

$$T_J - T_A = R_{\theta JA} \times P_D = R_{\theta JA} \times R_{DS(on)} \times I^2$$

T<sub>J</sub>: Junction Temperature.

T<sub>A</sub>: Ambient Temperature.

$R_{\theta}$  = Thermal resistance between IC and air, through PCB.

R<sub>DS(on)</sub>: Intrinsic resistance of the IC MOSFET.

I: Load DC current.

Taking into account of  $R_{\theta}$  obtain with:

• 1 oz, 2 layers: 100°C/W.

At 3 A, 25°C ambient temperature,  $R_{DS(on}$  20 m $\Omega$  @  $V_{IN}$  5 V, the junction temperature will be:

$$T_J = R_{\theta JA} \times P_D = 25 + (0.02 \times 3^2) \times 100 = 43^{\circ}C$$

Taking into account of  $R_{\theta}$  obtain with:

• 2 oz, 4 layers: 60°C/W.

At 3 A, 65°C ambient temperature,  $R_{DS(on)}$  24 m $\Omega$  @  $V_{IN}$  5 V, the junction temperature will be:

$$\mathsf{T_J} = \mathsf{T_A} + \mathsf{R_{\theta}} \times \mathsf{P_D} = 65 + \left(0.024 \times 3^2\right) \times 60 = 78^{\circ}\,\mathsf{C}$$

#### **ORDERING INFORMATION**

| Device      | Marking | Option                 | Package                       | Shipping <sup>†</sup> |

|-------------|---------|------------------------|-------------------------------|-----------------------|

| NCP437FCT2G | AR      | Auto discharge         | WLCSP 1 x 1.5 mm<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP436FCT2G | AQ      | Without Auto discharge | WLCSP 1 x 1.5 mm<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

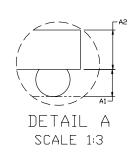

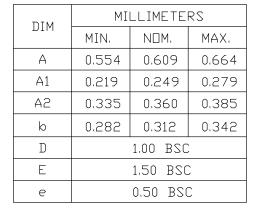

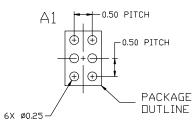

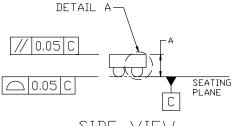

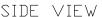

#### WLCSP6 1.0x1.5x0.609 CASE 567FH **ISSUE A**

**DATE 21 JUN 2022**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS

- COPLANARITY APPLIES TO THE SPHERICAL CROWNS OF THE SOLDER BALLS.

## RECOMMENDED MOUNTING FOOTPRINT\*

For additional information on our Pb-Free the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

= Specific Device Code XXX Α = Assembly Location

= Year

W = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| g.               |                      |                                                                                                                                                                                     |             |  |  |  |  |

|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DOCUMENT NUMBER: | 98AON79918E          | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |

| DESCRIPTION:     | WLCSP6 1.0x1.5x0.609 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative