# CMOS LSI Iris/Zoom/Focus/Day-Night Switching Drive Controller LC898201

#### Overview

LC898201 is the appropriate motor control LSI for the surveillance camera usage, and it can drive iris, focus, zoom and Day/Night switching simultaneously.

It incorporates feedback control circuits (max 2-systems), stepper motor control circuits (max 3-system) and VCM control circuit (1-system).

- Feedback Control Applies Iris

Stepper Motor Controls Apply Focus, Zoom and Day/Night

Switching

- Feedback Control Applies Iris

Stepper Motor Controls Apply Focus and Zoom

VCM Applies Day/Night Switching

LC898201 can control a variety of lens units like these examples.

#### **Features**

- Built-in Equalizer Circuit by Digital Operation

- Iris Control Equalizer Circuit

- Focus Control Equalizer Circuit (MR sensor can be connected)

- Coefficients can be Set Arbitrarily through the SPI Interface

- Computed Values in the Equalizer can be Monitored

- Built-in 3ch Stepper Motor Control Circuits

- SPI Bus Interface

- PI Control Circuit

- 30 mA Sink Output Terminal

- Built-in PI Detecting Function (A/D method)

- A/D Converter

- 12bit (6ch): Iris, Focus, PI Detection, General

- D/A Converter

- 8bit (4ch): Hall Offset, Constant Current Bias, MR Sensor Offset

- Operation Amplifier

- ◆ 3ch (Iris Control ×1, Focus Control ×2)

- PWM Pulse Generator

- PWM Pulse Generator for Feedback Control (Up to 12 bit Accuracy)

- PWM Pulse Generator for Stepper Motor Control (Up to 1024 Micro Steps)

- PWM Pulse Generator for General-purpose H-Bridge (128 Voltage Levels)

- Motor Driver

- ch1 to ch6: Io max = 200 mA

- ch7: Io max = 300 mA

- Built-in Thermal Protection Circuit

- Built-in Low-voltage Malfunction Prevention Circuit

TQFP64 7x7 CASE 932BC

#### **ORDERING INFORMATION**

| Device        | Package                                   | Shipping <sup>†</sup> |

|---------------|-------------------------------------------|-----------------------|

| LC898201TA-NH | TQFP64 7x7<br>(Pb–Free /<br>Halogen Free) | 1000 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### Features (Continued)

- Operation Clock

- Selective Usage either Internal OSC (Typ. 48 MHz) or External Oscillating Circuit (48 MHz)

- Package

- TQFP64  $(7 \times 7)$  0.4 mm Pitch

- Lead-free, Halogen-free

- Power Supply Voltage

- Logic Unit: 2.7 V to 3.6 V (IO, Internal Core)

- Driver Unit: 2.7 V to 5.5 V (Motor Drive)

1

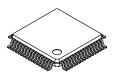

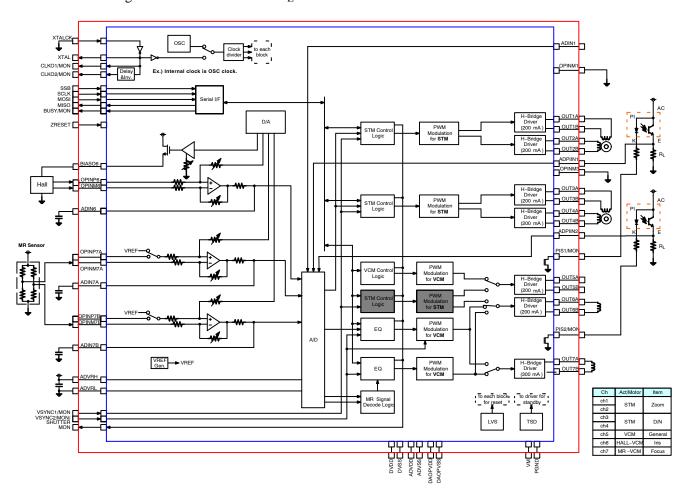

### **BLOCK DIAGRAMS**

### **Application 1**

Stepper 3ch-ex.1 & using Crystal oscillator (or Ceramic oscillator) & PI sensor: R<sub>L</sub> emitter connection.

Figure 1. Application 1

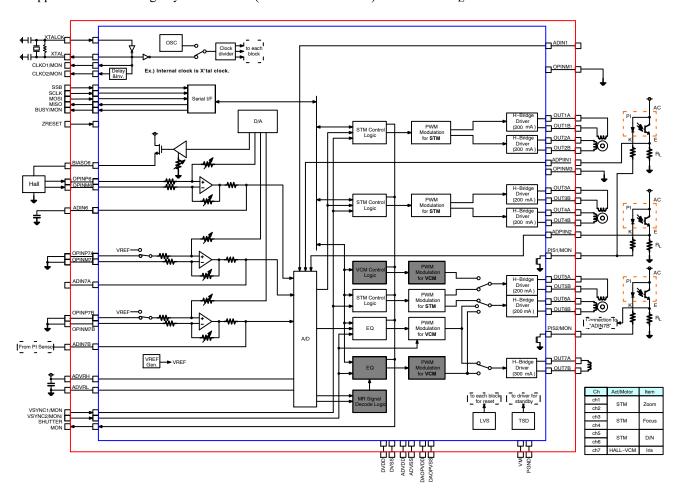

# **Application 2**

Stepper 3ch-ex.2 & using internal OSC & PI sensor: R<sub>L</sub> collector connection.

Figure 2. Application 2

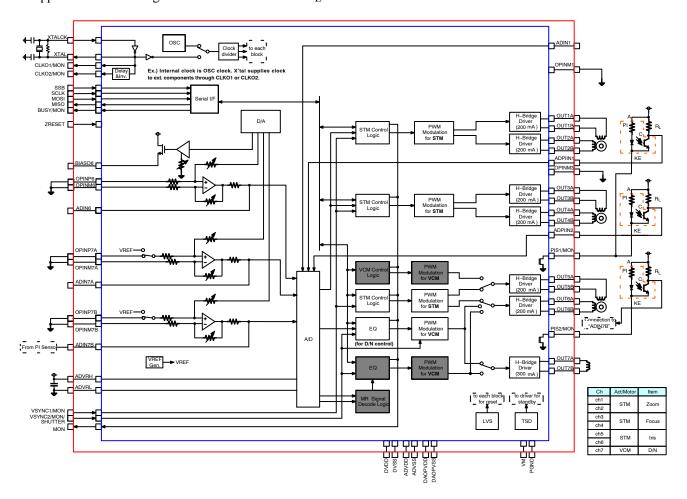

# Application-3

Stepper 2ch & using internal OSC & PI sensor: R<sub>L</sub> emitter connection.

Figure 3. Application 3

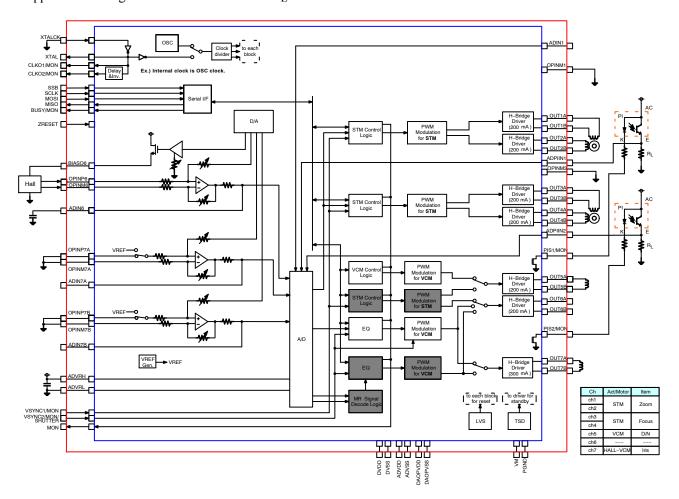

# Application-4

MR-VCM & using internal OSC & PI sensor: R<sub>L</sub> emitter connection.

Figure 4. Application 4

#### **PIN DESCRIPTION**

**Table 1. PIN DESCRIPTION**

**SPI INTERFACE (SLAVE)**

| ТҮРЕ |        |                              |            |    |             |  |

|------|--------|------------------------------|------------|----|-------------|--|

| I    | INPUT  | Р                            | Power, GND | NC | NOT CONNECT |  |

| 0    | OUTPUT |                              |            |    | •           |  |

| B(I) |        | BIDIRECTION: INPUT at Reset  |            |    |             |  |

| B(O) |        | BIDIRECTION: OUTPUT at Reset |            |    |             |  |

|   | SSB                         | 1    | Chip select                                      |

|---|-----------------------------|------|--------------------------------------------------|

|   | SCLK                        | 1    | Clock                                            |

|   | MOSI                        | 1    | Received data                                    |

|   | MISO                        | B(O) | Transmit data                                    |

|   | BUSY/MON                    | B(O) | Transfer busy / Monitor output                   |

| F | PI SENSOR DRIVE SIGNAL OUTF | TUT  |                                                  |

|   | PIS1/MON                    | B(O) | PI sensor drive signal output 1 / Monitor output |

|   | PIS2/MON                    | B(O) | PI sensor drive signal output 2 / Monitor output |

VSYNC1/MON B(I) Video synchronizing signal input / Monitor output (with pull-down resistance)

VSYNC2/MON /SHUTTER B(I) Video synchronizing signal input / Monitor output / Shutter input

(with pull-down resistance)

#### MONITOR OUTPUT

| MON | B(O) | Monitor output |

|-----|------|----------------|

|-----|------|----------------|

#### **CLOCK OUTPUT**

XTALCK

I Oscillation amplifier input

XTAL

O Oscillation amplifier output

CLKO1/MON

B(O) Clock output 1 / Monitor output

CLKO2/MON

B(O) Clock output 2 / Monitor output

**RESET**

ZRESET I Reset signal input (Low active)

### **BIAS CURRENT PIN**

BIASO6 O CH6 Bias current output

### OP AMP PIN

OPINP6

I

CH6 OP Amp input (+)

OPINM6

I

CH6 OP Amp input (-)

OPINP7A

I

CH7-A OP Amp input (+)

OPINM7A

I

CH7-A OP Amp input (-)

OPINP7B

I

CH7-B OP Amp input (+)

OPINM7B

I

CH7-B OP Amp input (-)

### A/D INPUT PIN

ADIN1 B General A/D input

ADIN6 B CH6 A/D input (CH6 OP Amp output)

ADIN7A B CH7-A A/D input (CH7 OP Amp output)

| A/D INPUT PIN |   |                                       |

|---------------|---|---------------------------------------|

| ADIN7B        | В | CH7-B A/D input (CH7 OP Amp output)   |

| ADPIIN1       | 1 | CH1/2 PI sensor signal A/D input      |

| ADPIIN2       | 1 | CH3/4 PI sensor signal A/D input      |

| ADVRH         | 1 | A/D conversion range standard voltage |

| ADVRL         | 1 | A/D conversion range standard voltage |

| H-BRIDGE      |   |                                       |

| OUT1A         | Ο | CH1 H-Bridge output                   |

| OUT1B         | 0 | CH1 H-Bridge output                   |

| OUT2A         | 0 | CH2 H-Bridge output                   |

| OUT2B         | 0 | CH2 H-Bridge output                   |

| OUT3A         | 0 | CH3 H-Bridge output                   |

| OUT3B         | 0 | CH3 H-Bridge output                   |

| OUT4A         | 0 | CH4 H-Bridge output                   |

| OUT4B         | 0 | CH4 H-Bridge output                   |

| OUT5A         | 0 | CH5 H-Bridge output                   |

| OUT5B         | 0 | CH5 H-Bridge output                   |

| OUT6A         | 0 | CH6 H-Bridge output                   |

| OUT6B         | 0 | CH6 H-Bridge output                   |

| OUT7A         | 0 | CH7 H-Bridge output                   |

| OUT7B         | 0 | CH7 H-Bridge output                   |

| MISCELLANEOUS |   |                                       |

| OPINM1        | 1 | Connect to GND (DAOPVSS)              |

| OPINM3        | 1 | Connect to GND (DAOPVSS)              |

| POWER PIN     |   |                                       |

| DVDD          | Р | Digital VDD                           |

| DVSS          | Р | Digital GND                           |

| DAOPVDD       | Р | D/A, OP Amp VDD                       |

| DAOPVSS       | Р | D/A, OP Amp GND                       |

| ADVDD         | Р | A/D VDD                               |

| ADVSS         | Р | A/D GND                               |

| VM            | Р | H-Bridge VDD                          |

| PGND          | Р | H-Bridge GND                          |

### Process when pins are not used

- PIN TYPE "O" The pin must be left open

- PIN TYPE "I" The pin must not be left open. Please make sure to connect the pin to  $V_{DD}$  or  $V_{SS}$  even when it is not used. (Please check with us whether to connect to  $V_{DD}$  or  $V_{SS}$ )

- PIN TYPE "B" Please contact us if you are uncertain about a processing method in the pin description in the PIN layout table

A problem may occur if the processing method is used wrongly for any unused pin.

Please make sure to contact us.

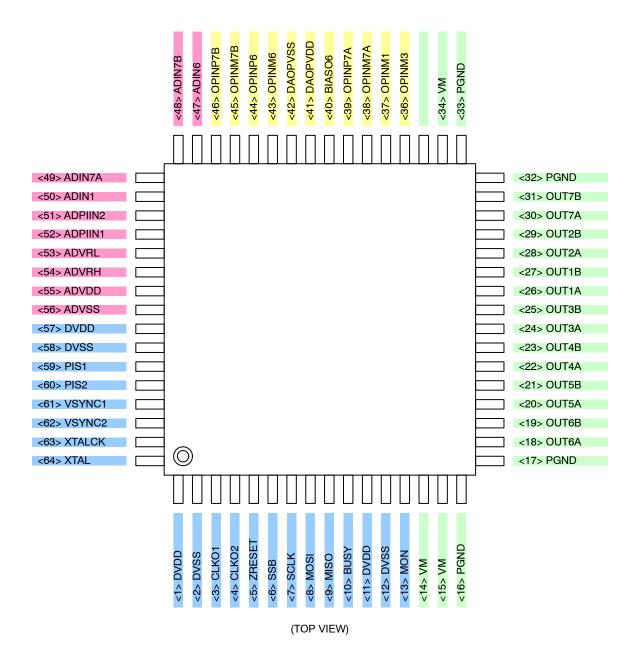

#### **PIN ASSIGNMENT**

Figure 5. TQFP64 (7×7)

### **PIN NUMBER**

Table 2. PIN NUMBER

| Pin No. | Туре | Pin name |

|---------|------|----------|

| 1       | Р    | DVDD     |

| 2       | Р    | DVSS     |

| 3       | B(O) | CLKO1    |

| 4       | B(O) | CLKO2    |

| 5       | I    | ZRESET   |

| 6       | I    | SSB      |

| 7       | I    | SCLK     |

| 8       | I    | MOSI     |

| 9       | B(O) | MISO     |

| 10      | B(O) | BUSY     |

| 11      | Р    | DVDD     |

| 12      | Р    | DVSS     |

| 13      | B(O) | MON      |

| 14      | Р    | VM       |

| 15      | Р    | VM       |

| 16      | Р    | PGND     |

| 17      | Р    | PGND     |

| 18      | 0    | OUT6A    |

| 19      | 0    | OUT6B    |

| 20      | 0    | OUT5A    |

| 21      | 0    | OUT5B    |

| 22      | 0    | OUT4A    |

| 23      | 0    | OUT4B    |

| 24      | 0    | OUT3A    |

| 25      | 0    | OUT3B    |

| 26      | 0    | OUT1A    |

| 27      | 0    | OUT1B    |

| 28      | 0    | OUT2A    |

| 29      | 0    | OUT2B    |

| 30      | 0    | OUT7A    |

| 31      | 0    | OUT7B    |

| 32      | Р    | PGND     |

| 33      | Р    | PGND     |

| 34      | Р    | VM       |

| 35      | Р    | VM       |

| 36      | 1    | ОРІММЗ   |

| 37      | 1    | OPINM1   |

| 38      | I    | OPINM7A  |

| 39      | I    | OPINP7A  |

| 40      | 0    | BIASO6   |

Table 2. PIN NUMBER (continued)

| Pin No. | Туре | Pin name |

|---------|------|----------|

| 41      | Р    | DAOPVDD  |

| 42      | Р    | DAOPVSS  |

| 43      | I    | OPINM6   |

| 44      | I    | OPINP6   |

| 45      | I    | ОРІММ7В  |

| 46      | I    | OPINP7B  |

| 47      | В    | ADIN6    |

| 48      | В    | ADIN7B   |

| 49      | В    | ADIN7A   |

| 50      | В    | ADIN1    |

| 51      | I    | ADPIIN2  |

| 52      | I    | ADPIIN1  |

| 53      | I    | ADVRL    |

| 54      | I    | ADVRH    |

| 55      | Р    | ADVDD    |

| 56      | Р    | ADVSS    |

| 57      | Р    | DVDD     |

| 58      | Р    | DVSS     |

| 59      | B(O) | PIS1     |

| 60      | B(O) | PIS2     |

| 61      | B(I) | VSYNC1   |

| 62      | B(I) | VSYNC2   |

| 63      | I    | XTALCK   |

| 64      | 0    | XTAL     |

#### **ELECTRICAL CHARACTERISTICS**

### Logic, Analog

Logic, Analog power: DVDD/DVSS, OPDAVDD/ OPDAVSS, ADVDD/ADVSS, these should be connected at the same voltage. They are shown DVDD/DVSS as follows.

### ABSOLUTE MAXIMUM RATINGS (DVSS = 0 V)

| Parameter             | Symbol                             | Conditions            | Ratings          | Unit |

|-----------------------|------------------------------------|-----------------------|------------------|------|

| Supply Voltage        | DVDD max                           | T <sub>A</sub> ≤ 25°C | -0.3 to 4.6      | V    |

| Input/Output Voltage  | V <sub>IN</sub> , V <sub>OUT</sub> | T <sub>A</sub> ≤ 25°C | -0.3 to DVDD+0.3 | V    |

| Storage Temperature   | T <sub>stg</sub>                   |                       | -55 to 125       | °C   |

| Operating Temperature | T <sub>opr</sub>                   |                       | –20 to 85        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### ALLOWABLE OPERATING RANGES ( $T_A = -20 \text{ to } 85^{\circ}\text{C}$ , DVSS = 0 V)

| Parameter            | Symbol          | Min | Тур | Max  | Unit | Applicable Pins           |

|----------------------|-----------------|-----|-----|------|------|---------------------------|

| Power Supply Voltage | DVDD            | 2.7 | 3.3 | 3.6  | V    |                           |

| Input Voltage Range  | V <sub>IN</sub> | 0   | -   | DVDD | V    | Except for OPINM1, OPINM3 |

|                      |                 | 0   | -   | VM   | V    | OPINM1, OPINM3            |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### DC CHARACTERISTICS: INPUT/OUTPUT LEVEL (T<sub>A</sub> = -20 to 85°C, DVSS = 0 V, DVDD = 2.7 to 3.6 V)

| Parameter                 | Symbol           | Conditions                          | Min        | Тур | Max       | Unit | Applicable<br>Pins |

|---------------------------|------------------|-------------------------------------|------------|-----|-----------|------|--------------------|

| High-level Input Voltage  | V <sub>IH</sub>  | CMOS                                | 0.7 DVDD   |     |           | V    | (2)(3)             |

| Low-level Input Voltage   | V <sub>IL</sub>  |                                     |            |     | 0.2 DVDD  | V    |                    |

| High-level Input Voltage  | V <sub>IH</sub>  | CMOS Schmidt                        | 0.75 DVDD  |     |           | V    | (1)                |

| Low-level Input Voltage   | V <sub>IL</sub>  |                                     |            |     | 0.15 DVDD | V    |                    |

| High-level Output Voltage | V <sub>OH</sub>  | I <sub>OH</sub> = -4 mA             | DVDD - 0.4 |     |           | V    | (2)(3)(4)          |

| Low-level Output Voltage  | V <sub>OL</sub>  | I <sub>OL</sub> = 4 mA              |            |     | 0.4       | V    | (2)(3)             |

|                           |                  | I <sub>OL</sub> = 30 mA             |            |     | 0.4       | V    | (4)                |

| PullDown Resistance       | Rdn              |                                     | 40         | 80  | 200       | kΩ   | (3)                |

| Analog Input Voltage      | V <sub>AI</sub>  |                                     | DVSS       |     | DVDD      | V    | (5)                |

|                           |                  |                                     | PGND       |     | VM        | V    | (6)                |

| VGA Output Resistance     | R <sub>out</sub> |                                     |            | 1   |           | kΩ   | (7)                |

| Analog Output Current     | I <sub>AO</sub>  | CMSDAC<br>= 001b & WH_DAV4<br>= 00h |            | 1   |           | mA   | (8)                |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTE: Applicable Pins:

- (1) ZRESET, SSB, SCLK, MOSI

- (2) MISO, BUSY, MON, CLKO1, CLKO2

- (3) VSYNC1, VSYNC2

- (4) PIS1, PIS2

- (5) OPINP6, OPINM6, OPINP7A, OPINM7A, OPINP7B, OPINM7B, ADPIIN1, ADPIIN2

- (6) OPINM1, OPINM3

- (7) ADIN1, ADIN6, ADIN7A, ADIN7B

- (8) BIASO6

VM

### ABSOLUTE MAXIMUM RATINGS ( $T_A = 25$ °C, PGND = 0 V)

| Parameter                 | Symbol              | Conditions                                     | Ratings     | Unit |  |

|---------------------------|---------------------|------------------------------------------------|-------------|------|--|

| Supply Voltage            | VM <sub>max</sub>   |                                                | -0.3 to 7.0 | V    |  |

| Output Peak Current       | I <sub>opeak1</sub> | OUT1A/B to OUT6A/B<br>t ≤ 10 ms, On-duty ≤ 20% | 300         | mA   |  |

|                           | I <sub>opeak2</sub> | OUT7A/B<br>t ≤ 10 ms, On-duty ≤ 20%            | 450         | mA   |  |

| Output Continuous Current | I <sub>omax1</sub>  | OUT1A/B to OUT6A/B                             | 200         | mA   |  |

|                           | I <sub>omax2</sub>  | OUT7A/B                                        | 300         | mA   |  |

| Storage Temperature       | T <sub>stg</sub>    |                                                | -55 to 125  | °C   |  |

| Operating Temperature     | T <sub>opr</sub>    |                                                | -20 to 85   | °C   |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### ALLOWABLE OPERATING RANGES (T<sub>A</sub> = 25°C, PGND = 0 V)

| Parameter            | Symbol | Conditions | Ratings    | Unit |

|----------------------|--------|------------|------------|------|

| Power Supply Voltage | VM     |            | 2.7 to 5.5 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, PGND = 0 V, VM = 5 V)

| Parameter             | Symbol           | Conditions                  | Min | Тур  | Max | Unit | Applicable Pins |

|-----------------------|------------------|-----------------------------|-----|------|-----|------|-----------------|

| Output ON Resistance  | R <sub>onu</sub> | I <sub>O</sub> = 200 mA Pch |     | 0.85 |     | Ω    | (9)             |

|                       | R <sub>ond</sub> | I <sub>O</sub> = 200 mA Nch |     | 0.45 |     | Ω    |                 |

| Output ON Resistance  | R <sub>onu</sub> | I <sub>O</sub> = 300 mA Pch |     | 0.85 |     | Ω    | (10)            |

|                       | R <sub>ond</sub> | I <sub>O</sub> = 300 mA Nch |     | 0.45 |     | Ω    |                 |

| Diode Forward Voltage | $V_D$            | I <sub>D</sub> = -200 mA    |     | 0.9  |     | V    | (9)             |

|                       |                  | I <sub>D</sub> = -300 mA    |     | 0.9  |     | V    | (10)            |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTE: Applicable Pins:

(9) OUT1A, OUT1B, OUT2A, OUT2B, OUT3A, OUT3B, OUT4A, OUT4B, OUT5A, OUT5B, OUT6A, OUT6B (10) OUT7A, OUT7B

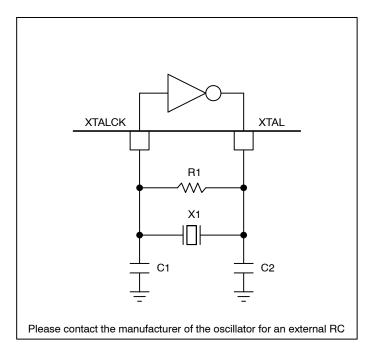

# **EXAMPLE OF EXTERNAL CIRCUIT**

Connection example of oscillation circuit.

<sup>\*</sup> In the case of X'tal, it takes about 50 ms for oscillation to stabilize (please check with the manufacturer for a precise time period).

Figure 6. Example of External Circuit

### **AC CHARACTERISTICS**

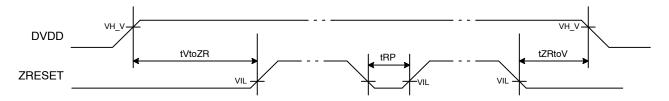

### 1-a) Power Supply, Reset Pin

Figure 7.

### 1-b) Specification

DVDD: DVDD, OPDAVDD, ADVDD

VH\_V: 2.7 V

VIL:  $0.15 \times DVDD$

| Parameter                                            | Symbol | Min | Тур | Max | Unit |

|------------------------------------------------------|--------|-----|-----|-----|------|

| The time from the rise of DVDD to the rise of ZRESET | tVtoZR | 1   |     |     | ms   |

| The time from the fall of DVDD to the fall of ZRESET | tZRtoV | 500 |     |     | μs   |

| Low period of ZRESET                                 | tRP    | 100 |     |     | μs   |

VM can be turn on/off regardless above power supply AC timing.

### 2-a) Power Supply, Reset Pin

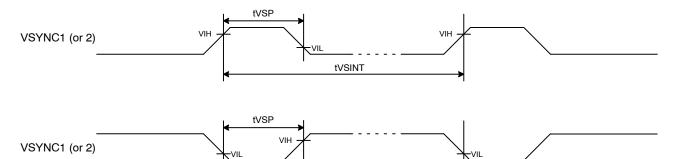

Upper: "H" active Use setting of 0250h-0253h-bit2 = 0Lower: "L" active Use setting of the above bit = 1

Figure 8.

tVSINT

### 2-b) Specification

VIH:  $0.7 \times DVDD$ VIL:  $0.2 \times DVDD$

| Parameter                     | Symbol | Conditions      | Min | Тур | Max | Unit |

|-------------------------------|--------|-----------------|-----|-----|-----|------|

| Active period of VSYNC1(or 2) | tVSP   | STMCLK = 12 MHz | 100 |     |     | ns   |

| Interval time of VSYNC1(or 2) | tVSINT |                 | 2   |     |     | ms   |

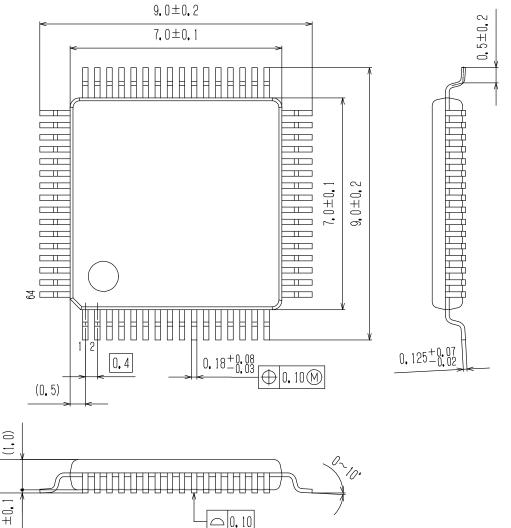

#### TQFP64 7x7 / TQFP64 CASE 932BC ISSUE O

**DATE 31 MAY 2012**

| DOCUMENT NUMBER: 98AON80202E |                     | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                 | TQFP64 7X7 / TQFP64 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

1,2 MAX

onsemi, ONSEMi., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative