# LDO Regulator, 300 mA, Low Dropout Voltage, Ultra Low Noise, High PSRR with Power Good NCV8164

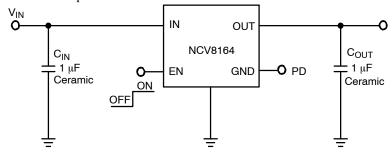

The NCV8164 is a 300 mA LDO, next generation of high PSRR, ultra—low noise and low dropout regulators with Power Good open collector output. Designed to meet the requirements of RF and sensitive analog circuits, the NCV8164 device provides ultra—low noise, high PSRR and low quiescent current. The device also offer excellent load/line transients. The NCV8164 is designed to work with a 1  $\mu F$  input and a 1  $\mu F$  output ceramic capacitor. It is available in industry standard TSOP–5, WDFNW6 0.65P, 2 mm x 2 mm and DFNW8 0.65P, 3 mm x 3 mm.

#### **Features**

- Operating Input Voltage Range: 1.6 V to 5.5 V

- Available in Fixed Voltage Option: 1.2 V to 5.0 V

- Adjustable Version Reference Voltage: 1.2 V

- ±2% Accuracy Over Load and Temperature

- Ultra Low Quiescent Current Typ. 30 μA

- Standby Current: Typ. 0.1 μA

- Very Low Dropout: 110 mV at 300 mA for 3.3 V Variant

- Ultra High PSRR: Typ. 85 dB at 10 mA, f = 1 kHz

- Ultra Low Noise: 9 μV<sub>RMS</sub> (Fixed Version)

- Stable with a 1 µF Small Case Size Ceramic Capacitors

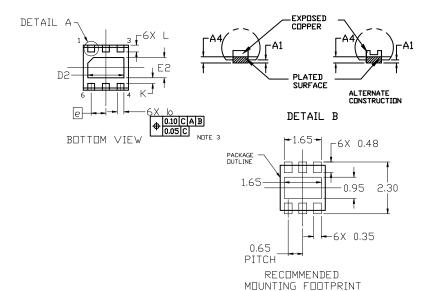

- Available in TSOP–5 3 mm x 1.5 mm x 1 mm CASE 483

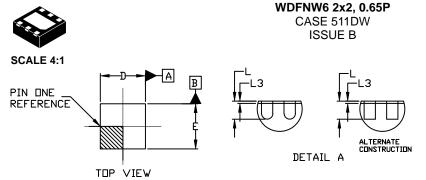

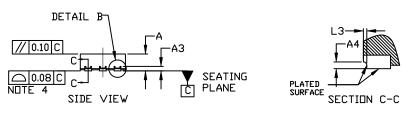

- ♦ WDFNW6 2 mm x 2 mm x 0.75 mm CASE 511DW

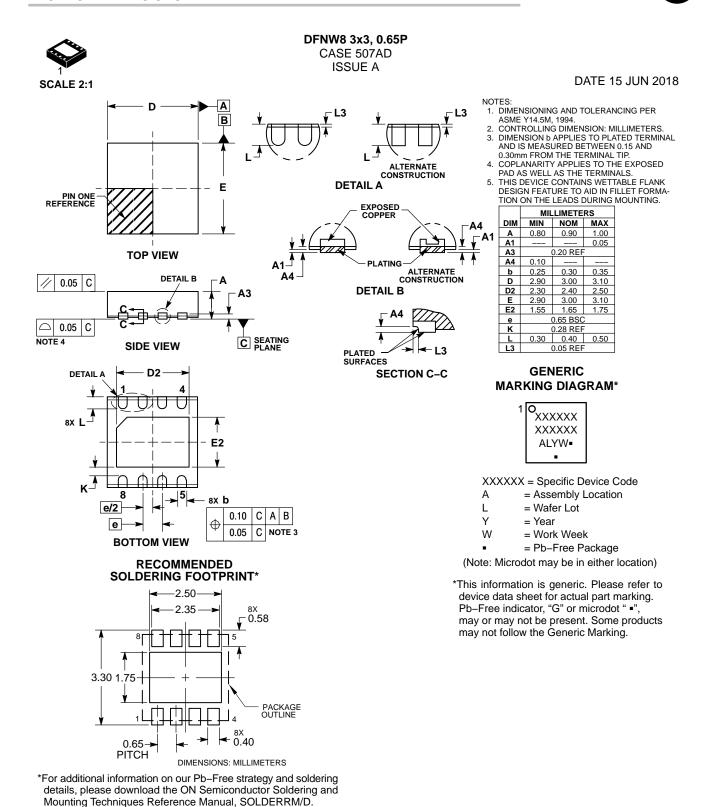

- DFNW8 3 mm x 3 mm x 0.9 mm CASE 507AD

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements

- AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- Communication Systems

- In-Vehicle Networking

- Telematics, Infotainment and Clusters

- General Purpose Automotive

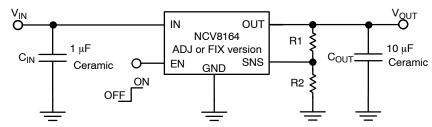

Figure 1. Typical Application Schematics

1

# MARKING DIAGRAMS TSOP-5 CASE 483 WDFNW6 2x2, 0.65P CASE 511DW DFNW8 3x3, 0.65P CASE 507AD XXXAYW XXM XXM ALYW ALYW T

XXX = Specific Device Code A = Assembly Location

L = Wafer Lot

M = Month Code

Y = Year

W = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

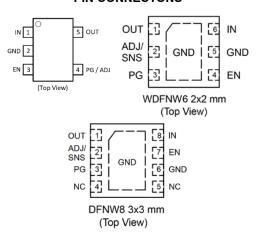

#### **PIN CONNECTONS**

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 10 of this data sheet.

# **PIN FUNCTION DESCRIPTION**

| Pin No.<br>TSOP-5 | Pin No.<br>WDFNW6 | Pin No.<br>DFNW8 | Pin<br>Name | Description                                                                                                           |  |

|-------------------|-------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 1                 | 6                 | 8                | IN          | Input voltage supply pin                                                                                              |  |

| 5                 | 1                 | 1                | OUT         | Regulated output voltage. The output should be bypassed with small 1 $\mu\text{F}$ ceramic capacitor                  |  |

| 3                 | 4                 | 7                | EN          | Chip enable: Applying $V_{EN} < 0.25 \ V$ disables the regulator, Pulling $V_{EN} > 0.7 \ V$ enables the LDO          |  |

| 4 / –             | 3                 | 3                | PG          | Power Good, open collector. Use 10 k $\Omega$ to 100 k $\Omega$ pull—up resistor connected to output or input voltage |  |

| 2                 | 5                 | 6                | GND         | Common ground connection                                                                                              |  |

| - / 4             | 2                 | 2                | ADJ         | Adjustable output feedback pin (for adjustable version only)                                                          |  |

| -                 | 2                 | 2                | SNS         | Sense feedback pin. Must be connected to OUT pin on PCB (for fixed versions only)                                     |  |

| _                 | -                 | 4, 5             | N/C         | Not connected, pin can be tied to ground plane for better power dissipation                                           |  |

| _                 | EPAD              | EPAD             | EPAD        | Expose pad should be tied to ground plane for better power dissipation                                                |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                        | Symbol             | Value                                | Unit |

|-----------------------------------------------|--------------------|--------------------------------------|------|

| Input Voltage (Note 1)                        | V <sub>IN</sub>    | -0.3 to 6                            | V    |

| Output Voltage                                | V <sub>OUT</sub>   | -0.3 to V <sub>IN</sub> +0.3, max. 6 | V    |

| Chip Enable Input                             | V <sub>CE</sub>    | -0.3 to 6                            | V    |

| Power Good Voltage                            | $V_{PG}$           | -0.3 to 6                            | V    |

| Power Good Current                            | l <sub>PG</sub>    | 30                                   | mA   |

| Output Short Circuit Duration                 | tsc                | unlimited                            | S    |

| Maximum Junction Temperature                  | TJ                 | 150                                  | °C   |

| Storage Temperature                           | T <sub>STG</sub>   | -55 to 150                           | °C   |

| ESD Capability, Human Body Model (Note 2)     | ESD <sub>HBM</sub> | 2000                                 | V    |

| ESD Capability, Charged Device Model (Note 2) | ESD <sub>CDM</sub> | 1000                                 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Charged Device Model tested per EIA/JESD22-C101, Field Induced Charge Model

#### THERMAL CHARACTERISTICS

| Rating                                                 | Symbol    | Value | Unit |

|--------------------------------------------------------|-----------|-------|------|

| <b>_</b>                                               | Symbol    | value | Onit |

| THERMAL CHARACTERISTICS, TSOP-5 PACKAGE                |           |       | 1    |

| Thermal Resistance, Junction-to-Ambient (Note 3)       | RθJA      | 158   | °C/W |

| Thermal Resistance, Junction-to-Case (top)             | RθJC(top) | 155   | °C/W |

| Thermal Resistance, Junction-to-Case (bottom) (Note 4) | RθJC(bot) | 102   | °C/W |

| Thermal Resistance, Junction-to-Board                  | Rејв      | 197   | °C/W |

| Characterization Parameter, Junction-to-Top            | Ψлт       | 40    | °C/W |

| Characterization Parameter, Junction-to-Board          | ΨЈВ       | 82    | °C/W |

| THERMAL CHARACTERISTICS, WDFNW6-2X2, 0.65 PITCH PACKAG | iΕ        |       |      |

| Thermal Resistance, Junction-to-Ambient (Note 3)       | RθJA      | 51    | °C/W |

| Thermal Resistance, Junction-to-Case (top)             | RθJC(top) | 142   | °C/W |

| Thermal Resistance, Junction-to-Case (bottom) (Note 4) | RθJC(bot) | 2.0   | °C/W |

| Thermal Resistance, Junction-to-Board                  | Rejb      | 117   | °C/W |

| Characterization Parameter, Junction-to-Top            | Ψлт       | 1.9   | °C/W |

| Characterization Parameter, Junction-to-Board          | ΨЈВ       | 7.7   | °C/W |

| THERMAL CHARACTERISTICS, DFNW8-3X3, 0.65 PITCH PACKAGE |           |       |      |

| Thermal Resistance, Junction-to-Ambient (Note 3)       | RθJA      | 50    | °C/W |

| Thermal Resistance, Junction-to-Case (top)             | RθJC(top) | 142   | °C/W |

| Thermal Resistance, Junction-to-Case (bottom) (Note 4) | RθJC(bot) | 7.9   | °C/W |

| Thermal Resistance, Junction-to-Board                  | Rejb      | 125   | °C/W |

| Characterization Parameter, Junction-to-Top            | ΨЈТ       | 2.0   | °C/W |

| Characterization Parameter, Junction-to-Board          | ΨЈВ       | 7.5   | °C/W |

|                                                        |           |       |      |

<sup>3.</sup> The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a high-K board, following the

JEDEC51.7 guidelines with assumptions as above, in an environment described in JESD51–2a.

4. The junction—to—case (bottom) thermal resistance is obtained by simulating a cold plate test on the IC exposed pad. Test description can be found in the ANSI SEMI standard G30–88.

# **ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}C \leq T_{J} \leq 150^{\circ}C; \ V_{IN} = V_{OUT(NOM)} + 0.5 \ V; \ I_{OUT} = 1 \ mA, \ C_{IN} = C_{OUT} = 1 \ \mu F, \ V_{EN} = V_{IN}, \ unless otherwise noted.$  Typical values are at  $T_{J} = +25^{\circ}C$  (Note 5))

| Parameter                                                       | Test Co                                                                                                       | onditions                                                  | Symbol              | Min   | Тур  | Max   | Unit |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|-------|------|-------|------|

| Operating Input Voltage                                         |                                                                                                               |                                                            | V <sub>IN</sub>     | 1.6   |      | 5.5   | V    |

| Output Voltage Accuracy                                         | $V_{IN} = V_{OUT(NOM)} + 0.5 \text{ V to } 5.5 \text{ V},$<br>$0.1 \text{ mA} \le I_{OUT} \le 300 \text{ mA}$ |                                                            | V <sub>OUT</sub>    | -2    |      | +2    | %    |

| Reference Voltage (Adjustable Ver.<br>ADJ pin connected to OUT) | ***                                                                                                           | 3 V to 5.5 V,<br><sub>OUT</sub> ≤ 300 mA                   | $V_{ADJ}$           | 1.176 | 1.2  | 1.224 | V    |

| Line Regulation                                                 | V <sub>OUT(NOM)</sub> + 0.                                                                                    | $5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$   | Line <sub>Reg</sub> |       | 0.5  |       | mV/V |

| Load Regulation                                                 | I <sub>OUT</sub> = 1 m                                                                                        | A to 300 mA                                                | Load <sub>Reg</sub> |       | 2    |       | mV   |

| Dropout Voltage (Note 6) TSOP-5, WDFNW6                         | I <sub>OUT</sub> = 300 mA                                                                                     | V <sub>OUT(NOM)</sub> = 1.5 V                              | V <sub>DO</sub>     |       | 170  | 295   | mV   |

| 130F-5, WDFINWO                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 1.8 V                              | 1                   |       | 155  | 255   |      |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 2.5 V                              | 1                   |       | 125  | 200   |      |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 2.8 V                              | 1                   |       | 115  | 185   |      |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 3.0 V                              |                     |       | 113  | 177   |      |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 3.3 V                              | 1                   |       | 110  | 170   |      |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 5.0 V                              | 1                   |       | 95   | 135   | 1    |

| Dropout Voltage (Note 6)                                        | I <sub>OUT</sub> = 300 mA                                                                                     | V <sub>OUT(NOM)</sub> = 1.5 V                              | V <sub>DO</sub>     |       | 180  | 315   | mV   |

| DFNW8                                                           |                                                                                                               | V <sub>OUT(NOM)</sub> = 1.8 V                              | 1                   |       | 165  | 275   | 1    |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 2.5 V                              |                     |       | 140  | 220   | 1    |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 2.8 V                              |                     |       | 130  | 205   | 1    |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 3.0 V                              |                     |       | 127  | 197   | 1    |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 3.3 V                              | 1                   |       | 125  | 190   | 1    |

|                                                                 |                                                                                                               | V <sub>OUT(NOM)</sub> = 5.0 V                              | 1                   |       | 112  | 170   | 1    |

| Output Current Limit                                            | V <sub>OUT</sub> = 90                                                                                         | % V <sub>OUT(NOM)</sub>                                    | I <sub>CL</sub>     | 350   | 560  |       | mA   |

| Short Circuit Current                                           | V <sub>OU</sub>                                                                                               | T = 0 V                                                    | I <sub>SC</sub>     |       | 580  |       |      |

| Quiescent Current                                               | I <sub>OUT</sub>                                                                                              | = 0 mA                                                     | IQ                  |       | 30   | 40    | μΑ   |

| Shutdown Current                                                | V <sub>EN</sub> ≤                                                                                             | 0.25 V                                                     | I <sub>DIS</sub>    |       | 0.01 | 1.5   | μΑ   |

| EN Pin Threshold Voltage                                        | EN Input Voltage "H"                                                                                          |                                                            | V <sub>ENH</sub>    | 0.7   |      |       | V    |

|                                                                 | EN Input                                                                                                      | Voltage "L"                                                | V <sub>ENL</sub>    |       |      | 0.25  | 1    |

| EN Pull Down Current                                            | V <sub>EN</sub> = 5.5 V                                                                                       |                                                            | I <sub>EN</sub>     |       | 0.2  | 0.6   | μΑ   |

| Power Good Threshold Voltage                                    | Output Voltage Raising                                                                                        |                                                            | V <sub>PGUP</sub>   |       | 95   |       | %    |

|                                                                 | Output Vo                                                                                                     | oltage Falling                                             | V <sub>PGDW</sub>   |       | 90   |       | 1    |

| Power Good Output Voltage Low                                   | IPG = 5 mA, Open drain                                                                                        |                                                            | V <sub>PGLO</sub>   |       |      | 0.3   | V    |

| Turn-On Time (Note 7)                                           | C <sub>OUT</sub> = 1 μF, Fro<br>to V <sub>OUT</sub> = 99                                                      | m assertion of V <sub>EN</sub><br>5% V <sub>OUT(NOM)</sub> |                     |       | 120  |       | μS   |

# **ELECTRICAL CHARACTERISTICS** (continued)

$(-40^{\circ}C \leq T_{J} \leq 150^{\circ}C; \ V_{IN} = V_{OUT(NOM)} + 0.5 \ V; \ I_{OUT} = 1 \ mA, \ C_{IN} = C_{OUT} = 1 \ \mu F, \ V_{EN} = V_{IN}, \ unless \ otherwise \ noted.$  Typical values are at  $T_{J} = +25^{\circ}C \ (Note 5))$

| Parameter                             | Test Conditions                                            |               | Symbol            | Min | Тур      | Max | Unit                 |

|---------------------------------------|------------------------------------------------------------|---------------|-------------------|-----|----------|-----|----------------------|

| Power Supply Rejection Ratio (Note 7) | V <sub>OUT(NOM)</sub> = 3.3 V,<br>I <sub>OUT</sub> = 10 mA | f = 100 Hz    | P <sub>SRR</sub>  |     | 83       |     | dB                   |

|                                       | I <sub>ΟUT</sub> = 10 mA                                   | f = 1 kHz     |                   |     | 85       |     |                      |

|                                       |                                                            | f = 10 kHz    | 7                 |     | 80<br>61 |     |                      |

|                                       |                                                            | f = 100 kHz   |                   |     |          |     |                      |

| Output Voltage Noise (Fixed Ver.)     | f = 10 Hz to 100 kHz                                       | IOUT = 10 mA  | V <sub>N</sub>    |     | 9        |     | $\mu V_{\text{RMS}}$ |

| Thermal Shutdown Threshold (Note 7)   | Temperature rising                                         |               | T <sub>SDH</sub>  |     | 165      |     | °C                   |

| ,                                     | Temperature hysteresis                                     |               | T <sub>HYST</sub> |     | 15       |     | °C                   |

| Active output discharge resistance    | V <sub>EN</sub> < 0.25 V, \                                | ersion A only | R <sub>DIS</sub>  |     | 260      |     | Ω                    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 5. Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at  $T_J = T_A = 25^{\circ}C$ .

- 6. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible. Dropout voltage is characterized when V<sub>OUT</sub> falls 3% below V<sub>OUT(NOM)</sub>.

- 7. Guaranteed by design and characterization.

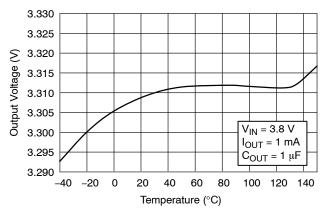

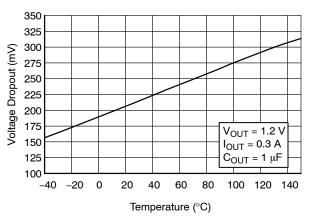

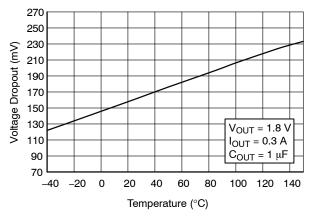

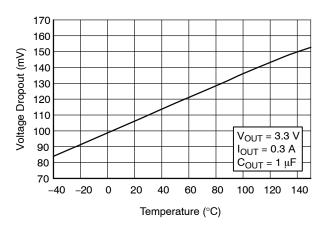

### **TYPICAL CHARACTERISTICS**

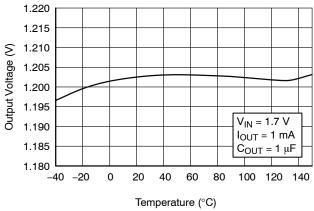

Figure 2. Output Voltage vs. Temperature –  $V_{OUT} = 1.2 \text{ V}$

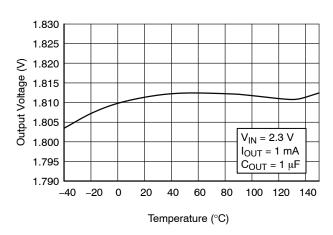

Figure 3. Output Voltage vs. Temperature –  $V_{OUT} = 1.8 \text{ V}$

Figure 4. Output Voltage vs. Temperature –  $V_{OUT} = 3.3 \text{ V}$

Figure 5. Dropout Voltage vs. Temperature –  $V_{OUT} = 1.2 \text{ V}$

Figure 6. Dropout Voltage vs. Temperature –  $V_{OUT} = 1.8 \text{ V}$

Figure 7. Dropout Voltage vs. Temperature –  $V_{OUT} = 3.3 \text{ V}$

# TYPICAL CHARACTERISTICS (continued)

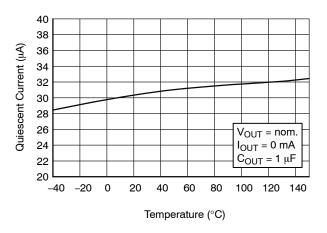

Figure 8. Quiescent Current va Temperature

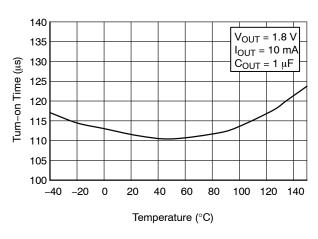

Figure 9. Turn-on Time vs. Temperature

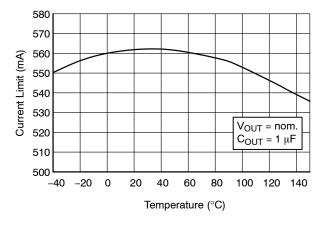

Figure 10. Current Limit vs. Temperature

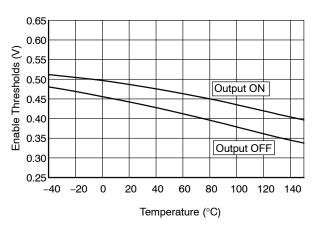

Figure 11. Enable Thresholds vs Temperature

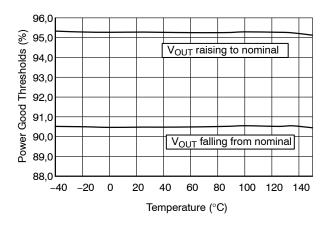

Figure 12. Power Good Threshold vs. Temperature

Figure 13. Active Discharge Resistance vs. Temperature

#### TYPICAL CHARACTERISTICS (continued)

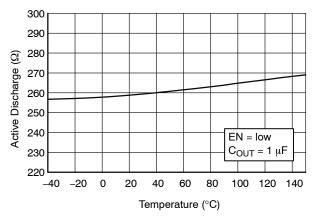

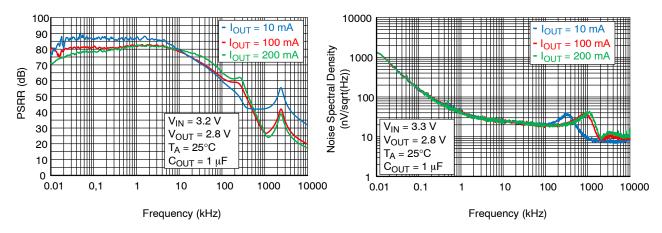

Figure 14. Power Supply Rejection Ration for  $V_{OUT} = 2.8 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$

Figure 15. Output Voltage Noise Spectral Density for  $V_{OUT}$  = 2.8 V,  $C_{OUT}$  = 1  $\mu F$

#### APPLICATIONS INFORMATION

The NCV8164 is the member of new family of high output current and low dropout regulators which delivers low quiescent and ground current consumption, good noise and power supply ripple rejection ratio performance. The NCV8164 incorporates EN pin and power good output for simple controlling by MCU or logic. Standard features include current limiting, soft—start feature and thermal protection.

## Input Decoupling (CIN)

It is recommended to connect at least 1  $\mu$ F ceramic X5R or X7R capacitor between IN and GND pin of the device. This capacitor will provide a low impedance path for any unwanted AC signals or noise superimposed onto constant input voltage. The good input capacitor will limit the influence of input trace inductances and source resistance during sudden load current changes. Higher capacitance and lower ESR capacitors will improve the overall line transient response.

# Output Decoupling (COUT)

The NCV8164 does not require a minimum Equivalent Series Resistance (ESR) for the output capacitor. The device is designed to be stable with standard ceramics capacitors with values of 1  $\mu$ F or greater. The X5R and X7R types have the lowest capacitance variations over temperature thus they are recommended.

# **Power Good Output Connection**

The NCV8164 include Power Good functionality for better interfacing to MCU system. Power Good output is open collector type, capable to sink up to 10 mA. Recommended operating current is between 10  $\mu A$  and

1 mA to obtain low saturation voltage. External pull-up resistor can be connected to any voltage up to 5.5 V (please see Absolute Maximum Ratings table above).

#### **Power Dissipation and Heat Sinking**

The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part. For reliable operation junction temperature should be limited to +125°C, however device is capable to work up to junction temperature +150°C. The maximum power dissipation the NCV8164 can handle is given by:

$$P_{D(MAX)} = \frac{\left[T_{J(MAX)} - T_{A}\right]}{R_{\theta JA}}$$

(eq. 1)

The power dissipated by the NCV8164 for given application conditions can be calculated from the following equations:

$$P_D \approx V_{IN}(I_{GND}(I_{OUT})) + I_{OUT}(V_{IN} - V_{OUT})$$

(eq. 2)

or

$$V_{\text{IN(MAX)}} \approx \frac{P_{\text{D(MAX)}} + \left(V_{\text{OUT}} \times I_{\text{OUT}}\right)}{I_{\text{OUT}} + I_{\text{GND}}}$$

(eq. 3)

#### Hints

VIN and GND printed circuit board traces should be as wide as possible. When the impedance of these traces is high, there is a chance to pick up noise or cause the regulator to malfunction. Place external components, especially the output capacitor, as close as possible to the NCV8164, and make traces as short as possible.

#### **Adjustable Version**

Not only adjustable version, but also any fixed version can be used to create adjustable voltage, where original fixed voltage becomes reference voltage for resistor divider and feedback loop. Output voltage can be equal or higher than original fixed option, while possible range is from 1.2 V up to 5.0 V. Figure 16 shows how to add external resistors to increase output voltage above fixed value.

Output voltage is then given by equation

$$V_{OUT} = V_{FIX} \times (1 + R1/R2)$$

(eq. 4)

where  $V_{FIX}$  is voltage of original fixed version (from 1.2 V up to 5.0 V) or adjustable version (1.2 V). Do not operate the device at output voltage about 5.2 V, as device can be damaged.

In order to avoid influence of current flowing into SNS pin to output voltage accuracy (SNS current varies with voltage option and temperature, typical value is 300 nA) it is recommended to use values of R1 and R2 below 500 k $\Omega$ .

Figure 16. Adjustable Variant Application

Please note that output noise is amplified by  $V_{OUT}/V_{FIX}$  ratio. For example, if original 1.2 V fixed variant is used to create 3.6 V output voltage, output noise is increased 3.6 / 1.2 = 3 times and real value will be 3  $\times$  9  $\mu$ Vrms = 27  $\mu$ Vrms. For noise sensitive applications it is

recommended to use as high fixed variant as possible – for example in case above it is better to use 3.3 V fixed variant to create 3.6 V output voltage, as output noise will be amplified only  $3.6 / 3.3 = 1.09 \times (9.8 \,\mu\text{Vrms})$ .

# **ORDERING INFORMATION**

| Device part no.   | Voltage Option | Marking | Option                          | Package                 | Shipping †           |

|-------------------|----------------|---------|---------------------------------|-------------------------|----------------------|

| NCV8164ASNADJT1G  | ADJ            | M2      | With Active Output<br>Discharge |                         |                      |

| NCV8164ASN120T1G  | 1.2 V          | MA      | With Active Output<br>Discharge |                         |                      |

| NCV8164ASN150T1G  | 1.5 V          | MN      | With Active Output<br>Discharge |                         |                      |

| NCV8164ASN180T1G  | 1.8 V          | MJ      | With Active Output<br>Discharge | TSOP-5                  | 0000 / Table 0 David |

| NCV8164ASN250T1G  | 2.5 V          | MP      | With Active Output<br>Discharge | (Pb-Free)               | 3000 / Tape & Reel   |

| NCV8164ASN280T1G  | 2.8 V          | MK      | With Active Output<br>Discharge |                         |                      |

| NCV8164ASN300T1G  | 3.0 V          | MQ      | With Active Output<br>Discharge |                         |                      |

| NCV8164ASN330T1G  | 3.3 V          | ML      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMTWADJTAG | ADJ            | L3      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMTW110TAG | 1.1 V          | LC      | With Active Output<br>Discharge | WDFNW6<br>(WF, Pb-Free) | 3000 / Tape & Reel   |

| NCV8164AMTW120TAG | 1.2 V          | LA      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMTW180TAG | 1.8 V          | LJ      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMTW280TAG | 2.8 V          | LK      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMTW290TAG | 2.9 V          | LH      | With Active Output<br>Discharge |                         |                      |

| NCV8164AMLADJTCG  | ADJ            | K2      | With Active Output<br>Discharge |                         |                      |

| NCV8164AML120TCG  | 1.2 V          | KA      | With Active Output<br>Discharge |                         |                      |

| NCV8164AML150TCG  | 1.5 V          | KN      | With Active Output<br>Discharge |                         |                      |

| NCV8164AML180TCG  | 1.8 V          | KJ      | With Active Output<br>Discharge | DFNW8<br>(WF, Pb-Free)  |                      |

| NCV8164AML250TCG  | 2.5 V          | KP      | With Active Output<br>Discharge |                         | 3000 / Tape & Reel   |

| NCV8164AML280TCG  | 2.8 V          | KK      | With Active Output<br>Discharge |                         |                      |

| NCV8164AML300TCG  | 3.0 V          | KQ      | With Active Output<br>Discharge |                         |                      |

| NCV8164AML330TCG  | 3.3 V          | KL      | With Active Output<br>Discharge |                         |                      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

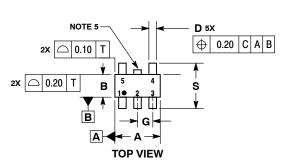

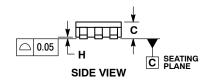

TSOP-5 **CASE 483 ISSUE N**

**DATE 12 AUG 2020**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME

- CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH

THICKNESS. MINIMUM LEAD THICKNESS IS THE

MINIMUM THICKNESS OF BASE MATERIAL.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A. OPTIONAL CONSTRUCTION: AN ADDITIONAL

- TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 2.85        | 3.15 |  |  |

| В   | 1.35        | 1.65 |  |  |

| C   | 0.90        | 1.10 |  |  |

| D   | 0.25        | 0.50 |  |  |

| G   | 0.95        | BSC  |  |  |

| Н   | 0.01        | 0.10 |  |  |

| J   | 0.10        | 0.26 |  |  |

| K   | 0.20        | 0.60 |  |  |

| М   | 0 °         | 10 ° |  |  |

| S   | 2.50        | 3.00 |  |  |

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code XXX = Specific Device Code

= Assembly Location = Date Code

= Year = Pb-Free Package

= Work Week W

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98ARB18753C | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TSOP-5      |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

| DOCUMENT NUMBER: | 98AON17792G      | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DFNW8 3x3, 0.65P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

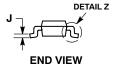

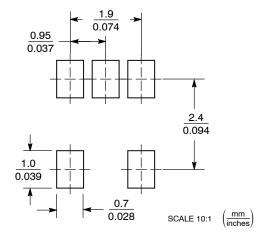

#### **DATE 15 JUN 2018**

#### NDTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION 6 APPLIES TO PLATED TERMINALS AND IS MEASURED BETWEEN 0.15 AND 0.30MM FROM THE TERMINAL TIP.

- 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- 5. THIS DEVICE CONTAINS WETTABLE FLANK

DESIGN FEATURES TO AID IN FILLET

FORMATION ON THE LEADS DURING MOUNTING.

|     | MILLIMETERS |          |      |  |  |

|-----|-------------|----------|------|--|--|

| DIM | MIN.        | N□M.     | MAX. |  |  |

| Α   | 0.70        | 0.75     | 0.80 |  |  |

| A1  | -           | -        | 0.05 |  |  |

| A3  | _           | 0.20 REF | -    |  |  |

| Α4  | 0.10        | -        |      |  |  |

| b   | 0.25        | 0.30     | 0.35 |  |  |

| D   | 1.90        | 2.00     | 2.10 |  |  |

| D2  | 1.50        | 1.60     | 1.70 |  |  |

| Е   | 1.90        | 2.00     | 2.10 |  |  |

| E2  | 0.80        | 0.90     | 1.00 |  |  |

| ٩   | 0.65 BSC    |          |      |  |  |

| K   | 0.25 REF    |          |      |  |  |

| L   | 0.25        | 0.30     | 0.35 |  |  |

| L3  | 0.05 REF    |          |      |  |  |

# GENERIC MARKING DIAGRAM\*

M = Month Code= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " •", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON79327G       | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | WDFNW6 2x2, 0.65P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative