# **MOSFET** - N-Channel, POWERTRENCH®

**30 V, 58 A, 9 m**Ω

## FDD8880, FDD8880-G

#### **General Description**

This N-Channel MOSFET has been designed specifically to improve the overall efficiency of DC/DC converters using either synchronous or conventional switching PWM controllers. It has been optimized for low gate charge, low r<sub>DS(ON)</sub> and fast switching speed.

#### **Features**

- $r_{DS(ON)} = 9 \text{ m}\Omega$ ,  $V_{GS} = 10 \text{ V}$ ,  $I_D = 35 \text{ A}$

- $r_{DS(ON)} = 12 \text{ m}\Omega$ ,  $V_{GS} = 4.5 \text{ V}$ ,  $I_D = 35 \text{ A}$

- High Performance Trench Technology for Extremely Low r<sub>DS(ON)</sub>

- Low Gate Charge

- High Power and Current Handling Capability

- These Devices are Pb-Free and are RoHS Compliant

#### **Applications**

• DC/DC Converters

#### MOSFET MAXIMUM RATINGS (T<sub>C</sub> = 25°C unless otherwise noted)

| Symbol            |                                                                                   | Parameter                                                                                     | Ratings    | Unit  |

|-------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------|-------|

| V <sub>DSS</sub>  | Drain to Source Voltage                                                           |                                                                                               | 30         | V     |

| V <sub>GS</sub>   | Gate to Source Voltage                                                            |                                                                                               | ±20        | V     |

| I <sub>D</sub>    | Drain Continuous (T <sub>A</sub> = 25°C, Current V <sub>GS</sub> = 10 V) (Note 1) |                                                                                               | 58         | Α     |

|                   |                                                                                   | Continuous ( $T_A = 25$ °C, $V_{GS} = 4.5$ V) (Note 1)                                        | 51         | Α     |

|                   |                                                                                   | Continuous ( $T_{amb}$ = 25°C,<br>$V_{GS}$ = 10 V, with $R_{\theta JA}$ = 52°C/W)<br>(Note 1) | 13         | Α     |

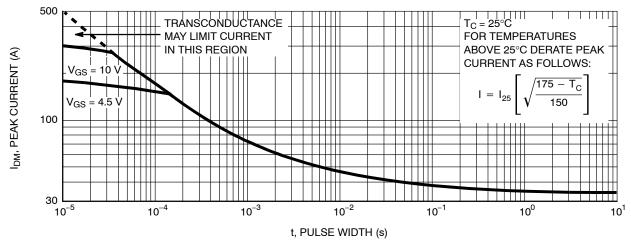

|                   |                                                                                   | Pulsed                                                                                        | Figure 4   | Α     |

| E <sub>AS</sub>   | Single Pulse Avalanche Energy (Note 2)                                            |                                                                                               | 53         | mJ    |

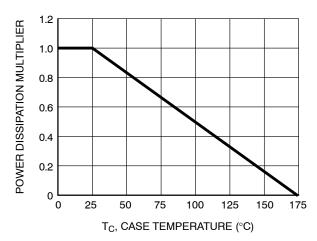

| P <sub>D</sub>    | Power Dissipation                                                                 |                                                                                               | 55         | W     |

|                   | Derate above 25°C                                                                 |                                                                                               | 0.37       | mW/°C |

| $T_J$ , $T_{STG}$ | Operating and Storage Temperature                                                 |                                                                                               | -55 to 175 | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Package current limitation is 35A.

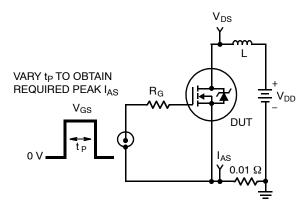

- 2. Starting  $T_J = 25^{\circ}C$ , L = 0.14 mH,  $I_{AS} = 28$  A,  $V_{DD} = 27$  V,  $V_{GS} = 10$  V.

| V <sub>DSS</sub> MAX | r <sub>DS(ON)</sub> MAX | I <sub>D</sub> MAX |

|----------------------|-------------------------|--------------------|

| 30 V                 | 9 mΩ @ 10 V             | 58 A               |

|                      | 12 m $\Omega$ @ 4.5 V   |                    |

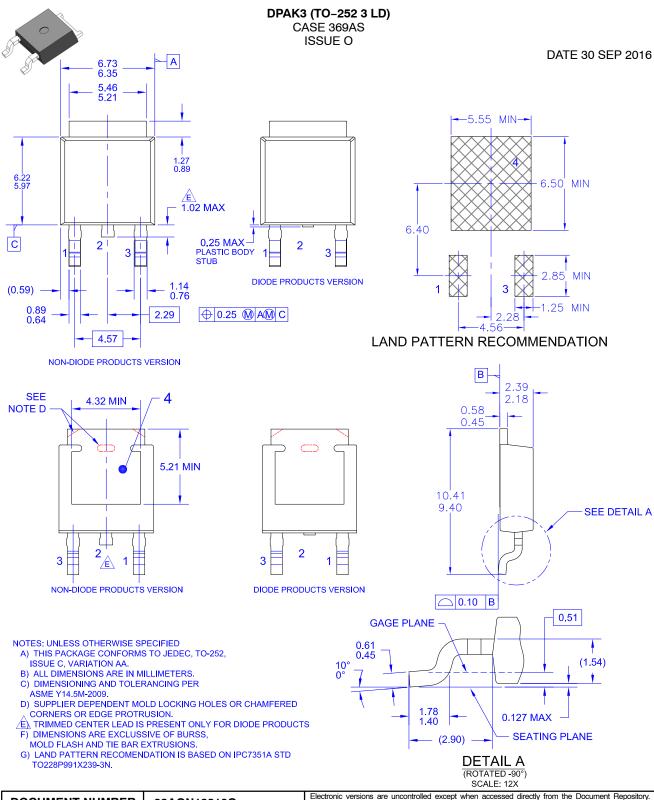

DPAK3 (TO-252 3 LD) CASE 369AS

#### **MARKING DIAGRAM**

\$Y = **onsemi** Logo

&Z = Assembly Plant Code &3 = 3-Digit Date Code Format

&K = 2-Digits Lot Run Traceability Code

FDD8880 = Device Code

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 12 of this data sheet.

## THERMAL CHARACTERISTICS

| Symbol          | Parameter                                                                         | Ratings | Unit |

|-----------------|-----------------------------------------------------------------------------------|---------|------|

| $R_{	heta JC}$  | Thermal Resistance, Junction to Case TO-252                                       | 2.73    | °C/W |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient TO-252                                    | 100     | °C/W |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient TO-252, 1 in <sup>2</sup> Copper Pad Area | 52      | °C/W |

## **ELECTRICAL CHARACTERISTICS** (T<sub>C</sub> = 25°C unless otherwise noted)

| Symbol              | Parameter                                  | Test Conditions                                                                                             | Min | Тур   | Max   | Unit |

|---------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|-------|------|

| OFF CHAR            | ACTERISTICS                                | •                                                                                                           | •   | •     |       |      |

| B <sub>VDSS</sub>   | Drain to Source Breakdown Voltage          | $I_D = 250 \mu A, V_{GS} = 0 V$                                                                             | 30  | _     | -     | V    |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current            | V <sub>DS</sub> = 24 V, V <sub>GS</sub> = 0 V                                                               | -   | _     | 1     | μΑ   |

|                     |                                            | V <sub>DS</sub> = 24 V, V <sub>GS</sub> = 0 V, T <sub>C</sub> = 150°C                                       | -   | _     | 250   |      |

| I <sub>GSS</sub>    | Gate to Source Leakage Current             | V <sub>GS</sub> = ±20 V                                                                                     | -   | _     | ±100  | nA   |

| ON CHARA            | CTERISTICS                                 | •                                                                                                           | •   | •     |       |      |

| V <sub>GS(TH)</sub> | Gate to Source Threshold Voltage           | $V_{GS} = V_{DS}$ , $I_D = 250 \mu A$                                                                       | 1.2 | _     | 2.5   | V    |

| r <sub>DS(ON)</sub> | Drain to Source On Resistance              | I <sub>D</sub> = 35 A, V <sub>GS</sub> = 10 V                                                               | -   | 0.007 | 0.009 | Ω    |

|                     |                                            | I <sub>D</sub> = 35 A, V <sub>GS</sub> = 4.5 V                                                              | -   | 0.009 | 0.012 | 1    |

|                     |                                            | I <sub>D</sub> = 35 A, V <sub>GS</sub> = 10 V, T <sub>J</sub> = 175°C                                       | -   | 0.013 | 0.015 |      |

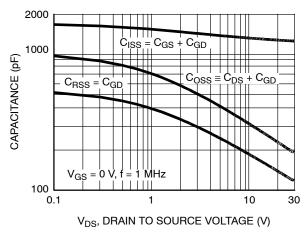

| DYNAMIC (           | CHARACTERISTICS                            | •                                                                                                           | •   | •     |       |      |

| C <sub>ISS</sub>    | Input Capacitance                          | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V, f = 1 MHz                                                    | -   | 1260  | _     | pF   |

| C <sub>OSS</sub>    | Output Capacitance                         |                                                                                                             | -   | 260   | -     | pF   |

| C <sub>RSS</sub>    | Reverse Transfer Capacitance               |                                                                                                             | -   | 150   | _     | pF   |

| $R_{G}$             | Gate Resistance                            | V <sub>GS</sub> = 0.5 V, f = 1 MHz                                                                          | -   | 2.3   | _     | Ω    |

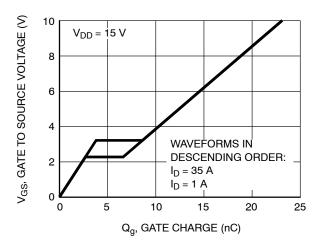

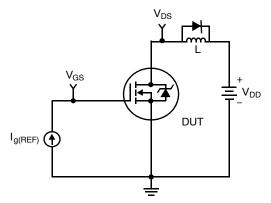

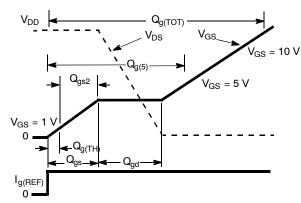

| $Q_{g(TOT)}$        | Total Gate Charge at 10 V                  | $V_{GS} = 0 \text{ V to } 10 \text{ V}, V_{DD} = 15 \text{ V}, \\ I_D = 35 \text{ A}, I_g = 1.0 \text{ mA}$ | -   | 23    | 31    | nC   |

| Q <sub>g(5)</sub>   | Total Gate Charge at 5 V                   | $V_{GS} = 0 \text{ V to 5 V}, V_{DD} = 15 \text{ V},$<br>$I_D = 35 \text{ A}, I_g = 1.0 \text{ mA}$         | -   | 13    | 17    | nC   |

| $Q_{g(TH)}$         | Threshold Gate Charge                      | $V_{GS} = 0 \text{ V to 1 V}, V_{DD} = 15 \text{ V},$<br>$I_D = 35 \text{ A}, I_g = 1.0 \text{ mA}$         | -   | 1.3   | 1.7   | nC   |

| Q <sub>gs</sub>     | Gate to Source Gate Charge                 | V <sub>DD</sub> = 15 V, I <sub>D</sub> = 35 A, I <sub>g</sub> = 1.0 mA                                      | -   | 3.8   | _     | nC   |

| Q <sub>gs2</sub>    | Gate Charge Threshold to Plateau           |                                                                                                             | -   | 2.5   | -     | nC   |

| $Q_{gd}$            | Gate to Drain "Miller" Charge              |                                                                                                             | -   | 5.0   | -     | nC   |

| SWITCHING           | G CHARACTERISTICS (V <sub>GS</sub> = 10 V) |                                                                                                             |     |       |       |      |

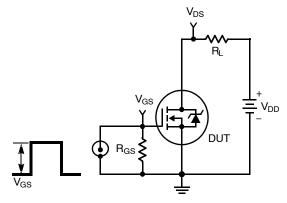

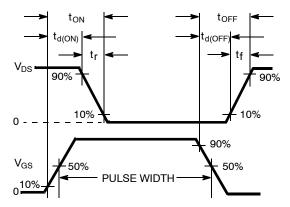

| t <sub>ON</sub>     | Turn-On Time                               | $V_{DD} = 15 \text{ V}, I_D = 35 \text{ A}, V_{GS} = 10 \text{ V},$                                         | -   | -     | 147   | ns   |

| t <sub>d(ON)</sub>  | Turn-On Delay Time                         | $R_{GS} = 10 \Omega$                                                                                        | -   | 8     | _     | ns   |

| t <sub>r</sub>      | Rise Time                                  |                                                                                                             | -   | 91    | _     | ns   |

| t <sub>d(OFF)</sub> | Turn-Off Delay Time                        |                                                                                                             | -   | 38    | _     | ns   |

| t <sub>f</sub>      | Fall Time                                  |                                                                                                             | -   | 32    | _     | ns   |

| t <sub>OFF</sub>    | Turn-Off Time                              |                                                                                                             | -   | _     | 108   | ns   |

| DRAIN-SO            | URCE DIODE CHARACTERISTICS                 |                                                                                                             | -   |       |       |      |

| V <sub>SD</sub>     | Source to Drain Diode Voltage              | I <sub>SD</sub> = 35 A                                                                                      | -   | _     | 1.25  | V    |

|                     |                                            | I <sub>SD</sub> = 15 A                                                                                      |     |       | 1.0   | V    |

| t <sub>rr</sub>     | Reverse Recovery Time                      | I <sub>SD</sub> = 35 A, dI <sub>SD</sub> /dt = 100 A/μs                                                     | -   | _     | 27    | ns   |

| Q <sub>RR</sub>     | Reverse Recovered Charge                   | I <sub>SD</sub> = 35 A, dI <sub>SD</sub> /dt = 100 A/μs                                                     | _   | _     | 14    | nC   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **TYPICAL CHARACTERISTICS**

$(T_J = 25^{\circ}C \text{ unless otherwise noted})$

60 CURRENT LIMITED BY PACKAGE 50 ID, DRAIN CURRENT (A) 40  $V_{GS}' = 10 V$ 30  $V_{GS}$ = 4.5 ∖ 20 10 0 L 25 50 75 100 125 150 175 T<sub>C</sub>, CASE TEMPERATURE (°C)

Figure 1. Normalized Power Dissipation vs.

Case Temperature

Figure 2. Maximum Continuous Drain Current vs.

Case Temperature

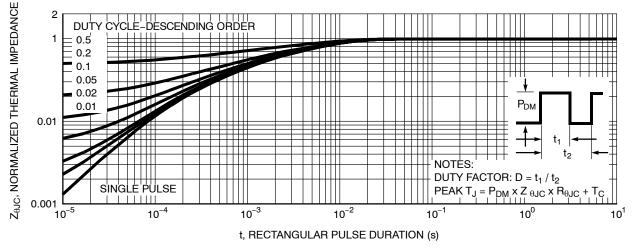

Figure 3. Normalized Maximum Transient Thermal Impedance

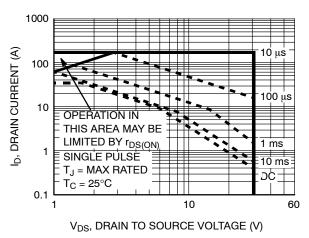

Figure 4. Peak Current Capability

#### **TYPICAL CHARACTERISTICS**

$(T_J = 25^{\circ}C \text{ unless otherwise noted})$  (continued)

Figure 5. Forward Bis Safe Operating Area

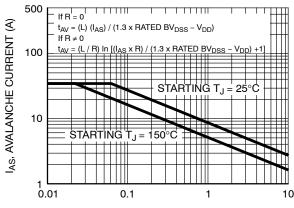

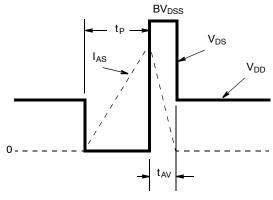

t<sub>AV</sub>, TIME IN AVALANCHE (ms)

NOTE: Refer to **onsemi** Application Notes AN-7514 and AN-7515

Figure 6. Unclamped Inductive Switching Capability

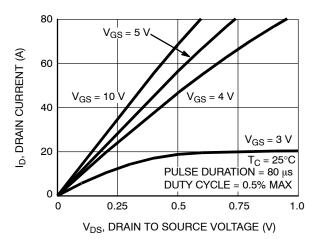

Figure 7. Transfer Characteristics

Figure 8. Saturation Characteristics

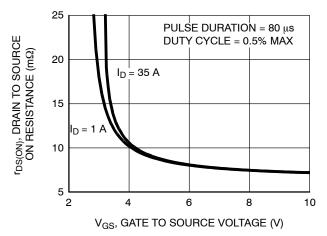

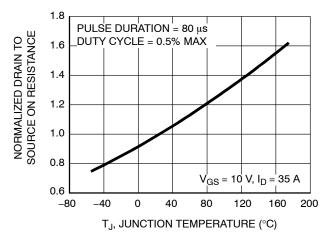

Figure 9. Drain to Source On Resistance vs.

Gate Voltage and Drain Current

Figure 10. Normalized Drain to Source On Resistance vs. Junction Temperature

#### **TYPICAL CHARACTERISTICS**

(T<sub>J</sub> = 25°C unless otherwise noted) (continued)

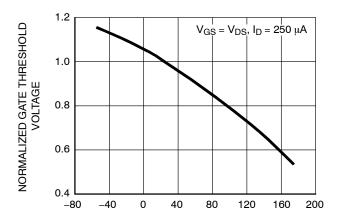

Figure 11. Normalized Gate Threshold Voltage vs.

Junction Temperature

Figure 13. Capacitance vs. Drain to Source Voltage

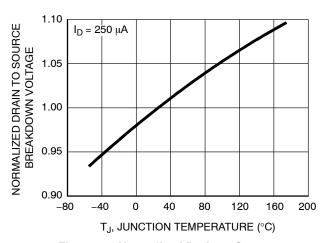

Figure 12. Normalized Drain to Source Breakdown Voltage vs. Junction Temperature

Figure 14. Gate Charge Waveforms for Constant Gate Current

## **TEST CIRCUITS AND WAVEFORMS**

Figure 15. Unclamped Energy Test Circuit

Figure 16. Unclamped Energy Waveforms

Figure 17. Gate Charge Test Circuit

Figure 18. Gate Charge Waveforms

Figure 19. Switching Time Test Circuit

Figure 20. Switching Time Waveforms

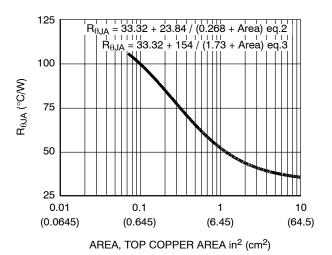

#### THERMAL RESISTANCE VS. MOUNTING PAD AREA

The maximum rated junction temperature,  $T_{JM}$ , and the thermal resistance of the heat dissipating path determines the maximum allowable device power dissipation,  $P_{DM}$ , in an application. Therefore the application's ambient temperature,  $T_A$  (°C), and thermal resistance  $R_{\theta JA}$  (°C/W) must be reviewed to ensure that  $T_{JM}$  is never exceeded. Equation 1 mathematically represents the relationship and serves as the basis for establishing the rating of the part.

$$P_{DM} = \frac{(T_{JM} - T_A)}{R_{\theta,JA}}$$

(eq. 1)

In using surface mount devices such as the TO-252 package, the environment in which it is applied will have a significant influence on the part's current and maximum power dissipation ratings. Precise determination of  $P_{DM}$  is complex and influenced by many factors:

- Mounting pad area onto which the device is attached and whether there is copper on one side or both sides of the board.

- The number of copper layers and the thickness of the board.

- 3. The use of external heat sinks.

- 4. The use of thermal vias.

- 5. Air flow and board orientation.

- 6. For non steady state applications, the pulse width, the duty cycle and the transient thermal response of the part, the board and the environment they are in.

**onsemi** provides thermal information to assist the designer's preliminary application evaluation. Figure 21 defines the  $R_{\theta JA}$  for the device as a function of the top copper (component side) area. This is for a horizontally positioned FR–4 board with 1oz copper after 1000 seconds of steady state power with no air flow. This graph provides the necessary information for calculation of the steady state junction temperature or power dissipation. Pulse

applications can be evaluated using the **onsemi** device Spice thermal model or manually utilizing the normalized maximum transient thermal impedance curve.

Thermal resistances corresponding to other copper areas can be obtained from Figure 21 or by calculation using Equation 2 or 3. Equation 2 is used for copper area defined in inches square and Equation 3 is for area in centimeters square. The area, in square inches or square centimeters is the top copper area including the gate and source pads.

$$R_{\theta JA} = 33.32 + \frac{23.84}{(0.268 + Area)}$$

Area in Inches Squared (eq. 2)

$$R_{\theta JA} = 33.32 + \frac{154}{(1.73 + Area)}$$

Area in Inches Squared (eq. 3)

Figure 21. Thermal Resistance vs. Mounting Pad Area

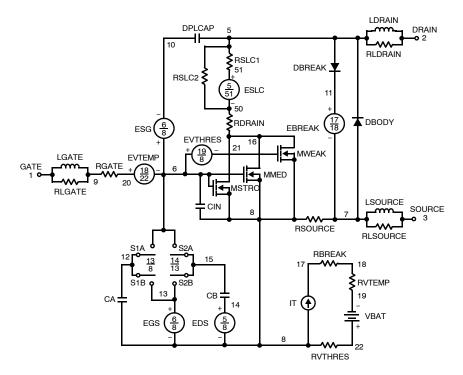

#### **PSPICE ELECTRICAL MODEL**

.SUBCKT FDD8880 2 1 3; rev April 2004 Ca 12 8 9.5e-10 Cb 15 14 9.5e-10 Cin 6 8 1.15e-9 Dbody 7 5 DbodyMOD Dbreak 5 11 DbreakMOD Dplcap 10 5 DplcapMOD Ebreak 11 7 17 18 33.15 Eds 14 8 5 8 1 Egs 13 8 6 8 1 Esg 6 10 6 8 1 Evthres 6 21 19 8 1 Evtemp 20 6 18 22 1 It 8 17 1 Lgate 1 9 5.3e-9 Ldrain 2 5 1.0e-9 Lsource 3 7 1.7e-9 RLgate 1 9 53 RLdrain 2510 RLsource 3 7 17 Mmed 16 6 8 8 MmedMOD Mstro 16 6 8 8 MstroMOD Mweak 16 21 8 8 MweakMOD Rbreak 17 18 RbreakMOD 1 Rdrain 50 16 Rdrain MOD 3.2e-3 Rgate 9 20 2.2 RSLC1 5 51 RSLCMOD 1e-6 RSLC2 5 50 1e3 Rsource 8 7 Rsource MOD 3.2e-3 Rvthres 22 8 RvthresMOD 1 Rvtemp 18 19 RvtempMOD 1 S1a 6 12 13 8 S1AMOD S1b 13 12 13 8 S1BMOD S2a 6 15 14 13 S2AMOD S2b 13 15 14 13 S2BMOD Vbat 22 19 DC 1 ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))\*(PWR(V(5,51)/(1e-6\*170),5))} .MODEL DbodyMOD D (IS=2E-12 IKF=10 N=1.01 RS=3.76e-3 TRS1=8e-4 TRS2=2e-7 + CJO=4.8e-10 M=0.55 TT=1e-17 XTI=2) .MODEL DbreakMOD D (RS=0.2 TRS1=1e-3 TRS2=-8.9e-6) .MODEL DplcapMOD D (CJO=5.5e-10 IS=1e-30 N=10 M=0.45) .MODEL MmedMOD NMOS (VTO=2.0 KP=10 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=2.2)

.MODEL MstroMOD NMOS (VTO=2.5 KP=170 IS=1e-30 N=10 TOX=1 L=1u W=1u)

.MODEL MweakMOD NMOS (VTO=1.69 KP=0.05 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=22 RS=0.1)

```

.MODEL RbreakMOD RES (TC1=8.3e-4 TC2=-8e-7)

.MODEL RdrainMOD RES (TC1=1.8e-3 TC2=8e-6)

.MODEL RSLCMOD RES (TC1=9e-4 TC2=1e-6)

.MODEL RsourceMOD RES (TC1=5e-3 TC2=1e-6)

.MODEL RvthresMOD RES (TC1=-1e-3 TC2=-8.2e-6)

.MODEL RvtempMOD RES (TC1=-2.6e-3 TC2=2e-7)

.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-4 VOFF=-3.5)

.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-3.5 VOFF=-4)

.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-1.3 VOFF=-0.8)

.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-0.8 VOFF=-1.3)

.ENDS

```

NOTE: For further discussion of the PSPICE model, consult **A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options**; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank Wheatley.

Figure 22.

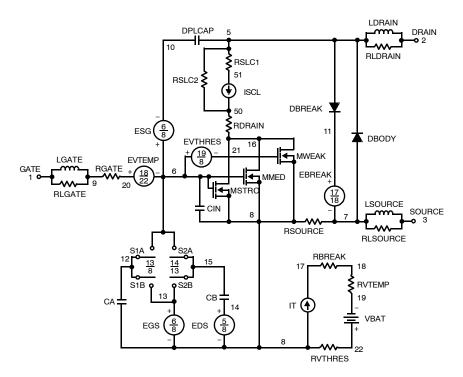

#### SABER ELECTRICAL MODEL

```

rev April 2004

template FDD8880 n2,n1,n3

electrical n2,n1,n3

var i iscl

dp..model\ dbodymod = (isl=2e-12,ikf=10,nl=1.01,rs=3.76e-3,trs1=8e-4,trs2=2e-7,cjo=4.8e-10,m=0.55,tt=1e-17,xti=2)

dp..model dbreakmod = (rs=0.2, trs1=1e-3, trs2=-8.9e-6)

dp..model dplcapmod = (cjo=5.5e-10,isl=10e-30,nl=10,m=0.45)

m..model mmedmod = (type= n,vto=2.0,kp=10,is=1e-30,tox=1)

m..model mstrongmod = (type= n, vto=2.5, kp=170, is=1e-30, tox=1)

m..model mweakmod = (type=_n, vto=1.69, kp=0.05, is=1e-30, tox=1, rs=0.1)

sw vcsp..model s1amod = (ron=1e-5, roff=0.1, von=-4, voff=-3.5)

sw vcsp..model s1bmod = (ron=1e-5, roff=0.1, von=-3.5, voff=-4)

sw vcsp..model s2amod = (ron=1e-5, roff=0.1, von=-1.3, voff=-0.8)

sw vcsp..model s2bmod = (ron=1e-5, roff=0.1, von=-0.8, voff=-1.3)

c.ca n12 n8 = 9.5e-10

c.cb n15 \ n14 = 9.5e-10

c.cin n6 n8 = 1.15e-9

dp.dbody n7 n5 = model = dbodymod

dp.dbreak n5 n11 = model=dbreakmod

dp.dplcap n10 n5 = model=dplcapmod

spe.ebreak n11 n7 n17 n18 = 33.15

spe.eds n14 \ n8 \ n5 \ n8 = 1

spe.egs n13 \ n8 \ n6 \ n8 = 1

spe.esg n6 n10 n6 n8 = 1

spe.evthres n6 n21 n19 n8 = 1

spe.evtemp n20 \ n6 \ n18 \ n22 = 1

i.it n8 n17 = 1

1.1gate n1 n9 = 5.3e-9

1.1 drain n2 n5 = 1.0 e-9

1.1source n3 n7 = 1.7e-9

res.rlgate n1 n9 = 53

res.rldrain n2 n5 = 10

res.rlsource n3 n7 = 17

m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u

m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u

m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u

res.rbreak n17 n18 = 1, tc1=8.3e-4,tc2=-8e-7

res.rdrain n50 n16 = 3.2e-3, tc1=1.8e-3,tc2=8e-6

res.rgate n9 \ n20 = 2.2

res.rslc1 n5 n51 = 1e-6, tc1=9e-4,tc2=1e-6

res.rslc2 n5 n50 = 1e3

res.rsource n8 n7 = 3.2e-3, tc1=5e-3,tc2=1e-6

res.rvthres n22 n8 = 1, tc1 = -1e - 3, tc2 = -8.2e - 6

res.rvtemp n18 n19 = 1, tc1=-2.6e-3, tc2=2e-7

sw vcsp.s1a n6 n12 n13 n8 = model=s1amod

sw vcsp.s1b n13 n12 n13 n8 = model=s1bmod

sw vcsp.s2a n6 n15 n14 n13 = model=s2amod

sw vcsp.s2b n13 n15 n14 n13 = model=s2bmod

```

```

v.vbat n22 n19 = dc=1 equations { i (n51->n50) +=iscl iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/170))** 5)) } } }

```

Figure 23.

#### JUNCTION SPICE THERMAL MODEL th **REV 23 April 2004** FDD8880T RTHERM1 CTHERM1 CTHERM1 TH 6 8e-4 CTHERM2 6 5 1e-3 CTHERM3 5 4 2.5e-3 6 CTHERM4 4 3 2.6e-3 CTHERM5 3 2 8e-3 RTHERM2 CTHERM2 CTHERM6 2 TL 1.5e-2 RTHERM1 TH 6 1.44e-1 RTHERM2 6 5 1.9e-1 RTHERM3 5 4 3.0e-1 RTHERM3 **CTHERM3** RTHERM4 4 3 4.0e-1 RTHERM5 3 2 5.7e-1 RTHERM6 2 TL 5.8e-1 4 SABER THERMAL MODEL RTHERM4 CTHERM4 SABER thermal model FDD8880T 3 template thermal\_model th tl thermal\_c th, tl RTHERM5 CTHERM5 ctherm.ctherm1 th 6 = 8e - 4ctherm.ctherm2 6.5 = 1e-32 ctherm.ctherm3 5 4 = 2.5e-3ctherm.ctherm4 4 3 = 2.6e-3RTHERM6 CTHERM6 ctherm.ctherm5 3 2 = 8e-3ctherm.ctherm6 2 tl =1.5e-2rtherm.rtherm1 th 6 = 1.44e - 1rtherm.rtherm2 6 5 = 1.9e-1rtherm.rtherm354 = 3.0e - 1CASE rtherm.rtherm $4\ 4\ 3 = 4.0e - 1$ Figure 24. rtherm.rtherm5 3 2 = 5.7e-1rtherm.rtherm6 2 tl =5.8e-1

#### PACKAGE MARKING AND ORDERING INFORMATION

}

| Device    | Device Marking | Package Type                                   | Reel Size | Tape Width | Shipping <sup>†</sup> |

|-----------|----------------|------------------------------------------------|-----------|------------|-----------------------|

| FDD8880   | FDD8880        | DPAK3 (TO-252 3 LD)<br>(TO-252AA)<br>(Pb-Free) | 13"       | 16 mm      | 2500 / Tape & Reel    |

| FDD8880-G | FDD8880        | DPAK3 (TO-252 3 LD)<br>(TO-252AA)<br>(Pb-Free) | 13"       | 16 mm      | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

POWERTRENCH is registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

| DOCUMENT NUMBER: | 98AON13810G         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DPAK3 (TO-252 3 LD) |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

onsemi and ONSemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative