# Voltage Regulator -**Sequenced Linear, Dual**

The NCV8509 Series are dual voltage regulators whose output voltages power up in such a manner as to protect the integrity of modern day microcontroller I/O and ESD input structures. Newer generation microcontrollers require two power supplies. One voltage is used for powering the core, while the other powers the I/O.

#### Features

- Power–Up Sequence

- Output Voltage Options:

- V<sub>OUT1</sub> 5 V (±2%) 115 mA, V<sub>OUT2</sub> 2.6 V (2%) 100 mA

- ◆ V<sub>OUT1</sub> 5 V (±2%) 115 mA, V<sub>OUT2</sub> 2.5 V (2%) 100 mA

- ◆ V<sub>OUT1</sub> 3.3 V (±2%) 115 mA, V<sub>OUT2</sub> 1.8 V (2%) 100 mA

- Low 175 µA Quiescent Current

- Power Shunt

- Programmable RESET Time

- Dual Drive RESET Valid

- Programmable SLEW Rate Control

- Thermal Shutdown

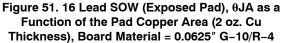

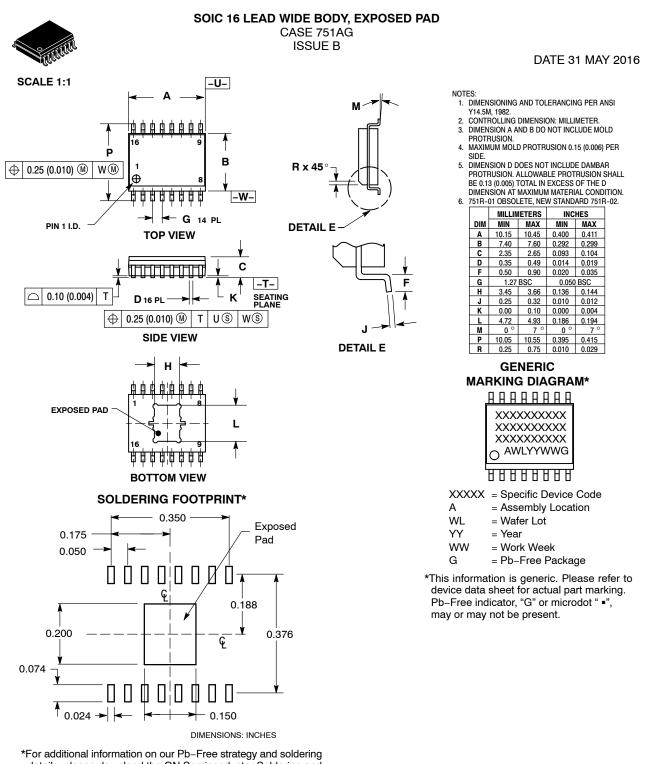

- 16 Lead SOW Exposed Pad

- NCV Prefix, for Automotive and Other Applications Requiring Site and Change Control

- AEC Qualified

- PPAP Capable

- These are Pb-Free Devices

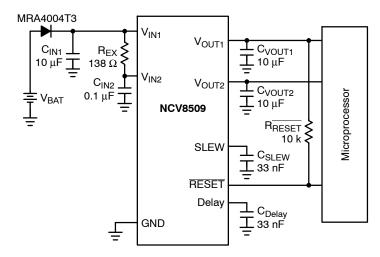

## **Typical Applications**

- Automotive Powertrain

- Telematics

Figure 1. Application Diagram

# **ON Semiconductor®**

http://onsemi.com

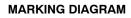

xx

А

SOIC 16 LEAD WIDE BODY EXPOSED PAD PDW SUFFIX CASE 751AG

- ww G

- = Pb-Free Device

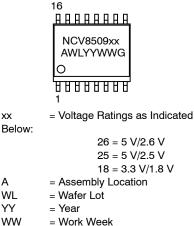

#### **PIN CONNECTIONS**

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 17 of this data sheet.

#### MAXIMUM RATINGS

| Ra                                                            | Value                                                                       | Unit              |              |

|---------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|--------------|

| V <sub>IN1</sub> (dc)                                         |                                                                             | -0.3 to 50        | V            |

| V <sub>IN1</sub> Peak Transient Voltage                       |                                                                             | 50                | V            |

| V <sub>IN2</sub> (dc)                                         |                                                                             | 50                | V            |

| V <sub>IN2</sub> (Current out of pin)                         |                                                                             | 10                | mA           |

| Operating Voltage                                             |                                                                             | 50                | V            |

| Input Voltage Range (SLEW, RESET, Delay)                      |                                                                             | –0.3 to 10        | V            |

| V <sub>OUT1</sub>                                             |                                                                             | 10                | V            |

| V <sub>OUT2</sub>                                             |                                                                             | 10                | V            |

| Electrostatic Discharge (Human Body Model)<br>(Machine Model) |                                                                             | 4.0<br>400        | kV<br>V      |

| Package Thermal Resistance, SOW-16 E Pad:                     | Junction-to-Case, R <sub>θJC</sub><br>Junction-to-Ambient, R <sub>θJA</sub> | 16<br>57          | °C/W<br>°C/W |

| Lead Temperature Soldering:                                   | Reflow: (SMD styles only) (Note 1)                                          | 240 peak (Note 2) | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. 60 second maximum above 183°C.

2.  $-5^{\circ}C/+0^{\circ}C$  allowable conditions.

# $\textbf{ELECTRICAL CHARACTERISTICS} \quad (6.0 \text{ V} < \text{V}_{\text{IN1}} < 18 \text{ V}, \text{ } \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{ } \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, \text{ } -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{ } \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{ } \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, \text{$

$C_{VOUT1} = C_{VOUT2} = 10 \ \mu\text{F}$ ; unless otherwise noted.)

| Characteristic                                          | Test Conditions                                                         | Min   | Тур | Max   | Unit |

|---------------------------------------------------------|-------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>OUT1</sub>                                       |                                                                         | ·     |     |       |      |

| Output Voltage                                          |                                                                         |       |     |       |      |

| 5 V Option                                              | 1.0 mA < I <sub>VOUT1</sub> < 100 mA                                    | 4.9   | 5.0 | 5.1   | V    |

| 3.3 V Option                                            | 1.0 mA < I <sub>VOUT1</sub> < 100 mA                                    | 3.234 | 3.3 | 3.366 | V    |

| Dropout Voltage (V <sub>IN1</sub> – V <sub>OUT1</sub> ) | I <sub>OUT</sub> = 100 mA                                               | -     | 400 | 600   | mV   |

|                                                         | I <sub>OUT</sub> = 100 μA                                               | -     | 100 | 200   | mV   |

| Load Regulation                                         | 1.0 mA < I <sub>VOUT1</sub> < 100 mA                                    | -     | 10  | 50    | mV   |

| Line Regulation                                         | 6.0 V < V <sub>IN1</sub> < 18 V                                         | -     | 10  | 50    | mV   |

| Current Limit                                           | V <sub>OUT1</sub> = V <sub>OUT1</sub> (typ) – 500 mV                    | 115   | 305 | 610   | mA   |

|                                                         | V <sub>OUT1</sub> = 0 V                                                 | -     | 105 | 300   | mA   |

| V <sub>OUT2</sub>                                       |                                                                         |       |     |       |      |

| Output Voltage                                          |                                                                         |       |     |       |      |

| 2.6 V Option                                            | 1.0 mA < I <sub>VOUT2</sub> < 100 mA                                    | 2.548 | 2.6 | 2.652 | V    |

| 2.5 V Option                                            | 1.0 mA < I <sub>VOUT2</sub> < 100 mA                                    | 2.450 | 2.5 | 2.550 | V    |

| 1.8 V Option                                            | 1.0 mA < I <sub>VOUT2</sub> < 100 mA                                    | 1.764 | 1.8 | 1.836 | V    |

| Load Regulation                                         | 1.0 mA < I <sub>VOUT2</sub> < 100 mA                                    | -     | 5.0 | 50    | mV   |

| Line Regulation                                         | 6.0 V < V <sub>IN1</sub> = V <sub>IN2</sub> < 18 V                      | -     | 10  | 50    | mV   |

| Current Limit                                           | $V_{OUT2} = V_{OUT2}$ (typ) – 500 mV                                    | 105   | 305 | 610   | mA   |

|                                                         | V <sub>OUT2</sub> = 0 V                                                 | -     | 105 | 300   | mA   |

| General                                                 |                                                                         |       |     |       | -    |

| Quiescent Current                                       | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 100 μA, V <sub>IN1</sub> = 12 V | -     | 125 | 175   | μA   |

|                                                         | $I_{OUT1} = I_{OUT2} = 50 \text{ mA}, V_{IN1} = 14 \text{ V}$           | -     | 5.0 | 10    | mA   |

| Thermal Shutdown (Note 3)                               | (Guaranteed by Design)                                                  | 150   | 180 | 210   | °C   |

3. Both outputs will turn off.

| Characteristic                                   | Test Conditions                                                                  | Min          | Тур          | Max                                              | Unit     |

|--------------------------------------------------|----------------------------------------------------------------------------------|--------------|--------------|--------------------------------------------------|----------|

| SLEW                                             |                                                                                  |              |              |                                                  |          |

| SLEW Charging Current                            | SLEW = 1.0 V                                                                     | 4.0          | 6.0          | 8.0                                              | μA       |

| V <sub>OUT1</sub> SLEW Rate (Note 4)             | C <sub>SLEW</sub> = 33 nF                                                        |              |              |                                                  |          |

| 5 V Option                                       |                                                                                  | -            | 710          | -                                                | V/s      |

| 3.3 V Option                                     |                                                                                  | -            | 469          | -                                                | V/s      |

| V <sub>OUT2</sub> SLEW Rate                      | C <sub>SLEW</sub> = 33 nF                                                        |              |              |                                                  |          |

| 2.6 V Option                                     |                                                                                  | -            | 370          | -                                                | V/s      |

| 2.5 V Option                                     |                                                                                  | -            | 355          | -                                                | V/s      |

| 1.8 V Option                                     |                                                                                  | -            | 256          | -                                                | V/s      |

| SLEW Control Threshold                           | (See Figure 53)                                                                  | 1.5          | 1.8          | 2.1                                              | V        |

| RESET                                            |                                                                                  |              |              |                                                  |          |

| RESET Threshold Increasing                       | -                                                                                | 94.5         | 96.5         | 98.5                                             | %        |

| (Note 5)                                         |                                                                                  |              |              |                                                  |          |

| RESET Threshold Decreasing                       | -                                                                                |              | 4 70         | 0.005 1/                                         | .,       |

| 5 V Option                                       |                                                                                  | 4.5          | 4.73         | $0.965 \times V_{OUT}$                           | V        |

| 3.3 V Option                                     |                                                                                  | 2.97         | 3.12         | $0.965 \times V_{OUT}$                           | V        |

| 2.6 V Option                                     |                                                                                  | 2.34<br>2.25 | 2.46<br>2.36 | $0.965 \times V_{OUT}$                           | V<br>V   |

| 2.5 V Option                                     |                                                                                  | 1.62         | 1.70         | $0.965 \times V_{OUT}$<br>$0.965 \times V_{OUT}$ | V        |

| 1.8 V Option                                     |                                                                                  |              |              |                                                  |          |

| RESET Output Low                                 | $I_{\text{RESET}} = 1.0 \text{ mA}$                                              | -            | 0.1          | 0.4                                              | V        |

| RESET Output Peak                                | Power Down (See Figure 41)                                                       | -            | 0.6          | 1.0                                              | V        |

| RESET Threshold Hysteresis                       | -                                                                                | 50           | 100          | 150                                              |          |

| 5 V Option                                       |                                                                                  | 50           | 100          | 150                                              | mV       |

| 3.3 V Option<br>2.6 V Option                     |                                                                                  | 33           | 66<br>50     | 99<br>78                                         | mV       |

| 2.5 V Option                                     |                                                                                  | 26<br>25     | 52<br>50     | 78<br>75                                         | mV<br>mV |

| 1.8 V Option                                     |                                                                                  | 18           | 36           | 75<br>54                                         | mV       |

| Delay                                            |                                                                                  | 10           | 50           | 54                                               | 1110     |

| Delay Switching Threshold                        | _                                                                                | 1.125        | 1.5          | 1.875                                            | V        |

| Delay Charge Current                             | Delay = 1.0 V                                                                    | 4.0          | 6.0          | 8.0                                              | μA       |

| Delay Saturation Voltage                         | V <sub>OUT1</sub> Out of Regulation                                              |              | -            | 0.1                                              | V        |

| Delay Discharge Current                          | Delay = 5.0 V $V_{OUT1}$ out of Regulation                                       | 10           | _            | -                                                | mA       |

| Output Tracking                                  |                                                                                  |              |              |                                                  |          |

| Delta 1 [V <sub>OUT1</sub> - V <sub>OUT2</sub> ] |                                                                                  |              |              |                                                  |          |

| 5 V Option                                       | $C_{OUT1} = C_{OUT2}$ , $I_{OUT1} = I_{OUT2}$                                    | _            | _            | 3.2                                              | V        |

| 3.3 V Option                                     | $C_{OUT1} = C_{OUT2}$ , $I_{OUT1} = I_{OUT2}$                                    | -            | -            | 2.8                                              | V        |

| Delta 2 [V <sub>OUT2</sub> – V <sub>OUT1</sub> ] | $C_{OUT1} = C_{OUT2}$ , $I_{OUT1} = I_{OUT2}$                                    | _            | _            | 100                                              | mV       |

| Power Shunt                                      |                                                                                  | 1            | 1            | 1                                                |          |

| Shunt Voltage 1 (V <sub>IN2</sub> )              | V <sub>IN1</sub> = 6.0 V, I <sub>OUT2</sub> = 100 mA, No R <sub>EX</sub>         | 3.3          | -            | 4.6                                              | V        |

| Shunt Voltage 2 (V <sub>IN2</sub> )              | V <sub>IN1</sub> = 12 V, 1.0 mA < I <sub>OUT2</sub> < 100 mA, No R <sub>EX</sub> | 3.25         | 4.5          | 5.75                                             | V        |

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} (6.0 \text{ V} < \text{V}_{\text{IN1}} < 18 \text{ V}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0 \text{ mA}, -40^{\circ}\text{C} < 125^{\circ}\text{C}, \text{I}_{\text{VOUT1}} = 5.0 \text{ mA}, \text{I}_{\text{VOUT2}} = 5.0$  $C_{VOUT1} = C_{VOUT2} = 10 \ \mu\text{F}$ ; unless otherwise noted.)

Not a tested parameter.

RESET signal sensitive to V<sub>OUT1</sub> and V<sub>OUT2</sub>.

# **PIN DESCRIPTION**

| Pin No.               | Symbol            | Description                                                                 |  |

|-----------------------|-------------------|-----------------------------------------------------------------------------|--|

| 1                     | SLEW              | Control for output rise time during power up. Requires capacitor to ground. |  |

| 2                     | Delay             | Timing capacitor for RESET function.                                        |  |

| 3                     | GND               | Ground.                                                                     |  |

| 4, 5, 7–9, 11, 14, 16 | NC                | No connection.                                                              |  |

| 6                     | RESET             | Active reset (accurate to $V_{OUT} > 1.0 V$ ).                              |  |

| 10                    | V <sub>OUT2</sub> | 100 mA output (±2% output voltage) for powering microprocessor core.        |  |

| 12                    | V <sub>IN2</sub>  | Input voltage for V <sub>OUT2</sub> .                                       |  |

| 13                    | V <sub>IN1</sub>  | Input voltage for V <sub>OUT1</sub> , and internal circuitry.               |  |

| 15                    | V <sub>OUT1</sub> | 100 mA output (±2% output voltage) for powering microprocessor I/O.         |  |

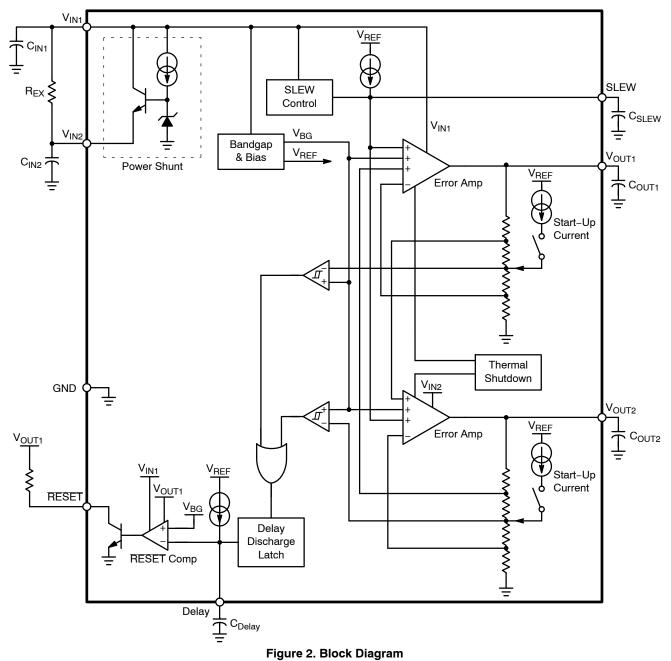

Figure 2. Block Diagram

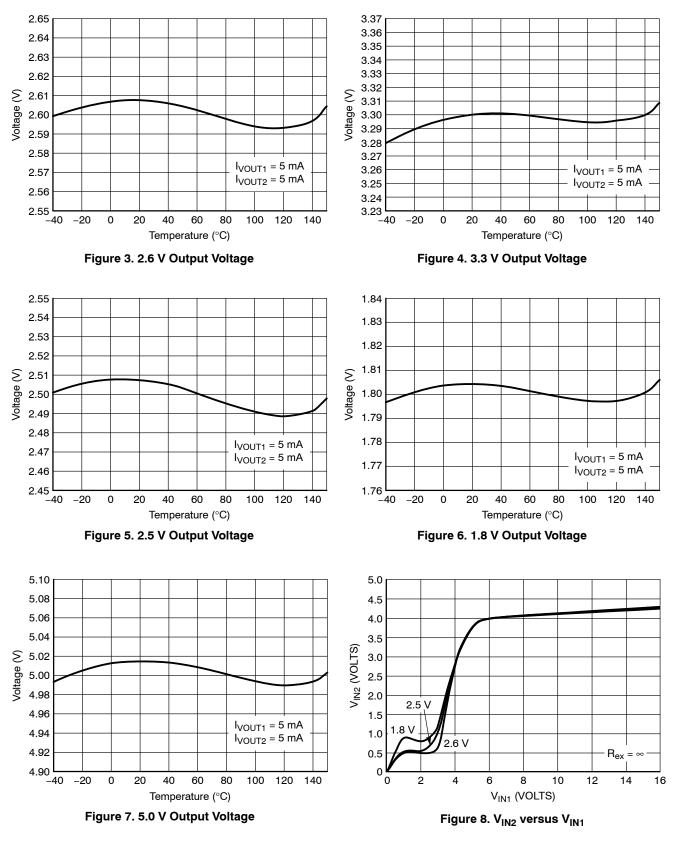

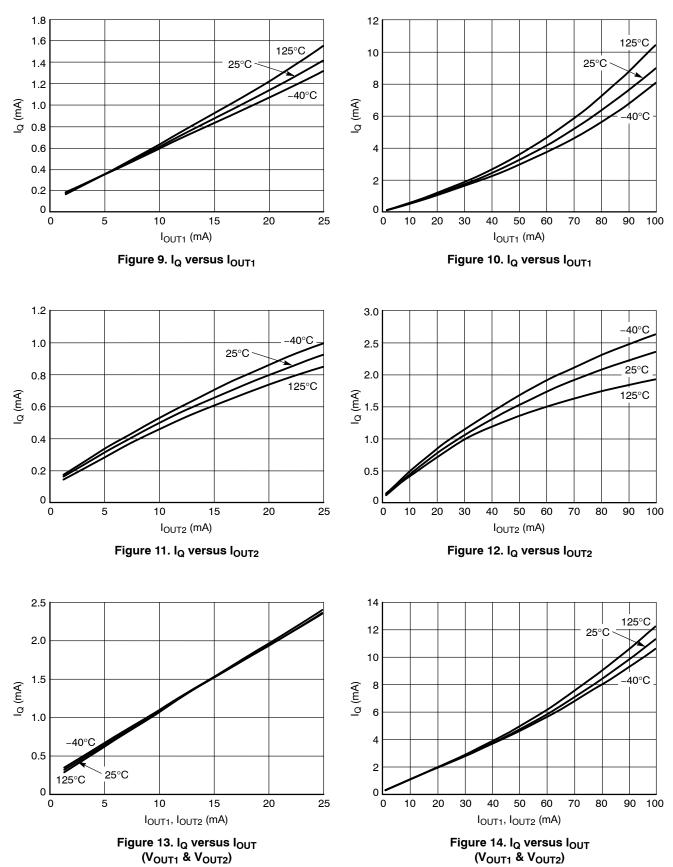

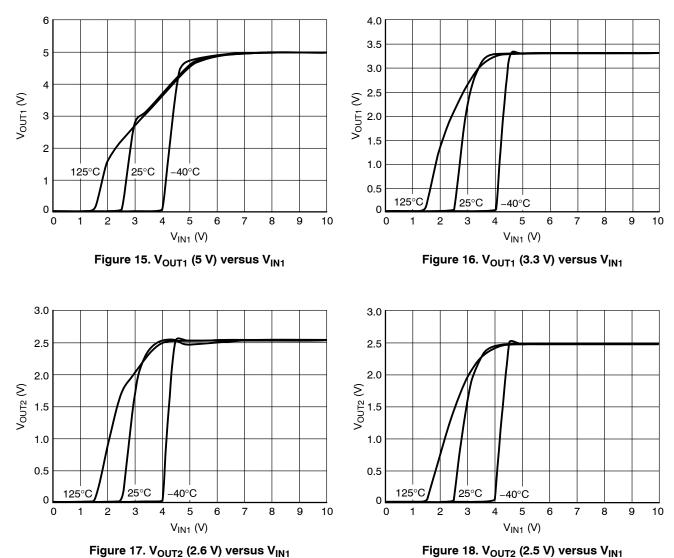

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

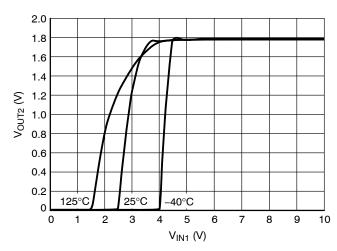

Figure 19.  $V_{OUT2}$  (1.8 V) versus  $V_{IN1}$

# **TYPICAL PERFORMANCE CHARACTERISTICS**

0.1

0.01

0 10 20

30

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

STABLE

REGION

60

OUTPUT CURRENT (mA)

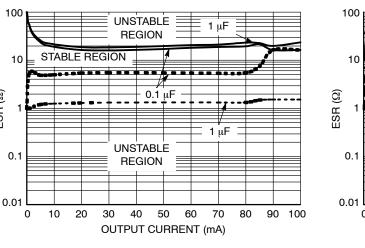

Figure 28. V<sub>OUT1</sub> Output Capacitor ESR (0.1  $\mu$ F / 1  $\mu$ F)

70

80

90

100

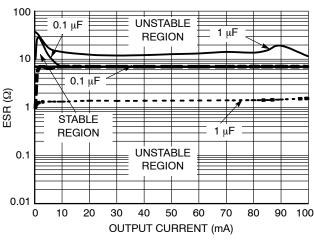

1

0.1

0.01 0

ESR (Ω)

10

20

30

40 50

Figure 30. V<sub>OUT2</sub> (2.5 V) Output Capacitor ESR (0.1 µF / 1 µF)

Figure 29. V<sub>OUT2</sub> (2.6 V) Output Capacitor ESR (0.1  $\mu$ F / 1  $\mu$ F)

50

OUTPUT CURRENT (mA)

60

UNSTABLE

REGION

40

1 μF

70

80

90 100

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

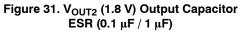

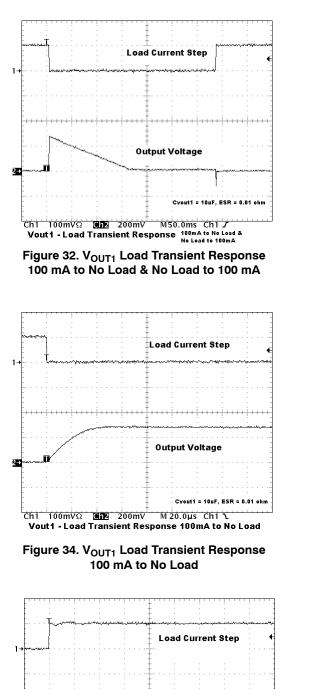

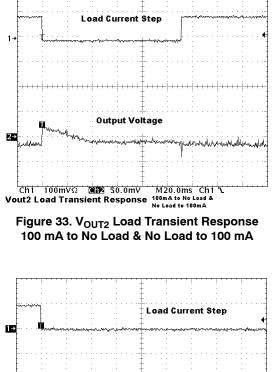

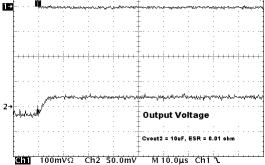

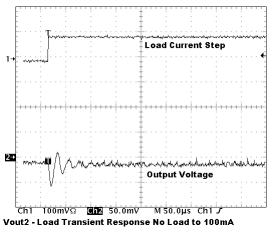

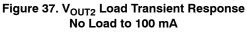

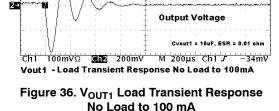

(Load Transient waveforms shown were measured on the 5 V/2.6 V device)

Vout2 - Load Transient Response 100mA to No Load

#### Figure 35. V<sub>OUT2</sub> Load Transient Response 100 mA to No Load

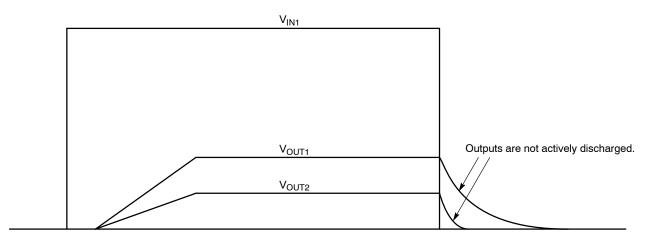

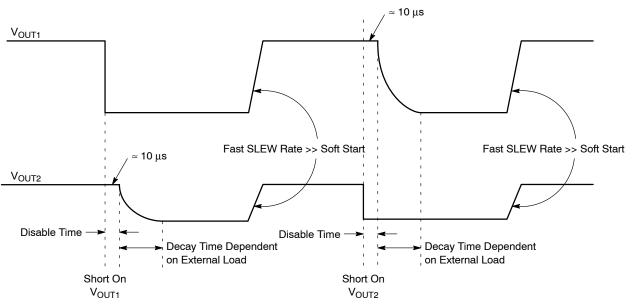

# TIMING DIAGRAMS

### Figure 38. Response to Impulse

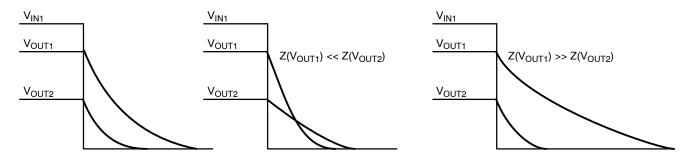

#### Figure 39. Output Decay vs. Load Impedance

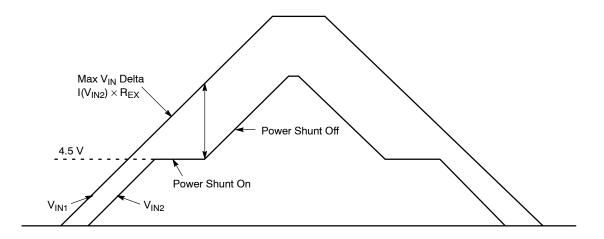

# Figure 40. V<sub>IN</sub> Power Shunt

#### **CIRCUIT DESCRIPTION**

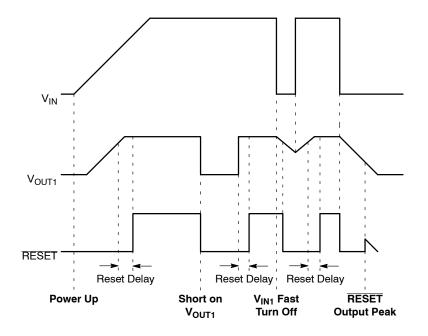

Figure 41. Dual Drive RESET Valid

#### RESET

The RESET function gets its drive from both the input  $(V_{IN1})$  and the output  $(V_{OUT1})$ . Because of this, it is able to maintain a more reliable reset valid signal. Most regulators maintain a valid reset signal down to 1 V on the output voltage. The reset on the NCV8509 is valid down to 0 V on the output voltage  $V_{OUT1}$  (power is provided via  $V_{IN1}$ ) and the reset on the NCV8509 is valid down to 0 V on the input voltage  $V_{IN1}$  (power is provided via  $V_{OUT1}$ ). Refer to Figure 41 for operation timing diagrams.

#### **Delay Function**

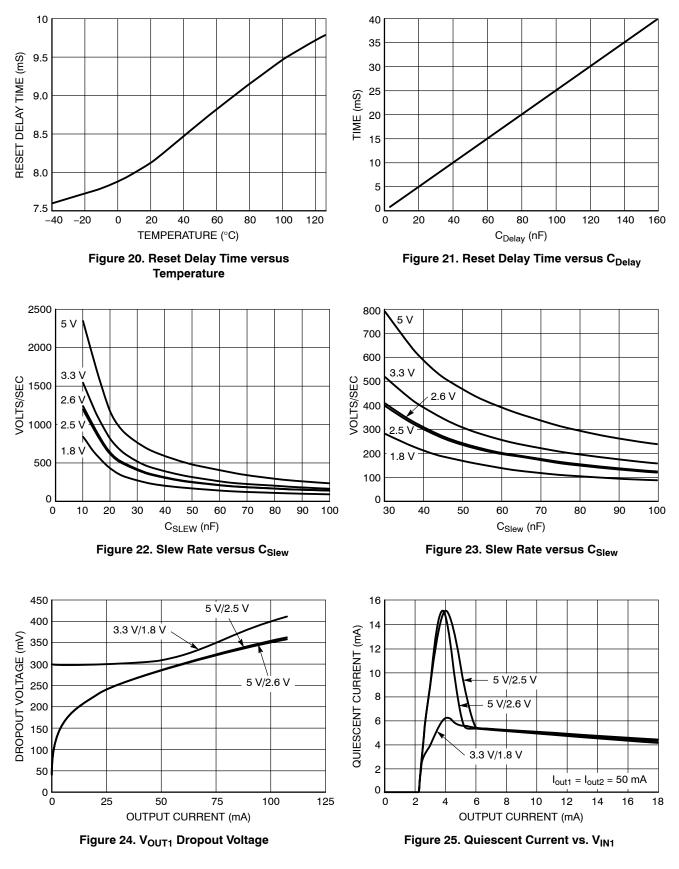

The reset delay circuit provides a programmable (by external capacitor) delay on the  $\overline{\text{RESET}}$  output lead.

The delay lead provides source current (typically  $6.0 \,\mu A$ ) to the external delay capacitor during the following proceedings:

- 1. During power up (once the regulation threshold has been verified);

- 2. After a reset event has occurred and the device is back in regulation.

The delay capacitor is discharged when the regulation  $(\overline{\text{RESET}}$  threshold) has been violated. This is a latched incident. The capacitor will fully discharge and wait for the device to regulate before going through the delay time event again.

#### **Power Shunt**

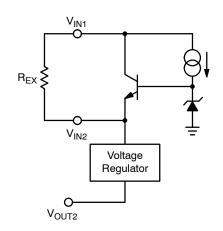

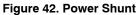

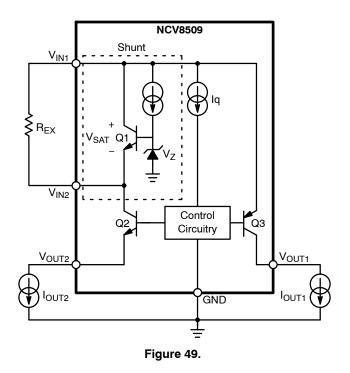

$R_{EX}$  routes some of the current used in the  $V_{OUT2}$  to a second input pin ( $V_{IN2}$ ). This is accomplished by using an internal shunt. A simplified version of this shunt is shown in Figure 42. This has the effect of reducing the amount of power dissipated on chip. The effects of choosing the external resistor value are shown in Figure 43.

Selection of the optimum Rex resistor value can be done using the following equation:

# (Vin(max) - 4.5)

# lout2(max)

When not using the power shunt, short  $V_{IN1}$  to  $V_{IN2}$ .

#### Why Use a Power Shunt?

The power shunt circuitry helps manage and optimize power dissipation on the integrated circuit.

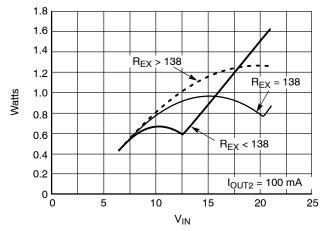

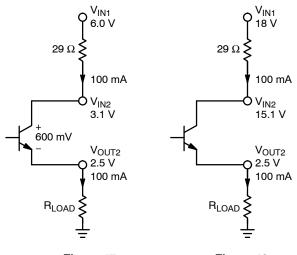

Figure 44 shows a 100 mA load. A 135  $\Omega$  resistor dissipates 1.35 W as shown.

Without the power shunt, the 135  $\Omega$  resistor would run into head room issues at 6.0 V and would only be able to drive 21.5 mA as shown in Figure 45 before causing the 2.5 V output to collapse.

Figure 46 shows the power shunt circuitry adding the current back in at low voltage operation. So the power is moved off chip at high voltage where it is needed most.

To further clarify, Figure 47 shows the maximum allowed resistor value (29  $\Omega$ ) without the power shunt for 6.0 V operation.

Figure 48 shows the scenario at high voltage. Only 290 mW of power is dissipated off chip compared to Figure 44 with 1.35 W.

Figure 47.

Figure 48.

#### **Power Dissipation**

NCV8509 has a power shunt circuit which reduces the power on chip by utilizing an external resistor,  $R_{EX}$ . Thus the power on chip,  $P_{IC}$ , is equal to the total power,  $P_T$ , minus the power dissipated in the resistor  $P_{REX}$ . Refer to Figure 49.

$$PIC = PTOTAL - PREX$$

<sup>(1)</sup>

where

$$PTOTAL = (VIN1 - VOUT1) IOUT1$$

<sup>(2)</sup>

+

$$(V_{IN1} - V_{OUT2}) I_{OUT2} + (V_{IN1} \times I_q)$$

and

$$P_{REX} = (V_{IN1} - V_{IN2}) I_{OUT2}$$

<sup>(3)</sup>

$V_{IN2} = \begin{cases} INT & ORT & for V_{IN1} < (V_{REF} + V_{SAT}) & (4) \\ V_{REF} & for (V_{REF} + V_{SAT}) < V_{IN1} < (V_{REF} + (I_{OUT2} \times R_{EX})) \\ for (V_{REF} + (I_{OUT2} \times I_{OUT})) < V_{IN1} & (V_{IN1} - (I_{OUT2} \times R_{EX})) \\ & where V_{REF} = V_Z - V_{BE} when Q1 is normally conducting. \end{cases}$

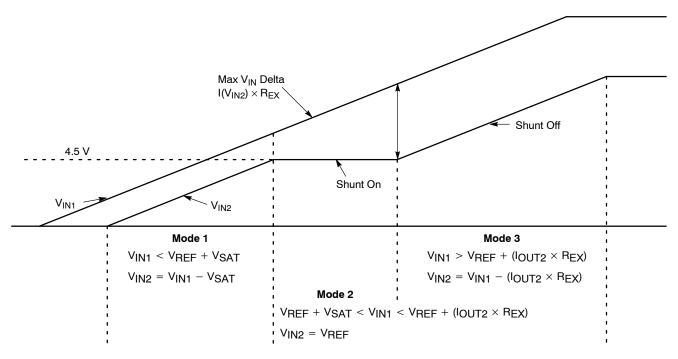

Based on equation 3, the power in  $R_{EX}$  is dependent on  $V_{IN2}$ . (Increasing  $R_{EX}$  may require an increase in  $C_{IN2}$ . A careful system validation should be performed for stability). The voltage on  $V_{IN2}$  is controlled by the shunt circuit, which has three modes of operation, as seen in Figure 50.

**Mode 1.** At low battery  $V_{IN2}$  is equal to  $V_{IN1}$  minus the saturation voltage of the shunt output NPN.

Mode 2. Once  $V_{IN1}$  rises above the reference voltage of the shunt circuit,  $V_{IN2}$  will regulate at the  $V_{REF}$ .

**Mode 3.**  $V_{IN2}$  would continue to regulate at  $V_{REF}$ , but since  $I_{OUT2}$  is not infinite, when  $V_{IN1}$  rises higher than the

reference voltage plus the voltage drop across the external resistor  $R_{EX}$ , it will force  $V_{IN2}$  to be  $V_{IN1} - (I_{OUT2} \times R_{EX})$ . Equation 4 provides a summary for  $V_{IN2}$ .

Combining equations 3 and 4 gives three different equations for power across  $R_{EX}$ .

$$P_{MODE1} = (V_{SAT} \times I_{OUT2})$$

(5)

$$P_{MODE2} = (V_{IN1} - V_{REF}) \times I_{OUT2}$$

<sup>(6)</sup>

$$\mathsf{P}_{\mathsf{MODE3}} = \mathsf{I}_{\mathsf{OUT2}} \times \mathsf{R}_{\mathsf{EX}} \tag{7}$$

Figure 50. V<sub>IN</sub> Shunt

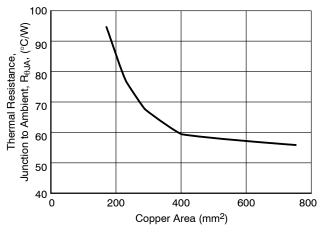

Once the value of  $P_{IC(max)}$  is known, the maximum permissible value of  $R_{\theta JA}$  can be calculated:

$$\mathsf{R}_{\theta}\mathsf{J}\mathsf{A} = \frac{150^{\circ}\mathsf{C} - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{I}\mathsf{C}}} \tag{8}$$

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with

$R_{\theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

#### **Heat Sinks**

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\theta IA}$ :

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA}$$

<sup>(9)</sup>

where:

$R_{\theta JC}$  = the junction-to-case thermal resistance,

$R_{\theta CS}$  = the case-to-heatsink thermal resistance, and

$R_{\theta SA}$  = the heatsink-to-ambient thermal resistance.

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta JA}$ , it too is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

Figure 52. Fault Response. Note the High SLEW Rate Coming Out of Fault Conditions. Soft Start Only Applies to a Power Up Sequence.

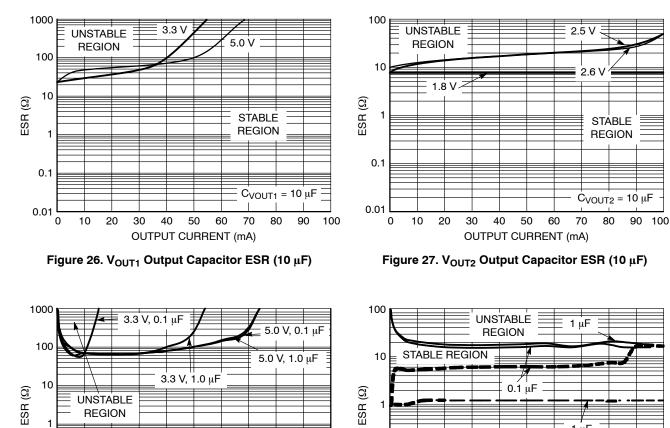

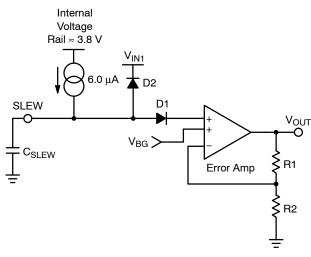

#### **Slew Rate Control**

Figure 53 shows the circuitry associated with Slew Rate Control. The diagram highlights the control of one output for simplicity.  $V_{OUT1}$  and  $V_{OUT2}$  are both controlled on the IC.

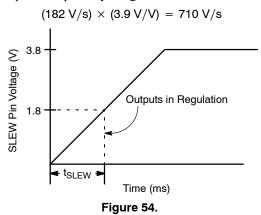

The slew rate capacitor ( $C_{SLEW}$ ) is charged with an on-chip current source runing at 6.0  $\mu$ A (typ.). Charging a capacitor with a current source creates a linear voltage ramp as shown in Figure 54.

The lowest voltage to the positive terminals of the comparator (Error Amp) dominates the output voltage ( $V_{OUT}$ ). Consequently, when  $C_{SLEW}$  is fully discharged on power up, it is the dominant factor on the positive terminal and disables the output. The output ( $V_{OUT}$ ) follows the linear ramp on the SLEW pin (after being gained up with R1 and R2) until  $V_{BG}$  becomes the dominant voltage. This occurs when SLEW =  $V_{BG} + V_{D1}$  or approximately 1.8 V.

Figure 53. Slew Control Circuitry

Slew time can be calculated using the standard capacitor equation.

$$I = C \frac{dv}{dt}$$

,  $t = \frac{C(\Delta V)}{I}$

Using a 33 nF capacitor, the slew time is:

The corresponding slew rate for this is 1.8 V/9.9 ms = 182 V/s ON THE SLEW PIN.

To calculate the slew rate on outputs, you must multiply by the gain set up by R1 and R2.

$$A_V = \frac{V_{OUT}}{1.28 \text{ V}}$$

For a 5 V output, the gain would be:

$$A_V = \frac{5 V}{1.28 V} = 3.9 V/V$$

assuming  $V_{BG} = 1.28$  V.

The resultant slew rate on the output is the slew rate on the SLEW pin multiplied by the gain, or:

#### **ORDERING INFORMATION**

| Device          | Output Voltage | Package                   | Shipping <sup>†</sup> |

|-----------------|----------------|---------------------------|-----------------------|

| NCV8509PDW18G   | 0.03/// 03//   | SOIC 16 Lead<br>(Pb-Free) | 47 Units/Rail         |

| NCV8509PDW18R2G | 3.3 V/1.8 V    | SOIC 16 Lead<br>(Pb-Free) | 1000 Tape & Reel      |

| NCV8509PDW25G   |                | SOIC 16 Lead<br>(Pb-Free) | 47 Units/Rail         |

| NCV8509PDW25R2G | 5 V/2.5 V      | SOIC 16 Lead<br>(Pb-Free) | 1000 Tape & Reel      |

| NCV8509PDW26G   | 5.1/2.0.1/     | SOIC 16 Lead<br>(Pb-Free) | 47 Units/Rail         |

| NCV8509PDW26R2G | 5 V/2.6 V      | SOIC 16 Lead<br>(Pb-Free) | 1000 Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

DOCUMENT NUMBER:

98AON21237D

Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

SOIC-16, WB EXPOSED PAD

PAGE 1 OF 1

ON Semiconductor and up are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative