# 150 mA CMOS Low Iq Low-Dropout Voltage Regulator with Voltage Detector Output

The NCP400 is an integration of a low–dropout regulator and a voltage detector in a very small chip scale package. The voltage regulator is capable of supplying 150 mA with a low dropout of 160 mV at 100 mA. It contains a voltage reference unit, an error amplifier, comparators, PMOS power transistor, current limit and thermal shutdown protection circuits for the regulator portion.

A highly accurate voltage detector with hysteresis and an externally programmable time delay generator are implemented to prevent erratic system reset operation. It features complementary output with active low reset function.

The NCP400 is designed to work with low cost ceramic capacitors and requires only a small 1.0  $\mu$ F capacitor at regulator output. Its low quiescent current is ideal for battery powered applications.

#### **Features**

- LDO Voltage Regulator and Voltage Detector Together in a Very Small Wafer Level Package, 6 Bump Flip—Chip, 1.0 x 1.5 mm

- Low Quiescent Current of 50 μA Typical

- Internal Current Limit and Thermal Shutdown Protection

- Low Cost and Small Size Ceramic Capacitors

- Input Voltage Range of 1.8 V to 5.0 V

- Voltage Regulator

- 1.8 V (\*) Output with 2% Accuracy

- Excellent Line and Load Regulation

- Low Dropout of 160 mV at 100 mA

- Voltage Detector

- 2.3 V (\*) Threshold with 2% Accuracy

- Externally Programmable Time Delay Generator

- Excellent Line and Load Regulation

- This is a Pb-Free Device

- (\*) Other voltages can be developed upon request. Please contact your ON Semiconductor representative.

## **Typical Applications**

- Memory Cards

- Cellular Phones

- Digital Still Cameras and Camcorders

- Battery Powered Equipment

ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAM

6 Bump Flip-Chip FC SUFFIX CASE 499AH

400 = Device Code

A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

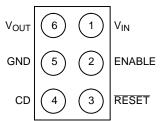

#### PIN CONNECTIONS

(Bottom View)

#### **ORDERING INFORMATION**

| Device      | Package                | Shipping <sup>†</sup> |

|-------------|------------------------|-----------------------|

| NCP400FCT2G | Flip-Chip<br>(Pb-Free) | 3000 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

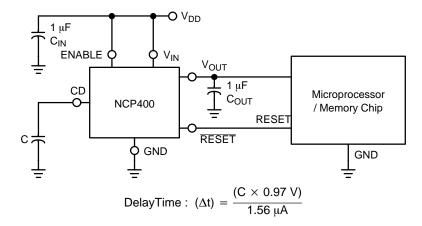

# **TYPICAL OPERATION CIRCUIT**

Figure 1. Power Supply and Reset Circuit for Microprocessor and/or Memory Chip

# **PIN DESCRIPTION**

| Pin No. | Symbol           | Description                                                                                                                                                                                      |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>IN</sub>  | Positive power supply input voltage.                                                                                                                                                             |

| 2       | ENABLE           | This input is used to place the device into low–power standby. When this input is pulled low, the device is disabled. If this function is not used, ENABLE should be connected to $V_{\rm IN}$ . |

| 3       | RESET            | Voltage detect output signal.                                                                                                                                                                    |

| 4       | CD               | Delay capacitor pin.                                                                                                                                                                             |

| 5       | GND              | Power supply ground.                                                                                                                                                                             |

| 6       | V <sub>OUT</sub> | Voltage regulator output voltage.                                                                                                                                                                |

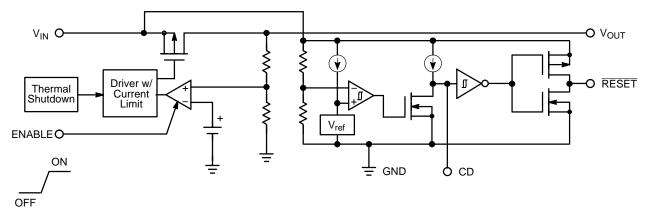

# REPRESENTATIVE BLOCK DIAGRAM

Figure 2. Representative Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                                       | Symbol           | Value                        | Unit |

|--------------------------------------------------------------------------------------------------------------|------------------|------------------------------|------|

| Input Voltage                                                                                                | V <sub>IN</sub>  | 0 to 5.5                     | V    |

| Enable Voltage                                                                                               | ENABLE           | -0.3 to V <sub>IN</sub> +0.3 | V    |

| Output Voltage                                                                                               | V <sub>OUT</sub> | -0.3 to V <sub>IN</sub> +0.3 | V    |

| Delay Capacitor Pin Voltage                                                                                  | V <sub>CD</sub>  | -0.3 to V <sub>IN</sub> +0.3 | V    |

| Reset Pin Voltage                                                                                            | Vreset           | -0.3 to V <sub>IN</sub> +0.3 | V    |

| Reset Pin Current                                                                                            | Ireset           | 70                           | mA   |

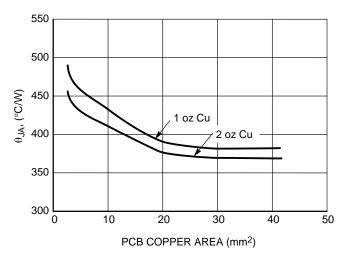

| Power Dissipation and Thermal Characteristics for Microbump–6<br>Thermal Resistance Junction–to–Air (Note 3) | $R_{	heta JA}$   | Refer to Figure 22           | °C/W |

| Operating Junction Temperature                                                                               | T <sub>J</sub>   | -40 to +125                  | °C   |

| Operating Ambient Temperature                                                                                | T <sub>A</sub>   | -40 to +85                   | °C   |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

- This device contains ESD protection and exceeds the following tests:

Human Body Model (HBM) ±2000 V per MIL–STD–883, Method 3015

Machine Model (MM) ±200 V.

- Latchup capability (85°C)100 mA DC with trigger voltage.

PCB top layer uses a single copper layer and is tested @ 250 mW.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN} = V_{OUT(nom.)} + 1.0 \text{ V}$ , ENABLE =  $V_{IN}$ ,  $C_{IN} = 1.0 \text{ }\mu\text{F}$ ,  $C_{OUT} = 1.0 \text{ }\mu\text{F}$ ,  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.)

| Characteristic                                                                                                                                         | Symbol                                 | Min        | Тур          | Max        | Unit  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|--------------|------------|-------|

| Input Voltage ( $T_A = -40^{\circ}C$ to $85^{\circ}C$ )                                                                                                | V <sub>IN</sub>                        | 1.8        | _            | 5.0        | V     |

| Output Voltage (T <sub>A</sub> = 25°C, I <sub>OUT</sub> = 1.0 mA)                                                                                      | V <sub>OUT</sub>                       | 1.764      | 1.8          | 1.836      | V     |

| Output Voltage ( $T_A = -40^{\circ}\text{C}$ to 85°C, $I_{OUT} = 1.0 \text{ mA}$ )                                                                     | V <sub>OUT</sub>                       | 1.746      | 1.8          | 1.854      | V     |

| Line Regulation (I <sub>OUT</sub> = 10 mA, V <sub>IN</sub> = 2.8 V to 5.0 V)                                                                           | Reg line                               | -          | 1.0          | 3.5        | mV/V  |

| Load Regulation (I <sub>OUT</sub> = 1.0 mA to 150 mA)                                                                                                  | Reg load                               | -          | 0.3          | 0.8        | mV/mA |

| Maximum Output Current                                                                                                                                 | I <sub>OUT(nom.)</sub>                 | -          | 150          | -          | mA    |

| Dropout Voltage (I <sub>OUT</sub> = 100 mA, Measured at V <sub>OUT</sub> -3.0%)                                                                        | V <sub>IN</sub> -V <sub>OUT</sub>      | -          | 160          | 200        | mV    |

| Quiescent Current (Enable Input = 0V, I <sub>OUT</sub> = 0 mA) (Enable Input = V <sub>IN</sub> , I <sub>OUT</sub> = 1.0 mA to Io(nom.))                | I <sub>Q_SD</sub><br>I <sub>Q_EN</sub> | -<br>-     | 0.25<br>37   | 1.0<br>100 | μΑ    |

| Enable Input Threshold Voltage<br>(Voltage Decreasing, Output Turns Off, Logic Low)<br>(Voltage Increasing, Output Turns On, Logic High)               | V <sub>TH(EN)</sub>                    | 0.17<br>-  | 0.25<br>1.25 | -<br>1.65  | V     |

| Output Short Circuit Current (V <sub>OUT</sub> = 0 V, V <sub>IN</sub> = 5.0 V) (Note 4)                                                                | I <sub>OUT(MAX)</sub>                  | 200        | 400          | 800        | mA    |

| Ripple Rejection (f = 1.0 kHz, lo = 60 mA)                                                                                                             | RR                                     | _          | 50           | -          | dB    |

| Output Noise Voltage (f = 20 Hz to 100 kHz, I <sub>OUT</sub> = 60 mA)                                                                                  | V <sub>N</sub>                         | -          | 110          | -          | μVrms |

| Output Voltage Temperature Coefficient                                                                                                                 | T <sub>C</sub>                         | -          | ±100         | -          | ppm°C |

| Detector Threshold (T <sub>A</sub> = 25°C)                                                                                                             | V <sub>DET</sub>                       | 2.254      | 2.30         | 2.346      | V     |

| Detector Threshold Hysteresis                                                                                                                          | V <sub>HYS</sub>                       | 0.069      | 0.115        | 0.161      | V     |

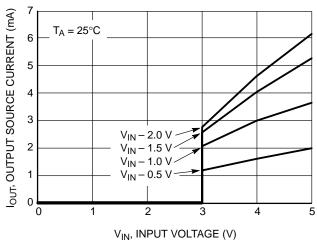

| Reset Output Current N-Channel Sink Current (Reset = 0.5 V, V <sub>IN</sub> = 1.8 V) P-Channel Source Current (Reset = 2.4 V, V <sub>IN</sub> = 4.5 V) | I <sub>RESET</sub>                     | 1.0<br>1.0 | 7.0<br>5.5   | -<br>-     | mA    |

| CD Delay Pin Threshold Voltage (Pin 4) (V <sub>IN</sub> =2.0 V)                                                                                        | V <sub>TH(CD)</sub>                    | 0.76       | 0.97         | 1.14       | V     |

| Delay Capacitor Pin Sink Current (Pin 4) (V <sub>IN</sub> = 1.8 V, VCD = 0.5 V)                                                                        | I <sub>CD_SINK</sub>                   | 0.2        | 39           | -          | mA    |

| Delay Current Pin Source Current (Pin 4)<br>(VCD = 0, V <sub>IN</sub> = 2.8 V)                                                                         | I <sub>CD_</sub> SOURCE                | 0.78       | 1.56         | 3.12       | μΑ    |

<sup>4.</sup> Values are guaranteed by design.

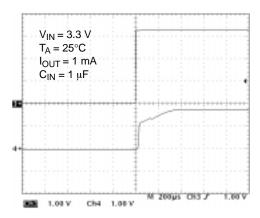

## **TYPICAL CHARACTERISTICS**

Upper Trace: Input Voltage 1 V/div Lower Trace: Output Voltage 1 V/div

Figure 3. Turn-ON Response

$I_{OUT}$  = 150 mA to 1 mA,V $_{IN}$  = 3.3 V,  $C_{IN}$  = 1  $\mu F$  Upper Trace: Output Voltage 200 mV/div Lower Trace: Output Loading Current 100 mA/div

**Figure 5. Load Transient Response**

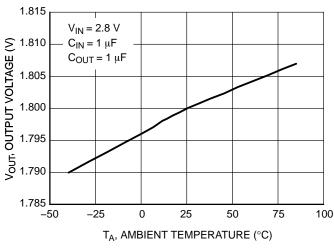

Figure 7. Output Voltage vs. Temperature

Upper Trace: Input voltage 2 V/div Lower Trace: Output voltage 50 mV/div

Figure 4. Line Transient Response

$I_{OUT}$  = 1 mA to 150 mA,V $_{IN}$  = 3.3 V,C $_{IN}$  = 1  $\mu$ F Upper Trace: Output Voltage 200 mV/div Lower Trace: Output Loading Current 100 mA/div

**Figure 6. Load Transient Response**

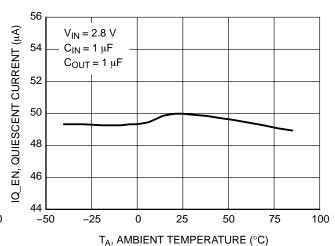

Figure 8. Quiescent Current (Enable) vs. Temperature

## **TYPICAL CHARACTERISTICS**

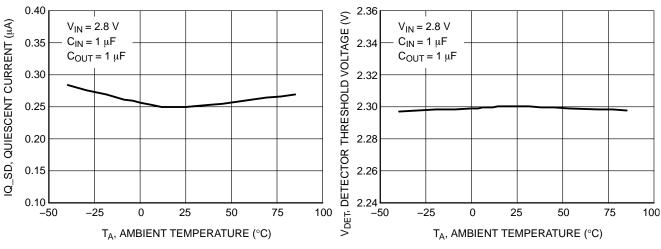

Figure 9. Quiescent Current (Shutdown) vs. Temperature

Figure 10. Detector Threshold Voltage vs. Temperature

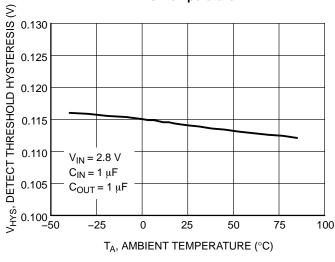

Figure 11. Dectector Threshold Hysteresis Voltage vs. Temperature

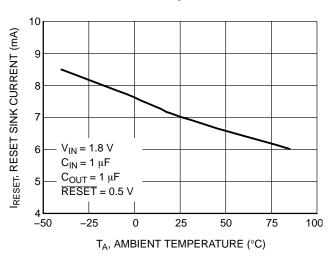

Figure 12. RESET Pin N-Channel Sink Current vs. Temperature

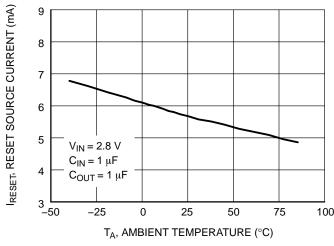

Figure 13. RESET Pin P-Channel Source Current vs. Temperature

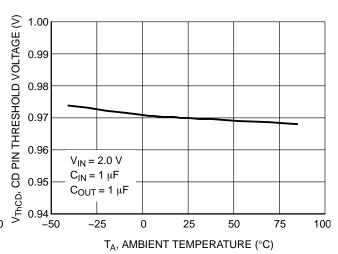

Figure 14. CD Delay Pin Threshold Voltage vs. Temperature

#### **TYPICAL CHARACTERISTICS**

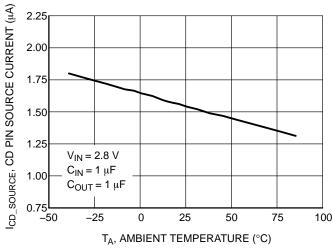

Figure 15. CD Pin Source Current vs. Temperature

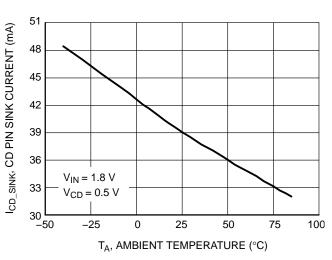

Figure 16. CD Pin Sink Current vs. Temperature

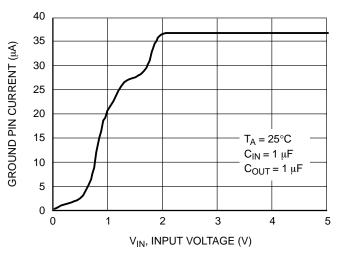

Figure 17. Ground Pin Current vs. Input Voltage

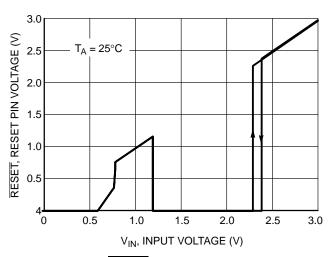

Figure 18. RESET Pin Voltage vs. Input Voltage

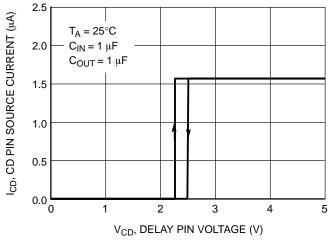

Figure 19. Delay Pin Source Current vs. Voltage

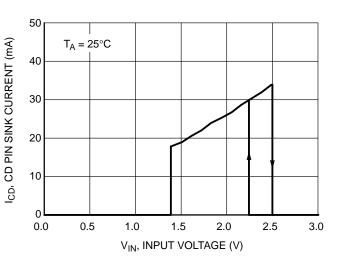

Figure 20. CD Pin Sink Current vs. Input Voltage

# **TYPICAL CHARACTERISTICS**

Figure 21. Reset Output Source Current vs. Input Voltage

Figure 22.  $\theta_{\text{JA}}$  vs. Copper Area

#### **OPERATION DESCRIPTION**

#### **Low Dropout Voltage Regulator**

The low dropout voltage regulator contains a voltage reference unit, an error amplifier, a PMOS power transistor, resistors for setting output voltage, current limit and thermal shutdown protection circuits.

#### **Enable Operation**

The enable pin will turn on or off the regulator. The limits of threshold are covered in the electrical specification section of this data sheet. If the enable is not used then the pin should be connected to  $V_{\rm in}$ .

# **Voltage Detector**

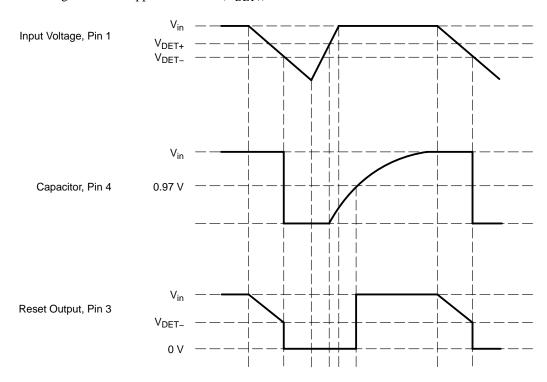

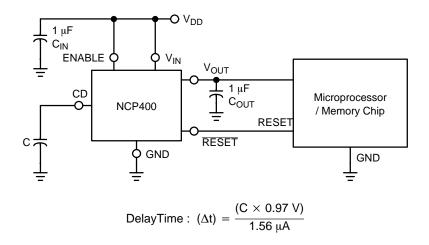

The NCP400 consist of a precision voltage detector that drives a time delay generator. Figures 23 and 24 show a timing diagram and a typical application. Initially consider that input voltage  $V_{in}$  is at a nominal level and it is greater than the voltage detector upper threshold ( $V_{DET+}$ ). The

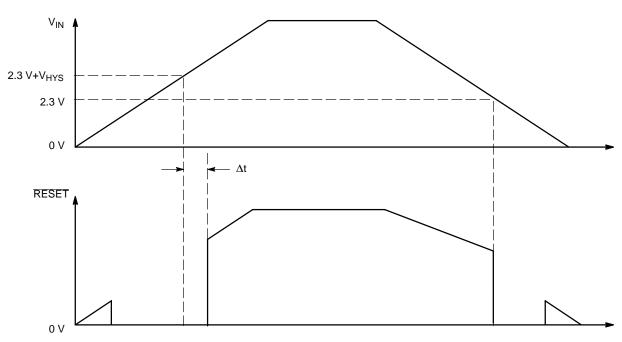

voltage at CD Pin (Pin 4) will be at the same level as Vin, and the reset output (Pin 3) will be in the high state. If there is a power interruption and Vin becomes significantly deficient, it will fall below the lower detector threshold (VDET-) and the external time delay capacitor CD will be immediately discharged by an internal N-Channel MOSFET that connects to Pin 4. This sequence of events causes the Reset output to be in the low state. After completion of the power interruption, Vin will again return to its nominal level and become greater than the V<sub>DET+</sub>. The voltage detector will turn off the N-Channel MOSFET and allow internal current source to charge the external capacitor CD, thus creating a programmable delay for releasing the reset signal. When the voltage at CD Pin 4 exceeds the inverter threshold, typically 0.97 V, the reset output will revert back to its original state. The detail reset output time delay calculation is shown in Figure 24.

Figure 23. Timing diagram

# **APPLICATION NOTES**

Figure 24. Timing Diagram

Delay Time:

$$(\Delta t) = \frac{(C \times \Delta V_{ThCD})}{I_{CD}}$$

where: C is the CD pin capacitor

$\Delta V_{ThCD}$  is the delay threshold voltage

I<sub>CD</sub> is delay current source.

As target use C = 3300 pF and have

$$\Delta t$$

= 2 ms: With internal  $\Delta V_{ThCD}$  = 0.97 V and  $I_{CD}$  =1.56  $\mu A$ , then

$$\Rightarrow$$

Delay Time:  $(\Delta t) = \frac{(3300 \text{ pF} \times 0.97 \text{ V})}{1.56 \mu\text{A}} = 2.05 \text{ ms}$

#### APPLICATION INFORMATION

#### **Low Dropout Voltage Regulator**

## -Input Decoupling

A 1.0  $\mu F$  capacitor either ceramic or tantalum is recommended and should be connected close to the NCP400 package. Higher values and lower ESR will improve the overall line transient response.

#### -Output Decoupling

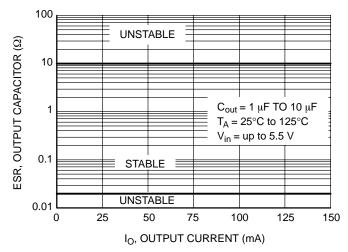

The NCP400 is a stable Regulator and does not require any specific Equivalent Series Resistance (ESR) or a

minimum output current. Capacitors exhibiting ESRs ranging from a few  $m\Omega$  up to  $10~\Omega$  can thus safely be used. The minimum decoupling value is  $1.0~\mu F$  and can be augmented to fulfill stringent load transient requirements. The regulator accepts ceramic chip capacitors as well as tantalum devices. Larger values improve noise rejection and load regulation transient response. Figure 25 shows the stable area of the regulator with different output capacitor ESR and output current.

Figure 25. Output Capacitor versus Output Current

#### -Thermal Protection

Internal thermal shutdown circuit is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When the thermal protection activated, higher than 150°C, the regulator turns off. This feature is provided to prevent failures from accidental overheating.

## -Hints

Please be sure the Vin and GND lines are sufficiently wide. When the impedance of these lines is high, there is a chance to pick up noise or cause the regulator to

malfunction. Set external components, especially the output capacitor, as close as possible to the circuit, and make leads a short as possible.

## **Voltage Detector**

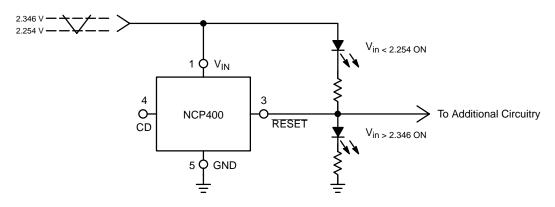

The voltage detector has built—in hysteresis to prevent erratic reset operation. This device is specifically designed for use as reset controllers in portable microprocessor based systems, it can offer a cost—effective solution in numerous applications where precise voltage monitoring and time delay are required. Figures 26 through 27 shows various application examples.

# **APPLICATION CIRCUIT INFORMATION**

Figure 26. Input Voltage Indicator

Figure 27. Microprocessor Reset Circuit

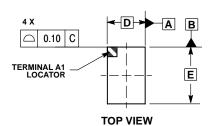

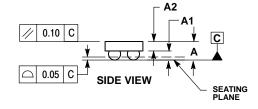

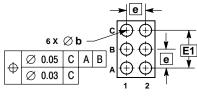

**6 PIN FLIP-CHIP** CASE 499AH-01 **ISSUE O**

**DATE 19 APR 2004**

**BOTTOM VIEW**

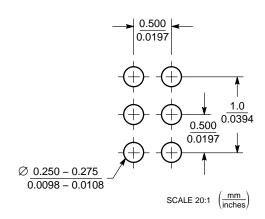

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL

CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 0.448       | 0.533 |  |  |

| A1  | 0.210 0.270 |       |  |  |

| A2  | 0.238       | 0.263 |  |  |

| D   | 1.000 BSC   |       |  |  |

| Е   | 1.50 BSC    |       |  |  |

| b   | 0.290       | 0.340 |  |  |

| е   | 0.500 BSC   |       |  |  |

| E1  | 1.000 BSC   |       |  |  |

# **GENERIC** MARKING DIAGRAM\*

XXX= Specific Device Code Α = Assembly Location

= Wafer Lot Υ = Year W = Work Week

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.

| DOCUMENT NUMBER: | 98AON15006D                                           | Electronic versions are uncontrol                                    | '           |  |

|------------------|-------------------------------------------------------|----------------------------------------------------------------------|-------------|--|

| STATUS:          | ON SEMICONDUCTOR STANDARD                             | accessed directly from the Document versions are uncontrolled except | ' '         |  |

| NEW STANDARD:    |                                                       | "CONTROLLED COPY" in red.                                            |             |  |

| DESCRIPTION:     | 6 PIN FLIP-CHIP, NCP400, 1.00 X 1.5 MM, 0.50 MM PITCH |                                                                      | PAGE 1 OF 2 |  |

| ON | Semiconductor® | 01 |

|----|----------------|----|

|----|----------------|----|

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 98AON15006      | D       |

PAGE 2 OF 2

| ISSUE | REVISION                                  | DATE        |

|-------|-------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION. REQ. BY S. BROW. | 19 APR 2004 |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

|       |                                           |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative