# High Performance Switcher Integrated with HV Startup and SENSEFET®

The FSL5x8 is an integrated peak-current-mode controlled pulse width modulation (PWM) power switch, specifically designed for off-line switch-mode power supplies. The PWM controller includes an advanced soft-start, frequency hopping, optimized gate driver, internal transconductance amplifier, temperature-compensated precise current source for loop compensation and enhanced self-protections as well. Compared to a discrete MOSFET and PWM controller solution, the FSL5x8 allows to reduce total cost, component count, size, and weight, while simultaneously increasing efficiency, productivity, and system reliability. This device provides a basic platform for cost-effective design of both isolated and non-isolated Flyback converters.

#### **Features**

- Integrated Rugged 800 V Super-Junction MOSFET with SENSEFET Technology

- Built-in HV Current Source for Start-up

- Peak-current-mode Control with Slope Compensation

- AC Line Compensation for Accurate Over Power Protection

- Advanced Soft-start for Low Electrical Stress

- Pulse-by-pulse Current Limit

- FSL5x8A: 100 kHz and FSL5x8H: 130 kHz

- Line Brown-in, Brown-out Function

- Line Over-voltage Protection (LOVP)

- Adjustable Burst-mode Operation

- Frequency Hopping for Low EMI

- All Protections are Auto-Recovery: Brown-out, OLP, OVP, AOCP and TSD

- These Devices are Pb-Free, Halogen Free/BFR Free and RoHS Compliant

#### **Typical Applications**

- Power Supplies for White Goods

- Industrial Auxiliary Power Supply, E-metering SMPS

- Consumer Electronics (Chargers, Set-top-boxes and TVs)

#### ON Semiconductor®

www.onsemi.com

PDIP-7 CASE 626A

#### **MARKING DIAGRAM**

A = Plant Code

Y = 1-digit Year Code

W = 1-digit Week Code

WL = 2-digit Die-Run Code

L5x8 = Specific Device Code

x = Device Option (1 or 3)

y = Frequency Option (A or H)

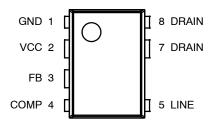

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 25 of this data sheet.

#### PRODUCT INFORMATION & INDICATIVE RECOMMENDED OUTPUT POWER

|                |         | Operating               |                        | Output Power Table (Open Frame) (Notes 1, 2) |                              |                           |                             |

|----------------|---------|-------------------------|------------------------|----------------------------------------------|------------------------------|---------------------------|-----------------------------|

| Part<br>Number | Package | Junction<br>Temperature | Operation<br>Frequency | Current Limit (A)                            | Max. R <sub>DS(ON)</sub> (Ω) | 230 V <sub>AC</sub> ± 15% | 85 ~ 265<br>V <sub>AC</sub> |

| FSL518H        | PDIP-7  | −40 ~ 125°C             | 130 kHz                | 0.46                                         | 8.0                          | 15 W                      | 12 W                        |

| FSL538H        | PDIP-7  | −40 ~ 125°C             | 130 kHz                | 0.66                                         | 4.6                          | 21 W                      | 17 W                        |

| FSL518A        | PDIP-7  | −40 ~ 125°C             | 100 kHz                | 0.61                                         | 8.0                          | 17 W                      | 14 W                        |

| FSL538A        | PDIP-7  | −40 ~ 125°C             | 100 kHz                | 0.86                                         | 4.6                          | 25 W                      | 20 W                        |

- 1. The junction temperature can limit the maximum output power.

- 2. Maximum practical continuous power in an open-frame design at 50°C ambient.

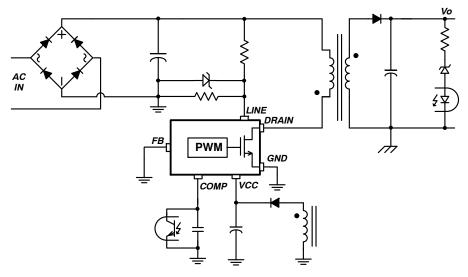

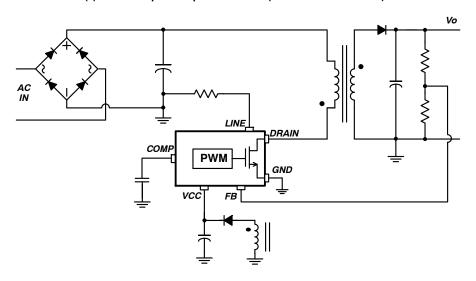

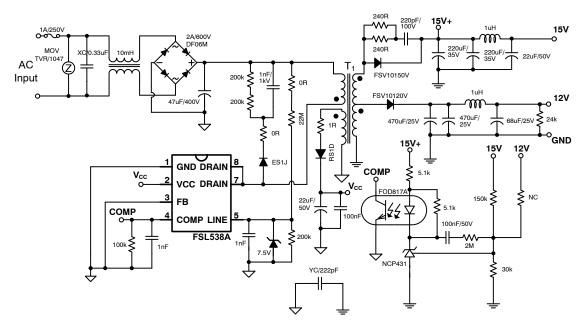

(a) Isolated Opto-coupler Feedback (Enable Line Detection)

(b) Non-isolated Direct Feedback (Disable Line Detection)

Figure 1. Application Schematic - Isolated or Non-isolated Flyback Converter

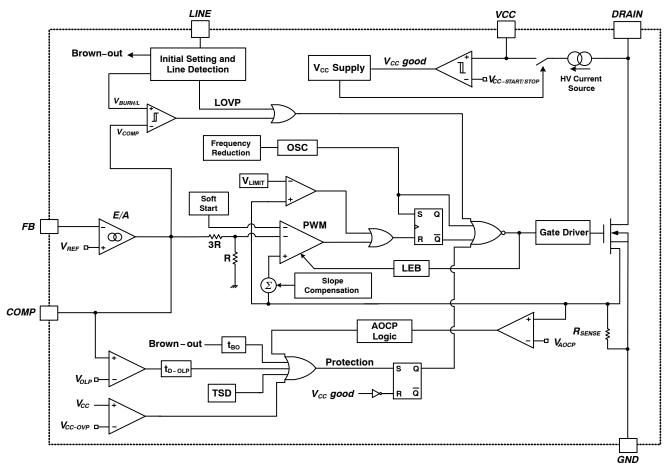

Figure 2. Internal Block Diagram

#### PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name | Pin Function                              | Description                                                                                                                                                                                                                       |

|---------|----------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Ground                                    | SENSEFET source terminal and internal controller ground.                                                                                                                                                                          |

| 2       | VCC      | Power Supply                              | This pin is connected to an external capacitor and provides internal operating current of the IC. It also includes an auto-recovery over-voltage protection.                                                                      |

| 3       | FB       | Feedback                                  | This pin is connected to the input of transconductance amplifier for regulating output voltage of the power converter. If transconductance amplifier is not used, connect FB to GND.                                              |

| 4       | COMP     | Feedback-Loop<br>Compensation             | Control-loop compensation. For opto-coupler feedback, connect COMP to opto coupler directly.                                                                                                                                      |

| 5       | LINE     | Brown in/out, LOVP,<br>Burst-mode Setting | For line detection(Line OVP, Brown in/out), this pin needs to be connected to the high-voltage DC link through voltage divider. And it's also multiple-function pin for burst-mode adjustment.                                    |

| 7,8     | DRAIN    | MOSFET Drain                              | High-voltage power MOSFET drain connection. In addition, during startup and protection mode, the internal high-voltage current source supplies internal bias current and charges the external capacitor connected to the VCC pin. |

#### **MAXIMUM RATINGS**

| Rating                                                                                | Symbol               | Value                   | Unit |

|---------------------------------------------------------------------------------------|----------------------|-------------------------|------|

| DRAIN Pin Voltage                                                                     | V <sub>DS</sub>      | -0.3 to 800             | V    |

| VCC Pin Voltage                                                                       | V <sub>CC</sub>      | -0.3 to 26              | V    |

| Feedback Pin Voltage                                                                  | V <sub>FB</sub>      | -0.3 to 5.0             | V    |

| Compensation Pin Voltage                                                              | V <sub>COMP</sub>    | -0.3 to 5.0             | V    |

| Line-detection Pin Voltage                                                            | V <sub>LINE</sub>    | –0.3 to V <sub>CC</sub> | V    |

| DRAIN Pin Pulsed Current (Note 3)<br>FSL518H/A<br>FSL538H/A                           | I <sub>D-PULSE</sub> | 2.1<br>2.8              | А    |

| Single Pulse Avalanche Energy (Note 4)<br>FSL518H/A<br>FSL538H/A                      | Eas                  | 6.0<br>11.7             | mJ   |

| Total Power Dissipation (PDIP-7)<br>FSL518H/A & FSL538H/A                             | P <sub>D</sub>       | 1.25                    | W    |

| Junction Temperature (Note 5)                                                         | T <sub>J</sub>       | 150                     | °C   |

| Operating Junction Temperature (Note 6)                                               | TJ                   | -40 to +125             | °C   |

| Storage Temperature                                                                   | T <sub>STG</sub>     | -55 to +150             | °C   |

| ESD Capability HBM, JESD22-A114<br>ESD Capability HBM, JESD22-A114 (Except DRAIN pin) |                      | 1000<br>2000            | V    |

| ESD Capability CDM, JESD22-C101                                                       |                      | 1000                    | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. Repetitive peak switching current when the inductive load is assumed: Limited by maximum duty and junction temperature.

- 4. L= 45 mH, starting  $T_J = 25$ °C.

- 5. Although this parameter guarantees IC operation, it does not guarantee all electrical characteristics

- 6. Junction temperature can limit maximum output power of power converter controlled by the device.

#### THERMAL CHARACTERISTICS

| Rating                                                                       | Symbol        | Value | Unit |

|------------------------------------------------------------------------------|---------------|-------|------|

| Thermal Characteristics, PDIP-7 Thermal Resistance, Junction-to-Air (Note 7) |               |       | °C/W |

| FSL518H/A & FSL538H/A                                                        | $R_{	hetaJA}$ | 100   |      |

| Thermal Reference, Junction-to-Lead (Note 7)<br>FSL518H/A & FSL538H/A        | $R_{\psiJL}$  | 18    |      |

<sup>7.</sup> JEDEC recommended environment, JESD51-2, and test board, JESD51-3, with minimum land pattern.

#### **ELECTRICAL CHARACTERISTICS**

$T_J$  = -40 to +125°C and  $V_{CC}$  = 14 V unless otherwise specified.

| Parameter                           | Test Conditions                                                                                                                                       | Symbol              | Min                      | Тур                      | Max                      | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|--------------------------|--------------------------|------|

| SENSEFET Section                    |                                                                                                                                                       |                     |                          |                          |                          |      |

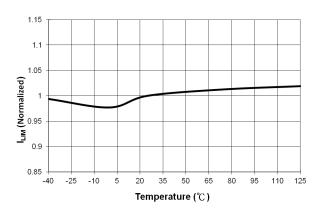

| MOSFET Peak Current Limit           | T <sub>J</sub> = 25°C, Duty = 60%<br>di/dt = 100 mA/µs FSL518H<br>di/dt = 100 mA/µs FSL518A<br>di/dt = 143 mA/µs FSL538H<br>di/dt = 143 mA/µs FSL538A | I <sub>LIM</sub>    | 428<br>560<br>614<br>790 | 460<br>610<br>660<br>860 | 492<br>660<br>706<br>930 | mA   |

| Drain-to-Source On-State Resistance | MOSFET ON, T <sub>J</sub> = 25°C<br>FSL518H/A, I <sub>DRAIN</sub> = 0.46 A<br>FSL538H/A, I <sub>DRAIN</sub> = 0.66 A                                  | R <sub>DS(ON)</sub> |                          | 6.3<br>3.8               | 8.0<br>4.6               | Ω    |

| Output Capacitance (Note 9)         | $V_{DS} = 480 \text{ V}, V_{GS} = 0 \text{ V}, f = 1 \text{ MHz}, \\ T_{J} = 25^{\circ}\text{C} \\ FSL518H/A \\ FSL538H/A$                            | C <sub>OSS</sub>    |                          | 3.8<br>5.0               |                          | pF   |

#### **ELECTRICAL CHARACTERISTICS** (continued)

$T_J = -40 \text{ to } +125^{\circ}\text{C}$  and  $V_{CC} = 14 \text{ V}$  unless otherwise specified.

| Parameter                                                                            | Test Conditions                                                                                                                                 | Symbol                | Min                     | Тур                    | Max                  | Unit |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|------------------------|----------------------|------|

| SENSEFET Section                                                                     |                                                                                                                                                 |                       |                         |                        |                      |      |

| Effective Output Capacitance (Note 9)                                                | $V_{DS} = 0$ to 480 V, $V_{GS} = 0$ V, $T_{J} = 25^{\circ}C$ FSL518H/A FSL538H/A                                                                | C <sub>OSS(eff)</sub> |                         | 31<br>40               |                      | pF   |

| DRAIN Voltage Rise Time (Note 8)                                                     | V <sub>DRAIN</sub> = 40 V to 360 V<br>FSL518H/A, I <sub>DRAIN</sub> = 0.4 A<br>FSL538H/A, I <sub>DRAIN</sub> = 0.6 A                            | t <sub>r</sub>        |                         | 26<br>35               |                      | ns   |

| DRAIN Voltage Fall Time (Note 8)                                                     | V <sub>DRAIN</sub> = 360 V to 40 V<br>FSL518H/A, I <sub>DRAIN</sub> = 0.4 A<br>FSL538H/A, I <sub>DRAIN</sub> = 0.6 A                            | t <sub>f</sub>        |                         | 34<br>30               |                      | ns   |

| Drain to Source Breakdown Voltage                                                    | $V_{GS} = 0 \text{ V}, I_D = 250 \mu\text{A}, T_J = 25^{\circ}\text{C}$                                                                         | BV <sub>DSS</sub>     | 800                     |                        |                      | V    |

| Zero Gate Voltage Drain Current                                                      | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = 0 V, T <sub>J</sub> = 25°C<br>V <sub>DS</sub> = 640 V, V <sub>GS</sub> = 0 V, T <sub>J</sub> = 125°C | I <sub>DSS</sub>      |                         |                        | 25<br>250            | μА   |

| VCC Section                                                                          |                                                                                                                                                 |                       |                         |                        |                      |      |

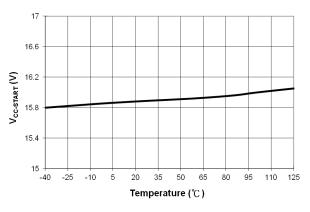

| Controller Turn-on Threshold Voltage                                                 |                                                                                                                                                 | V <sub>CC-START</sub> | 15                      | 16                     | 17                   | ٧    |

| Under-voltage Lockout Threshold<br>Voltage                                           |                                                                                                                                                 | V <sub>CC-STOP</sub>  | 7                       | 8                      | 9                    | ٧    |

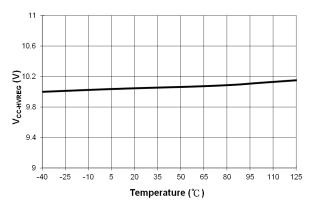

| V <sub>CC</sub> Regulation Voltage                                                   | During Protection, T <sub>J</sub> = 25°C                                                                                                        | V <sub>CC-HVREG</sub> | 9                       | 10                     | 11                   | V    |

| Restart Time in Protection Mode (Note 9)                                             |                                                                                                                                                 | t <sub>AR</sub>       |                         | 800                    |                      | ms   |

| Soft-start Time                                                                      |                                                                                                                                                 | t <sub>SS</sub>       | 7                       | 10                     | 13                   | ms   |

| Oscillation Section                                                                  |                                                                                                                                                 |                       |                         |                        |                      |      |

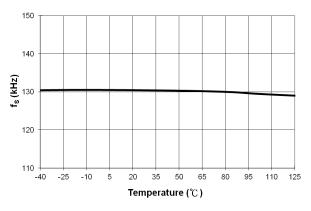

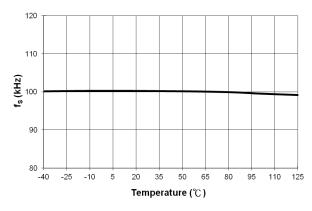

| Switching Frequency                                                                  | V <sub>CC</sub> = 14 V, V <sub>COMP</sub> = 3.6 V, T <sub>J</sub> = 25°C<br>FSL5x8H<br>FSL5x8A                                                  | f <sub>S</sub>        | 122<br>94               | 130<br>100             | 138<br>106           | kHz  |

| Switching Frequency Variation                                                        | T <sub>J</sub> = -40 ~ 125°C                                                                                                                    | $\Delta f_{S}$        |                         | ±5                     | ±10                  | %    |

| Frequency Modulation Range                                                           | V <sub>COMP</sub> = 3.6 V<br>FSL5x8H<br>FSL5x8A                                                                                                 | f <sub>M</sub>        |                         | ±6.2<br>±4.8           |                      | kHz  |

| Frequency Modulation Period (Note 9)                                                 | V <sub>COMP</sub> = 3.6 V                                                                                                                       | T <sub>FM</sub>       |                         | 3.2                    |                      | ms   |

| Green-mode Entry Frequency                                                           | V <sub>COMP</sub> = 1.4 V<br>FSL5x8H<br>FSL5x8A                                                                                                 | f <sub>N</sub>        |                         | 115<br>89              |                      | kHz  |

| Green-mode Ending Frequency                                                          | V <sub>BURL</sub> = 0.4 V                                                                                                                       | f <sub>G</sub>        | 22                      | 25                     | 28                   | kHz  |

| Frequency-limiting Voltage                                                           |                                                                                                                                                 | V <sub>COMP-S</sub>   |                         | V <sub>OLP</sub>       |                      | V    |

| Green-mode Entry COMP Voltage (Note 9)                                               |                                                                                                                                                 | V <sub>COMP-N</sub>   |                         | 1.4                    |                      | V    |

| Green-mode Ending COMP Voltage                                                       |                                                                                                                                                 | V <sub>COMP-G</sub>   |                         | V <sub>BURL</sub>      |                      | V    |

| Burst-Mode Section                                                                   |                                                                                                                                                 |                       |                         |                        |                      |      |

| COMP Threshold Voltage for Entering<br>Burst-mode when Line Detection is<br>Enabled  | VLINE IN VLINE-SETO during tSET VLINE IN VLINE-SET1 during tSET VLINE IN VLINE-SET2 during tSET                                                 | V <sub>BURL</sub>     | 0.35<br>0.45<br>0.55    | 0.4<br>0.5<br>0.6      | 0.45<br>0.55<br>0.65 | V    |

| COMP Threshold Voltage for Entering<br>Burst-mode when Line Detection is<br>Disabled | 0.9 V < V <sub>LINE</sub> < 1.2 V<br>1.2 V < V <sub>LINE</sub> < 3.6 V                                                                          | V <sub>BURL</sub>     | 0.4<br>Av-burst × Vline |                        | LINE                 | V    |

| COMP Threshold Voltage for Leaving<br>Burst-mode                                     |                                                                                                                                                 | V <sub>BURH</sub>     | \                       | / <sub>BURL</sub> + 0. | .1                   | ٧    |

|                                                                                      | ·                                                                                                                                               |                       |                         |                        |                      |      |

#### **ELECTRICAL CHARACTERISTICS** (continued)

$T_J = -40 \text{ to } +125^{\circ}\text{C}$  and  $V_{CC} = 14 \text{ V}$  unless otherwise specified.

| Parameter                                                                                       | Test Conditions                                                                    | Symbol                      | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------|------|------|------|------|

| Control Section                                                                                 |                                                                                    |                             |      |      |      |      |

| Maximum Duty Ratio                                                                              | V <sub>COMP</sub> = 3.6 V                                                          | D <sub>MAX</sub>            | 68   | 75   | 82   | %    |

| COMP Output High Voltage                                                                        | COMP-pin Open                                                                      | V <sub>COMP</sub> -<br>OPEN |      | 5    |      | V    |

| COMP Sourcing Current                                                                           |                                                                                    | I <sub>COMP</sub>           | 70   | 100  | 135  | μΑ   |

| Transconductance of Internal Error<br>Amplifier                                                 |                                                                                    | G <sub>M</sub>              |      | 300  |      | μS   |

| Current-sourcing capability of Internal Error Amplifier                                         | V <sub>FB</sub> = V <sub>REF</sub> - 1 V                                           | I <sub>GM-SOURCE</sub>      | 55   | 90   | 125  | μА   |

| Current-sinking capability of Internal<br>Error Amplifier                                       | V <sub>FB</sub> = V <sub>REF</sub> + 1 V                                           | I <sub>GM-SINK</sub>        | -55  | -90  | -125 | μА   |

| Reference Voltage to Regulate FB-pin Voltage                                                    |                                                                                    | V <sub>REF</sub>            | 2.45 | 2.5  | 2.55 | ٧    |

| Leading-edge Blanking Time of Internal<br>SENSEFET Current Signal (Note 9)                      |                                                                                    | t <sub>LEB</sub>            |      | 250  |      | ns   |

| Propagation Delay of Turning-off Power MOSFET (Note 9)                                          |                                                                                    | t <sub>PD</sub>             |      | 100  |      | ns   |

| LINE Section                                                                                    |                                                                                    |                             |      |      |      |      |

| Threshold Voltage for Line Detection<br>Enable                                                  | V <sub>LINE</sub> > V <sub>LINE-DET</sub>                                          | V <sub>LINE-DET</sub>       | 0.15 |      |      | V    |

| Threshold Voltage for Line Detection Disable                                                    | V <sub>LINE</sub> < V <sub>LINE</sub> -ADJ                                         | V <sub>LINE-ADJ</sub>       |      |      | 0.05 | V    |

| Burst-mode Level Setting Time when Line<br>Detection is Enabled (Note 9)                        |                                                                                    | t <sub>SET</sub>            |      | 100  |      | μs   |

| Sourcing Current for Detecting Burst<br>Setting Zener Voltage in t <sub>SET</sub>               | During t <sub>SET</sub> , V <sub>CC</sub> = 15 V, V <sub>LINE</sub> = 10 V         | I <sub>SET</sub>            | 1.6  | 2.7  | 3.8  | mA   |

| Burst-mode Level 0 Set up Voltage                                                               | During t <sub>SET</sub>                                                            | V <sub>LINE-SET0</sub>      | 12.4 |      |      | V    |

| Burst-mode Level 1 Set up Voltage                                                               | During t <sub>SET</sub>                                                            | V <sub>LINE-SET1</sub>      | 9.3  |      | 10.6 | V    |

| Burst-mode Level 2 Set up Voltage                                                               | During t <sub>SET</sub>                                                            | V <sub>LINE-SET2</sub>      |      |      | 7.9  | V    |

| Sourcing Current for Setting Burst-mode<br>Level when Line Detection is Disabled                | V <sub>LINE</sub> = 0 V before V <sub>CC</sub> is charged to V <sub>CC-START</sub> | I <sub>BURST</sub>          | 9.4  | 10   | 10.6 | μА   |

| LINE-pin Voltage to Burst-mode Level<br>Attenuation when Line Detection is<br>Disabled (Note 9) |                                                                                    | A <sub>V-BURST</sub>        |      | 1/3  |      | V/V  |

| Protections: Over-Voltage Protection (OV                                                        | /P)                                                                                |                             |      |      |      |      |

| Over-Voltage Protection Threshold Voltage for VCC-pin                                           |                                                                                    | V <sub>CC-OVP</sub>         | 23.0 | 24.5 | 26.0 | V    |

| Delay time for OVP (Note 9)                                                                     |                                                                                    | t <sub>D-OVP</sub>          |      | 6.0  |      | μs   |

| Protections: Over-Load Protection (OLP)                                                         |                                                                                    | •                           |      | •    | •    |      |

| OLP-Triggering Threshold Voltage on COMP-pin                                                    |                                                                                    | V <sub>OLP</sub>            | 3.3  | 3.6  | 3.9  | ٧    |

| Delay Time for OLP                                                                              | V <sub>COMP</sub> > V <sub>OLP</sub> after Soft-start Time                         | t <sub>D-OLP</sub>          | 30   | 60   | 90   | ms   |

|                                                                                                 | •                                                                                  | •                           |      | •    | •    | •    |

#### **ELECTRICAL CHARACTERISTICS** (continued)

$T_J$  = -40 to  $+125^{\circ}C$  and  $V_{CC}$  = 14 V unless otherwise specified.

| Parameter                                                                                         | Test Conditions                                                                                                | Symbol                            | Min  | Тур              | Max  | Unit  |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------------------|------|-------|

| Abnormal Over-Current Protection (AOC                                                             | P)                                                                                                             |                                   |      |                  |      |       |

| AOCP Monitoring duration after t <sub>LEB</sub> (Note 9)                                          |                                                                                                                | t <sub>AOCP</sub>                 |      | 150              |      | ns    |

| Threshold Drain Current for Triggering AOCP (Note 9)                                              |                                                                                                                | I <sub>AOCP</sub>                 |      | I <sub>LIM</sub> |      | mA    |

| Number of pulse for AOCP to skip switching operation for N <sub>AOCP-HALT</sub> times (Note 9)    |                                                                                                                | N <sub>AOCP-TRIG</sub>            |      | 2                |      | times |

| Number of skipped pulses after N <sub>AOCP-TRIG</sub> is satisfied (Note 9)                       |                                                                                                                | N <sub>AOCP-HALT</sub>            |      | 7                |      | times |

| Number of Pulse for Satisfying N <sub>AOCP-TRIG</sub> to Trigger Auto-restart Protection (Note 9) |                                                                                                                | N <sub>AOCP</sub> -<br>COUNT      |      | 3                |      | times |

| Protections: Line Detection (BI, BO, LOV                                                          | P)                                                                                                             | ·                                 |      |                  |      |       |

| Brown-out (BO) Threshold Voltage on LINE-pin                                                      |                                                                                                                | V <sub>LINE-BO</sub>              | 0.80 | 0.85             | 0.90 | V     |

| Brown-in (BI) Threshold Voltage on LINE-pin                                                       |                                                                                                                | V <sub>LINE-BI</sub>              | 0.95 | 1                | 1.05 | V     |

| Hysteresis between BI and BO                                                                      | V <sub>LINE-BI</sub> – V <sub>LINE-BO</sub>                                                                    | ΔV <sub>LINE</sub> -<br>BIBO      | 0.09 | 0.15             | 0.21 | V     |

| Delay Time for Brown-out (Note 9)                                                                 |                                                                                                                | t <sub>BO</sub>                   |      | 100              |      | ms    |

| Threshold Voltage for Line Over-Voltage Protection (LOVP)                                         |                                                                                                                | V <sub>LINE-OVP</sub>             | 4.3  | 4.5              | 4.7  | V     |

| Recovering Level for LOVP                                                                         |                                                                                                                | V <sub>LINE-OVP-</sub><br>RECOVER | 4.2  | 4.4              | 4.6  | V     |

| Hysteresis Voltage for LOVP                                                                       | V <sub>LINE-OVP</sub> - V <sub>LINE-OVP-RECOVER</sub>                                                          | $\Delta V_{LINE-OVP}$             | 0.05 | 0.1              | 0.15 | V     |

| Delay Time for LOVP (Note 9)                                                                      |                                                                                                                | t <sub>LINE-OVP</sub>             |      | 2                |      | μs    |

| Protections: Thermal Shutdown                                                                     |                                                                                                                |                                   |      |                  |      |       |

| Junction Temperature to Trigger Thermal<br>Shutdown (Note 9)                                      |                                                                                                                | T <sub>SD</sub>                   |      | 147              |      | °C    |

| Junction Temperature for Resuming from Thermal Shutdown (Note 9)                                  |                                                                                                                | T <sub>RECOVER</sub>              |      | 95               |      | °C    |

| Total Device Section                                                                              |                                                                                                                |                                   |      |                  |      |       |

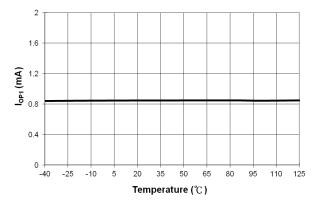

| Operating Supply Current (Control Part in Burst-mode)                                             | $V_{COMP}$ = 0 V, $V_{DRAIN}$ = 12 V, $R_{DRAIN}$ = 500 $\Omega$                                               | I <sub>OP1</sub>                  |      | 0.9              | 1.2  | mA    |

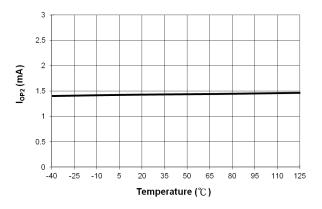

| Operating Supply Current                                                                          | V <sub>COMP</sub> = 3.2 V, V <sub>DRAIN</sub> = 12 V                                                           | I <sub>OP2</sub>                  |      | 1.7              | 2.0  | mA    |

| VCC-pin current at startup condition                                                              | V <sub>CC</sub> = 14.9 V, V <sub>COMP</sub> = 3.6 V<br>(Before V <sub>CC</sub> Reaches V <sub>CC-START</sub> ) | ISTART                            |      | 170              | 205  | μА    |

| Startup Charging Current (JFET saturation current)                                                | V <sub>CC</sub> = 0 V, V <sub>DRAIN</sub> = 40 V                                                               | I <sub>CH</sub>                   | 1.2  | 4                |      | mA    |

| Minimum DRAIN-pin Voltage to Start<br>Operation (Note 10)                                         | V <sub>CC</sub> = V <sub>COMP</sub> = 0 V                                                                      | V <sub>START</sub>                |      |                  | 40   | V     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Evaluated in the typical flyback application board, T<sub>A</sub> = 25°C

9. This parameter is not tested in production, but verified by design/characterization.

<sup>10.</sup> It is guaranteed that  $I_{CH}$  can charge  $V_{CC}$  up to  $V_{CC-START}$  if DRAIN-pin voltage is higher than  $V_{START}$ .

Figure 3. V<sub>CC-START</sub> vs. Temperature

Figure 5. V<sub>CC-HVREG</sub> vs. Temperature

Figure 7. FSL5x8H  $I_{OP1}$  vs. Temperature

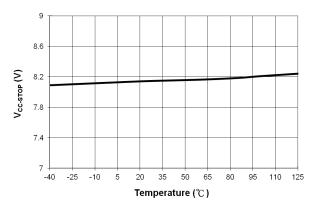

Figure 4. V<sub>CC-STOP</sub> vs. Temperature

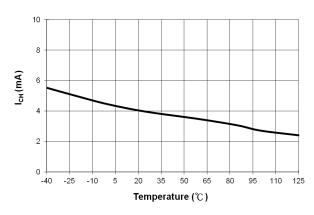

Figure 6. I<sub>CH</sub> vs. Temperature

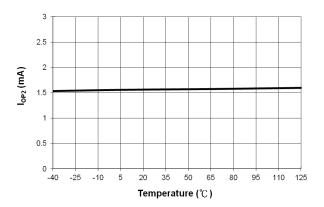

Figure 8. FSL5x8H  $I_{OP2}$  vs. Temperature

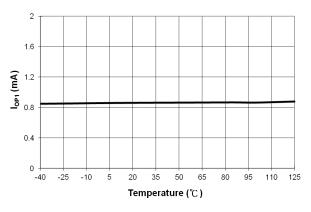

Figure 9. FSL5x8A I<sub>OP1</sub> vs. Temperature

Figure 11. FSL5x8H f<sub>s</sub> vs. Temperature

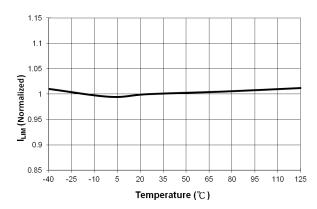

Figure 13. FSL518H  $I_{LIM}$  (Normalized to 25°C) vs. Temperature

Figure 10. FSL5x8A I<sub>OP2</sub> vs. Temperature

Figure 12. FSL5x8A f<sub>s</sub> vs. Temperature

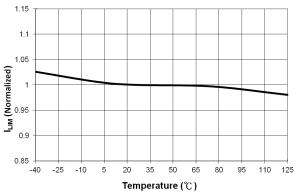

Figure 14. FSL518A  $I_{LIM}$  (Normalized to 25°C) vs. Temperature

#### **TYPICAL CHARACTERISTICS**

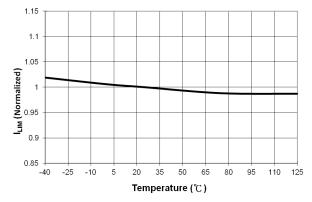

Figure 15. FSL538H  $I_{LIM}$  (Normalized to 25°C) vs. Temperature

130

120

Icomp (µA)

90

80

-40

Figure 17. I<sub>COMP</sub> vs. Temperature

35 50 65

Temperature (°C)

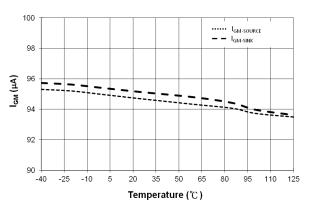

Figure 19. I<sub>GM</sub> vs. Temperature

Figure 16. FSL538A  $I_{LIM}$  (Normalized to 25°C) vs. Temperature

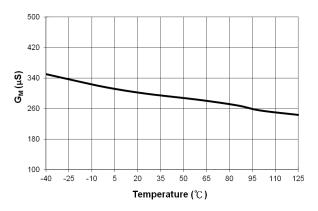

Figure 18.  $G_{\rm M}$  vs. Temperature

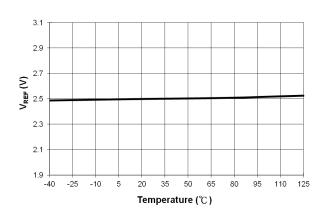

Figure 20. V<sub>REF</sub> vs. Temperature

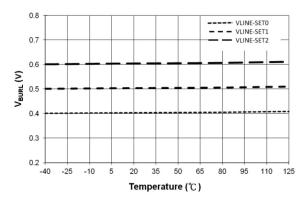

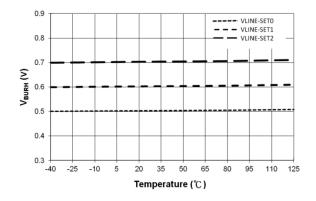

Figure 21. V<sub>BURL</sub> vs. Temperature

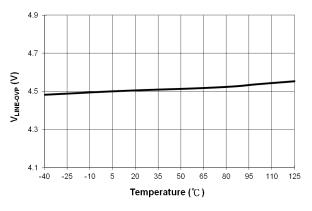

Figure 23. V<sub>LINE-OVP</sub> vs. Temperature

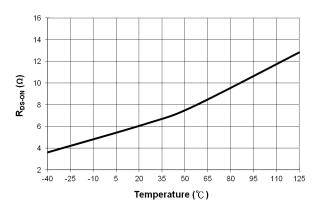

Figure 25. FSL518H/A  $R_{DS(ON)}$  vs. Temperature

Figure 22.  $V_{BURH}$  vs. Temperature

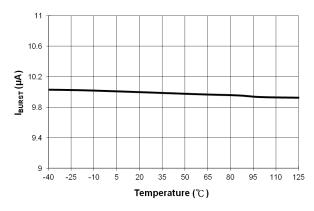

Figure 24. I<sub>BURST</sub> vs. Temperature

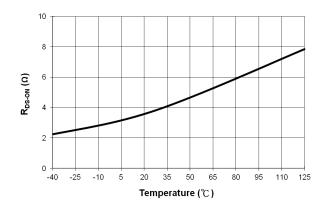

Figure 26. FSL538H/A  $R_{DS(ON)}$  vs. Temperature

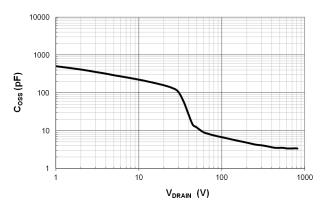

Figure 27. FSL518H/A C<sub>OSS</sub> vs. V<sub>DRAIN</sub>

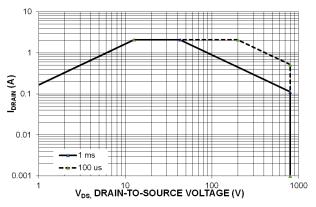

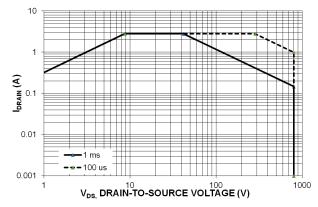

Figure 29. FSL518H/A Safe Operating Range

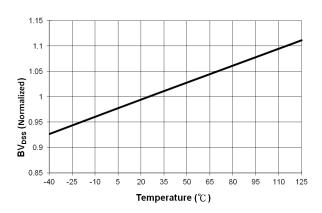

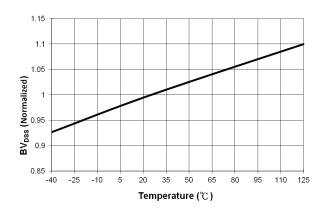

Figure 31. FSL518H/A  $BV_{DSS}$  vs. Temperature

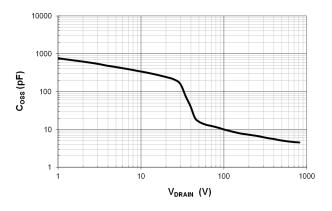

Figure 28. FSL538H/A C<sub>OSS</sub> vs. V<sub>DRAIN</sub>

Figure 30. FSL538H/A Safe Operating Range

Figure 32. FSL538H/A  $BV_{DSS}$  vs. Temperature

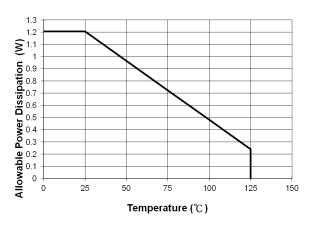

Figure 33. FSL5x8H/A Power Dissipation vs. Temperature

#### APPLICATION INFORMATION

# HV Current Source for $V_{CC}$ Start up and $V_{CC}$ Regulation

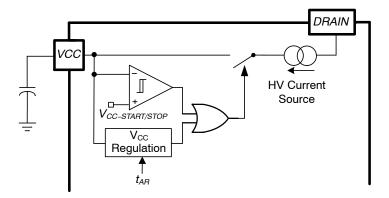

The HV current source utilizes voltage on DRAIN pin to charge capacitor on VCC pin. This current source is activated during start-up and provides operating current when  $V_{CC}$  is lower than  $V_{CC\text{-HVREG}}.$  Thanks to  $V_{CC}$  start-up function, no external start-up circuitry is needed. The HV current source is disabled when  $V_{CC}$  voltage is charged to  $V_{CC\text{-START}}.$

$V_{CC}$  regulation also helps avoiding start-up failure during soft-start and keeps FSL5x8 operating to count auto-restart delay time ( $t_{AR}$ ) in protection mode, as illustrated in Figure 34. It also enables the use of smaller capacitance for  $V_{CC}$  biasing. The  $V_{CC}$  regulation is not functional when the external bias is higher than  $V_{CC-HVREG}$ .

Figure 34. V<sub>CC</sub> Start Up and V<sub>CC</sub> Regulation

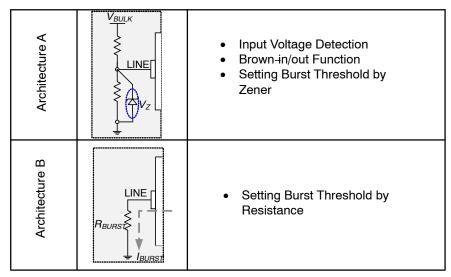

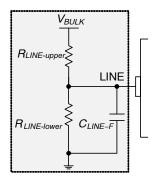

# Initial Setting for Line Detection and Adjusting Burst-mode Operation

LINE pin is used for both input-voltage detection and burst-mode setting. When a voltage divider is connected between bulk capacitor and LINE pin, a Zener diode connected to LINE pin will allow to set level of burst-mode operation. If there is no voltage divider, the line-detection function is disabled and burst-mode operation level is set linearly by simply connecting a resistor between LINE pin and GND pin. In order to avoid interference from switching

noise, connecting a ceramic capacitor to LINE pin is recommended.

When line detection is enabled, voltage on LINE pin is monitored to offer brown-in (BI), brown-out (BO) and line over-voltage protections (LOVP).

With  $I_{BURST}$ ,  $V_{LINE}$  reflects resistance of the external resistor. FSL5x8 adjusts burst-mode operation threshold based on real-time  $V_{LINE}$  level. Please refer to burst threshold setting table for LINE pin configuration and settings.

Figure 35. Architecture of LINE-pin Setting

#### **BURST THRESHOLD SETTING TABLE**

|                | Line Detection Enable/Disable | V <sub>LINE</sub> (V)                                                      | V <sub>BURH</sub> /V <sub>BURL</sub> (V)                                                                                                                |  |

|----------------|-------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architecture A | 12.4 V < V <sub>Z</sub>       |                                                                            | 0.5 / 0.4                                                                                                                                               |  |

| Architecture A | Enable                        | 9.3 V < V <sub>Z</sub> < 10.6 V                                            | 0.6 / 0.5                                                                                                                                               |  |

|                |                               | V <sub>Z</sub> < 7.9 V                                                     | 0.7 / 0.6                                                                                                                                               |  |

| Aughitesture D | Disable                       | $0.9 \text{ V} < I_{BURST} \times R_{BURST} < 1.2 \text{ V}$               | 0.5 / 0.4                                                                                                                                               |  |

| Architecture B | Disable                       | $1.2 \text{ V} < I_{\text{BURST}} \times R_{\text{BURST}} < 3.6 \text{ V}$ | $\begin{aligned} A_{V\text{-BURST}} \times (I_{BURST} \times R_{BURST}) + 0.1 \\ /A_{V\text{-BURST}} \times (I_{BURST} \times R_{BURST}) \end{aligned}$ |  |

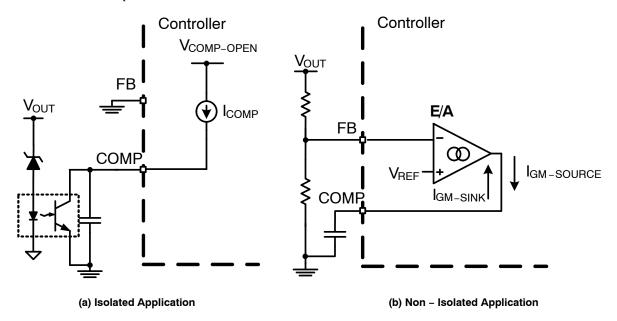

# Initial Setting for Configuration of Feedback Regulation

Being simultaneous to the initial setting of LINE-pin functions, configuration of feedback regulation is also decided based on peripheral circuitry to FB pin. If a voltage divider is connected to FB pin, the IC will regulate output voltage by referring to the reference voltage,  $V_{REF}$  of transconductance error amplifier.

In the case that external error amplifier is used for output regulation, simply connect FB pin to GND pin. The external output regulation circuitry will sinks  $I_{COMP}$  (100  $\mu A$ ) to control PWM duty cycle for accuracy output regulation.

Figure 36. Isolated vs. Non-Isolated Application

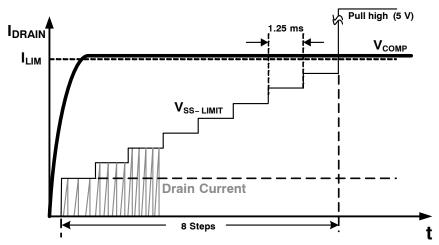

#### **Advanced Soft-Start Operation**

After V<sub>CC</sub> is charged to V<sub>CC-START</sub> and all settings about LINE-pin and FB-pin functions are done, switching operation can be initiated with a soft-start period. For soft-start period of 10 ms, both drain current and switching

frequency limits are settled to target value gradually as shown in Fig. 37. Thus, output voltage will be increased smoothly and the voltage stresses in switching devices can be minimized.

Figure 37. Soft-start Operation

#### **Main Control Frequency Reduction**

Operating frequency of switching operation is synchronized with COMP-pin voltage,  $V_{\rm COMP}$  When  $V_{\rm COMP}$  drops, operating frequency will also decrease. This helps reducing switching losses and thus improve light-load efficiency operation. The operating frequency will not be decreased below 22-kHz so acoustic noise can be avoided.

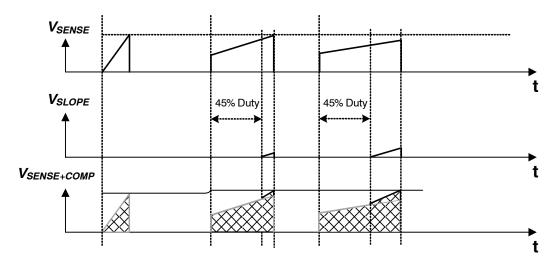

#### **PWM Control**

The FSL5x8 operates with peak-current mode to regulate output voltage. The duty cycle of PWM is determined by

comparing drain peak current and  $V_{\rm COMP}$ . The  $V_{\rm COMP}$  can be controlled by either the input signal of error amplifier or the signal delivered via opto-coupler and feedback loop for output regulation.

#### **Slope Compensation**

Built-in slope compensation is added into the PWM procedure when duty cycle is higher than 45%. It helps to avoid sub-harmonic oscillation of peak-current control.

Figure 38. Slope Compensation

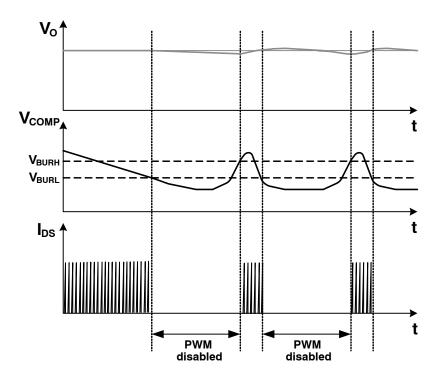

#### **Burst-mode Operation**

As loading of the power converter decreases,  $V_{COMP}$  decreases, thus reducing switching frequency of the oscillator. When minimum operating frequency is reached, to further reduce delivered output power, the device goes

into burst–mode. In burst–mode, switching operation is halted when  $V_{COMP}$  is lower than  $V_{BURL}$  and resumed when  $V_{COMP}$  is higher than  $V_{BURH}$ . By skipping un-needed switching cycles, the FSL5x8 drastically reduced the power wasted during light load conditions.

Figure 39. Burst-mode Behavior

$V_{BURL}$  and  $V_{BURH}$  can be adjusted LINE-pin voltage detected. It is provided for tuning light load efficiency and acoustic noise. By adjusting  $V_{BURL}$ , minimum peak value of drain current of each switching cycle is adjusted as described in Equation 1.

$$I_{\text{DRAIN.PEAK.BURL}} = \frac{V_{\text{BURL}}}{4 \cdot 0.6} \cdot I_{\text{LIM}}$$

(eq. 1)

#### **Line Compensation**

Propagation delay in turning off power MOSFET makes drain current exceed current limit by an amount that related to slope of drain current. The device adjusts its internal current-limit reference voltage according to duty cycle to compensate the effect of propagation delay. As a result, the delivered output power is kept under control across different input voltage conditions.

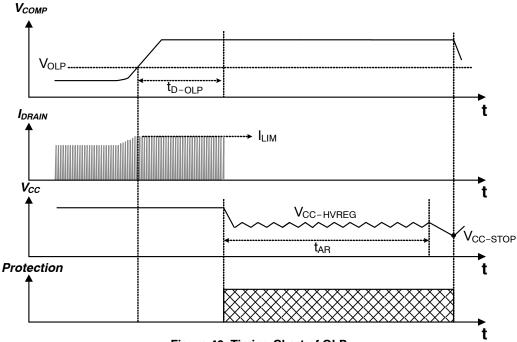

# Protections Over Load Protection (OLP)

$V_{COMP}$  will be pulled higher than  $V_{OLP}$  when drain current hits current limit and switching frequency operates at its highest range. If the condition continues for  $t_{D\text{-}OLP}$  OLP will be triggered and switching operation is stopped as shown in Fig. 40.

The figure also shows typical protection mode behavior of the IC. The operation current is supplied by HV current source for  $t_{AR}$  that can extend the restart period to reduce average power dissipation when fault is still present. After  $t_{AR}$ ,  $V_{CC}$  drops to  $V_{CC\text{-STOP}}$  to reset protective operation and then, controller will be restarted.

Figure 40. Timing Chart of OLP

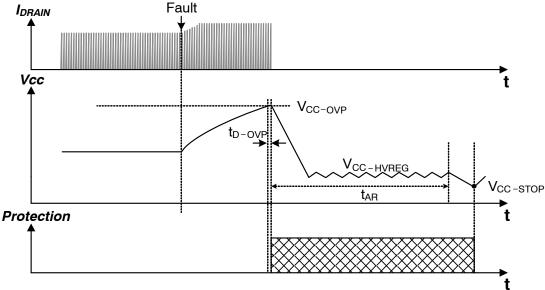

#### Over Voltage Protection (OVP)

A malfunction of voltage-feedback circuitry for output regulation in power converter could result in excessive energy delivered to output. In this condition, both output voltage and  $V_{\rm CC}$  can be increased by unstable operation, and

OVP will be triggered after delay time  $t_{D\text{-}OVP}$  when  $V_{CC}$  rises above  $V_{CC\text{-}OVP}$

Figure 41. Timing Chart of OVP

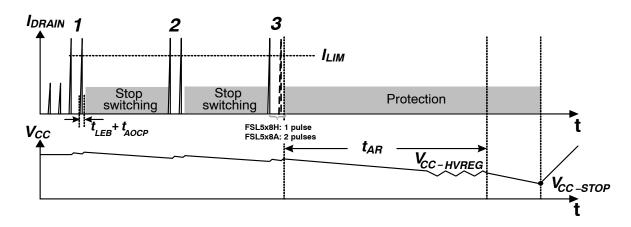

#### **Abnormal Over-Current Protection (AOCP)**

When the secondary-side rectifier diodes or the transformer windings are shorted, a steep drain current with extremely high di/dt will flow through the MOSFET during the minimum turn-on time. Under this condition, each switching cycle generates very high current stress on power MOSFET. The controller monitors drain current within a

limited leading-edge time duration  $t_{LEB} + t_{AOCP}$  of each switching cycle. If drain current exceeds current limit for a few consecutive switching cycles,  $N_{AOCP\text{-}TRIG}$ , switching will be stopped for number of pulses,  $N_{AOCP\text{-}HALT}$ . If the fault condition is met for three times,  $N_{AOCP\text{-}COUNT}$ , the controller goes into protection mode as shown in Fig. 42.

Figure 42. Timing Chart of AOCP

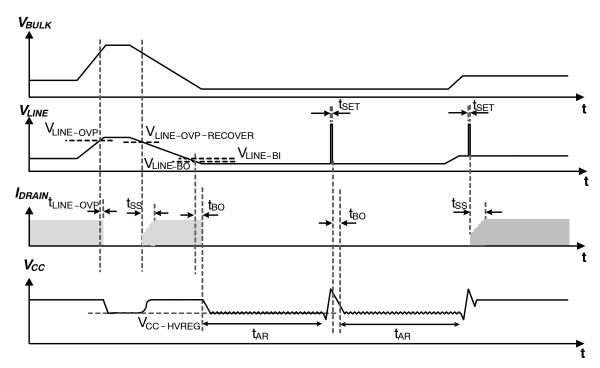

# Brown-in, Brown-out (BI/BO) and Line Over-Voltage Protection (LOVP)

When a voltage divider is connected between LINE pin and input bulk capacitor, line-detection function is enabled and  $V_{LINE}$  reflects peak of AC input voltage. If  $V_{LINE}$  is below  $V_{LINE-BI}$  after initial setting, switching operation will not be initiated until  $V_{LINE}$  reaches  $V_{LINE-BI}$ . If  $V_{LINE}$  is

lower than  $V_{LINE-BO}$  for  $t_{BO}$  during normal operation, brown-out will be triggered and the controller will go into protection mode. If  $V_{LINE}$  is higher than  $V_{LINE-OVP}$ , switching operation is halted until  $V_{LINE}$  drops down below  $V_{LINE-OVP-RECOVER}$ . Both recovering from LOVP or after BI, the controller performs a soft start sequence.

Figure 43. LOVP, Brown-out and Brown-in Behavior

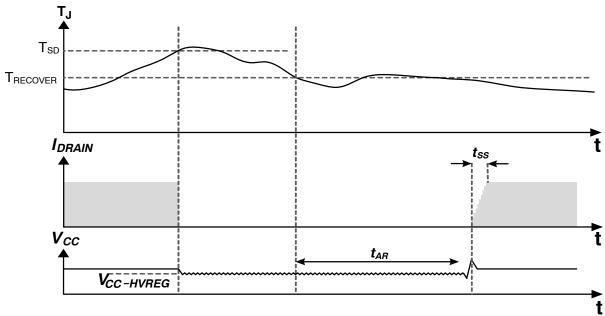

#### Thermal Shutdown (TSD)

Since SENSEFET and controller are integrated in the same package, it is easier for the controller to detect temperature inside the package. When junction temperature exceeds shut-down temperature,  $T_{SD}$ , thermal shutdown is activated. The controller will go into protection mode after thermal shutdown. If temperature is not lower than  $T_{RECOVER}$ , switching operation will not be resumed.

#### **DESIGN CONSIDERATIONS**

#### **Peripheral Components**

While designing flyback converters using FSL5x8H/A, there are some design considerations on selecting value and rating of components and PCB (Printed Circuit Board) layout as the following.

#### • Input/Output Capacitor

It is typical to select the input capacitor as  $2{\sim}3~\mu F$  per watt of peak input power for universal input range (85–265  $V_{RMS}$ ) and 1  $\mu F$  per watt of peak input power for European high input voltage range (195–265  $V_{RMS}$ ).

The minimum DC link voltage is obtained as:

$$V_{DC_{min}} = \sqrt{2 \cdot \left(V_{line_{min}}\right)^2 - \frac{P_{in} \cdot \left(1 - D_{ch}\right)}{f_L \cdot C_{DC}}}, \quad (eq. 2)$$

where  $D_{ch}$  is the DC link capacitor charging duty ratio which is typically about 0.2.  $f_L$  is line voltage frequency.

Considering the output voltage ripple, capacitance at the output terminal can be determined as the following. For better voltage ripple at output terminal, low ESR (Effective Series Resistance) type capacitor is recommended.

$$C_{OUT} = \frac{0.25 \cdot I_{OUT}}{V_{OUT-ripple} \cdot f_{min}}, \qquad \text{(eq. 3)}$$

where  $I_{OUT}$  is a max output load current,  $V_{OUT\text{-}ripple}$  is deviation of a ripple voltage and  $f_{min}$  should minimum frequency between operating frequency deviation.

#### • V<sub>CC</sub> Capacitance

FSL5x8 includes HV start-up circuit providing startup current, which determine startup time. It can be calculated with  $I_{CH}$  and  $V_{CC}$  capacitance. The typical value of  $V_{CC}$  capacitor is selected in a range of 10 to 47  $\mu F$ . It is recommended that  $V_{CC}$  capacitor and FSL5x8 should be placed as close as possible to reject noise decoupling.

$$Start-up Time = \frac{C_{VCC} \cdot V_{CC-START}}{I_{CH}}, \qquad \text{(eq. 4)}$$

#### • Consideration on Designing BI/BO/LOVP

Line input voltage can be detected for brown-in (BI), brown-out (BO) and input line over-voltage protection (LOVP) by connecting LINE pin with dividing resisters linking to input bulk capacitor. Each level of BI and LOVP can be determined as following. Meanwhile,  $C_{LINE-F}$  should be choosen considering some noises on the line induced by switching of the main switch and etc. It is typical to select  $3\sim5$  times of time constant higher than switching frequency.

Figure 45. LINE Pin Settle for BI/BO/LOVP

$$\begin{aligned} & \text{Brown-in AC Voltage} = \\ & V_{\text{LINE-BI}} \times \frac{R_{\text{LINE-upper}} + R_{\text{LINE-lower}}}{R_{\text{LINE-lower}}} \times \frac{1}{\sqrt{2}} \end{aligned} \end{aligned} \tag{eq. 5}$$

$$& \text{Line OVP AC Voltage} = \\ & V_{\text{LINE-OVP}} \times \frac{R_{\text{LINE-upper}} + R_{\text{LINE-lower}}}{R_{\text{LINE-lower}}} \times \frac{1}{\sqrt{2}} \end{aligned} \tag{eq. 6}$$

$$& C_{\text{LINE-F}} = \frac{3}{\left(R_{\text{LINE-upper}} / / R_{\text{LINE-lower}}\right) \cdot f_{\text{SW}}} \end{aligned}$$

#### <u>Selecting FB/COMP and Consideration when One of</u> <u>Both is Selected</u>

For non-isolated converters, connects the output voltage divider to FB pin. For isolated converters, FB pin should be connected to GND, and the external feedback circuit should connect to COMP as well.

#### • Preventing Audible Noise

Even though the switching frequency of the FSL5x8 is above the range of human hearing, audible noise can be generated during transient or burst operation. In most flyback converters, the major noise sources are transformers and capacitors. Transformers produce audible noise, since they contain many physically movable elements, such as coils, isolation tapes and bobbins. The most effective way to reduce the audible noise in the transformer is to remove the possibility of physical movement of the transformer elements by using adhesive material or by varnishing.

Ceramic capacitors can also produce audible noise, because of their piezoelectric characteristics. By replacing the ceramic capacitor with a film capacitor, the audible noise can be reduced. Another way to lower audible noise is to reduce the snubber capacitor value,

which decreases the pulse current that charges the capacitor every time the FSL5x8 resumes switching operation in burst-mode.

For more information, please refer to AN-4148.

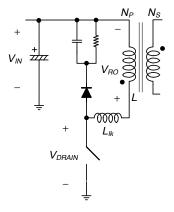

#### Maximum Duty and Reflected Output Voltage

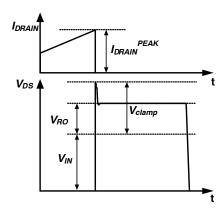

When MOSFET in FSL5x8 is turned off, the input voltage together with the reflected output voltage ( $V_{RO}$ ) on primary winding of the transformer are imposed on MOSFET.

$$V_{DRAIN_{max}} = \sqrt{2} \cdot V_{line_{max}} + V_{RO}$$

(eq. 8)

$V_{linemax}$  is maximum ac-input voltage in r.m.s. value.  $V_{RO}$  is a function of maximum duty ( $D_{max}$ ) and minimum DC-link voltage.

$$V_{RO} = \frac{D_{max}}{1 - D_{max}} \cdot V_{DC_{min}}$$

(eq. 9)

The designed  $D_{max}$  should not exceed FSL5x8's maximum duty raio specification,  $D_{MAX}$ . It is typical to have 70% of de-rating on  $V_{DRAINmax}$  according to MOSFET's breakdown voltage. With 800 V of breakdown voltage in FSL5x8, more room are created to target higher  $D_{max}$ .

#### Transformer Design Considerations

When  $D_{max}$  is assigned, turn ratio of the transformer has been decided.

$$n = \frac{N_P}{N_S} = \frac{V_{RO}}{V_{OUT} + V_F},$$

(eq. 10)

where  $N_P$  and  $N_S$  stands for primary and secondary windings' turn ratio of the transformer,  $V_{OUT}$  stands for output voltage, and  $V_F$  stands for forward voltage of rectifying diode connecting to the secondary winding.

Inductance  $(L_m)$  of the primary winding can be obtained from input power  $(P_{in})$  and switching frequency  $(f_{sw})$ , with ripple factor  $(K_{RF})$  left to be decided.  $K_{RF} \ge 1$  results in lower inductance and discontinuous-conduction-mode (DCM) design, which tend to have smaller switching loss.  $K_{RF} < 1$  results in a continuous-conduction-mode (CCM) design. Which tend to be able to deliver more power with same maximum drain current.

$$L_{m} = \frac{\left(V_{DC_{min}} \cdot D_{max}\right)^{2}}{2 \times P_{in} \cdot f_{SW} \cdot K_{RF}}$$

(eq. 11)

The inductance value affects maximum drain current  $(I_{DRAINPEAK})$ , which should be limited by FSL5x8's  $I_{LIM}$  specification with some margin. Care needs to be taken when designing  $L_m$  and choosing part from FSL5x8 series.

$$I_{DRAIN_{PEAK}} = \frac{P_{in}}{V_{DC_{min}} \cdot D_{max}} = \frac{V_{DC_{min}} \cdot D_{max}}{2 \cdot L_m \cdot f_{SW}} \quad \text{(eq. 12)}$$

#### • Clamping Circuit for internal MOSFET

Due to parasitic or leakage inductance, it is inevitable that voltage on DRAIN pin of MOSFET shows some spikes during switching off. A clamping circuit is generally implemented if the spike can be so high that makes DRAIN voltage possibly exceeds MOSFET's breakdown voltage,  $BV_{DSS}$ . The clamping circuit can be RCD snubber or transient-voltage suppressor. In both cases, the design target is to clamp the reflected voltage that appears across primary winding with a clamping voltage  $V_{clamp}$ .

*V<sub>clamp</sub>* should be set up properly considering power loss and BV<sub>DSS</sub> of MOSFET. *V<sub>clamp</sub>* is way too high, MOSFET is likely to get damage at maximum input voltage. Whereas, too low one could cause power loss increasing at the clamp circuit. Generally, value in 2~2.5 times of VRO is usually chosen. Additionally, it should not exceed over 90% of BV<sub>DSS</sub>.

$$\sqrt{2} \cdot V_{\text{line}_{\text{max}}} + V_{\text{clamp}} \le 90\% \cdot BV_{\text{DSS}}$$

(eq. 13)

<u>AN-4137</u> and <u>AN-4140</u> provide detailed flyback converter, transformer, and snubber design information. A design tool with accompanying manual is also made for FSL5x8 series.

Figure 46. Magnetic Component and RCD Snubber

Figure 47. Typical Waveform of DRAIN Current and Voltage

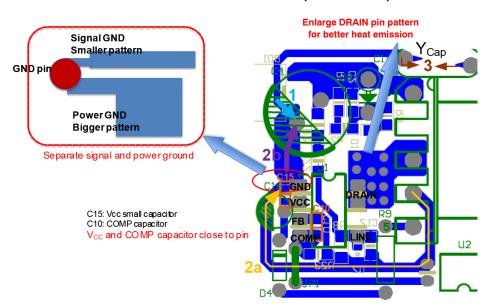

#### **PCB Layout Recommendations**

Hereafter are a few hints that would help designers to make their SMPS working better.

- High-frequency switching current/voltage makes PCB layout a very important design issue. Good PCB layout minimizes EMI (Electromagnetic Interference) and helps the power supply survive during surge/ESD (ElectroStatic Discharge) tests.

- To improve EMI performance and reduce line frequency ripples, the output of the bridge rectifier should be connected to capacitor C<sub>DC</sub> as close as possible.

- The high-frequency current loop is formed from the beginning of bridge rectifier, C<sub>DC</sub>, power transformer, Integrated MOSFET and return to GND of C<sub>DC</sub>. The area enclosed by this current loop should be designed as small as possible to reduce conduction and radiation noise. Keep the traces (especially 2a → 2b → 1) short, direct, and wide. High-voltage traces related the drain of MOSFET and RCD snubber should be kept far way from control circuits to prevent unnecessary interference. If a heatsink is used for MOSFET, connect this heatsink to power ground.

- As indicated by 2a, the ground of control circuits should be connected first, then to other circuitry.

- Place C<sub>Vcc</sub> as close to VCC pin of the FSL5x8H/A as possible for good decoupling. It is recommended to use a few of micro-farad capacitor and 100 nF ceramic capacitor for high frequency noise decoupling as well.

There are some suggestions for grounding connection.

- GND: There are two kinds of GND in power conversion board and should be separated for avoiding interference and better performance.

- Regarding the ESD discharge path, the charges go from secondary, through the transformer stray capacitance, to GND first, and back to mains. It should be noted that control circuits should not be placed on the discharge path. Point discharge for common choke can decrease high-frequency impedance and increase ESD immunity.

- 3 should be a point-discharger route to bypass the static electricity energy. It is suggested to map out this discharge route.

- Should a Y-cap be required between primary and secondary, connect this Y-cap to the positive terminal of C<sub>DC</sub>. If this Y-cap is connected to primary GND, it should be connected to the negative terminal of C<sub>DC</sub> (GND) directly. Point discharge of this Y-cap helps for ESD; however, the creepage between these two pointed ends should be at least 5 mm according to safety requirements.

#### **Thermal Considerations**

Power MOSFET dissipates heat during switching operation. If chip temperature exceed T<sub>SD</sub>, thermal shutdown would be triggered and FSL5x8 stops operating to protect itself from damage. The path of lowest thermal impedance from FSL5x8's chip to external are DRAIN pins. It is recommended to increase area of connected copper to DRAIN pin as much as possible.

Figure 48. Layout Considerations

#### **Design Example**

Hereafter is a typical schematic of an isolated flyback.

Figure 49. FSL538AFLYGEVB Schematic

#### **REFERENCES**

For more details on specific designs, please refer to below documents:

- AN-4148 Audible Noise Reduction Technique for FPS Applications <a href="https://www.onsemi.com/pub/Collateral/AN-4148.pdf">https://www.onsemi.com/pub/Collateral/AN-4148.pdf</a>.

- AN-4137 Design Guidelines for Off-line Flyback Converters Using Power Switch <a href="https://www.onsemi.com/pub/Collateral/AN-4137.pdf.pdf">https://www.onsemi.com/pub/Collateral/AN-4137.pdf.pdf</a>

- AN-4140 Transformer Design Consideration for Offline Flyback Converters Using Power Switch <a href="https://www.onsemi.com/pub/Collateral/AN-4140.pdf">https://www.onsemi.com/pub/Collateral/AN-4140.pdf</a>.

- EVBUM2650/D: 14.5 W auxiliary power for white goods and industrial equipment with FSL538HPG <a href="https://www.onsemi.com/pub/Collateral/EVBUM2650-D.PDF">https://www.onsemi.com/pub/Collateral/EVBUM2650-D.PDF</a>

- EVBUM2651/D: 15 W auxiliary power for white goods and industrial equipment with FSL538APG <a href="https://www.onsemi.com/pub/Collateral/EVBUM2651-D.PDF">https://www.onsemi.com/pub/Collateral/EVBUM2651-D.PDF</a>

- EVBUM2652/D: 8 W auxiliary power for white goods and industrial equipment with FSL518APG <a href="https://www.onsemi.com/pub/Collateral/EVBUM2652-D.PDF">https://www.onsemi.com/pub/Collateral/EVBUM2652-D.PDF</a>

- FSL5x8 Application note and Design tool <a href="https://www.onsemi.com/PowerSolutions/supportDoc.do?type=tools&rpn=FSL538">https://www.onsemi.com/PowerSolutions/supportDoc.do?type=tools&rpn=FSL538</a>

#### **ORDERING INFORMATION**

| Device    | Current Limit (A) | $R_{DS.ON,max}\left(\Omega\right)$ | Package             | Shipping <sup>†</sup> |

|-----------|-------------------|------------------------------------|---------------------|-----------------------|

| FSL518HPG | 0.46              | 8.0                                | PDIP-7<br>(Pb-Free) | Tube                  |

| FSL518APG | 0.61              | 8.0                                | PDIP-7<br>(Pb-Free) | Tube                  |

| FSL538HPG | 0.66              | 4.6                                | PDIP-7<br>(Pb-Free) | Tube                  |

| FSL538APG | 0.86              | 4.6                                | PDIP-7<br>(Pb-Free) | Tube                  |

SENSEFET is a registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

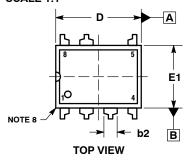

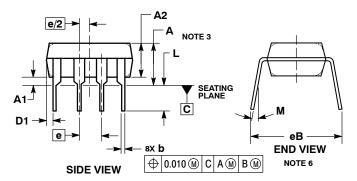

#### PDIP-7 (PDIP-8 LESS PIN 6) CASE 626A ISSUE C

**DATE 22 APR 2015**

**END VIEW** WITH I FADS CONSTRAINED NOTE 5

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- DIMENSIONING AND IDLEHANDING PER ASME Y14.5M, 1994

CONTROLLING DIMENSION: INCHES.

DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACKAGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3.

DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM

- PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

- TO DATUM C.

DIMENSION •B IS MEASURED AT THE LEAD TIPS WITH THE

LEADS UNCONSTRAINED.

DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE

LEADS, WHERE THE LEADS EXIT THE BODY.

- PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE CORNERS).

|     | INCHES    |       | MILLIM   | ETERS |

|-----|-----------|-------|----------|-------|

| DIM | MIN       | MAX   | MIN      | MAX   |

| Α   |           | 0.210 |          | 5.33  |

| A1  | 0.015     |       | 0.38     |       |

| A2  | 0.115     | 0.195 | 2.92     | 4.95  |

| b   | 0.014     | 0.022 | 0.35     | 0.56  |

| b2  | 0.060 TYP |       | 1.52     | TYP   |

| С   | 0.008     | 0.014 | 0.20     | 0.36  |

| D   | 0.355     | 0.400 | 9.02     | 10.16 |

| D1  | 0.005     |       | 0.13     |       |

| E   | 0.300     | 0.325 | 7.62     | 8.26  |

| E1  | 0.240     | 0.280 | 6.10     | 7.11  |

| е   | 0.100     | BSC   | 2.54 BSC |       |

| eВ  |           | 0.430 |          | 10.92 |

| L   | 0.115     | 0.150 | 2.92     | 3.81  |

| М   |           | 10°   |          | 10°   |

#### **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code

= Assembly Location

WL = Wafer Lot YY = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON11774D             | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DESCRIPTION:     | PDIP-7 (PDIP-8 LESS PIN | PDIP-7 (PDIP-8 LESS PIN 6)                                                                                                                                                     |  |  |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative