# **LDO Voltage Regulator** -

# **Adjustable Output, Load Dump Protection** 60 V, 100 mA

# **LM2931, NCV2931 Series**

The LM2931 series consists of positive fixed and adjustable output voltage regulators that are specifically designed to maintain proper regulation with an extremely low input-to-output voltage differential. These devices are capable of supplying output currents in excess of 100 mA and feature a low bias current of 0.4 mA at 10 mA output.

Designed primarily to survive in the harsh automotive environment, these devices will protect all external load circuitry from input fault conditions caused by reverse battery connection, two battery jump starts, and excessive line transients during load dump. This series also includes internal current limiting, thermal shutdown, and additionally, is able to withstand temporary power-up with mirror-image insertion.

Due to the low dropout voltage and bias current specifications, the LM2931 series is ideally suited for battery powered industrial and consumer equipment where an extension of useful battery life is desirable. The 'C' suffix adjustable output regulators feature an output inhibit pin which is extremely useful in microprocessor-based systems.

#### **Features**

- Input-to-Output Voltage Differential of < 0.6 V @ 100 mA

- Output Current in Excess of 100 mA

- Low Bias Current

- 60 V Load Dump Protection

- -50 V Reverse Transient Protection

- Internal Current Limiting with Thermal Shutdown

- Temporary Mirror-Image Protection

- Ideally Suited for Battery Powered Equipment

- Economical 5-Lead TO-220 Package with Two Optional Leadforms

- Available in Surface Mount SOP-8, D<sup>2</sup>PAK and DPAK Packages

- High Accuracy (±2.5%) Reference (LM2931AC) Available

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- Pb-Free Packages are Available

# **Applications**

- Battery Powered Consumer Products

- Hand-held Instruments

- Camcorders and Cameras

### ON Semiconductor®

#### www.onsemi.com

#### **FIXED OUTPUT VOLTAGE**

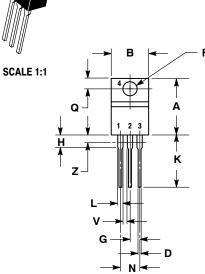

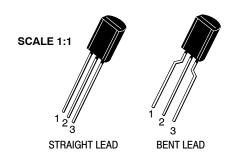

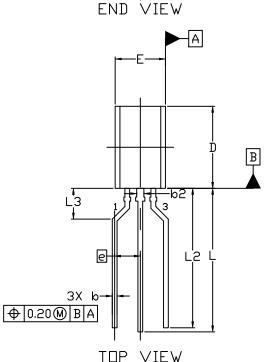

TO-92 **Z SUFFIX CASE 29-10** TO-220

Pin 1. Output 2. Ground 3. Input

T SUFFIX CASE 221AB DPΔK

**DT SUFFIX**

**CASE 369C**

Pin 1. Input

D<sup>2</sup>PAK **D2T SUFFIX CASE 936**

2. Ground 3. Output

SOT-223 ST SUFFIX **CASE 318H**

#### ADJUSTABLE OUTPUT VOLTAGE

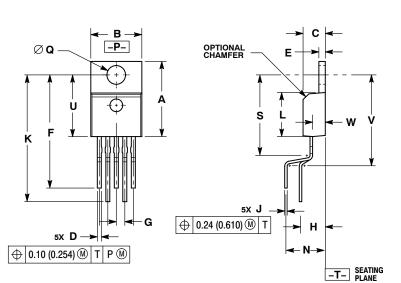

TO-220 **TH SUFFIX CASE 314A**

TO-220 **TV SUFFIX CASE 314B**

TO-220

T SUFFIX

CASE 314D

D<sup>2</sup>PAK **D2T SUFFIX CASE 936A**

Pin 1. Adjust

- 2. Output Inhibit

- 3. Ground 4. Input

- 5. Output

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

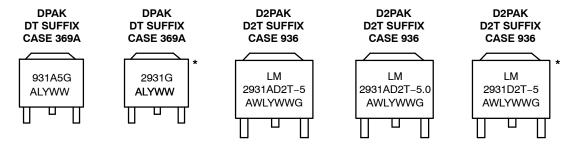

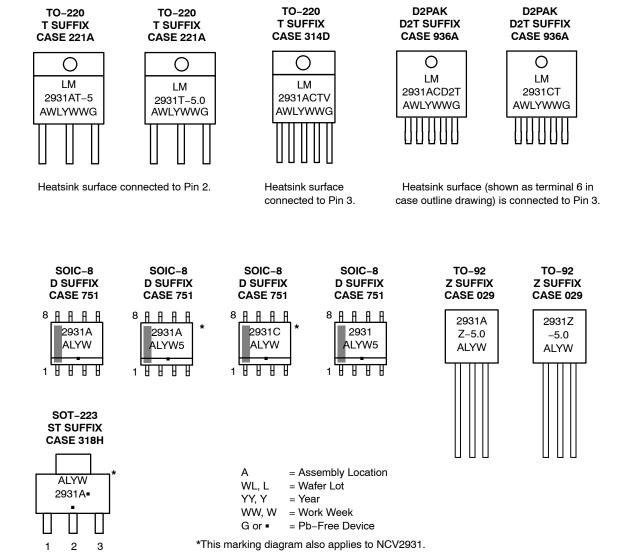

#### **DEVICE MARKING INFORMATION**

See general marking and heatsink information in the device marking section on page 15 of this data sheet.

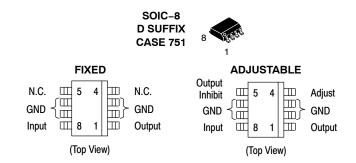

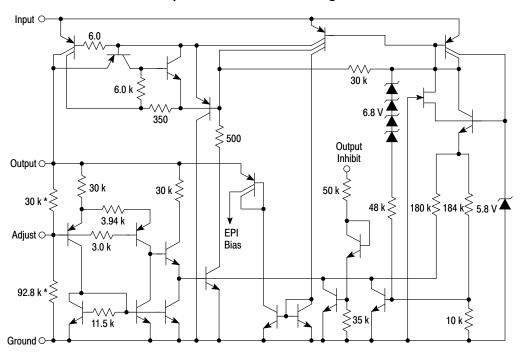

### **Representative Schematic Diagram**

<sup>\*</sup>Deleted on Adjustable Regulators

This device contains 26 active transistors.

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                 | Symbol            | Value              | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------|

| Input Voltage Continuous                                                                                                                                                               | VI                | 40                 | Vdc  |

| Transient Input Voltage (τ ≤ 100 ms)                                                                                                                                                   | $V_I(\tau)$       | 60                 | Vpk  |

| Transient Reverse Polarity Input Voltage 1.0% Duty Cycle, τ ≤ 100 ms                                                                                                                   | $-V_{I}(\tau)$    | -50                | Vpk  |

| Electrostatic Discharge Sensitivity (ESD) Human Body Model (HBM) Class 2, JESD22 A114-C Machine Model (MM) Class A, JESD22 A115-A Charged Device Model (CDM), JESD22 C101-C            | -                 | 2000               | V    |

|                                                                                                                                                                                        | -                 | 200                | V    |

|                                                                                                                                                                                        | -                 | 2000               | V    |

| Power Dissipation Case 29 (TO–92 Type) T <sub>A</sub> = 25°C Thermal Resistance, Junction–to–Ambient Thermal Resistance, Junction–to–Case Case 221A, 314A, 314B and 314D (TO–220 Type) | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θJA</sub>  | 178                | °C/W |

|                                                                                                                                                                                        | R <sub>θJC</sub>  | 83                 | °C/W |

| T <sub>A</sub> = 25°C Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case Case 318H (SOT-223)                                                                 | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θJA</sub>  | 65                 | °C/W |

|                                                                                                                                                                                        | R <sub>θJC</sub>  | 5.0                | °C/W |

| T <sub>A</sub> = 25°C Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case                                                                                     | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θJA</sub>  | 242                | °C/W |

|                                                                                                                                                                                        | R <sub>θJC</sub>  | 21                 | °C/W |

| Case 369A (DPAK) (Note 1)  T <sub>A</sub> = 25°C  Thermal Resistance, Junction-to-Ambient  Thermal Resistance, Junction-to-Case                                                        | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θJA</sub>  | 92                 | °C/W |

|                                                                                                                                                                                        | R <sub>θJC</sub>  | 6.0                | °C/W |

| Case 751 (SOP-8) (Note 2)  T <sub>A</sub> = 25°C  Thermal Resistance, Junction-to-Ambient  Thermal Resistance, Junction-to-Case  Case 936 and 936A (D <sup>2</sup> PAK) (Note 3)       | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θJA</sub>  | 160                | °C/W |

|                                                                                                                                                                                        | R <sub>θJC</sub>  | 25                 | °C/W |

| T <sub>A</sub> = 25°C Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case                                                                                     | P <sub>D</sub>    | Internally Limited | W    |

|                                                                                                                                                                                        | R <sub>θ</sub> JA | 70                 | °C/W |

|                                                                                                                                                                                        | R <sub>θ</sub> JC | 5.0                | °C/W |

| Operating Ambient Temperature Range                                                                                                                                                    | T <sub>A</sub>    | -40 to +125        | °C   |

| Operating Die Junction Temperature                                                                                                                                                     | TJ                | +150               | °C   |

| Storage Temperature Range                                                                                                                                                              | T <sub>stg</sub>  | -65 to +150        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

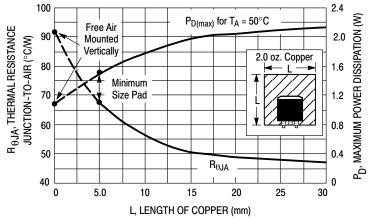

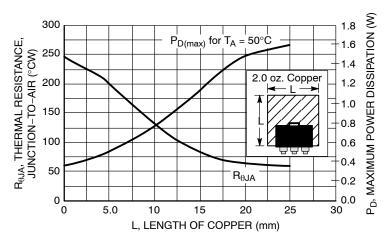

- 1. DPAK Junction-to-Ambient Thermal Resistance is for vertical mounting. Refer to Figure 25 for board mounted Thermal Resistance.

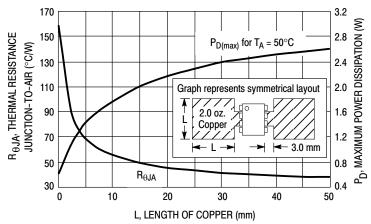

- 2. SOP-8 Junction-to-Ambient Thermal Resistance is for minimum recommended pad size. Refer to Figure 24 for Thermal Resistance variation versus pad size.

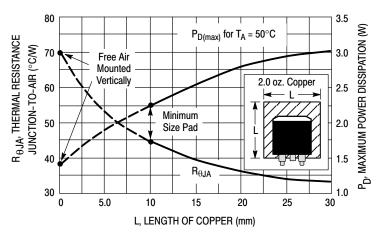

- 3. D<sup>2</sup>PAK Junction to Ambient Thermal Resistance is for vertical mounting. Refer to Figure 26 for board mounted Thermal Resistance.

- 4. NCV rated devices are subjected to and meet the AECQ-100 quality standards.

# **ELECTRICAL CHARACTERISTICS** ( $V_{in} = 14 \text{ V}$ , $I_O = 10 \text{ mA}$ , $C_O = 100 \text{ }\mu\text{F}$ , $C_{O(ESR)} = 0.3 \Omega$ , $T_A = 25^{\circ}\text{C}$ [Note 5])

|                                                                                   |                     | LM2931 | -5.0/NCV | 2931–5.0 | LM2931A-5.0/NCV2931A-5.0 |       |      |        |

|-----------------------------------------------------------------------------------|---------------------|--------|----------|----------|--------------------------|-------|------|--------|

| Characteristic                                                                    | Symbol              | Min    | Тур      | Max      | Min                      | Тур   | Max  | Unit   |

| FIXED OUTPUT                                                                      |                     | •      |          | •        |                          |       | •    |        |

| Output Voltage                                                                    | Vo                  |        |          |          |                          |       |      | V      |

| V <sub>in</sub> = 14 V, I <sub>O</sub> = 10 mA, T <sub>A</sub> = 25°C             |                     | 4.75   | 5.0      | 5.25     | 4.81                     | 5.0   | 5.19 |        |

| $V_{in}$ = 6.0 V to 26 V, $I_O \le$ 100 mA, $T_A = -40^\circ$ to +125°C           |                     | 4.50   | -        | 5.50     | 4.75                     | -     | 5.25 |        |

| Line Regulation                                                                   | Reg <sub>line</sub> |        |          |          |                          |       |      | mV     |

| V <sub>in</sub> = 9.0 V to 16 V                                                   |                     | _      | 2.0      | 10       | -                        | 2.0   | 10   |        |

| V <sub>in</sub> = 6.0 V to 26 V                                                   |                     | _      | 4.0      | 30       | -                        | 4.0   | 30   |        |

| Load Regulation (I <sub>O</sub> = 5.0 mA to 100 mA)                               | Reg <sub>load</sub> | _      | 14       | 50       | -                        | 14    | 50   | mV     |

| Output Impedance                                                                  | Z <sub>O</sub>      |        |          |          |                          |       |      | mΩ     |

| $I_{O}$ = 10 mA, $\Delta I_{O}$ = 1.0 mA, f = 100 Hz to 10 kHz                    |                     | _      | 200      | -        | -                        | 200   | -    |        |

| Bias Current                                                                      | Ι <sub>Β</sub>      |        |          |          |                          |       |      | mA     |

| V <sub>in</sub> = 14 V, I <sub>O</sub> = 100 mA, T <sub>A</sub> = 25°C            |                     | _      | 5.8      | 30       | -                        | 5.8   | 30   |        |

| $V_{in}$ = 6.0 V to 26 V, $I_O$ = 10 mA, $T_A$ = $-40^{\circ}$ to $+125^{\circ}C$ |                     | _      | 0.4      | 1.0      | -                        | 0.4   | 1.0  |        |

| Output Noise Voltage (f = 10 Hz to 100 kHz)                                       | V <sub>n</sub>      | _      | 700      | -        | -                        | 700   | _    | μVrms  |

| Long Term Stability                                                               | S                   | _      | 20       | -        | -                        | 20    | _    | mV/kHR |

| Ripple Rejection (f = 120 Hz)                                                     | RR                  | 60     | 90       | -        | 60                       | 90    | _    | dB     |

| Dropout Voltage                                                                   | $V_I$ – $V_O$       |        |          |          |                          |       |      | V      |

| I <sub>O</sub> = 10 mA                                                            |                     | _      | 0.015    | 0.2      | -                        | 0.015 | 0.2  |        |

| I <sub>O</sub> = 100 mA                                                           |                     | -      | 0.16     | 0.6      | -                        | 0.16  | 0.6  |        |

| Over-Voltage Shutdown Threshold                                                   | V <sub>th(OV)</sub> | 26     | 29.5     | 40       | 26                       | 29.5  | 40   | V      |

| Output Voltage with Reverse Polarity Input $(V_{in} = -15 \text{ V})$             | -V <sub>O</sub>     | -0.3   | 0        | -        | -0.3                     | 0     | -    | V      |

<sup>5.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.6. NCV devices are qualified for automotive use.

$\textbf{ELECTRICAL CHARACTERISTICS} \ (V_{in} = 14 \ V, \ I_O = 10 \ mA, \ C_O = 100 \ \mu F, \ C_{O(ESR)} = 0.3 \ \Omega, \ T_A = 25^{\circ}C \ [Note \ 7])$

|                                                                                                                                                                    |                                | LM29                   | LM2931C/NCV2931C       |                        | LM293                  | AC/NCV                 | 2931AC                 |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------|

| Characteristic                                                                                                                                                     | Symbol                         | Min                    | Тур                    | Max                    | Min                    | Тур                    | Max                    | Unit    |

| ADJUSTABLE OUTPUT                                                                                                                                                  | •                              | •                      |                        |                        |                        |                        |                        | •       |

| Reference Voltage (Note 8, Figure 18)<br>$I_O = 10$ mA, $T_A = 25^{\circ}C$<br>$I_O \le 100$ mA, $T_A = -40$ to $+125^{\circ}C$                                    | V <sub>ref</sub>               | 1.14<br>1.08           | 1.20                   | 1.26<br>1.32           | 1.17<br>1.15           | 1.20                   | 1.23<br>1.25           | V       |

| Output Voltage Range                                                                                                                                               | V <sub>O range</sub>           | 3.0 to<br>24           | 2.7 to<br>29.5         | -                      | 3.0 to<br>24           | 2.7 to<br>29.5         | -                      | V       |

| Line Regulation (V <sub>in</sub> = V <sub>O</sub> + 0.6 V to 26 V)                                                                                                 | Reg <sub>line</sub>            | _                      | 0.2                    | 1.5                    | -                      | 0.2                    | 1.5                    | mV/V    |

| Load Regulation (I <sub>O</sub> = 5.0 mA to 100 mA)                                                                                                                | Reg <sub>load</sub>            | -                      | 0.3                    | 1.0                    | -                      | 0.3                    | 1.0                    | %/V     |

| Output Impedance $I_O = 10$ mA, $\Delta I_O = 1.0$ mA, $f = 10$ Hz to 10 kHz                                                                                       | Z <sub>O</sub>                 | -                      | 40                     | -                      | -                      | 40                     | -                      | mΩ/V    |

| Bias Current $I_O = 100 \text{ mA}$ $I_O = 10 \text{ mA}$ Output Inhibited $(V_{th(OI)} = 2.5 \text{ V})$                                                          | I <sub>B</sub>                 | -<br>-                 | 6.0<br>0.4<br>0.2      | -<br>1.0<br>1.0        |                        | 6.0<br>0.4<br>0.2      | -<br>1.0<br>1.0        | mA      |

| Adjustment Pin Current                                                                                                                                             | I <sub>Adj</sub>               | -                      | 0.2                    | -                      | _                      | 0.2                    | -                      | μΑ      |

| Output Noise Voltage (f = 10 Hz to 100 kHz)                                                                                                                        | V <sub>n</sub>                 | -                      | 140                    | -                      | -                      | 140                    | -                      | μVrms/V |

| Long-Term Stability                                                                                                                                                | S                              | _                      | 0.4                    | -                      | -                      | 0.4                    | -                      | %/kHR   |

| Ripple Rejection (f = 120 Hz)                                                                                                                                      | RR                             | 0.10                   | 0.003                  | -                      | 0.10                   | 0.003                  | -                      | %/V     |

| Dropout Voltage $I_O = 10 \text{ mA}$ $I_O = 100 \text{ mA}$                                                                                                       | V <sub>I</sub> –V <sub>O</sub> | -<br>-                 | 0.015<br>0.16          | 0.2<br>0.6             | -<br>-                 | 0.015<br>0.16          | 0.2<br>0.6             | V       |

| Over-Voltage Shutdown Threshold                                                                                                                                    | $V_{th(OV)}$                   | 26                     | 29.5                   | 40                     | 26                     | 29.5                   | 40                     | V       |

| Output Voltage with Reverse Polarity Input $(V_{in} = -15 \text{ V})$                                                                                              | -V <sub>O</sub>                | -0.3                   | 0                      | -                      | -0.3                   | 0                      | -                      | V       |

| Output Inhibit Threshold Voltages  Output "On": $T_A = 25^{\circ}C$ $T_A = -40^{\circ}$ to +125°C  Output "Off": $T_A = 25^{\circ}C$ $T_A = -40^{\circ}$ to +125°C | V <sub>th(OI)</sub>            | -<br>-<br>2.50<br>3.25 | 2.15<br>-<br>2.26<br>- | 1.90<br>1.20<br>-<br>- | -<br>-<br>2.50<br>3.25 | 2.15<br>-<br>2.26<br>- | 1.90<br>1.20<br>-<br>- | V       |

| Output Inhibit Threshold Current (V <sub>th(OI)</sub> = 2.5 V)                                                                                                     | I <sub>th(OI)</sub>            | -                      | 30                     | 50                     | -                      | 30                     | 50                     | μΑ      |

<sup>7.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

8. The reference voltage on the adjustable device is measured from the output to the adjust pin across R<sub>1</sub>.

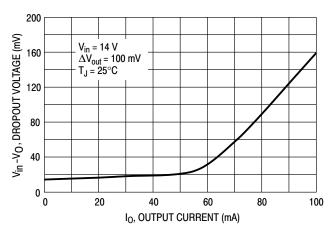

Figure 1. Dropout Voltage versus Output Current

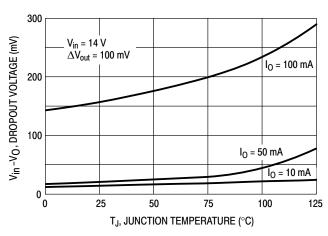

Figure 2. Dropout Voltage versus Junction Temperature

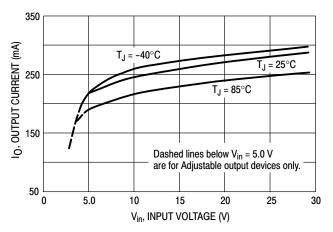

Figure 3. Peak Output Current versus Input Voltage

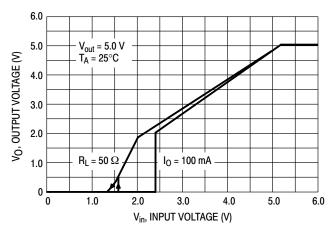

Figure 4. Output Voltage versus Input Voltage

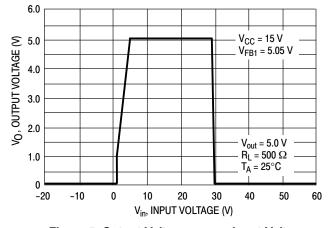

Figure 5. Output Voltage versus Input Voltage

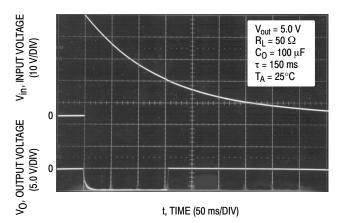

Figure 6. Load Dump Characteristics

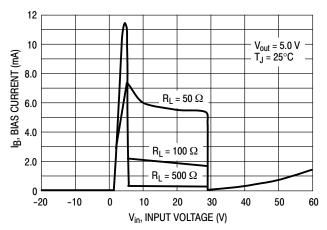

Figure 7. Bias Current versus Input Voltage

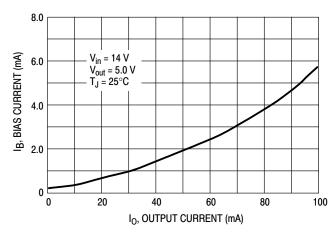

Figure 8. Bias Current versus Output Current

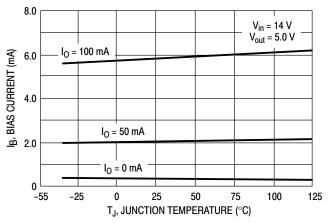

Figure 9. Bias Current versus Junction Temperature

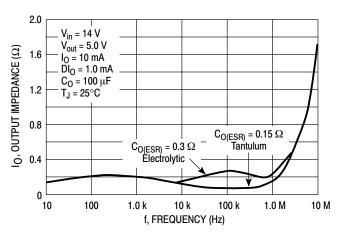

Figure 10. Output Impedance versus Frequency

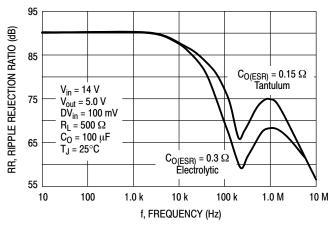

Figure 11. Ripple Rejection versus Frequency

Figure 12. Ripple Rejection versus Output Current

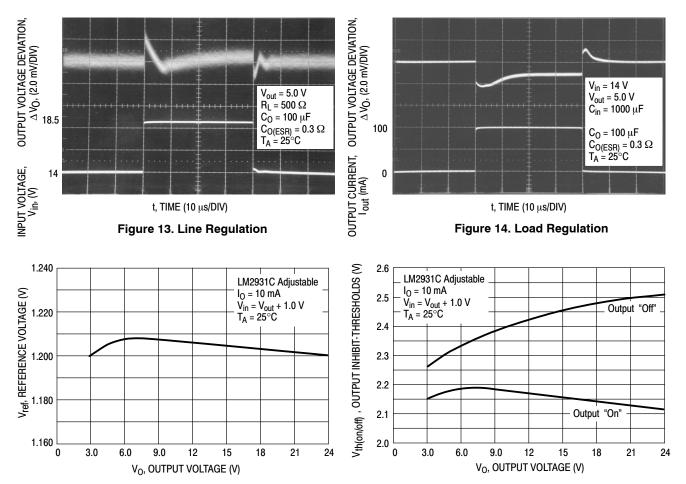

Figure 15. Reference Voltage versus Output Voltage

Figure 16. Output Inhibit-Thresholds versus Output Voltage

#### **APPLICATIONS INFORMATION**

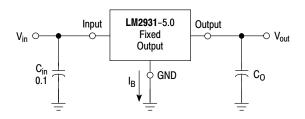

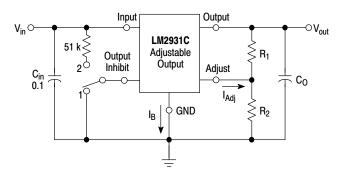

The LM2931 series regulators are designed with many protection features making them essentially blow-out proof. These features include internal current limiting, thermal shutdown, overvoltage and reverse polarity input protection, and the capability to withstand temporary power-up with mirror-image insertion. Typical application circuits for the fixed and adjustable output device are shown in Figures 17 and 18.

The input bypass capacitor  $C_{in}$  is recommended if the regulator is located an appreciable distance ( $\geq 4''$ ) from the supply input filter. This will reduce the circuit's sensitivity to the input line impedance at high frequencies.

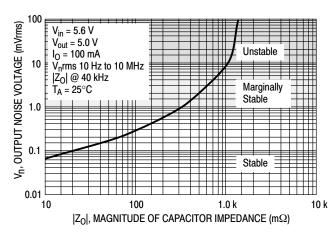

This regulator series is not internally compensated and thus requires an external output capacitor for stability. The capacitance value required is dependent upon the load current, output voltage for the adjustable regulator, and the type of capacitor selected. The least stable condition is encountered at maximum load current and minimum output voltage. Figure 22 shows that for operation in the "Stable" region, under the conditions specified, the magnitude of the output capacitor impedance  $|Z_O|$  must not exceed 0.4  $\Omega$ . This

limit must be observed over the entire operating temperature range of the regulator circuit.

With economical electrolytic capacitors, cold temperature operation can pose a serious stability problem. As the electrolyte freezes, around  $-30^{\circ}\mathrm{C}$ , the capacitance will decrease and the equivalent series resistance (ESR) will increase drastically, causing the circuit to oscillate. Quality electrolytic capacitors with extended temperature ranges of  $-40^{\circ}$  to  $+85^{\circ}\mathrm{C}$  and  $-55^{\circ}$  to  $+105^{\circ}\mathrm{C}$  are readily available. Solid tantalum capacitors may be a better choice if small size is a requirement, however, the maximum  $\left|Z_{\mathrm{O}}\right|$  limit over temperature must be observed.

Note that in the stable region, the output noise voltage is linearly proportional to  $\left| Z_O \right|$ . In effect,  $C_O$  dictates the high frequency roll–off point of the circuit. Operation in the area titled "Marginally Stable" will cause the output of the regulator to exhibit random bursts of oscillation that decay in an under–damped fashion. Continuous oscillation occurs when operating in the area titled "Unstable". It is suggested that oven testing of the entire circuit be performed with maximum load, minimum input voltage, and minimum ambient temperature.

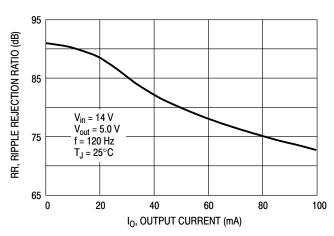

Figure 17. Fixed Output Regulator

Switch Position 1 = Output "On", 2 = Output "Off"

$$V_{out} = V_{ref} \left( 1 + \frac{R_2}{R_1} \right) + I_{Adj} R_2$$

22.5 k  $\geq \frac{R_1 R_2}{R_1 + R_2}$

Figure 18. Adjustable Output Regulator

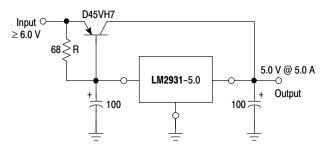

The LM2931 series can be current boosted with a PNP transistor. The D45VH7, on a heatsink, will provide an output current of 5.0 A with an input to output voltage differential of approximately 1.0 V. Resistor R in conjunction with the  $V_{BE}$  of the PNP determines when the pass transistor begins conducting. This circuit is not short circuit proof.

Figure 19. (5.0 A) Low Differential Voltage Regulator

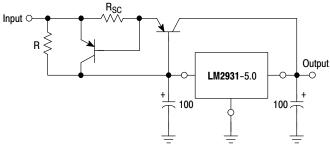

The circuit of Figure 19 can be modified to provide supply protection against short circuits by adding the current sense resistor  $R_{SC}$  and an additional PNP transistor. The current sensing PNP must be capable of handling the short circuit current of the LM2931. Safe operating area of both transistors must be considered under worst case conditions.

Figure 20. Current Boost Regulator with Short Circuit Projection

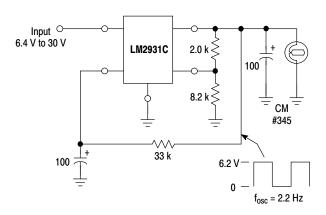

Figure 21. Constant Intensity Lamp Flasher

$10~\mu\text{F}$ 22 μF 0.50 Unstable **47** μF 100 μΕ 0.40 ESR (Ohms) 0.30 Stable 0.20 Note - Optimum stability uses a 22  $\mu$ F 0.10 output capacitor. Output capacitor values below 10 µF are not recommended. 0.00 10 20 30 40 50 60 70 80 90 100 0 OUTPUT CURRENT (mA)

Figure 22. Output Noise Voltage vs.

Output Capacitor Impedance

Figure 23. Output Capacitor ESR Stability vs.

Output Load Current

Figure 24. SOP-8 Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

Figure 25. DPAK Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

Figure 26. 3-Pin and 5-Pin D<sup>2</sup>PAK

Thermal Resistance and Maximum Power

Dissipation versus P.C.B. Copper Length

Figure 27. SOT-223 Thermal Resistance and Maximum Power Dissipation vs. P.C.B. Copper Length

#### **DEFINITIONS**

**Dropout Voltage** – The input/output voltage differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output decreases 100 mV from nominal value at 14 V input, dropout voltage is affected by junction temperature and load current.

**Line Regulation** – The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that the average chip temperature is not significantly affected.

**Load Regulation** – The change in output voltage for a change in load current at constant chip temperature.

**Maximum Power Dissipation** – The maximum total device dissipation for which the regulator will operate within specifications.

**Bias Current** – That part of the input current that is not delivered to the load.

**Output Noise Voltage** – The rms AC voltage at the output, with constant load and no input ripple, measured over a specified frequency range.

**Long-Term Stability** – Output voltage stability under accelerated life test conditions with the maximum rated voltage listed in the devices electrical characteristics and maximum power dissipation.

#### **ORDERING INFORMATION**

|                  | Ou      | ıtput     |                                 |                       |  |

|------------------|---------|-----------|---------------------------------|-----------------------|--|

| Device           | Voltage | Tolerance | Package                         | Shipping <sup>†</sup> |  |

| LM2931AD-5.0     | 5.0 V   | ±3.8%     | SOIC-8                          | 98 Units / Rail       |  |

| LM2931AD-5.0G    | 5.0 V   | ±3.8%     | SOIC-8<br>(Pb-Free)             | 98 Units / Rail       |  |

| LM2931AD-5.0R2   | 5.0 V   | ±3.8%     | SOIC-8                          | 2500 / Tape & Reel    |  |

| LM2931AD-5.0R2G  | 5.0 V   | ±3.8%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |  |

| LM2931ADT-5.0    | 5.0 V   | ±3.8%     | DPAK                            | 75 Units / Rail       |  |

| LM2931ADT-5.0G   | 5.0 V   | ±3.8%     | DPAK<br>(Pb-Free)               | 75 Units / Rail       |  |

| LM2931ADT-5.0RK  | 5.0 V   | ±3.8%     | DPAK                            | 2500 / VacPk Reel     |  |

| LM2931ADT-5.0RKG | 5.0 V   | ±3.8%     | DPAK<br>(Pb-Free)               | 2500 / VacPk Reel     |  |

| LM2931AD2T-5.0   | 5.0 V   | ±3.8%     | D <sup>2</sup> PAK              | 50 Units / Rail       |  |

| LM2931AD2T-5.0G  | 5.0 V   | ±3.8%     | D <sup>2</sup> PAK<br>(Pb-Free) | 50 Units / Rail       |  |

| LM2931AD2T-5.0R4 | 5.0 V   | ±3.8%     | D <sup>2</sup> PAK              | 800 / VacPk Reel      |  |

| LM2931AD2T-5R4G  | 5.0 V   | ±3.8%     | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |  |

| LM2931AT-5.0     | 5.0 V   | ±3.8%     | TO-220                          | 50 Units / Rail       |  |

| LM2931AT-5.0G    | 5.0 V   | ±3.8%     | TO-220<br>(Pb-Free)             | 50 Units / Rail       |  |

| LM2931AZ-5.0     | 5.0 V   | ±3.8%     | TO-92                           | 2000 / Inner Bag      |  |

| LM2931AZ-5.0G    | 5.0 V   | ±3.8%     | TO-92<br>(Pb-Free)              | 2000 / Inner Bag      |  |

| LM2931AZ-5.0RA   | 5.0 V   | ±3.8%     | TO-92                           | 2000 / Tape & Reel    |  |

| LM2931AZ-5.0RAG  | 5.0 V   | ±3.8%     | TO-92<br>(Pb-Free)              | 2000 / Tape & Reel    |  |

| LM2931AZ-5.0RP   | 5.0 V   | ±3.8%     | TO-92                           | 2000 / Ammo Pack      |  |

| LM2931AZ-5.0RPG  | 5.0 V   | ±3.8%     | TO-92<br>(Pb-Free)              | 2000 / Ammo Pack      |  |

| LM2931D-5.0      | 5.0 V   | ±5.0%     | SOIC-8                          | 98 Units / Rail       |  |

| LM2931D-5.0G     | 5.0 V   | ±5.0%     | SOIC-8<br>(Pb-Free)             | 98 Units / Rail       |  |

| LM2931D-5.0R2    | 5.0 V   | ±5.0%     | SOIC-8                          | 2500 / Tape & Reel    |  |

| LM2931D-5.0R2G   | 5.0 V   | ±5.0%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |  |

| LM2931D2T-5.0    | 5.0 V   | ±5.0%     | D <sup>2</sup> PAK              | 50 Units / Rail       |  |

| LM2931D2T-5.0G   | 5.0 V   | ±5.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 50 Units / Rail       |  |

| LM2931D2T-5.0R4  | 5.0 V   | ±5.0%     | D <sup>2</sup> PAK              | 800 / VacPk Reel      |  |

| LM2931D2T-5.0R4G | 5.0 V   | ±5.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV2931: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C. Guaranteed by design. NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

#### **ORDERING INFORMATION**

|                | Out        | tput      |                                 |                       |  |  |

|----------------|------------|-----------|---------------------------------|-----------------------|--|--|

| Device         | Voltage    | Tolerance | Package                         | Shipping <sup>†</sup> |  |  |

| LM2931DT-5.0   | 5.0 V      | ±5.0%     | DPAK                            | 75 Units / Rail       |  |  |

| LM2931DT-5.0G  | 5.0 V      | ±5.0%     | DPAK<br>(Pb-Free)               | 75 Units / Rail       |  |  |

| LM2931T-5.0    | 5.0 V      | ±5.0%     | TO-220                          | 50 Units / Rail       |  |  |

| LM2931T-5.0G   | 5.0 V      | ±5.0%     | TO-220<br>(Pb-Free)             | 50 Units / Rail       |  |  |

| LM2931Z-5.0    | 5.0 V      | ±5.0%     | TO-92                           | 2000 / Inner Bag      |  |  |

| LM2931Z-5.0G   | 5.0 V      | ±5.0%     | TO-92<br>(Pb-Free)              | 2000 / Inner Bag      |  |  |

| LM2931Z-5.0RA  | 5.0 V      | ±5.0%     | TO-92                           | 2000 / Tape & Reel    |  |  |

| LM2931Z-5.0RAG | 5.0 V      | ±5.0%     | TO-92<br>(Pb-Free)              | 2000 / Tape & Reel    |  |  |

| LM2931Z-5.0RP  | 5.0 V      | ±5.0%     | TO-92                           | 2000 / Ammo Pack      |  |  |

| LM2931Z-5.0RPG | 5.0 V      | ±5.0%     | TO-92<br>(Pb-Free)              | 2000 / Ammo Pack      |  |  |

| LM2931CD       | Adjustable | ±5.0%     | SOIC-8                          | 98 Units / Rail       |  |  |

| LM2931CDG      | Adjustable | ±5.0%     | SOIC-8<br>(Pb-Free)             | 98 Units / Rail       |  |  |

| LM2931CDR2     | Adjustable | ±5.0%     | SOIC-8                          | 2500 / Tape & Reel    |  |  |

| LM2931CDR2G    | Adjustable | ±5.0%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |  |  |

| LM2931CD2T     | Adjustable | ±5.0%     | D <sup>2</sup> PAK              | 50 Units / Rail       |  |  |

| LM2931CD2TG    | Adjustable | ±5.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 50 Units / Rail       |  |  |

| LM2931CD2TR4   | Adjustable | ±5.0%     | D <sup>2</sup> PAK              | 800 / VacPk Reel      |  |  |

| LM2931CD2TR4G  | Adjustable | ±5.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |  |  |

| LM2931CT       | Adjustable | ±5.0%     | TO-220                          | 50 Units / Rail       |  |  |

| LM2931CTG      | Adjustable | ±5.0%     | TO-220<br>(Pb-Free)             | 50 Units / Rail       |  |  |

| LM2931ACD      | Adjustable | ±2.0%     | SOIC-8                          | 98 Units / Rail       |  |  |

| LM2931ACDG     | Adjustable | ±2.0%     | SOIC-8<br>(Pb-Free)             | 98 Units / Rail       |  |  |

| LM2931ACDR2    | Adjustable | ±2.0%     | SOIC-8                          | 2500 / Tape & Reel    |  |  |

| LM2931ACDR2G   | Adjustable | ±2.0%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |  |  |

| LM2931ACD2TR4  | Adjustable | ±2.0%     | D <sup>2</sup> PAK              | 800 / VacPk Reel      |  |  |

| LM2931ACD2TR4G | Adjustable | ±2.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |  |  |

| LM2931ACTV     | Adjustable | ±2.0%     | TO-220                          | 50 Units / Rail       |  |  |

| LM2931ACTVG    | Adjustable | ±2.0%     | TO-220<br>(Pb-Free)             | 50 Units / Rail       |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV2931: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C. Guaranteed by design. NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

#### **ORDERING INFORMATION**

|                    | Out        | Output    |                                 |                       |

|--------------------|------------|-----------|---------------------------------|-----------------------|

| Device             | Voltage    | Tolerance | Package                         | Shipping <sup>†</sup> |

| NCV2931ACDR2*      | Adjustable | ±2.5%     | SOIC-8                          | 2500 / Tape & Reel    |

| NCV2931ACDR2G*     | Adjustable | ±2.5%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |

| NCV2931AD-5.0R2*   | 5.0 V      | ±3.8%     | SOIC-8                          | 2500 / Tape & Reel    |

| NCV2931AD-5.0R2G*  | 5.0 V      | ±3.8%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |

| NCV2931AST-5.0T3*  | 5.0 V      | ±3.8%     | SOT-223                         | 4000 / Tape & Reel    |

| NCV2931AST-5.0T3G* | 5.0 V      | ±3.8%     | SOT-223<br>(Pb-Free)            | 4000 / Tape & Reel    |

| NCV2931AZ-5.0G*    | 5.0 V      | ±3.8%     | TO-92<br>(Pb-Free)              | 2000 / Inner Bag      |

| NCV2931AZ-5.0RAG*  | 5.0 V      | ±3.8%     | TO-92<br>(Pb-Free)              | 2000 / Tape & Reel    |

| NCV2931CDR2*       | Adjustable | ±5.0%     | SOIC-8                          | 2500 / Tape & Reel    |

| NCV2931CDR2G*      | Adjustable | ±5.0%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |

| NCV2931D-5.0R2*    | 5.0 V      | ±5.0%     | SOIC-8                          | 2500 / Tape & Reel    |

| NCV2931D-5.0R2G*   | 5.0 V      | ±5.0%     | SOIC-8<br>(Pb-Free)             | 2500 / Tape & Reel    |

| NCV2931ADT-5.0RK*  | 5.0 V      | ±3.8%     | DPAK                            | 2500 / Tape & Reel    |

| NCV2931ADT5.0RKG*  | 5.0 V      | ±3.8%     | DPAK<br>(Pb-Free)               | 2500 / Tape & Reel    |

| NCV2931DT-5.0RK*   | 5.0 V      | ±5.0%     | DPAK                            | 2500 / Tape & Reel    |

| NCV2931DT-5.0RKG*  | 5.0 V      | ±5.0%     | DPAK<br>(Pb-Free)               | 2500 / Tape & Reel    |

| NCV2931ACD2TR4G*   | Adjustable | ± 2.5%    | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |

| NCV2931D2T-5.0R4*  | 5.0 V      | ±5.0%     | D <sup>2</sup> PAK              | 800 / VacPk Reel      |

| NCV2931D2T5.0R4G*  | 5.0 V      | ±5.0%     | D <sup>2</sup> PAK<br>(Pb-Free) | 800 / VacPk Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Spe-

cifications Brochure, BRD8011/D.

\*NCV2931: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C. Guaranteed by design. NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

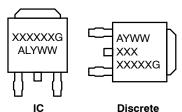

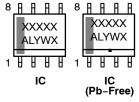

#### **MARKING DIAGRAMS**

Heatsink surface (shown as terminal 4 in case outline drawing) is connected to Pin 2.

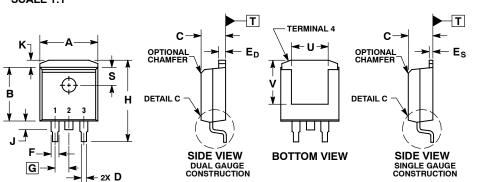

# **MECHANICAL CASE OUTLINE PACKAGE DIMENSIONS**

ON Semiconductor®

TO-220, SINGLE GAUGE CASE 221AB-01 **ISSUE A**

**DATE 16 NOV 2010**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCHES.

3. DIMENSION 2 DEFINES A ZONE WHERE ALL BODY AND LEAD IRREGULARTIES ARE ALLOWED.

4. PRODUCT SHIPPED PRIOR TO 2008 HAD DIMENSIONS S = 0.045 0.055 INCHES (1.143 1.397 MM)

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   | 0.570 | 0.620 | 14.48       | 15.75 |  |

| В   | 0.380 | 0.405 | 9.66        | 10.28 |  |

| С   | 0.160 | 0.190 | 4.07        | 4.82  |  |

| D   | 0.025 | 0.035 | 0.64        | 0.88  |  |

| F   | 0.142 | 0.147 | 3.61        | 3.73  |  |

| G   | 0.095 | 0.105 | 2.42        | 2.66  |  |

| Н   | 0.110 | 0.155 | 2.80        | 3.93  |  |

| J   | 0.018 | 0.025 | 0.46        | 0.64  |  |

| K   | 0.500 | 0.562 | 12.70       | 14.27 |  |

| L   | 0.045 | 0.060 | 1.15        | 1.52  |  |

| N   | 0.190 | 0.210 | 4.83        | 5.33  |  |

| Q   | 0.100 | 0.120 | 2.54        | 3.04  |  |

| R   | 0.080 | 0.110 | 2.04        | 2.79  |  |

| S   | 0.020 | 0.024 | 0.508       | 0.61  |  |

| T   | 0.235 | 0.255 | 5.97        | 6.47  |  |

| U   | 0.000 | 0.050 | 0.00        | 1.27  |  |

| ٧   | 0.045 |       | 1.15        |       |  |

| Z   |       | 0.080 |             | 2.04  |  |

| STYLE 1: |           | STYLE 2:  |           | STYLE 3:  |         |

|----------|-----------|-----------|-----------|-----------|---------|

| PIN 1.   | BASE      | PIN 1.    | BASE      | PIN 1.    | CATHODE |

| 2.       | COLLECTOR | 2.        | EMITTER   | 2.        | ANODE   |

| 3.       | EMITTER   | 3.        | COLLECTOR | 3.        | GATE    |

| 4.       | COLLECTOR | 4.        | EMITTER   | 4.        | ANODE   |

| STYLE 5: |           | STYLE 6:  |           | STYLE 7:  |         |

| PIN 1.   | GATE      | PIN 1.    | ANODE     | PIN 1.    | CATHODE |

| 2.       | DRAIN     | 2.        | CATHODE   | 2.        | ANODE   |

| 3.       | SOURCE    | 3.        | ANODE     | 3.        | CATHODE |

| 4.       | DRAIN     | 4.        | CATHODE   | 4.        | ANODE   |

| STYLE 9: |           | STYLE 10: |           | STYLE 11: |         |

| PIN 1.   | GATE      | PIN 1.    | GATE      | PIN 1.    | DRAIN   |

| 2.       | COLLECTOR | 2.        | SOURCE    | 2.        | SOURCE  |

| 3.       | EMITTER   | 3.        | DRAIN     | 3.        | GATE    |

| 4.       | COLLECTOR | 4.        | SOURCE    | 4.        | SOURCE  |

|          |           |           |           |           |         |

| 3.       | MAIN TERMINAL 1<br>MAIN TERMINAL 2<br>GATE<br>MAIN TERMINAL 2 |

|----------|---------------------------------------------------------------|

| 2.<br>3. | CATHODE<br>ANODE<br>EXTERNAL TRIP/DELAY<br>ANODE              |

| DOCUMENT NUMBER: | 98AON23085D          | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TO-220, SINGLE GAUGE |                                                                                                                                                                                  | PAGE 1 OF 1 |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

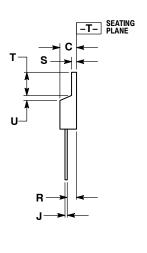

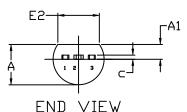

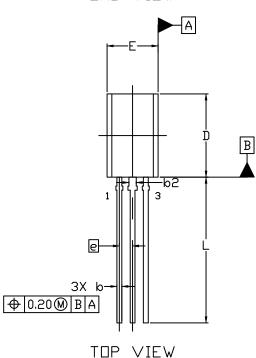

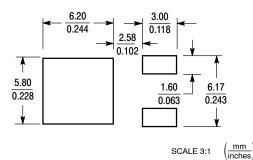

TO-92 (TO-226) 1 WATT CASE 29-10 ISSUE D

**DATE 05 MAR 2021**

#### STRAIGHT LEAD

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS.

- 4. DIMENSION 6 AND 62 DOES NOT INCLUDE DAMBAR PROTRUSION. LEAD WIDTH INCLUDING PROTRUSION SHALL NOT EXCEED 0.20. DIMENSION 62 LOCATED ABOVE THE DAMBAR PORTION OF MIDDLE LEAD.

|     | MILLIMETERS |       |       |  |  |

|-----|-------------|-------|-------|--|--|

| DIM | MIN.        | N□M.  | MAX.  |  |  |

| Δ   | 3.75        | 3.90  | 4.05  |  |  |

| A1  | 1.28        | 1.43  | 1.58  |  |  |

| Ø   | 0.38        | 0.465 | 0.55  |  |  |

| ρQ  | 0.62        | 0.70  | 0.78  |  |  |

| C   | 0.35        | 0.40  | 0.45  |  |  |

| D   | 7.85        | 8.00  | 8.15  |  |  |

| E   | 4.75        | 4.90  | 5.05  |  |  |

| E2  | 3.90        |       |       |  |  |

| е   | 1.27 BSC    |       |       |  |  |

| L   | 13.80       | 14.00 | 14.20 |  |  |

#### STYLES AND MARKING ON PAGE 3

| DOCUMENT NUMBER: | 98AON52857E           | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | TO-92 (TO-226) 1 WATT |                                                                                                                                                                                | PAGE 1 OF 3 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

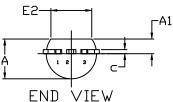

TO-92 (TO-226) 1 WATT CASE 29-10 ISSUE D

**DATE 05 MAR 2021**

#### FORMED LEAD

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS.

- 4. DIMENSION 6 AND 62 DOES NOT INCLUDE DAMBAR PROTRUSION. LEAD WIDTH INCLUDING PROTRUSION SHALL NOT EXCEED 0.20. DIMENSION 62 LOCATED ABOVE THE DAMBAR PORTION OF MIDDLE LEAD.

|     | MILLIMETERS |          |       |  |

|-----|-------------|----------|-------|--|

| DIM | MIN.        | N□M.     | MAX.  |  |

| Α   | 3.75        | 3.90     | 4.05  |  |

| A1  | 1.28        | 1.43     | 1.58  |  |

| b   | 0.38        | 0.465    | 0.55  |  |

| b2  | 0.62        | 0.70     | 0.78  |  |

| С   | 0.35        | 0.40     | 0.45  |  |

| D   | 7.85        | 8.00     | 8.15  |  |

| Е   | 4.75        | 4.90     | 5.05  |  |

| E2  | 3.90        |          |       |  |

| O.  | 2.50 BSC    |          |       |  |

| L   | 13.80       | 14.00    | 14.20 |  |

| L2  | 13.20       | 13.60    | 14.00 |  |

| L3  | ·           | 3.00 REF | ·     |  |

#### STYLES AND MARKING ON PAGE 3

| DOCUMENT NUMBER: | 98AON52857E           | Electronic versions are uncontrolled except when accessed directly from the Document Rep<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TO-92 (TO-226) 1 WATT |                                                                                                                                                                             | PAGE 2 OF 3 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### TO-92 (TO-226) 1 WATT

CASE 29-10 ISSUE D

#### **DATE 05 MAR 2021**

| 2. | EMITTER<br>BASE<br>COLLECTOR | STYLE 2:<br>PIN 1.<br>2.<br>3.  | BASE<br>EMITTER<br>COLLECTOR               | STYLE 3:<br>PIN 1.<br>2.<br>3.  | ANODE<br>ANODE<br>CATHODE    | PIN 1.<br>2. | CATHODE<br>CATHODE<br>ANODE           | STYLE 5:<br>PIN 1.<br>2.<br>3.  |                                   |

|----|------------------------------|---------------------------------|--------------------------------------------|---------------------------------|------------------------------|--------------|---------------------------------------|---------------------------------|-----------------------------------|

|    | GATE                         | PIN 1.                          | SOURCE<br>DRAIN                            | PIN 1.<br>2.                    | DRAIN                        | 2.           | BASE 1<br>EMITTER<br>BASE 2           |                                 | CATHODE<br>GATE<br>ANODE          |

| 2. | CATHODE & ANODE              | 2.                              | MAIN TERMINAL 1<br>GATE<br>MAIN TERMINAL 2 | 2.                              | ANODE 1<br>GATE<br>CATHODE 2 |              | EMITTER<br>COLLECTOR<br>BASE          | STYLE 15:<br>PIN 1.<br>2.<br>3. | ANODE 1                           |

| 2. | ANODE                        | DINI 1                          | COLLECTOR<br>BASE<br>EMITTER               | PIN 1                           | ANODE                        | PIN 1.<br>2. | GATE<br>ANODE<br>CATHODE              | 2.                              | NOT CONNECTED<br>CATHODE<br>ANODE |

| 2. |                              | PIN 1.<br>2.                    |                                            | PIN 1.<br>2.                    | GATE                         | PIN 1.<br>2. | EMITTER<br>COLLECTOR/ANODE<br>CATHODE | PIN 1.<br>2.                    | MT 1                              |

|    | V <sub>CC</sub>              |                                 | MT                                         | PIN 1.<br>2.                    |                              | PIN 1.<br>2. | NOT CONNECTED<br>ANODE<br>CATHODE     | PIN 1.<br>2.                    |                                   |

|    |                              | STYLE 32:<br>PIN 1.<br>2.<br>3. | BASE<br>COLLECTOR<br>EMITTER               | STYLE 33:<br>PIN 1.<br>2.<br>3. | RETURN                       | PIN 1.<br>2. | INPUT<br>GROUND<br>LOGIC              |                                 |                                   |

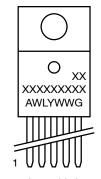

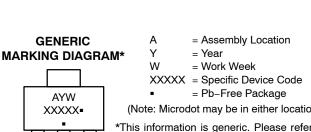

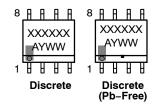

# GENERIC MARKING DIAGRAM\*

XXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON52857E           | Electronic versions are uncontrolled except when accessed directly from the Document Reposite<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TO-92 (TO-226) 1 WATT |                                                                                                                                                                                  | PAGE 3 OF 3 |  |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

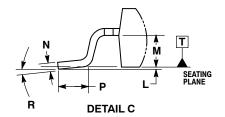

#### **TO-220 5 LEAD OFFSET CASE 314B-05 ISSUE L**

**DATE 01/07/1994**

- NOTES:

1 DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION D DOES NOT INCLUDE

INTERCONNECT BAR (DAMBAR) PROTRUSION.

DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 0.043 (1.092) MAXIMUM.

|     | INCHES    |       | MILLIMETERS |        |  |

|-----|-----------|-------|-------------|--------|--|

| DIM | MIN       | MAX   | MIN         | MAX    |  |

| Α   | 0.572     | 0.613 | 14.529      | 15.570 |  |

| В   | 0.390     | 0.415 | 9.906       | 10.541 |  |

| С   | 0.170     | 0.180 | 4.318       | 4.572  |  |

| D   | 0.025     | 0.038 | 0.635       | 0.965  |  |

| Е   | 0.048     | 0.055 | 1.219       | 1.397  |  |

| F   | 0.850     | 0.935 | 21.590      | 23.749 |  |

| G   | 0.067 BSC |       | 1.702 BSC   |        |  |

| Н   | 0.166     | BSC   | 4.216 BSC   |        |  |

| J   | 0.015     | 0.025 | 0.381       | 0.635  |  |

| K   | 0.900     | 1.100 | 22.860      | 27.940 |  |

| L   | 0.320     | 0.365 | 8.128       | 9.271  |  |

| N   | 0.320     | BSC   | 8.128 BSC   |        |  |

| Q   | 0.140     | 0.153 | 3.556       | 3.886  |  |

| S   |           | 0.620 |             | 15.748 |  |

| U   | 0.468     | 0.505 | 11.888      | 12.827 |  |

| ٧   |           | 0.735 |             | 18.669 |  |

| W   | 0.090     | 0.110 | 2.286       | 2.794  |  |

STYLE 1 THRU 4: CANCELLED

- STYLE 5: PIN 1. GATE

- 2. MIRROR 3. DRAIN

- 4. KELVIN 5. SOURCE

| DOCUMENT NUMBER: | 98ASB42218B          | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION      | TO-220 5 LEAD OFFSET | •                                                                                                                                                                               | PAGE 1 OF 1 |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

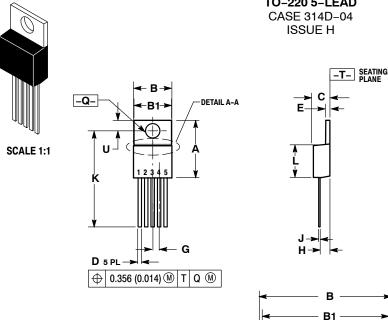

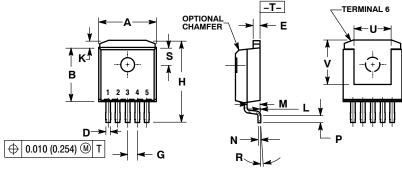

TO-220 5-LEAD

**DATE 29 JAN 2010**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M. 1982.

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION D DOES NOT INCLUDE

INTERCONNECT BAR (DAMBAR) PROTRUSION.

DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 10.92 (0.043) MAXIMUM.

|     | INCHES |       | MILLIN    | IETERS |

|-----|--------|-------|-----------|--------|

| DIM | MIN    | MAX   | MIN       | MAX    |

| Α   | 0.572  | 0.613 | 14.529    | 15.570 |

| В   | 0.390  | 0.415 | 9.906     | 10.541 |

| B1  | 0.375  | 0.415 | 9.525     | 10.541 |

| С   | 0.170  | 0.180 | 4.318     | 4.572  |

| D   | 0.025  | 0.038 | 0.635     | 0.965  |

| E   | 0.048  | 0.055 | 1.219     | 1.397  |

| G   | 0.067  | BSC   | 1.702 BSC |        |

| Н   | 0.087  | 0.112 | 2.210     | 2.845  |

| J   | 0.015  | 0.025 | 0.381     | 0.635  |

| K   | 0.977  | 1.045 | 24.810    | 26.543 |

| L   | 0.320  | 0.365 | 8.128     | 9.271  |

| Q   | 0.140  | 0.153 | 3.556     | 3.886  |

| U   | 0.105  | 0.117 | 2.667     | 2.972  |

STYLE 1 THRU 4: 1. OBSOLETE

#### **GENERIC MARKING DIAGRAM\***

= Assembly Location

WL = Wafer Lot

= Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98ASB42220B   | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TO-220 5-LEAD |                                                                                                                                                                               | PAGE 1 OF 1 |  |

**DETAIL A-A**

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

SCALE 2:1

A

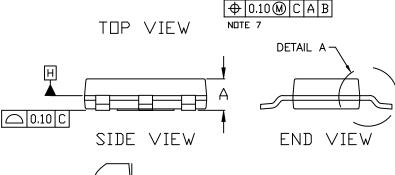

В

**DATE 13 MAY 2020**

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME

- DIMENSIDNING AND TOLERANCING PER ASME

Y14.5M, 2009.

CONTROLLING DIMENSION: MILLIMETERS

DIMENSIONS D & E1 ARE DETERMINED AT DATUM

H. DIMENSIONS DO NOT INCLUDE MOLD FLASH,

PROTRUSIONS DR GATE BURRS. SHALL NOT

EXCEED 0.23mm PER SIDE.

LEAD DIMENSIONS & AND &1 DO NOT INCLUDE

DAMBAR PROTRUSION. ALLOWABLE DAMBBAR

PROTRUSION IS 0.08mm PER SIDE.

DATUMS A AND B ARE DETERMINED AT DATUM H.

A1 IS DEFINED AS THE VERTICAL DISTANCE

FROM THE SEATING PLANE TO THE LOWEST

POINT OF THE PACKAGE BODY.

POSITIONAL TOLERANCE APPLIES TO DIMENSIONS

& AND &1.

- b AND b1.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN.        | N□M. | MAX. |  |

| Α   |             |      | 1.80 |  |

| A1  | 0.02        | 0.06 | 0.11 |  |

| b   | 0.60        | 0.74 | 0.88 |  |

| b1  | 2.90        | 3.00 | 3.10 |  |

| c   | 0.24        |      | 0.35 |  |

| D   | 6.30        | 6.50 | 6.70 |  |

| E   | 6.70        | 7.00 | 7.30 |  |

| E1  | 3.30        | 3.50 | 3.70 |  |

| е   | 2.30 BSC    |      |      |  |

| L   | 0.25        |      |      |  |

| Ŀ   | 0*          |      | 10°  |  |

(Note: Microdot may be in either location) \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

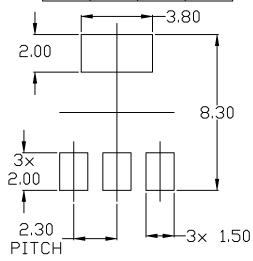

#### RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the IN Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98ASH70634A | Printed versions are uncontrolled except when accessed directly from the Document Hepos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOT-223     |                                                                                                                                                                            | PAGE 1 OF 1 |  |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

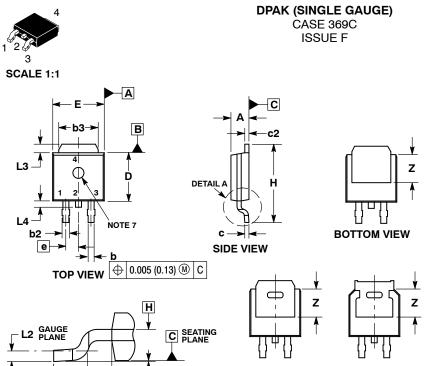

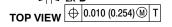

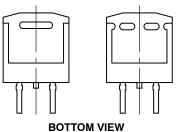

**DATE 21 JUL 2015**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: INCHES.

- 3. THERMAL PAD CONTOUR OPTIONAL WITHIN DI-

- MENSIONS b3, L3 and Z.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

5. DIMENSIONS D AND E ARE DETERMINED AT THE

- OUTERMOST EXTREMES OF THE PLASTIC BODY.

6. DATUMS A AND B ARE DETERMINED AT DATUM

- 7. OPTIONAL MOLD FEATURE.

|     | INCHES    |       | MILLIM   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.086     | 0.094 | 2.18     | 2.38   |

| A1  | 0.000     | 0.005 | 0.00     | 0.13   |

| b   | 0.025     | 0.035 | 0.63     | 0.89   |

| b2  | 0.028     | 0.045 | 0.72     | 1.14   |

| b3  | 0.180     | 0.215 | 4.57     | 5.46   |

| С   | 0.018     | 0.024 | 0.46     | 0.61   |

| c2  | 0.018     | 0.024 | 0.46     | 0.61   |

| D   | 0.235     | 0.245 | 5.97     | 6.22   |

| E   | 0.250     | 0.265 | 6.35     | 6.73   |

| е   | 0.090     | BSC   | 2.29 BSC |        |

| Н   | 0.370     | 0.410 | 9.40     | 10.41  |

| L   | 0.055     | 0.070 | 1.40     | 1.78   |

| L1  | 0.114 REF |       | 2.90 REF |        |

| L2  | 0.020 BSC |       | 0.51 BSC |        |

| L3  | 0.035     | 0.050 | 0.89     | 1.27   |

| L4  |           | 0.040 |          | 1.01   |

| Z   | 0.155     |       | 3.93     |        |

#### **GENERIC MARKING DIAGRAM\***

XXXXXX = Device Code

= Assembly Location Α

L = Wafer Lot Υ = Year WW = Work Week G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking.

# **SOLDERING FOOTPRINT\***

STYLE 8:

STYLE 3:

PIN 1. N/C 2. CATHODE

3. ANODE 4. CATHODE

PIN 1. ANODE 2. CATHODE

3. ANODE

4. CATHODE

STYLE 9:

PIN 1. ANODE 2. CATHODE

Α1

STYLE 2:

PIN 1. GATE 2. COLLECTOR

3. EMITTER 4. COLLECTOR

PIN 1. GATE 2. DRAIN

SOURCE

4. DRAIN

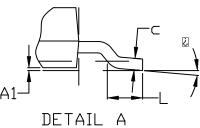

**DETAIL A** ROTATED 90° CW

STYLE 7:

STYLE 1:

STYLE 6:

PIN 1. MT1 2. MT2

3. GATE 4. MT2

PIN 1. BASE 2. COLLECTOR 3. EMITTER

4. COLLECTOR

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON10527D         | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | DPAK (SINGLE GAUGE) |                                                                                                                                                                               | PAGE 1 OF 1 |

**BOTTOM VIEW**

ALTERNATE CONSTRUCTIONS

STYLE 5:

STYLE 10:

PIN 1. GATE 2. ANODE 3. CATHODE

4. ANODE

PIN 1. CATHODE 2. ANODE

3. CATHODE 4. ANODE

STYLE 4:

PIN 1. CATHODE 2. ANODE 3. GATE

4. ANODE

3. RESISTOR ADJUST 4. CATHODE

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ÓN Semiconductor does not convey any license under its patent rights nor the rights of others

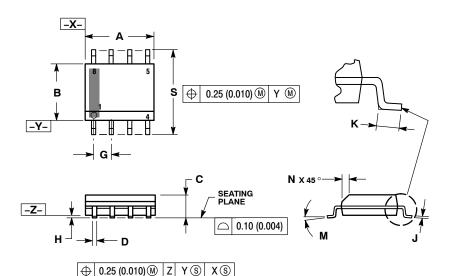

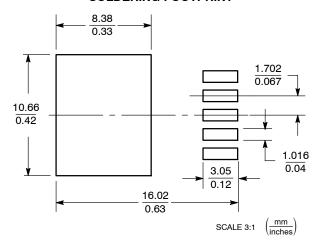

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INC       | HES   |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

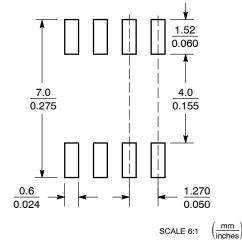

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

= Wafer Lot = Year = Work Week

= Pb-Free Package

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Docu<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in |             |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                | PAGE 1 OF 2 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

# DATE 16 FEB 2011

| STYLE 3: PIN 1. DRAIN, PIE #1 CTOR, #1 CTOR, #2 CTOR, #1 CTOR, #2 CTOR, #2 CTOR, #2 CTOR, #2 CTOR, #1 | 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE  STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #1 Vd  STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. TYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E PIN 1. INPUT 2. EXTERNAL BY 3. THIRD STAGE 4. GROUND E 5. DRAIN 6. GATE 3 7. SECOND STAGE 8. FIRST STAGE STYLE 11: ID PIN 1. SOURCE 1 2. GATE 1 T 3. SOURCE 2 ID 4. GATE 2 ID 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 ID 8. DRAIN 1 ID | PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 Vd 8. COLLECTOR, #1  STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. TYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2                                                                                                                                                                               |

| ID PIN 1. SOURCE 1 2. GATE 1 T 3. SOURCE 2 ID 4. GATE 2 ID 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 ID 8. DRAIN 1 STYLE 15: RCE PIN 1. ANODE 1 E 2. ANODE 1 RCE 3. ANODE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2                                                                                                                                                                                                                                                                                                                                 |