# 1/3-inch CMOS Digital Image Sensor

## Description

The AR0330 from ON Semiconductor is a 1/3-inch CMOS digital image sensor with an active-pixel array of 2304 (H)  $\times$  1536 (V). It can support 3.15 Mp (2048 (H)  $\times$  1536 (V)) digital still image capture and a 1080p60 + 20% EIS (2304 (H)  $\times$  1296 (V)) digital video mode. It incorporates sophisticated on-chip camera functions such as windowing, mirroring, column and row sub-sampling modes, and snapshot modes.

#### Table 1. KEY PERFORMANCE PARAMETERS

| <b>_</b>                                                                                                 |                                                                                                                                                                                                   |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter                                                                                                | Typical Value                                                                                                                                                                                     |  |  |  |  |

| Optical Format                                                                                           | 1/3-inch (6.0 mm)<br>Entire Array: 6.09 mm<br>Still Image: 5.63 mm (4:3)<br>HD Image: 5.82 mm (16:9)                                                                                              |  |  |  |  |

| Active Pixels                                                                                            | 2304 (H) × 1536 (V): (Entire Array)<br>5.07mm (H) × 3.38mm (V)<br>2048 (H) × 1536 (V) (4:3, Still Mode)<br>2304 (H) × 1296 (V) (16:9, HD Mode)                                                    |  |  |  |  |

| Pixel Size                                                                                               | $2.2 \times 2.2 \ \mu m$                                                                                                                                                                          |  |  |  |  |

| Color Filter Array                                                                                       | RGB Bayer                                                                                                                                                                                         |  |  |  |  |

| Shutter Type                                                                                             | ERS and GRR                                                                                                                                                                                       |  |  |  |  |

| Input Clock Range                                                                                        | 6–27 MHz                                                                                                                                                                                          |  |  |  |  |

| Output Clock Maximum                                                                                     | 196 Mp/s (4-lane HiSPi or MIPI)                                                                                                                                                                   |  |  |  |  |

| Output Video – 4-lane HiSPi                                                                              | 2304 × 1296 at 60 fps<br>< 450 mW (V <sub>CM</sub> 0.2 V, 198 MP/s)<br>2304 × 1296 at 30 fps<br>< 300 mW (V <sub>CM</sub> 0.2 V, 98 MP/s)                                                         |  |  |  |  |

| Responsivity                                                                                             | 2.0 V/lux-sec                                                                                                                                                                                     |  |  |  |  |

| SNR <sub>MAX</sub>                                                                                       | 39 dB                                                                                                                                                                                             |  |  |  |  |

| Dynamic Range                                                                                            | 69.5 dB                                                                                                                                                                                           |  |  |  |  |

| Supply Voltage<br>Digital<br>Analog<br>HiSPi PHY<br>HiSPi I/O (SLVS)<br>HiSPi I/O (HiVCM)<br>I/O/Digital | 1.7–1.9 V (1.8 V Nominal)<br>2.7–2.9 V<br>1.7–1.9 V (1.8 V Nominal)<br>0.3–0.9 V (0.4 or 0.8 V Nominal)<br>1.7–1.9 V (1.8 V Nominal)<br>1.7–1.9 V (1.8 V Nominal) or<br>2.4–3.1 V (2.8 V Nominal) |  |  |  |  |

| Operating Temperature<br>(Junction) –T <sub>J</sub>                                                      | -30°C to + 70°C                                                                                                                                                                                   |  |  |  |  |

| Package Options                                                                                          | CLCC - 11.4 mm × 11.4mm<br>CSP - 6.28 mm × 6.65 mm<br>Bare Die                                                                                                                                    |  |  |  |  |

# **ON Semiconductor®**

www.onsemi.com

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

## Features

- 2.2 µm Pixel with A-Pix<sup>™</sup> Technology

- Full HD support at 60 fps (2304 (H) × 1296 (V)) for Maximum Video Performance

- Superior Low-light Performance

- 3.4 Mp (3:2) and 3.15 Mp (4:3) Still Images

- Support for External Mechanical Shutter

- Support for External LED or Xenon Flash

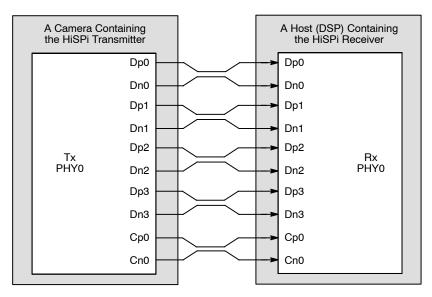

- Data Interfaces: Four-lane Serial High-speed Pixel Interface (HiSPi) Differential Signaling (SLVS), Four-lane Serial MIPI Interface, or Parallel

- On-chip Phase-locked Loop (PLL) Oscillator

- Simple Two-wire Serial Interface

- Auto Black Level Calibration

- 12-to-10 Bit Output A-Law Compression

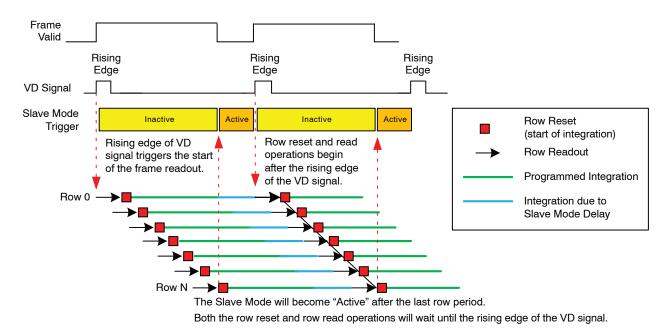

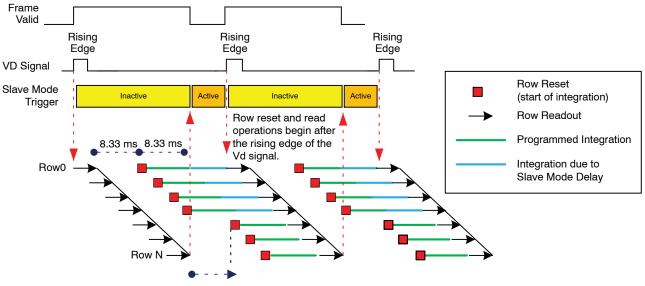

- Slave Mode for Precise Frame-rate Control and for Synchronizing Two Sensors

## Applications

- 1080p High-definition Digital Video Camcorder

- Web Cameras and Video Conferencing Cameras

- Security

## **ORDERING INFORMATION**

#### Table 2. AVAILABLE PART NUMBERS

| Part Number          | Product Description | Orderable Product Attribute Description |

|----------------------|---------------------|-----------------------------------------|

| AR0330CM1C00SHAA0-DP | 3 MP 1/3" CIS       | Dry Pack with Protective Film           |

| AR0330CM1C00SHAA0-DR | 3 MP 1/3" CIS       | Dry Pack without Protective Film        |

| AR0330CM1C00SHAA0-TP | 3 MP 1/3" CIS       | Tape & Reel with Protective Film        |

| AR0330CM1C00SHKA0-CP | 3 MP 1/3" CIS       | Chip Tray with Protective Film          |

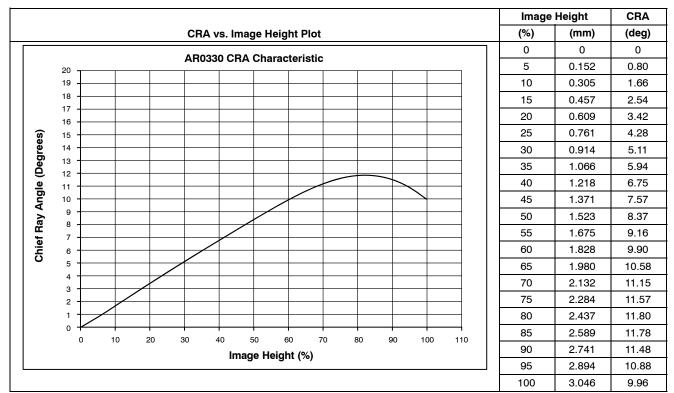

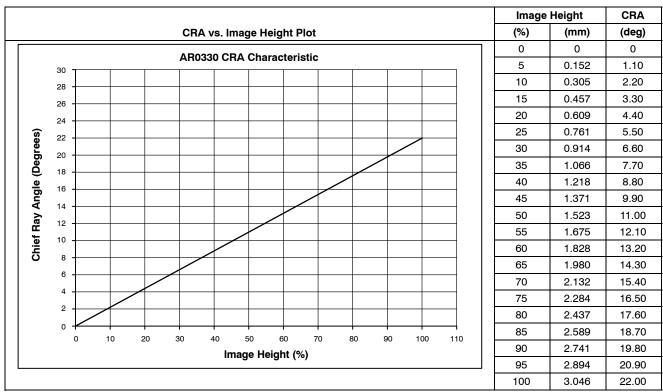

| AR0330CM1C00SHKA0-CR | 3 MP 1/3" CIS       | Chip Tray without Protective Film       |

| AR0330CM1C12SHAA0-DP | 3 MP 1/3" CIS       | Dry Pack with Protective Film           |

| AR0330CM1C12SHAA0-DR | 3 MP 1/3" CIS       | Dry Pack without Protective Film        |

| AR0330CM1C12SHKA0-CP | 3 MP 1/3" CIS       | Chip Tray with Protective Film          |

| AR0330CM1C12SHKA0-CR | 3 MP 1/3" CIS       | Chip Tray without Protective Film       |

| AR0330CM1C21SHKA0-CP | 3 MP 1/3" CIS       | Chip Tray with Protective Film          |

| AR0330CM1C21SHKA0-CR | 3 MP 1/3" CIS       | Chip Tray without Protective Film       |

#### **GENERAL DESCRIPTION**

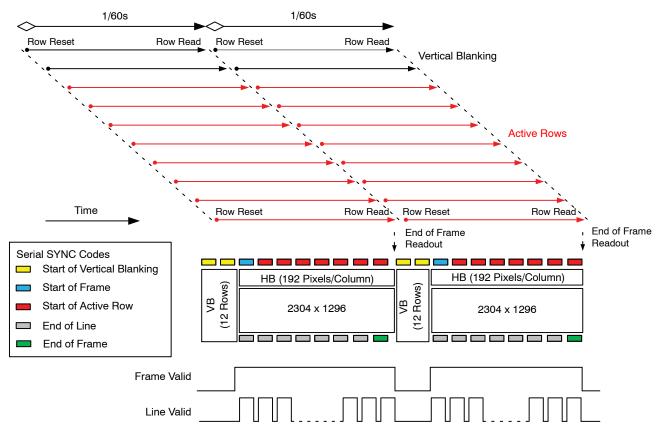

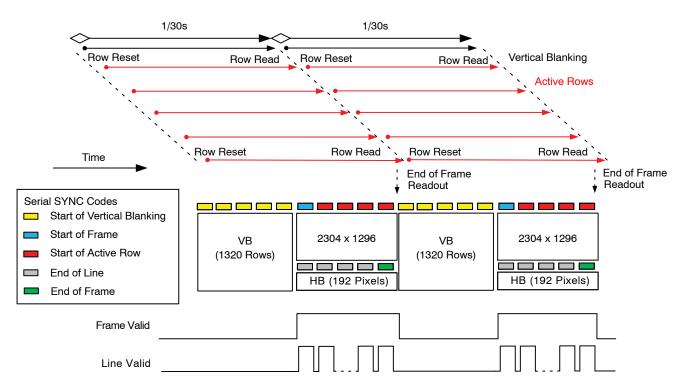

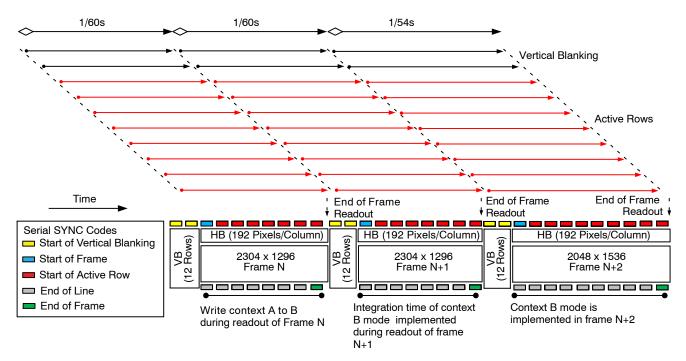

The AR0330 can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a  $2304 \times 1296$  image at 60 frames per second (fps). The sensor outputs 10- or 12-bit raw data, using either the parallel or serial (HiSPi, MIPI) output ports.

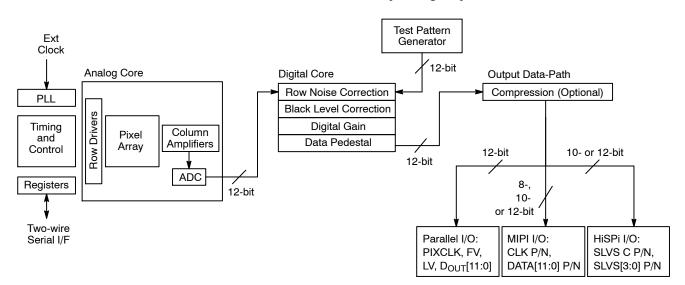

## **FUNCTIONAL OVERVIEW**

The AR0330 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip, phase-locked loop (PLL) that can generate all internal clocks from a single master input clock running between 6 and 27 MHz. The maximum output pixel rate is 196 Mp/s using a 4-lane HiSPi or MIPI serial interface and 98 Mp/s using the parallel interface.

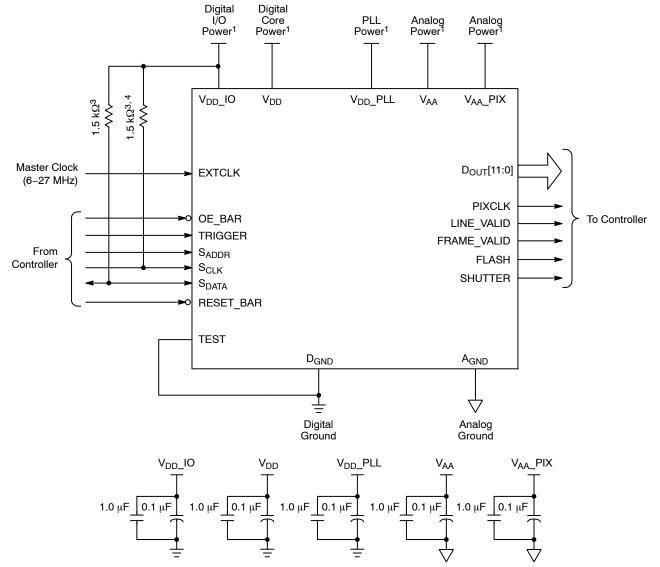

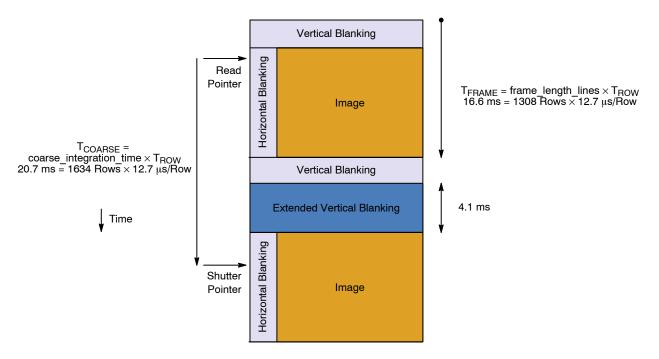

Figure 1. Block Diagram

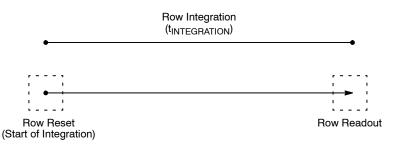

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 3.4 Mp active-pixel sensor array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the signal from the column is amplified in a column amplifier and then digitized in an analog-to-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain).

# WORKING MODES

The AR0330 sensor working modes are specified from the following aspect ratios:

## Table 3. AVAILABLE ASPECT RATIOS IN THE AR0330 SENSOR

| Aspect Ratio        |                 | Sensor Array Usage  |

|---------------------|-----------------|---------------------|

| 3:2 Still Format #1 |                 | 2256 (H) × 1504 (V) |

| 4:3 Still Format #2 |                 | 2048 (H) × 1536 (V) |

| 16:10               | Still Format #3 | 2256 (H) × 1440 (V) |

| 16:9                | HD Format       | 2304 (H) × 1296 (V) |

The AR0330 supports the following working modes. To operate the sensor at full speed (196 Mp/s) the sensor must use the 4-lane HiSPi or MIPI interface. The sensor will

operate at half-speed (98 Mp/s) when using the parallel interface.

| Mode                      | Aspect<br>Ratio | Active<br>Readout<br>Window | Sensor<br>Output<br>Resolution | FPS<br>(4-lane MIPI∕<br>HiSPi Interface) | FPS<br>(Parallel Interface) | Subsampling | FOV  |

|---------------------------|-----------------|-----------------------------|--------------------------------|------------------------------------------|-----------------------------|-------------|------|

| 1080p + EIS               | 16:9            | $2304 \times 1296$          | 2304 × 1296                    | 60                                       | N/A                         | -           | 100% |

|                           |                 |                             |                                | 30                                       | 30                          | -           | 100% |

| 3M Still                  | 4:3             | 2048 	imes 1536             | 2048 × 1536                    | 30                                       | 25                          | -           | 100% |

|                           | 3:2             | $2256 \times 1504$          | 2256 × 1504                    | 30                                       | 25                          | -           | 100% |

| WVGA + EIS                | 16:9            | 2304 × 1296                 | 1152 × 648                     | 60                                       | 60                          | 2×2         | 100% |

| WVGA + EIS<br>Slow-motion | 16:9            | 2304 × 1296                 | 1152 × 648                     | 120                                      | N/A                         | 2×2         | 100% |

| VGA Video                 | 16:10           | $2256 \times 1440$          | 752 × 480                      | 60                                       | 60                          | 3×3         | 96%  |

| VGA Video<br>Slow-motion  | 16:10           | 2256 × 1440                 | 752 × 480                      | 215                                      | 107                         | 3×3         | 96%  |

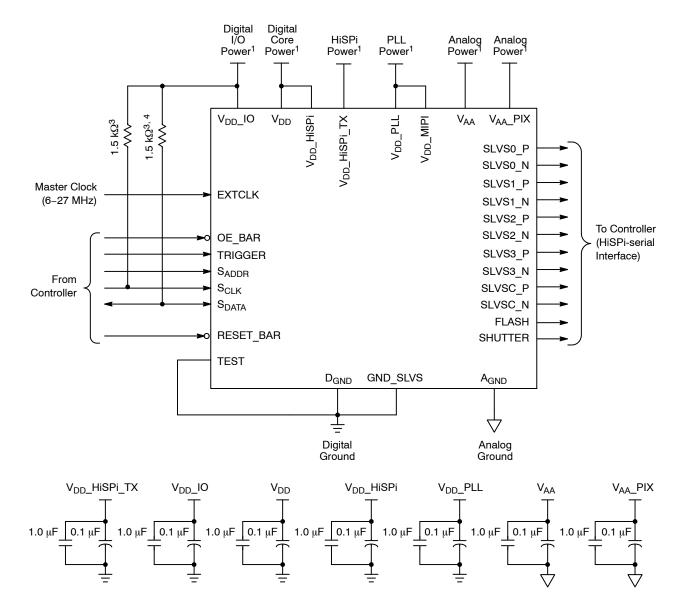

## **HiSPi POWER SUPPLY CONNECTIONS**

The HiSPi interface requires two power supplies. The  $V_{DD}$ -HiSPi powers the digital logic while the  $V_{DD}$ -HiSPi\_TX powers the output drivers. The digital logic supply is a nominal 1.8 V and ranges from 1.7 to 1.9 V. The HiSPi drivers can receive a supply voltage of 0.4 to 0.8 V or 1.7 to 1.9 V.

The common mode voltage is derived as half of the  $V_{DD}$ \_HiSPi\_TX supply. Two settings are available for the output common mode voltage:

1. SLVS Mode:

The V<sub>DD</sub>\_HiSPi\_Tx supply must be in the range of 0.4 to 0.8 V and the high\_vcm register bit R0x306E[9] must be set to "0". The output common mode voltage will be in the range of 0.2 to 0.4 V.

2. HiVCM Mode:

The V<sub>DD</sub>\_HiSPi\_Tx supply must be in the range of 1.7 to 1.9 V and the high\_vcm register bit R0x306E[9] must be set to "1". The output common mode voltage will be in the range of 0.76 to 1.07 V.

Two prior naming conventions have also been used with the  $V_{DD}$ \_HiSPi and  $V_{DD}$ \_HiSPi\_TX pins:

- 1. Digital logic supply was named V<sub>DD</sub>\_SLVS while the driver supply was named V<sub>DD</sub>\_SLVS\_TX.

- 2. Digital logic supply was named  $V_{DD}$ \_PHY while the driver supply was named  $V_{DD}$ \_SLVS.

## **TYPICAL CONFIGURATIONS**

#### Notes:

- 1. All power supplies must be adequately decoupled. ON Semiconductor recommends having 1.0 µF and 0.1 µF decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: VAA, VAA\_PIX, VDD\_PLL, VDD\_IO, and VDD. Actual values and results may vary depending on layout and design considerations.

- 2. To allow for space constraints, ON Semiconductor recommends having 0.1 µF decoupling capacitor inside the module as close to the pads as possible. In addition, place a 10 µF capacitor for each supply off-module but close to each supply.

- 3. ON Semiconductor recommends a resistor value of 1.5 kΩ, but a greater value may be used for slower two-wire speed.

- This pull-up resistor is not required if the controller drives a valid logic level on S<sub>CLK</sub> at all times. 4

- 5. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- TEST pin should be tied to D<sub>GND</sub>. 6.

- Set High VCM (R0x306E[9]) to 0 (default) to use the VDD HiSPi TX in the range of 0.4-0.8 V. Set High VCM to 1 to use a range of 7. 1.7–1.9 V.

- The package pins or die pads used for the MIPI data and clock as well as the parallel interface must be left floating. 8.

- 9. The V<sub>DD</sub>\_MIPI package pin and sensor die pad should be connected to a 2.8 V supply as V<sub>DD</sub>\_MIPI is tied to the V<sub>DD</sub>\_PLL supply both in the package routing and also within the sensor die itself.

- 10. If the SHUTTER or FLASH pins or pads are not used, then they must be left floating.

- 11. If the TRIGGER pin or pad is not used then it should be tied to  $D_{GND}$ . 12. The GND\_SLVS pad must be tied to  $D_{GND}$ . It is connected this way in the CLCC and CSP packages.

#### Figure 2. Serial 4-lane HiSPi Interface

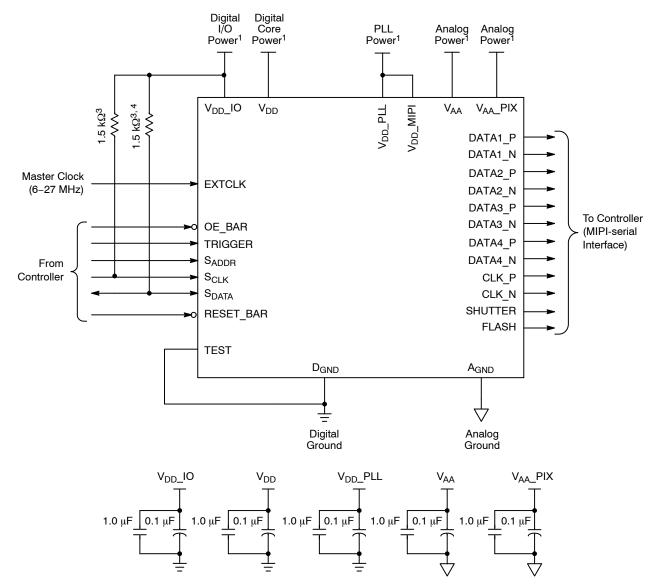

#### Notes:

- All power supplies must be adequately decoupled. ON Semiconductor recommends having 1.0 μF and 0.1 μF decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: V<sub>AA</sub>, V<sub>AA</sub>\_PIX, V<sub>DD</sub>\_PLL, V<sub>DD</sub>\_MIPI, V<sub>DD</sub>\_IO, and V<sub>DD</sub>. Actual values and results may vary depending on layout and design considerations.

- To allow for space constraints, ON Semiconductor recommends having 0.1 μF decoupling capacitor inside the module as close to the pads as possible. In addition, place a 10 μF capacitor for each supply off-module but close to each supply.

- 3. ON Semiconductor recommends a resistor value of 1.5 k $\Omega$ , but a greater value may be used for slower two-wire speed.

- This pull-up resistor is not required if the controller drives a valid logic level on S<sub>CLK</sub> at all times.

- 5. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. TEST pin must be tied to  $D_{GND}$  for the MIPI configuration.

- 7. ON Semiconductor recommends that GND\_MIPI be tied to D<sub>GND</sub>.

- 8. V<sub>DD</sub>\_MIPI is tied to V<sub>DD</sub>\_PLL in both the CLCC and the CSP package. ON Semiconductor strongly recommends that V<sub>DD</sub>\_MIPI must be connected to a V<sub>DD</sub>\_PLL in a module design since V<sub>DD</sub>\_PLL and V<sub>DD</sub>\_MIPI are tied together in the die.

- 9. The package pins or die pads used for the HiSPi data and clock as well as the parallel interface must be left floating.

- 10. HiSPi Power Supplies (V<sub>DD</sub>\_HISPI and V<sub>DD</sub>\_HISPI\_TX) can be tied to ground.

- 11. If the SHUTTER or FLASH pins or pads are not used, then they must be left floating.

- 12. If the TRIGGER pin or pad is not used then it should be tied to  $D_{GND}$ .

#### Figure 3. Serial MIPI

Notes:

- All power supplies must be adequately decoupled. ON Semiconductor recommends having 1.0 μF and 0.1 μF decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: V<sub>AA</sub>, V<sub>AA</sub>\_PIX, V<sub>DD</sub>\_PLL, V<sub>DD</sub>\_IO, and V<sub>DD</sub>. Actual values and results may vary depending on layout and design considerations.

- To allow for space constraints, ON Semiconductor recommends having 0.1 μF decoupling capacitor inside the module as close to the pads as possible. In addition, place a 10 μF capacitor for each supply off-module but close to each supply.

- 3. ON Semiconductor recommends a resistor value of 1.5 k $\Omega$ , but a greater value may be used for slower two-wire speed.

- 4. This pull-up resistor is not required if the controller drives a valid logic level on S<sub>CLK</sub> at all times.

- 5. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. TEST pin should be tied to the ground.

- 7. The data and clock package pins or die pads used for the HiSPi and MIPI interface must be left floating.

- The V<sub>DD</sub>\_MIPI package pin and sensor die pad should be connected to a 2.8 V supply as it is tied to the V<sub>DD</sub>\_PLL supply both in the package routing and also within the sensor die itself. HiSPi Power Supplies (V<sub>DD</sub>\_HISPI and V<sub>DD</sub>\_HISPI\_TX) can be tied to ground.

If the SHUTTER or FLASH pins or pads are not used, then they must be left floating.

- 9. If the SHUTTER of FLASH pins of page are not used, then they must be ren 10. If the TRICCER pin or pad is not used then it should be tied to David

- 10. If the TRIGGER pin or pad is not used then it should be tied to  $\mathsf{D}_{\text{GND}}.$

#### Figure 4. Parallel Pixel Data Interface

# **PIN DESCRIPTIONS**

## Table 5. PIN DESCRIPTIONS

| RESET_BAR               |        |                                                                                                                   |

|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------|

|                         | Input  | Asynchronous reset (active LOW). All settings are restored to factory default.                                    |

| EXTCLK                  | Input  | Master input clock, range 6-27 MHz.                                                                               |

| OE_BAR                  | Input  | Output enable (active LOW). Only available on bare die version.                                                   |

| TRIGGER                 | Input  | Receives slave mode VD signal for frame rate synchronization and trigger to start a GRR frame.                    |

| S <sub>ADDR</sub>       | Input  | Two-wire serial address select.                                                                                   |

| S <sub>CLK</sub>        | Input  | Two-wire serial clock input.                                                                                      |

| S <sub>DATA</sub>       | I/O    | Two-wire serial data I/O.                                                                                         |

| PIXCLK                  | Output | Pixel clock out. D <sub>OUT</sub> is valid on rising edge of this clock.                                          |

| D <sub>OUT</sub> [11:0] | Output | Parallel pixel data output.                                                                                       |

| FLASH                   | Output | Flash output. Synchronization pulse for external light source. Can be left floating if not used.                  |

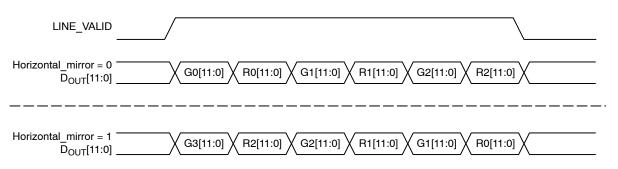

| FRAME_VALID             | Output | Asserted when D <sub>OUT</sub> data is valid.                                                                     |

| LINE_VALID              | Output | Asserted when D <sub>OUT</sub> data is valid.                                                                     |

| V <sub>DD</sub>         | Power  | Digital power.                                                                                                    |

| V <sub>DD</sub> _IO     | Power  | IO supply power.                                                                                                  |

| V <sub>DD</sub> _PLL    | Power  | PLL power supply. The MIPI power supply (V <sub>DD</sub> _MIPI) is tied to V <sub>DD</sub> _PLL in both packages. |

| D <sub>GND</sub>        | Power  | Digital GND.                                                                                                      |

| V <sub>AA</sub>         | Power  | Analog power.                                                                                                     |

| V <sub>AA</sub> _PIX    | Power  | Pixel power.                                                                                                      |

| A <sub>GND</sub>        | Power  | Analog GND.                                                                                                       |

| TEST                    | Input  | Enable manufacturing test modes. Tie to D <sub>GND</sub> for normal sensor operation.                             |

| SHUTTER                 | Output | Control for external mechanical shutter. Can be left floating if not used.                                        |

| SLVS0_P                 | Output | HiSPi serial data, lane 0, differential P.                                                                        |

| SLVS0_N                 | Output | HiSPi serial data, lane 0, differential N.                                                                        |

| SLVS1_P                 | Output | HiSPi serial data, lane 1, differential P.                                                                        |

| SLVS1_N                 | Output | HiSPi serial data, lane 1, differential N.                                                                        |

| SLVS2_P                 | Output | HiSPi serial data, lane 2, differential P.                                                                        |

| SLVS2_N                 | Output | HiSPi serial data, lane 2, differential N.                                                                        |

| SLVS3_P                 | Output | HiSPi serial data, lane 3, differential P.                                                                        |

| SLVS3_N                 | Output | HiSPi serial data, lane 3, differential N.                                                                        |

| SLVSC_P                 | Output | HiSPi serial DDR clock differential P.                                                                            |

| SLVSC_N                 | Output | HiSPi serial DDR clock differential N.                                                                            |

| DATA1_P                 | Output | MIPI serial data, lane 1, differential P.                                                                         |

| DATA1_N                 | Output | MIPI serial data, lane 1, differential N.                                                                         |

| DATA2_P                 | Output | MIPI serial data, lane 2, differential P.                                                                         |

| DATA2_N                 | Output | MIPI serial data, lane 2, differential N.                                                                         |

| DATA3_P                 | Output | MIPI serial data, lane 3, differential P.                                                                         |

| DATA3_N                 | Output | MIPI serial data, lane 3, differential N.                                                                         |

| DATA4_P                 | Output | MIPI serial data, lane 4, differential P.                                                                         |

| DATA4_N                 | Output | MIPI serial data, lane 4, differential N.                                                                         |

## Table 5. PIN DESCRIPTIONS (continued)

| Name                      | Туре   | Description                                                                                                                      |

|---------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| CLK_P                     | Output | Output MIPI serial clock, differential P.                                                                                        |

| CLK_N                     | Output | Output MIPI serial clock, differential N.                                                                                        |

| V <sub>DD</sub> _HiSPi    | Power  | 1.8 V power port to HiSPi digital logic.                                                                                         |

| V <sub>DD</sub> _HiSPi_TX | Power  | 0.4–0.8 V or 1.7–1.9 V. Refer to "HiSPi Power Supply Connections".                                                               |

| V <sub>AA</sub> _HV_NPIX  | Power  | Power supply pin used to program the sensor OTPM (one-time programmable memory).<br>This pin should be open if OTPM is not used. |

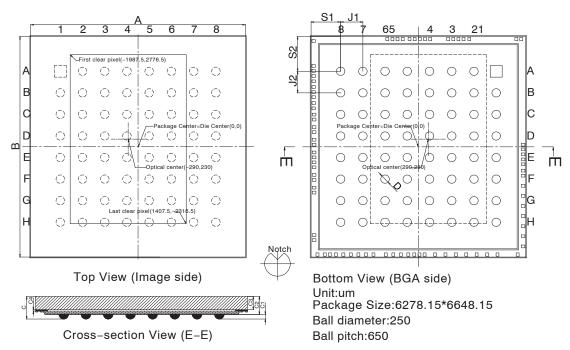

#### Table 6. CSP (HiSPi/MIPI) PACKAGE PINOUT

| · · · · · |                     |                          |                      |                     |                      |                 |                           |                        |

|-----------|---------------------|--------------------------|----------------------|---------------------|----------------------|-----------------|---------------------------|------------------------|

|           | 1                   | 2                        | 3                    | 4                   | 5                    | 6               | 7                         | 8                      |

| Α         | V <sub>AA</sub>     | V <sub>AA</sub> _HV_NPIX | A <sub>GND</sub>     | A <sub>GND</sub>    | V <sub>AA</sub>      | V <sub>DD</sub> | TEST                      | D <sub>GND</sub>       |

| в         | D <sub>GND</sub>    | NC                       | V <sub>AA</sub> _PIX | D <sub>GND</sub>    | V <sub>DD</sub> _IO  | TRIGGER         | RESET_BAR                 | EXTCLK                 |

| С         | V <sub>DD</sub>     | SHUTTER                  | D <sub>GND</sub>     | SLVSC_P             | SLVS3_P              | SLVS3_N         | SLVS2_N                   | SLVS2_P                |

| D         | S <sub>ADDR</sub>   | S <sub>CLK</sub>         | SDATA                | FLASH               | SLVSC_N              | SLVS1_P         | V <sub>DD</sub> _HiSPi_TX | V <sub>DD</sub> _HiSPi |

| Е         | V <sub>DD</sub> _IO | V <sub>DD</sub> _IO      | CLK_N                | CLK_P               | D <sub>GND</sub>     | SLVS1_N         | SLVS0_N                   | SLVS0_P                |

| F         | D <sub>GND</sub>    | V <sub>DD</sub> _IO      | D <sub>GND</sub>     | D <sub>GND</sub>    | DATA4_P              | DATA_N          | DATA_P                    | V <sub>DD</sub> _PLL   |

| G         | V <sub>DD</sub> _IO | V <sub>DD</sub>          | D <sub>GND</sub>     | V <sub>DD</sub> _IO | DATA4_N              | DATA3_N         | DATA2_N                   | V <sub>DD</sub>        |

| Н         | D <sub>GND</sub>    | V <sub>DD</sub> _IO      | V <sub>DD</sub> _IO  | D <sub>GND</sub>    | V <sub>DD</sub> _PLL | DATA3_P         | DATA2_P                   | V <sub>DD</sub> _PLL   |

NOTE: NC = No Connection.

NOTE: Pins labeled NC (Not Connected) should be tied to ground.

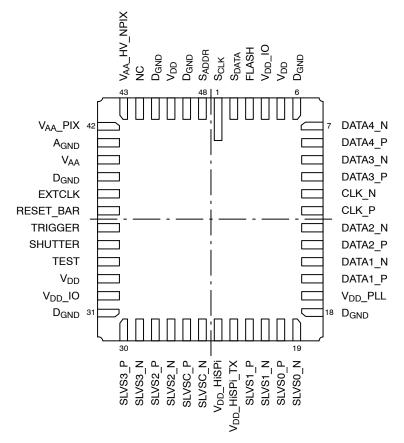

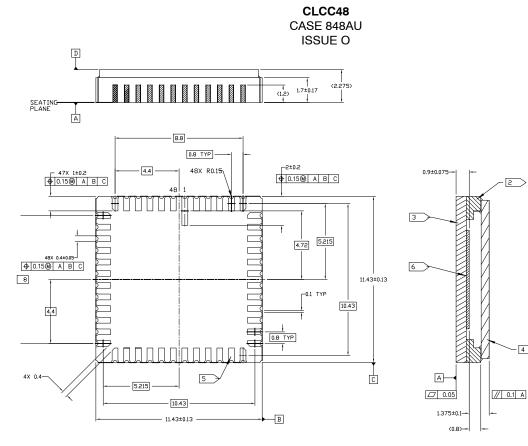

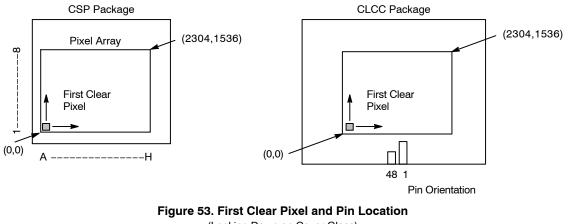

Figure 5. CLCC Package Pin Descriptions

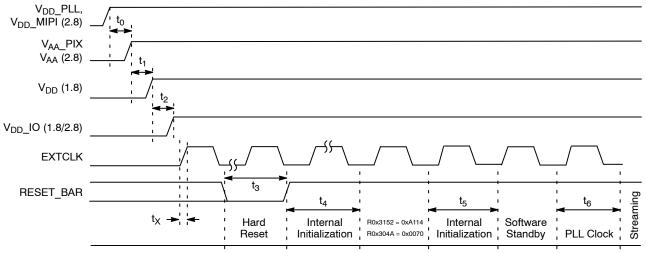

## SENSOR INITIALIZATION

#### Power-Up Sequence

The recommended power-up sequence for the AR0330CS is shown in Figure 6. The available power supplies ( $V_{DD}$ \_IO,  $V_{DD}$ \_PLL,  $V_{DD}$ \_MIPI,  $V_{AA}$ ,  $V_{AA}$ \_PIX) must have the separation specified below.

- 1. Turn on  $V_{DD}$ \_PLL and  $V_{DD}$ \_MIPI power supplies.

- 2. After 100  $\mu$ s, turn on V<sub>AA</sub> and V<sub>AA</sub>\_PIX power supply.

- 3. After 100  $\mu$ s, turn on V<sub>DD</sub> power supply.

- 4. After 100 µs, turn on V<sub>DD</sub>\_IO power supply.

- 5. After the last power supply is stable, enable EXTCLK.

- 6. Assert RESET\_BAR for at least 1 ms.

- 7. Wait 150,000 EXTCLK periods (for internal initialization into software standby.

- 8. Write R0x3152 = 0xA114 to configure the internal register initialization process.

- 9. Write R0x304A = 0x0070 to start the internal register initialization process.

- 10. Wait 150,000 EXTCLK periods.

- 11. Configure PLL, output, and image settings to desired values.

- 12. Wait 1ms for the PLL to lock.

- 13. Set streaming mode (R0x301A[2] = 1).

#### Notes:

- 1. A software reset (R0x301A[0] = 1) is not necessary after the procedure described above since a Hard Reset will automatically triggers a software reset. Independently executing a software reset, should be followed by steps seven through thirteen above.

- 2. The sensor must be receiving the external input clock (EXTCLK) before the reset pin is toggled. The sensor will begin an internal initialization sequence when the reset pin toggle from LOW to HIGH. This initialization sequence will run using the external input clock. Power on default state is software standby state, need to apply two-wire serial commands to start streaming. Above power up sequence is a general power up sequence. For different interface configurations, MIPI, and Parallel, some power rails are not needed. Those not needed power rails should be ignored in the general power up sequence.

#### Figure 6. Power Up

#### Table 7. POWER-UP SEQUENCE

| Symbol         | Definition                                                                                    | Min    | Тур | Max | Unit    |

|----------------|-----------------------------------------------------------------------------------------------|--------|-----|-----|---------|

| to             | V <sub>DD</sub> _PLL, V <sub>DD</sub> _MIPI to V <sub>AA</sub> /V <sub>AA</sub> _PIX (Note 3) | 0      | 100 | -   | μs      |

| t <sub>1</sub> | $V_{AA}/V_{AA}$ _PIX to $V_{DD}$                                                              | 0      | 100 | -   | μs      |

| t <sub>2</sub> | V <sub>DD</sub> to V <sub>DD</sub> IO                                                         | 0      | 100 | -   | μs      |

| t <sub>X</sub> | External Clock Settling Time (Note 1)                                                         | -      | 30  | -   | ms      |

| t <sub>3</sub> | Hard Reset (Note 2)                                                                           | 1      | -   | -   | ms      |

| t <sub>4</sub> | Internal Initialization                                                                       | 150000 | -   | -   | EXTCLKs |

| t <sub>5</sub> | Internal Initialization                                                                       | 150000 | -   | -   | EXTCLKs |

| t <sub>6</sub> | PLL Lock Time                                                                                 | 1      | -   | -   | ms      |

1. External clock settling time is component-dependent, usually taking about 10-100 ms.

2. Hard reset time is the minimum time required after power rails are settled. In a circuit where Hard reset is held down by RC circuit, then the RC time must include the all power rail settle time and Xtal settle time.

It is critical that V<sub>DD</sub>\_PLL is not powered up after the other power supplies. It must be powered before or at least at the same time as the others. If the case happens that V<sub>DD</sub>\_PLL is powered after other supplies then sensor may have functionality issues and will experience high current draw on this supply.

4. V<sub>DD</sub>\_MIPI is tied to V<sub>DD</sub>\_PLL in the both the CLCC and CSP packages and must be powered to 2.8 V. The V<sub>DD</sub>\_HiSPi and V<sub>DD</sub>\_HiSPi\_TX supplies do not need to be turned on if the sensor is configured to use the MIPI or parallel interface.

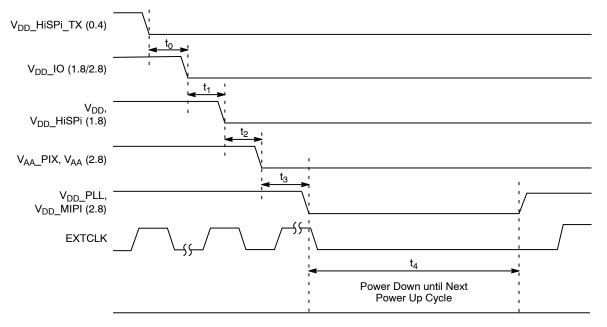

## **Power-Down Sequence**

The recommended power-down sequence for the AR0330 is shown in Figure 7. The available power supplies ( $V_{DD}$ \_IO,  $V_{DD}$ \_HiSPi,  $V_{DD}$ \_HiSPi\_TX,  $V_{DD}$ \_PLL,  $V_{DD}$ \_MIPI,  $V_{AA}$ ,  $V_{AA}$ \_PIX) must have the separation specified below.

- 1. Disable streaming if output is active by setting standby R0x301a[2] = 0.

- 2. The soft standby state is reached after the current row or frame, depending on configuration, has ended.

- 3. Turn off V<sub>DD</sub>\_HiSPi\_TX.

- 4. Turn off V<sub>DD</sub>\_IO.

- 5. Turn off V<sub>DD</sub> and V<sub>DD</sub>\_HiSPi.

- 6. Turn off  $V_{AA}/V_{AA}$ \_PIX.

- 7. Turn off V<sub>DD</sub>\_PLL, V<sub>DD</sub>\_MIPI.

## Figure 7. Power Down

#### Table 8. POWER-DOWN SEQUENCE

| Symbol         | Parameter                                                         | Min | Тур | Max | Unit |

|----------------|-------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>0</sub> | V <sub>DD</sub> _HiSPi_TX to V <sub>DD</sub> _IO                  | 0   | -   | -   | μs   |

| t <sub>1</sub> | V <sub>DD</sub> _IO to V <sub>DD</sub> and V <sub>DD</sub> _HiSPi | 0   | -   | -   | μs   |

| t <sub>2</sub> | $V_{DD}$ and $V_{DD}\_HiSPi$ to $V_{AA}/V_{AA}\_PIX$              | 0   | _   | —   | μs   |

| t <sub>3</sub> | V <sub>AA</sub> /V <sub>AA</sub> _PIX to V <sub>DD</sub> _PLL     | 0   | _   |     | μs   |

| t <sub>4</sub> | PwrDn until Next PwrUp Time                                       | 100 | _   | _   | ms   |

NOTE: t<sub>4</sub> is required between power down and next power up time; all decoupling caps from regulators must be completely discharged.

## **ELECTRICAL CHARACTERISTICS**

## Table 9. DC ELECTRICAL DEFINITIONS AND CHARACTERISTICS (MIPI MODE)

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{DD} IO = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA} PIX = 2.8 \text{ V}; V_{DD} PLL = 2.8 \text{ V}; Output Load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; Data Rate = 588 \text{ Mbps}; 2304 \times 1296 \text{ at } 60 \text{ fps})$

| Symbol                    | Definition                     | Min        | Тур        | Max        | Unit |

|---------------------------|--------------------------------|------------|------------|------------|------|

| V <sub>DD</sub>           | Core Digital Voltage           | 1.7        | 1.8        | 1.9        | V    |

| V <sub>DD</sub> IO        | I/O Digital Voltage            | 1.7<br>2.4 | 1.8<br>2.8 | 1.9<br>3.1 | V    |

| V <sub>AA</sub>           | Analog Voltage                 | 2.7        | 2.8        | 2.9        | V    |

| V <sub>AA</sub> _PIX      | Pixel Supply Voltage           | 2.7        | 2.8        | 2.9        | V    |

| V <sub>DD</sub> _PLL      | PLL Supply Voltage             | 2.7        | 2.8        | 2.9        | V    |

| V <sub>DD</sub> _MIPI     | MIPI Supply Voltage            | 2.7        | 2.8        | 2.9        | V    |

| I (V <sub>DD</sub> )      | Digital Operating Current      | -          | 114        | 136        | mA   |

| I (V <sub>DD</sub> IO)    | I/O Digital Operating Current  | -          | 0          | 0          | mA   |

| I (V <sub>AA</sub> )      | Analog Operating Current       | -          | 41         | 53         | mA   |

| I (V <sub>AA</sub> _PIX)  | Pixel Supply Current           | -          | 9.9        | 12         | mA   |

| I (V <sub>DD</sub> PLL)   | PLL Supply Current             | -          | 15         | 27         | mA   |

| I (V <sub>DD</sub> _MIPI) | MIPI Digital Operating Current | -          | 35         | 49         | mA   |

## Table 10. DC ELECTRICAL DEFINITIONS AND CHARACTERISTICS (HiSPi MODE)

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{DD}\_IO = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA}\_PIX = 2.8 \text{ V}; V_{DD}\_PLL = 2.8 \text{ V}; V_{DD}\_HiSPi = 1.8 \text{ V}, V_{DD}\_HiSPi\_TX = 0.4 \text{ V}; Output Load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; Data Rate = 588 \text{ Mbps}; DLL Set to 0; 2304 × 1296 at 60 \text{ fps})$

|                               |                                     | • •        | ,          |            |      |

|-------------------------------|-------------------------------------|------------|------------|------------|------|

| Symbol                        | Definition                          | Min        | Тур        | Max        | Unit |

| V <sub>DD</sub>               | Core Digital Voltage                | 1.7        | 1.8        | 1.9        | V    |

| V <sub>DD</sub> _IO           | I/O Digital Voltage                 | 1.7<br>2.4 | 1.8<br>2.8 | 1.9<br>3.1 | V    |

| V <sub>AA</sub>               | Analog Voltage                      | 2.7        | 2.8        | 2.9        | V    |

| V <sub>AA</sub> _PIX          | Pixel Supply Voltage                | 2.7        | 2.8        | 2.9        | V    |

| V <sub>DD</sub> _PLL          | PLL Supply Voltage                  | 2.7        | 2.8        | 2.9        | V    |

| V <sub>DD</sub> _HiSPi        | HiSPi Digital Voltage               | 1.7        | 1.8        | 1.9        | V    |

| V <sub>DD</sub> _HiSPi_TX     | HiSPi I/O Digital Voltage           | 0.3<br>1.7 | 0.4<br>1.8 | 0.9<br>1.9 | V    |

| I (V <sub>DD</sub> )          | Digital Operating Current           | _          | 96.3       | 137        | mA   |

| I (V <sub>DD</sub> _IO)       | I/O Digital Operating Current       | -          | 0          | 0          | mA   |

| I (V <sub>AA</sub> )          | Analog Operating Current            | _          | 45.1       | 53         | mA   |

| I (V <sub>AA</sub> _PIX)      | Pixel Supply Current                | -          | 10.5       | 12         | mA   |

| I (V <sub>DD</sub> PLL)       | PLL Supply Current                  | -          | 6.4        | 11         | mA   |

| I (V <sub>DD</sub> _HiSPi)    | HiSPi Digital Operating Current     | -          | 21.8       | 36         | mA   |

| I (V <sub>DD</sub> _HiSPi_TX) | HiSPi I/O Digital Operating Current | _          | 22.3       | 40         | mA   |

#### Table 11. DC ELECTRICAL DEFINITIONS AND CHARACTERISTICS (PARALLEL MODE)

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{DD}IO = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA}PIX = 2.8 \text{ V}; V_{DD}PLL = 2.8 \text{ V}; Output Load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; 2304 \times 1296 \text{ at } 30 \text{ fps})$

| Symbol                   | Definition                    | Min        | Тур        | Мах        | Unit |

|--------------------------|-------------------------------|------------|------------|------------|------|

| V <sub>DD</sub>          | Core Digital Voltage          | 1.7        | 1.8        | 1.9        | V    |

| V <sub>DD</sub> _IO      | I/O Digital Voltage           | 1.7<br>2.4 | 1.8<br>2.8 | 1.9<br>3.1 | V    |

| V <sub>AA</sub>          | Analog Voltage                | 2.7        | 2.8        | 2.9        | V    |

| V <sub>AA</sub> _PIX     | Pixel Supply Voltage          | 2.7        | 2.8        | 2.9        | V    |

| V <sub>DD</sub> _PLL     | PLL Supply Voltage            | 2.7        | 2.8        | 2.9        | V    |

| I (V <sub>DD</sub> )     | Digital Operating Current     | -          | 66.5       | 75         | mA   |

| I (V <sub>DD</sub> _IO)  | I/O Digital Operating Current | -          | 24         | 35         | mA   |

| I (V <sub>AA</sub> )     | Analog Operating Current      | -          | 36         | 44         | mA   |

| I (V <sub>AA</sub> _PIX) | Pixel Supply Current          | -          | 10.5       | 18         | mA   |

| I (V <sub>DD</sub> _PLL) | PLL Supply Current            | -          | 6          | 11         | mA   |

## Table 12. STANDBY POWER

$(f_{EXTCLK} = 24 \text{ MHz}; \text{ } \text{V}_{DD} = 1.8 \text{ } \text{V}; \text{ } \text{V}_{DD} \text{ } \text{ } \text{IO} = 1.8 \text{ } \text{V}; \text{ } \text{V}_{AA} = 2.8 \text{ } \text{V}; \text{ } \text{V}_{AA} \text{ } \text{PIX} = 2.8 \text{ } \text{V}; \text{ } \text{V}_{DD} \text{ } \text{PLL} = 2.8 \text{ } \text{V}; \text{ } \text{Output Load} = 68.5 \text{ } \text{pF}; \text{ } \text{T}_{\text{J}} = 60^{\circ}\text{C})$

|                        | Power   | Тур   | Max   | Unit |

|------------------------|---------|-------|-------|------|

| Hard Standby (CLK OFF) | Digital | 19.8  | 35.8  | μΑ   |

|                        | Analog  | 5.8   | 7.0   | μΑ   |

| Soft Standby (CLK OFF) | Digital | 23.5  | 39.7  | μΑ   |

|                        | Analog  | 5.4   | 5.9   | μΑ   |

| Soft Standby (CLK ON)  | Digital | 15700 | 16900 | μΑ   |

|                        | Analog  | 5.5   | 5.7   | μΑ   |

**CAUTION:** Stresses greater than those listed in Table 13 may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### Table 13. ABSOLUTE MAXIMUM RATINGS

| Symbol                        | Definition                | Min  | Max | Unit |

|-------------------------------|---------------------------|------|-----|------|

| V <sub>DD</sub> _MAX          | Core Digital Voltage      | -0.3 | 2.4 | V    |

| V <sub>DD</sub> _IO_MAX       | I/O Digital Voltage       | -0.3 | 4   | V    |

| V <sub>AA</sub> _MAX          | Analog Voltage            | -0.3 | 4   | V    |

| V <sub>AA</sub> _PIX          | Pixel Supply Voltage      | -0.3 | 4   | V    |

| V <sub>DD</sub> _PLL          | PLL Supply Voltage        | -0.3 | 4   | V    |

| V <sub>DD</sub> _MIPI         | MIPI Supply Voltage       | -0.3 | 4   | V    |

| V <sub>DD</sub> _HiSPi_MAX    | HiSPi Digital Voltage     | -0.3 | 2.4 | V    |

| V <sub>DD</sub> _HiSPi_TX_MAX | HiSPi I/O Digital Voltage | -0.3 | 2.4 | V    |

| t <sub>ST</sub>               | Storage Temperature       | -40  | 85  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

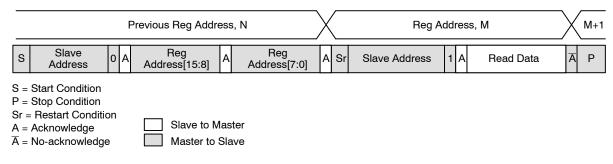

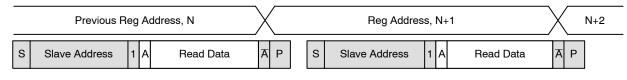

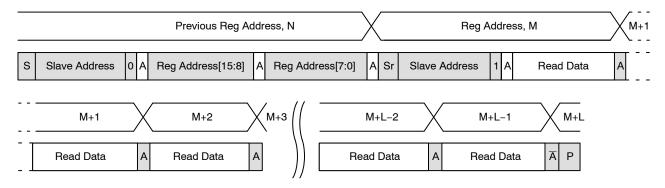

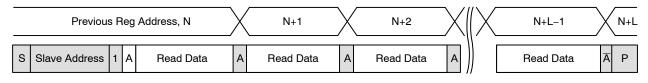

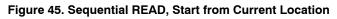

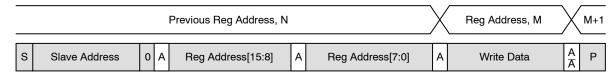

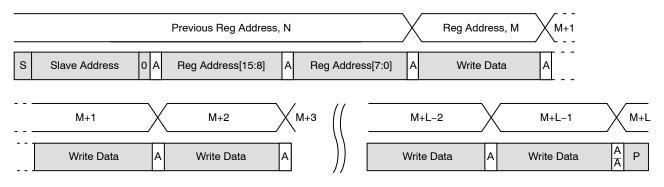

## **Two-Wire Serial Register Interface**

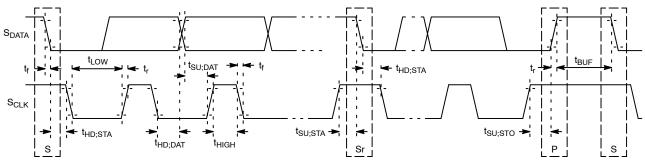

The electrical characteristics of the two-wire serial register interface (S<sub>CLK</sub>, S<sub>DATA</sub>) are shown in Figure 8 and Table 14.

NOTE: Read sequence: For an 8-bit READ, read waveforms start after WRITE command and register address are issued.

## Figure 8. Two-Wire Serial Bus Timing Parameters

## Table 14. TWO-WIRE SERIAL BUS CHARACTERISTICS

$(f_{EXTCLK} = 27 \text{ MHz}; \text{ V}_{DD} = 1.8 \text{ V}; \text{ V}_{DD}\text{_IO} = 2.8 \text{ V}; \text{ V}_{AA} = 2.8 \text{ V}; \text{ V}_{AA}\text{\_PIX} = 2.8 \text{ V}; \text{ V}_{DD}\text{\_PLL} = 2.8 \text{ V}; \text{ T}_{A} = 25^{\circ}\text{C})$

|                                                                  |                     | Standa        | rd Mode          | Fast I                  | Mode            |      |

|------------------------------------------------------------------|---------------------|---------------|------------------|-------------------------|-----------------|------|

| Parameter                                                        | Symbol              | Min           | Мах              | Min                     | Max             | Unit |

| S <sub>CLK</sub> Clock Frequency                                 | t <sub>SCL</sub>    | 0             | 100              | 0                       | 400             | kHz  |

| Hold Time (Repeated) START Condition                             |                     |               |                  |                         |                 |      |

| After this Period, the First Clock Pulse is Generated            | t <sub>HD;STA</sub> | 4.0           | -                | 0.6                     | _               | μs   |

| LOW Period of the S <sub>CLK</sub> Clock                         | t <sub>LOW</sub>    | 4.7           | _                | 1.3                     | _               | μs   |

| HIGH Period of the S <sub>CLK</sub> Clock                        | t <sub>HIGH</sub>   | 4.0           | -                | 0.6                     | _               | μs   |

| Set-up Time for a Repeated START<br>Condition                    | t <sub>SU;STA</sub> | 4.7           | -                | 0.6                     | -               | μs   |

| Data Hold Time                                                   | t <sub>HD;DAT</sub> | 0<br>(Note 4) | 3.45<br>(Note 5) | 0<br>(Note 6)           | 0.9<br>(Note 5) | μs   |

| Data Set-up Time                                                 | t <sub>SU;DAT</sub> | 250           | -                | 100<br>(Note 6)         | -               | ns   |

| Rise Time of both $S_{\mbox{DATA}}$ and $S_{\mbox{CLK}}$ Signals | t <sub>r</sub>      | _             | 1000             | 20 + 0.1 Cb<br>(Note 7) | 300             | ns   |

| Fall Time of both $S_{\mbox{DATA}}$ and $S_{\mbox{CLK}}$ Signals | t <sub>f</sub>      | _             | 300              | 20 + 0.1 Cb<br>(Note 7) | 300             | ns   |

| Set-up Time for STOP Condition                                   | t <sub>SU;STO</sub> | 4.0           | _                | 0.6                     | _               | μs   |

| Bus Free Time between a STOP and START Condition                 | t <sub>BUF</sub>    | 4.7           | -                | 1.3                     | -               | μs   |

| Capacitive Load for Each Bus Line                                | Cb                  | -             | 400              | -                       | 400             | pF   |

| Serial Interface Input Pin Capacitance                           | CIN_SI              | _             | 3.3              | -                       | 3.3             | pF   |

| S <sub>DATA</sub> Max Load Capacitance                           | CLOAD_SD            | _             | 30               | -                       | 30              | pF   |

| S <sub>DATA</sub> Pull-up Resistor                               | RSD                 | 1.5           | 4.7              | 1.5                     | 4.7             | kΩ   |

1. This table is based on I<sup>2</sup>C standard (v2.1 January 2000). Philips Semiconductor.

Two-wire control is I<sup>2</sup>C-compatible. 2.

3. All values referred to  $V_{IHmin} = 0.9 V_{DD}$  and  $V_{ILmax} = 0.1 V_{DD}$  levels. Sensor EXCLK = 27 MHz. 4. A device must internally provide a hold time of at least 300 ns for the  $S_{DATA}$  signal to bridge the undefined region of the falling edge of  $S_{CLK}$ . The maximum t<sub>HD;DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the S<sub>CLK</sub> signal.

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU;DAT</sub> 250 ns must then be met. This

will automatically be the case if the device does not stretch the LOW period of the S<sub>CLK</sub> signal. If such a device does stretch the LOW period of the S<sub>CLK</sub> signal, it must output the next data bit to the S<sub>DATA</sub> line t<sub>r</sub> max + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the S<sub>CLK</sub> line is released.

7. Cb = total capacitance of one bus line in pF.

NOTE: PLL disabled for t<sub>CP</sub>.

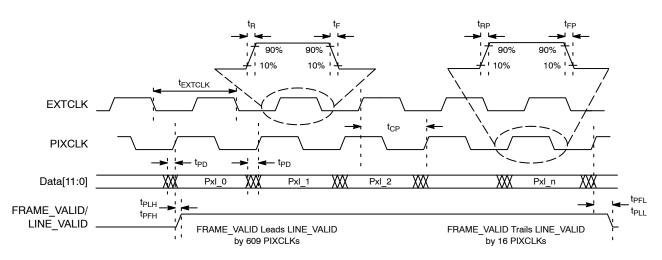

## Figure 9. I/O Timing Diagram

#### Table 15. I/O PARAMETERS

$(f_{EXTCLK} = 24 \text{ MHz}; \text{ } \text{V}_{\text{DD}} = 1.8 \text{ } \text{V}; \text{ } \text{V}_{\text{AA}} = 2.8 \text{ } \text{V}; \text{ } \text{V}_{\text{AA}} \text{ } \text{PIX} = 2.8 \text{ } \text{V}; \text{ } \text{V}_{\text{DD}} \text{ } \text{PLL} = 2.8 \text{ } \text{V}; \text{ } \text{Output Load} = 68.5 \text{ } \text{pF}; \text{ } \text{T}_{\text{J}} = 60^{\circ}\text{C}; \text{ } \text{CLK} \text{ } \text{OP} = 98 \text{ } \text{Mp/s})$

| Symbol          | Definition                       | Condition                                                  | Min                       | Max                                                    | Unit |

|-----------------|----------------------------------|------------------------------------------------------------|---------------------------|--------------------------------------------------------|------|

| V <sub>IH</sub> | Input HIGH Voltage               | V <sub>DD</sub> _IO = 1.8 V<br>V <sub>DD</sub> _IO = 2.8 V | 1.4<br>2.4                | V <sub>DD</sub> _IO + 0.3<br>V <sub>DD</sub> _IO + 0.3 | V    |

| V <sub>IL</sub> | Input LOW Voltage                | V <sub>DD</sub> _IO = 1.8 V<br>V <sub>DD</sub> _IO = 2.8 V | GND – 0.3<br>GND – 0.3    | 0.4<br>0.8                                             | μV   |

| I <sub>IN</sub> | Input Leakage Current            | No Pull-up Resistor; $V_{IN} = V_{DD} \text{ OR } D_{GND}$ | -20                       | 20                                                     | μA   |

| V <sub>OH</sub> | Output HIGH Voltage              | At Specified I <sub>OH</sub>                               | V <sub>DD</sub> _IO - 0.4 | -                                                      | V    |

| V <sub>OL</sub> | Output LOW Voltage               | At Specified I <sub>OL</sub>                               | -                         | 0.4                                                    | V    |

| I <sub>OH</sub> | Output HIGH Current              | At Specified V <sub>OH</sub>                               | -                         | -12                                                    | mA   |

| I <sub>OL</sub> | Output LOW Current               | At Specified V <sub>OL</sub>                               | _                         | 9                                                      | mA   |

| I <sub>OZ</sub> | Tri-state Output Leakage Current |                                                            | —                         | 10                                                     | μΑ   |

#### Table 16. I/O TIMING

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{DD}IO = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA}PIX = 2.8 \text{ V}; V_{DD}PLL = 2.8 \text{ V}; Output load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; CLK_OP = 98 \text{ Mp/s})$

| Symbol              | Definition                 | Conditions                | Min | Тур | Max                    | Unit |

|---------------------|----------------------------|---------------------------|-----|-----|------------------------|------|

| f <sub>EXTCLK</sub> | Input Clock Frequency      | PLL Enabled               | 6   | 24  | 27                     | MHz  |

| <sup>t</sup> EXTCLK | Input Clock Period         | PLL Enabled               | 166 | 41  | 20                     | ns   |

| t <sub>R</sub>      | Input Clock Rise Time      |                           | 0.5 | -   | Sine Wave<br>Rise Time | ns   |

| t <sub>F</sub>      | Input Clock Fall Time      |                           | 0.5 | -   | Sine Wave<br>Fall Time | ns   |

|                     | Clock Duty Cycle           |                           | 45  | 50  | 55                     | %    |

| t <sub>JITTER</sub> | Input Clock Jitter         |                           | -   | -   | 0.3                    | ns   |

| Output Pin Slew     | Fastest                    | C <sub>LOAD</sub> = 15 pF | -   | 0.7 | _                      | V/ns |

| f <sub>PIXCLK</sub> | PIXCLK frequency           | Default                   | =   | 80  | _                      | MHz  |

| t <sub>PD</sub>     | PIXCLK to data valid       | Default                   | _   | -   | 3                      | ns   |

| t <sub>PFH</sub>    | PIXCLK to FRAME_VALID HIGH | Default                   | -   | -   | 3                      | ns   |

| t <sub>PLH</sub>    | PIXCLK to LINE_VALID HIGH  | Default                   | —   | -   | 3                      | ns   |

| t <sub>PFL</sub>    | PIXCLK to FRAME_VALID LOW  | Default                   | _   | -   | 3                      | ns   |

| t <sub>PLL</sub>    | PIXCLK to LINE_VALID LOW   | Default                   | _   | -   | 3                      | ns   |

#### Table 17. PARALLEL I/O RISE SLEW RATE

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA} PIX = 2.8 \text{ V}; V_{DD} PLL = 2.8 \text{ V}; Output Load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; CLK_OP = 98 \text{ Mp/s})$

|        |       | Parallel Slew Rate (R0x306E[15:13]) |       |       |       |       |       |       |      |

|--------|-------|-------------------------------------|-------|-------|-------|-------|-------|-------|------|

| VDD_IO | 0     | 1                                   | 2     | 3     | 4     | 5     | 6     | 7     | Unit |

| 1.70 V | 0.069 | 0.115                               | 0.172 | 0.239 | 0.325 | 0.43  | 0.558 | 0.836 | V/ns |

| 1.80 V | 0.078 | 0.131                               | 0.195 | 0.276 | 0.375 | 0.507 | 0.667 | 1.018 |      |

| 1.95 V | 0.093 | 0.156                               | 0.233 | 0.331 | 0.456 | 0.62  | 0.839 | 1.283 |      |

| 2.50 V | 0.15  | 0.252                               | 0.377 | 0.539 | 0.759 | 1.07  | 1.531 | 2.666 |      |

| 2.80 V | 0.181 | 0.305                               | 0.458 | 0.659 | 0.936 | 1.347 | 1.917 | 3.497 |      |

| 3.10 V | 0.212 | 0.361                               | 0.543 | 0.78  | 1.114 | 1.618 | 2.349 | 4.14  |      |

## **HISPI TRANSMITTER**

NOTE: Refer to "High-Speed Serial Pixel Interface Physical Layer Specification v2.00.00" for further explanation of the HiSPi transmitter specification.

#### **SLVS Electrical Specifications**

#### Table 18. POWER SUPPLY AND OPERATING TEMPERATURE

$(f_{EXTCLK} = 24 \text{ MHz}; V_{DD} = 1.8 \text{ V}; V_{DD}IO = 1.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA}PIX = 2.8 \text{ V}; V_{DD}PLL = 2.8 \text{ V}; Output load = 68.5 \text{ pF}; T_J = 60^{\circ}\text{C}; CLK_OP = 98 \text{ Mp/s})$

| Symbol                    | Parameter                                     | Min | Тур | Max    | Unit |

|---------------------------|-----------------------------------------------|-----|-----|--------|------|

| I <sub>DD</sub> _HiSPi_TX | SLVS Current Consumption (Notes 1, 2)         | -   | _   | n × 18 | mA   |

| I <sub>DD</sub> _HiSPi    | HiSPi PHY Current Consumption (Notes 1, 2, 3) | -   | -   | n × 45 | mA   |

| Т <sub>Ј</sub>            | Operating Temperature (Note 4)                | -30 | _   | 70     | °C   |

1. Where 'n' is the number of PHYs.

2. Temperature of 25°C.

3. Up to 700 Mbps.

4. Specification values may be exceeded when outside this temperature range.

#### Table 19. SLVS ELECTRICAL DC SPECIFICATION ( $T_J = 25^{\circ}C$ )

| Symbol                  | Parameter                                                  | Min                        | Тур                       | Мах                        | Unit |

|-------------------------|------------------------------------------------------------|----------------------------|---------------------------|----------------------------|------|

| V <sub>CM</sub>         | SLVS DC Mean Common Mode Voltage                           | 0.45 * V <sub>DD</sub> _TX | 0.5 * V <sub>DD</sub> _TX | 0.55 * V <sub>DD_</sub> TX | V    |

| V <sub>OD</sub>         | SLVS DC Mean Differential Output Voltage                   | 0.36 * V <sub>DD</sub> _TX | 0.5 * V <sub>DD</sub> _TX | 0.64 * V <sub>DD</sub> _TX | V    |

| $\Delta V_{CM}$         | Change in $V_{\mbox{CM}}$ between Logic 1 and 0            | -                          | -                         | 25                         | mV   |

| V <sub>OD</sub>         | Change in  V <sub>OD</sub>   between Logic 1 and 0         | _                          | _                         | 25                         | mV   |

| NM                      | V <sub>OD</sub> Noise Margin                               | _                          | -                         | ±30                        | %    |

| $ \Delta V_{CM} $       | Difference in $V_{CM}$ between any Two Channels            | _                          | -                         | 50                         | mV   |

| $ \Delta V_{OD} $       | Difference in $V_{OD}$ between any Two Channels            | _                          | -                         | 100                        | mV   |

| V <sub>CM_AC</sub>      | Common-mode AC Voltage (pk) without VCM Cap<br>Termination | -                          | -                         | 50                         | mV   |

| V <sub>CM_AC</sub>      | Common-mode AC Voltage (pk) with VCM Cap<br>Termination    | -                          | -                         | 30                         | mV   |

| V <sub>OD_AC</sub>      | Maximum Overshoot Peak  V <sub>OD</sub>                    | _                          | -                         | 1.3 *  V <sub>OD</sub>     | V    |

| V <sub>Diff_pk-pk</sub> | Maximum Overshoot V <sub>Diff_pk-pk</sub>                  | _                          | _                         | 2.6 * V <sub>OD</sub>      | V    |

| R <sub>O</sub>          | Single-ended Output Impedance                              | 35                         | 50                        | 70                         | Ω    |

| $\Delta R_0$            | Output Impedance Mismatch                                  | _                          | -                         | 20                         | %    |

| Symbol                | Parameter                                    | Min    | Мах  | Unit |

|-----------------------|----------------------------------------------|--------|------|------|

| 1/UI                  | Data Rate (Note 1)                           | 280    | 700  | Mbps |

| t <sub>PW</sub>       | Bitrate Period (Note 1)                      | 1.43   | 3.57 | ns   |

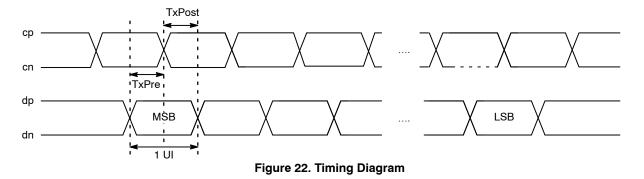

| t <sub>PRE</sub>      | Max Setup Time from Transmitter (Notes 1, 2) | 0.3    | -    | UI   |

| t <sub>POST</sub>     | Max Hold Time from Transmitter (Notes 1, 2)  | 0.3    | -    | UI   |

| t <sub>EYE</sub>      | Eye Width (Notes 1, 2)                       | -      | 0.6  | UI   |

| t <sub>TOTALJIT</sub> | Data Total Jitter (pk-pk) @1e-9 (Notes 1, 2) | _      | 0.2  | UI   |

| t <sub>CKJIT</sub>    | Clock Period Jitter (RMS) (Note 2)           | -      | 50   | ps   |

| tCYCJIT               | Clock Cycle-to-Cycle Jitter (RMS) (Note 2)   | _      | 100  | ps   |

| t <sub>R</sub>        | Rise Time (20-80%) (Note 3)                  | 150 ps | 0.25 | UI   |

| t <sub>F</sub>        | Fall Time (20-80%) (Note 3)                  | 150 ps | 0.25 | UI   |

| DCYC                  | Clock Duty Cycle (Note 2)                    | 45     | 55   | %    |

| t <sub>CHSKEW</sub>   | Mean Clock to Data Skew (Notes 1, 4)         | -0.1   | 0.1  | UI   |

| t <sub>PHYSKEW</sub>  | PHY-to-PHY Skew (Notes 1, 5)                 | -      | 2.1  | UI   |

| tDIFFSKEW             | Mean Differential Skew (Note 6)              | -100   | 100  | ps   |

#### Table 20. SLVS ELECTRICAL TIMING SPECIFICATION

1. One UI is defined as the normalized mean time between one edge and the following edge of the clock.

2. Taken from the 0 V crossing point with the DLL off.

3. Also defined with a maximum loading capacitance of 10 pF on any pin. The loading capacitance may also need to be less for higher bitrates so the rise and fall times do not exceed the maximum 0.3 UI.

4. The absolute mean skew between the Clock lane and any Data Lane in the same PHY between any edges.

5. The absolute skew between any Clock in one PHY and any Data lane in any other PHY between any edges.

6. Differential skew is defined as the skew between complementary outputs. It is measured as the absolute time between the two complementary edges at mean VCM point. Note that differential skew also is related to the ΔVCM\_AC spec which also must not be exceeded.

#### **HiVCM Electrical Specifications**

The HiSPi 2.0 specification also defines an alternative signaling level mode called HiVCM. Both  $V_{\rm OD}$  and  $V_{CM}$  are

still scalable with  $V_{DD}$ \_HiSPi\_TX, but with  $V_{DD}$ \_HiSPi\_TX nominal set to 1.8 V the common-mode is elevated to around 0.9 V.

## Table 21. HIVCM POWER SUPPLY AND OPERATING TEMPERATURES

| Symbol                    | Parameter                                     | Min | Тур | Max    | Unit |

|---------------------------|-----------------------------------------------|-----|-----|--------|------|

| I <sub>DD</sub> _HiSPi_TX | HiVCM Current Consumption (Notes 1, 2)        | -   | -   | n * 34 | mA   |

| I <sub>DD</sub> _HiSPi    | HiSPi PHY Current Consumption (Notes 1, 2, 3) | -   | -   | n * 45 | mA   |

| ТJ                        | Operating Temperature (Note 4)                | -30 | _   | 70     | °C   |

1. Where 'n' is the number of PHYs.

2. Temperature of 25°C.

3. Up to 700 Mbps.

4. Specification values may be exceeded when outside this temperature range.

| Symbol                  | Parameter                                                        | Min  | Тур  | Max                    | Unit |

|-------------------------|------------------------------------------------------------------|------|------|------------------------|------|

| V <sub>CM</sub>         | HiVCM DC Mean Common Mode Voltage                                | 0.76 | 0.90 | 1.07                   | V    |

| V <sub>OD</sub>         | HiVCM DC Mean Differential Output Voltage                        | 200  | 280  | 350                    | mV   |

| $\Delta V_{CM}$         | Change in $V_{\mbox{CM}}$ between Logic 1 and 0                  | -    | -    | 25                     | mV   |

| V <sub>OD</sub>         | Change in  V <sub>OD</sub>   between Logic 1 and 0               | _    | -    | 25                     | mV   |

| NM                      | V <sub>OD</sub> Noise Margin                                     | -    | -    | ±30                    | %    |

| $ \Delta V_{CM} $       | Difference in $V_{\mbox{CM}}$ between any Two Channels           | -    | -    | 50                     | mV   |

| $ \Delta V_{OD} $       | Difference in $V_{OD}$ between any Two Channels                  | _    | -    | 100                    | mV   |

| $\Delta V_{CM\_AC}$     | Common-mode AC Voltage (pk) without $V_{CM}$ Cap Termination     | _    | -    | 50                     | mV   |

| $\Delta V_{CM\_AC}$     | Common-mode AC Voltage (pk) with V <sub>CM</sub> Cap Termination | -    | -    | 30                     | mV   |

| V <sub>OD_AC</sub>      | Maximum Overshoot Peak  V <sub>OD</sub>                          | -    | -    | 1.3 *  V <sub>OD</sub> | V    |

| V <sub>Diff_pk-pk</sub> | Maximum Overshoot V <sub>Diff pk-pk</sub>                        | _    | -    | 2.6 * V <sub>OD</sub>  | V    |

| R <sub>O</sub>          | Single-ended Output Impedance                                    | 40   | 70   | 100                    | Ω    |

| $\Delta R_{O}$          | Output Impedance Mismatch                                        | _    | -    | 20                     | %    |

|                         | 4                                                                |      | -    |                        |      |

#### Table 22. HIVCM ELECTRICAL VOLTAGE AND IMPEDANCE SPECIFICATION (T, I = 25°C)

## Table 23. HIVCM ELECTRICAL AC SPECIFICATION

| Symbol                | Parameter                                    | Min    | Max  | Unit |

|-----------------------|----------------------------------------------|--------|------|------|

| 1/UI                  | Data Rate (Note 1)                           | 280    | 700  | Mbps |

| t <sub>PW</sub>       | Bitrate Period (Note 1)                      | 1.43   | 3.57 | ns   |

| t <sub>PRE</sub>      | Max Setup Time from Transmitter (Notes 1, 2) | 0.3    | _    | UI   |

| t <sub>POST</sub>     | Max Gold Time from Transmitter (Notes 1, 2)  | 0.3    | _    | UI   |

| t <sub>EYE</sub>      | Eye Width (Notes 1, 2)                       | -      | 0.6  | UI   |

| t <sub>TOTALJIT</sub> | Data Total Jitter (pk-pk) @1e-9 (Notes 1, 2) | -      | 0.2  | UI   |

| t <sub>CKJIT</sub>    | Clock Period Jitter (RMS) (Note 2)           | -      | 50   | ps   |

| <sup>t</sup> CYCJIT   | Clock Cycle-to-Cycle Jitter (RMS) (Note 2)   | -      | 100  | ps   |

| t <sub>R</sub>        | Rise Time (20-80%) (Note 3)                  | 150 ps | 0.3  | UI   |

| t <sub>F</sub>        | Fall Time (20-80%) (Note 3)                  | 150 ps | 0.3  | UI   |

| D <sub>CYC</sub>      | Clock Duty Cycle (Note 2)                    | 45     | 55   | %    |

| t <sub>CHSKEW</sub>   | Clock to Data Skew (Notes 1, 4)              | -0.1   | 0.1  | UI   |

| <b>t</b> PHYSKEW      | PHY-to-PHY Skew (Notes 1, 5)                 | -      | 2.1  | UI   |

| t <sub>DIFFSKEW</sub> | Mean Differential Skew (Note 6)              | -100   | 100  | ps   |

1. One UI is defined as the normalized mean time between one edge and the following edge of the clock.

Taken from the 0 V crossing point with the DLL off.

Also defined with a maximum loading capacitance of 10 pF on any pin. The loading capacitance may also need to be less for higher bitrates so the rise and fall times do not exceed the maximum 0.3 UI.

4. The absolute mean skew between the Clock lane and any Data Lane in the same PHY between any edges.

5. The absolute mean skew between any Clock in one PHY and any Data lane in any other PHY between any edges.

6. Differential skew is defined as the skew between complementary outputs. It is measured as the absolute time between the two complementary edges at mean V<sub>CM</sub> point. Note that differential skew also is related to the ΔVCM\_AC spec which also must not be exceeded.

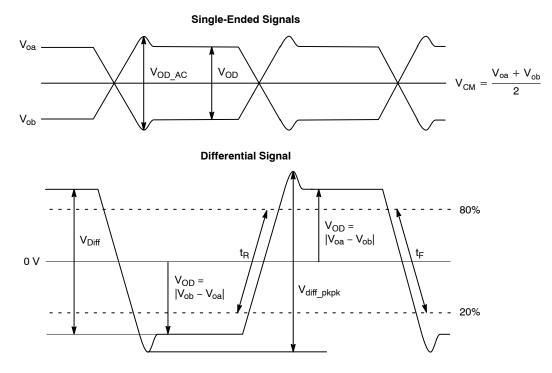

#### **Electrical Definitions**

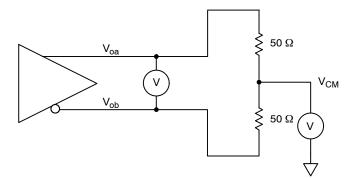

Figure 10 is the diagram defining differential amplitude  $V_{OD}$ ,  $V_{CM}$ , and rise and fall times. To measure  $V_{OD}$  and

$V_{CM}$  use the DC test circuit shown in Figure 11 and set the HiSPi PHY to constant Logic 1 and Logic 0. Measure  $V_{oa}$ ,  $V_{ob}$  and  $V_{CM}$  with voltmeters for both Logic 1 and Logic 0.

Figure 10. Single-Ended and Differential Signals

Figure 11. DC Test Circuit

$$V_{OD}(m) = |V_{oa}(m) - V_{ob}(m)|$$

(eq. 1)

Where *m* is either "1" for logic 1 or "0" for logic 0.

$$V_{OD} = \frac{V_{OD}(1) + V_{OD}(0)}{2}$$

(eq. 2)

$$V_{\text{Diff}} = V_{\text{OD}}(1) + V_{\text{OD}}(0)$$

(eq. 3)

$$\Delta V_{OD} = \left| V_{OD}(1) - V_{OD}(0) \right| \qquad (eq. 4)$$

$$V_{CM} = \frac{V_{CM}(1) + V_{CM}(0)}{2}$$

(eq. 5)

$$\Delta V_{CM} = \left| V_{CM}(1) - V_{CM}(0) \right| \qquad (eq. 6)$$

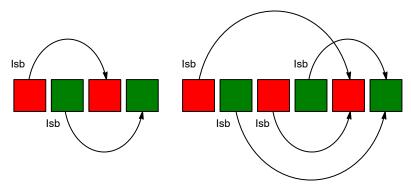

Both  $V_{OD}$  and  $V_{CM}$  are measured for all output channels. The worst case  $\Delta V_{OD}$  is defined as the largest difference in  $V_{OD}$  between all channels regardless of logic level. And the worst case  $\Delta V_{CM}$  is similarly defined as the largest difference in  $V_{CM}$  between all channels regardless of logic level.

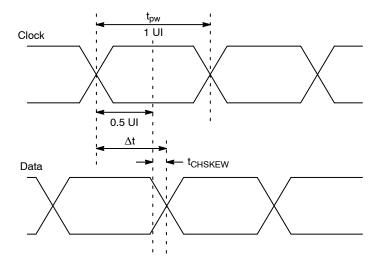

## **Timing Definitions**

- 1. Timing measurements are to be taken using the Square Wave test mode.

- 2. Rise and fall times are measured between 20% to 80% positions on the differential waveform, as shown in Figure 10.

- 3. Mean Clock-to-Data skew should be measured from the 0 V crossing point on Clock to the 0 V crossing point on any Data channel regardless of

edge, as shown in Figure 12. This time is compared with the ideal Data transition point of 0.5 UI with the difference being the Clock-to-Data Skew (see Equation 7).

$$t_{CHSKEW}(ps) = \Delta t - \frac{t_{pw}}{2}$$

(eq. 7)

$$t_{CHSKEW}(UI) = \frac{\Delta t}{t_{pw}} - 0.5$$

(eq. 8)

Figure 12. Clock-to-Data Skew Timing Diagram

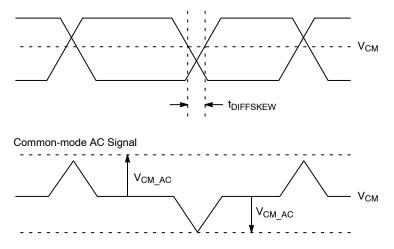

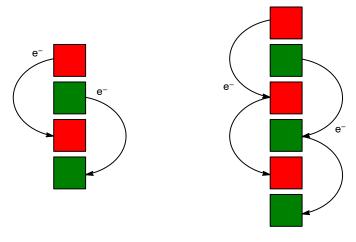

4. The differential skew is measured on the two single-ended signals for any channel. The time is taken from a transition on  $V_{oa}$  signal to

corresponding transition on  $V_{ob}$  signal at  $V_{CM}$  crossing point.

Figure 13. Differential Skew

Figure 13 also shows the corresponding AC  $V_{CM}$  common-mode signal. Differential skew between the  $V_{oa}$  and  $V_{ob}$  signals can cause spikes in the common-mode,

which the receiver needs to be able to reject.  $V_{CM\_AC}$  is measured as the absolute peak deviation from the mean DC  $V_{CM}$  common-mode.

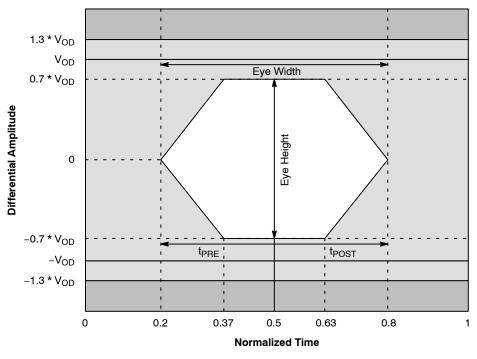

## **Transmitter Eye Mask**

Figure 14 defines the *eye mask* for the transmitter. 0.5 UI point is the instantaneous crossing point of the Clock. The area in white shows the area Data is prohibited from crossing into. The *eye mask* also defines the minimum eye height, the data  $t_{PRE}$  and  $t_{POST}$  times, and the *total jitter pk-pk +mean skew* ( $t_{TJSKEW}$ ) for Data.

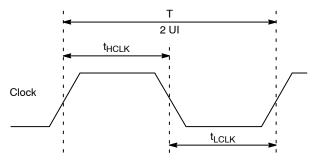

Clock Signal

$t_{\rm HCLK}$  is defined as the high clock period, and  $t_{\rm LCLK}$  is defined as the low clock period as shown in Figure 15. The clock duty cycle  $D_{\rm CYC}$  is defined as the percentage time the clock is either high ( $t_{\rm HCLK}$ ) or low ( $t_{\rm LCLK}$ ) compared with the clock period T.

$$D_{CYC}(1) = \frac{t_{HCLK}}{T} \qquad (eq. 9) \qquad t_{pw} = \frac{T}{2} \quad (i.e, 1 \text{ UI}) \qquad (eq. 11)$$

$$D_{CYC}(0) = \frac{t_{LCLK}}{T} \qquad (eq. 10) \qquad \text{Bitrate} = \frac{1}{t_{pw}} \qquad (eq. 12)$$

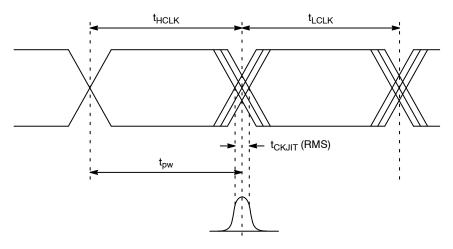

Figure 16 shows the definition of clock jitter for both the period and the cycle-to-cycle jitter.

Figure 16. Clock Jitter

Period Jitter ( $t_{CKJIT}$ ) is defined as the deviation of the instantaneous clock  $t_{PW}$  from an ideal 1 UI. This should be measured for both the clock high period variation  $\Delta t_{HCLK}$ , and the clock low period variation  $\Delta t_{LCLK}$  taking the RMS or 1-sigma standard deviation and quoting the worse case jitter between  $\Delta t_{HCLK}$  and  $\Delta t_{LCLK}$ .

Cycle-to-cycle jitter ( $t_{CYCJIT}$ ) is defined as the difference in time between consecutive clock high and clock low periods  $t_{HCLK}$  and  $t_{LCLK}$ , quoting the RMS value of the variation  $\Delta(t_{HCLK} - t_{LCLK})$ .

If pk-pk jitter is also measured, this should be limited to  $\pm 3$ -sigma.

| Symbol                | Parameter                                    | Min    | Max  | Unit |

|-----------------------|----------------------------------------------|--------|------|------|

| 1/UI                  | Data Rate (Note 1)                           | 280    | 700  | Mbps |

| t <sub>PW</sub>       | Bitrate Period (Note 1)                      | 1.43   | 3.57 | ns   |

| t <sub>PRE</sub>      | Max Setup Time from Transmitter (Notes 1, 2) | 0.3    | -    | UI   |

| t <sub>POST</sub>     | Max Gold Time from Transmitter (Notes 1, 2)  | 0.3    | -    | UI   |

| t <sub>EYE</sub>      | Eye Width (Notes 1, 2)                       | -      | 0.6  | UI   |

| t <sub>TOTALJIT</sub> | Data Total Jitter (pk-pk) @1e-9 (Notes 1, 2) | -      | 0.2  | UI   |

| t <sub>СКЛТ</sub>     | Clock Period Jitter (RMS) (Note 2)           | -      | 50   | ps   |

| t <sub>CYCJIT</sub>   | Clock Cycle-to-Cycle Jitter (RMS) (Note 2)   | -      | 100  | ps   |

| t <sub>R</sub>        | Rise Time (20-80%) (Note 3)                  | 150 ps | 0.3  | UI   |

| t <sub>F</sub>        | Fall Time (20-80%) (Note 3)                  | 150 ps | 0.3  | UI   |

| D <sub>CYC</sub>      | Clock Duty Cycle (Note 2)                    | 45     | 55   | %    |

| tCHSKEW               | Clock to Data Skew (Notes 1, 4)              | -0.1   | 0.1  | UI   |

| t <sub>PHYSKEW</sub>  | PHY-to-PHY Skew (Notes 1, 5)                 | -      | 2.1  | UI   |

| t <sub>DIFFSKEW</sub> | Mean Differential Skew (Note 6)              | -100   | 100  | ps   |

#### Table 24. HiVCM ELECTRICAL AC SPECIFICATION

1. One UI is defined as the normalized mean time between one edge and the following edge of the clock.

2. Taken from the 0 V crossing point with the DLL off.

3. Also defined with a maximum loading capacitance of 10 pF on any pin. The loading capacitance may also need to be less for higher bitrates so the rise and fall times do not exceed the maximum 0.3 UI.

4. The absolute mean skew between the Clock lane and any Data Lane in the same PHY between any edges.

5. The absolute mean skew between any Clock in one PHY and any Data lane in any other PHY between any edges.

6. Differential skew is defined as the skew between complementary outputs. It is measured as the absolute time between the two complementary edges at mean  $V_{CM}$  point. Note that differential skew also is related to the  $\Delta VCM_AC$  spec which also must not be exceeded.

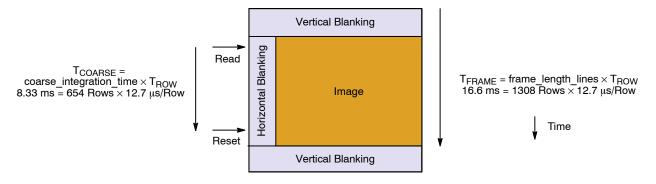

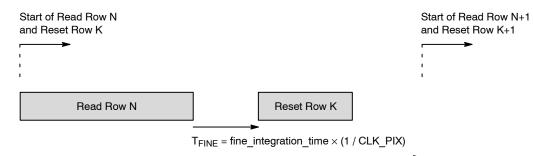

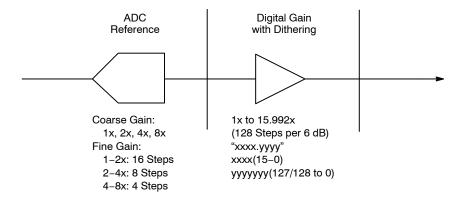

## SEQUENCER

The sequencer digital block determines the order and timing of operations required to sample pixel data from the array during each row period. It is controlled by an instruction set that is programmed into RAM from the sensor OTPM (One Time Programmable Memory). The OTPM is configured during production.

The instruction set determines the length of the sequencer operation that determines the "ADC Readout Limitation" (Equation 5) listed in the Sensor Frame Rate section. The instruction set can be shortened through register writes in order to achieve faster frame rates. Instructions for shortening the sequencer can be found in the AR0330 Developer Guide.

The sequencer digital block can be reprogrammed using the following instructions:

Program a new sequencer.

- 1. Place the sensor in standby.

- 2. Write 0x8000 to R0x3088 ("seq ctrl port").

- 3. Write each instruction incrementally to R0x3086. Each write must be 16-bit consisting of two bytes {Byte[N], Byte[N+1]}.

- 4. If the sequencer consists of an odd number of bytes, set the last byte to "0".

Read the instructions stored in the sequencer.

- 1. Place the sensor in standby.

- 2. Write 0xC000 to R0x3088 ("seq\_ctrl\_port").

- 3. Sequentially read one byte at a time from R0x3086 with 8-bit read command.

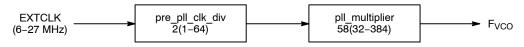

## SENSOR PLL

#### vco

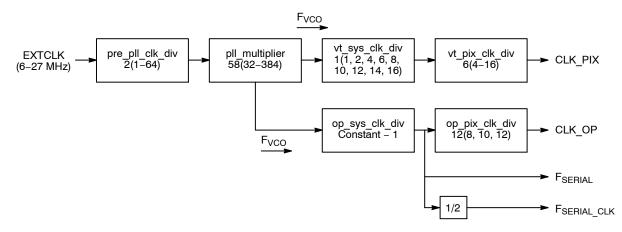

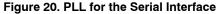

The sensor contains a phase-locked loop (PLL) that is used for timing generation and control. The required VCO clock frequency is attained through the use of a pre-PLL clock divider followed by a multiplier (see Figure 17). The multiplier is followed by set of dividers used to generate the output clocks required for the sensor array, the pixel analog and digital readout paths, and the output parallel and serial interfaces.

#### **Dual Readout Paths**

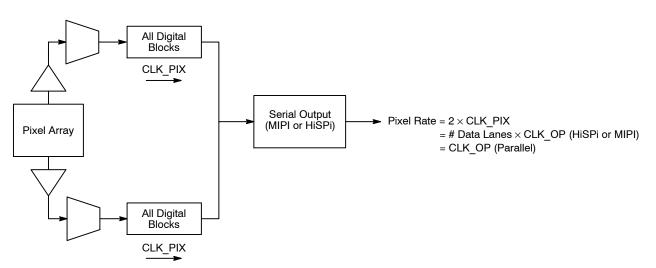

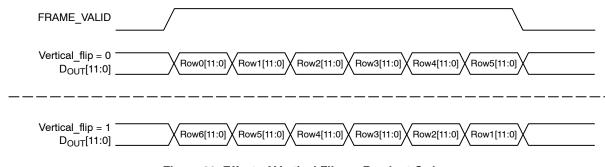

There are two readout paths within the sensor digital block (see Figure 18).

The sensor row timing calculations refers to each data-path individually. For example, the sensor default configuration uses 1248 clocks per row (line\_length\_pck) to output 2304 active pixels per row. The aggregate clocks per row seen by the receiver will be 2496 clocks ( $1248 \times 2$  readout paths).

Figure 17. Relationship between Readout Clock and Peak Pixel Rate

Figure 18. Sensor Dual Readout Paths

## Parallel PLL Configuration

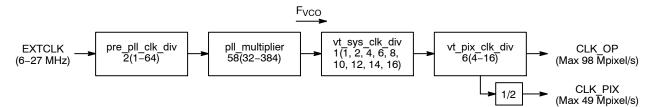

Figure 19. PLL for the Parallel Interface