STATE OF THE PARTY OF THE PARTY

T-46-09-05

## 54LS502/DM74LS502 8-Bit Successive Approximation Register

#### **General Description**

The LS502 is an 8-bit register with the interstage logic necessary to perform serial-to-parallel conversion and provide an active LOW Conversion Complete (CC) signal coincident with storage of the eighth bit. An active LOW Start (S) input performs synchronous initialization which forces Q7 LOW and all other outputs HIGH. Subsequent clocks shift this Q7 LOW signal downstream which simultaneously backfills the register such that the first serial data (D input) bit is stored in Q7, the second bit in Q6, the third in Q5, etc. The serial input data is also synchronized by an auxiliary flip-flop and brought out on QD.

Designed primarily for use in the successive approximation technique for analog-to-digital conversion, the LS502 can also be used as a serial-to-parallel converter ring counter and as the storage and control element in recursive digital

#### **Features**

- Low power Schottky version of 2502

- Storage and control for successive approximation A to D conversion

- Performs serial-to-parallel conversion

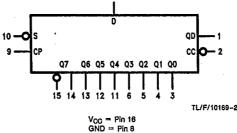

#### **Connection Diagram**

**Logic Symbol**

TL/F/10189~1 Order Number 54LS502DMQB, 54LS502FMQB,

DM74LS502WM or DM74LS502N See NS Package Number J16A, M16B, N16E or W16A

| Pin<br>Names   | Description                             |

|----------------|-----------------------------------------|

| D              | Serial Data Input                       |

| ই              | Start Input (Active LOW)                |

| CP             | Clock Pulse Input (Active Rising Edge)  |

| Q <sub>D</sub> | Synchronized Serial Data Output         |

| CC             | Conversion Complete Output (Active LOW) |

| Q0-Q7          | Parallel Register Outputs               |

| ፬ን             | Complement of Q7 Output                 |

### **Absolute Maximum Ratings (Note)**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage Input Voltage

Operating Free Air Temperature Range

54LS -55°C to +125°C DM74LS 0°C to +70°C

Storage Temperature Range -65°C to +150°C

### T-46-09-05

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

### **Recommended Operating Conditions**

| Symbol                                   | Parameter                         |          | 54LS502 |      |          | Units |      |          |

|------------------------------------------|-----------------------------------|----------|---------|------|----------|-------|------|----------|

|                                          | T atameter                        | Min      | Nom     | Max  | Min      | Nom   | Max  | - Cilita |

| Vcc                                      | Supply Voltage                    | 4.5      | 5       | 5.5  | 4.75     | 5     | 5.25 | ٧        |

| V <sub>IH</sub>                          | High Level Input Voitage          | 2        |         |      | . 2      |       |      | V        |

| V <sub>IL</sub>                          | Low Level Input Voltage           |          |         | 0.7  |          |       | 0.8  | V        |

| Юн                                       | High Level Output Current         |          |         | -0.4 |          |       | -0.4 | mA       |

| loL                                      | Low Level Output Current          |          |         | 4    |          |       | 8    | mA       |

| TA                                       | Free Air Operating Temperature    | -55      |         | 125  | 0        |       | 70   | °C       |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>S to CP | 5<br>5   |         |      | 5<br>5   |       |      | ns       |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>S to CP  | 5<br>5   |         |      | 5<br>5   |       |      | ns       |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>D to CP | 5<br>5   |         |      | 5<br>5   |       |      | ns       |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>D to CP  | 5<br>5   |         |      | 5<br>5   |       |      | ns       |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width HIGH or LOW        | 20<br>20 |         |      | 20<br>20 |       |      | ns       |

# Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol               | Parameter                            | Conditions                                    | Min  | Typ<br>(Note 1) | Max  | Units |        |

|----------------------|--------------------------------------|-----------------------------------------------|------|-----------------|------|-------|--------|

| Vi                   | Input Clamp Voltage                  | $V_{CC} = Min, I_I = -18 \text{ mA}$          |      |                 |      | -1.5  | ٧      |

| V <sub>OH</sub>      | High Level Output                    | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max, | 54LS | 2.5             |      |       | v      |

| Vo                   | Voltage                              | V <sub>IL</sub> = Max                         | DM74 | 2.7             |      |       | . •    |

| VOL Low Level Output | Low Level Output                     | V <sub>CC</sub> Min, I <sub>OL</sub> = Max,   | 54LS |                 |      | 0.4   |        |

|                      | Voltage                              | V <sub>IH</sub> = Min                         | DM74 |                 |      | 0.5   | l v    |

|                      |                                      | I <sub>OL</sub> = 4 mA, V <sub>CC</sub> = Min | DM74 |                 |      | 0.4   |        |

| lį                   | Input Current @ Max<br>Input Voltage | V <sub>CC</sub> = Max, V <sub>I</sub> = 10V   |      |                 | 0.1  | mA    |        |

| l <sub>IH</sub>      | High Level Input Current             | V <sub>CC</sub> = Max, V <sub>I</sub> = 2.7V  |      |                 |      | 20    | μΑ     |

| I <sub>IL</sub>      | Low Level Input Current              | V <sub>CC</sub> = Max, V <sub>I</sub> = 0.4V  |      |                 | -1.2 | mA    |        |

| los                  | Short Circuit                        | V <sub>CC</sub> = Max                         | 54LS | -20             |      | -100  | mA     |

|                      | Output Current                       | (Note 2) DM74                                 |      | -20             |      | -100  | I IIIA |

| lcc                  | Supply Current                       | V <sub>CC</sub> = Max                         |      |                 | 65   | mA    |        |

Note 1: All typicals are at VCC = 5V, TA = 25°C.

Note 2: Note more than one output should be shorted at a time, and the duration should not exceed one second.

| 7 | -46 | ^  | ^                | ^-  |

|---|-----|----|------------------|-----|

|   | -4n | 11 | $\mathbf{u}_{-}$ | IIL |

| Switching Characteristics V <sub>CC</sub> = +5.0V, T <sub>A</sub> = +25°C (See Section 1 for test waveforms and output loads) |                                                 |                   |          |      |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------|----------|------|--|--|--|--|

| Symbol                                                                                                                        | Parameter                                       | $R_L = 2 k\Omega$ | Units    |      |  |  |  |  |

|                                                                                                                               | - uraniotoi                                     | Min               | Max      | Jima |  |  |  |  |

| f <sub>max</sub>                                                                                                              | Maximum Clock Frequency                         | 25                |          | MHz  |  |  |  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub>                                                                                          | Propagation Delay<br>CP to Q <sub>n</sub> or CC |                   | 35<br>25 | ns   |  |  |  |  |

### **Functional Description**

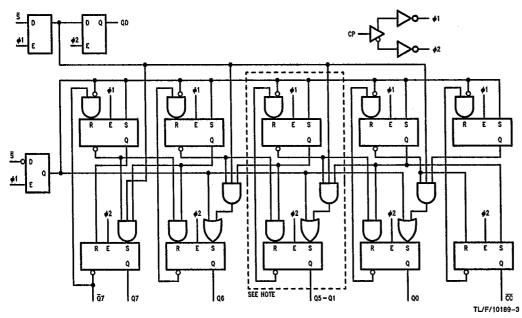

The register stages are composed of transparent RS latches arranged in master/slave pairs. The master and slave latches are enabled separately by non-overlapping complementary signals \$1 and \$2\$ derived internally from the CP input. Master latches are enabled when CP is LOW and slave latches are enabled when CP is HIGH. Information is transferred from master to slave, and thus to the outputs, by the LOW-to-HIGH transition of CP.

Initializing the register requires a LOW signal on \$\overline{S}\$ while exercising CP. With S and CP LOW, all master latches are SET (Q side HIGH). A LOW-to-HIGH CP transition, with S remaining LOW, then forces the slave latches to the condition wherein Q7 is LOW and all other register outputs, including CC, are HIGH. This condition will prevail as long as S remains LOW, regardless of subsequent CP rising edge. To start the conversion process, S must return to the HIGH state. On the next CP rising edge, the information stored in the serial data input latch is transferred to QD and Q7, while Q6 is forced to the LOW state. On the rising edge of the next seven clocks, this LOW signal is shifted downstream, one bit at a time, while the serial data enters the register position one bit behind this LOW signal, as shown in the Truth Table. Note that after a serial data bit appears at a particular output, that register position undergoes no further changes. After the shifted LOW signal reaches  $\overline{CC}$ , the register is locked up and no further changes can occur until the register is initialized for the next conversion process.

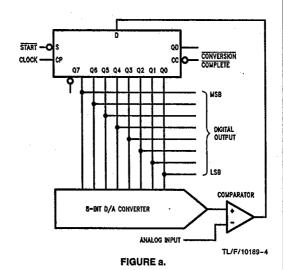

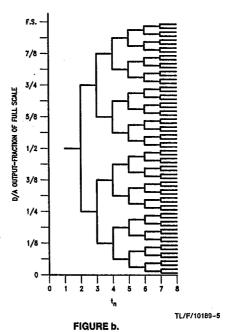

Figure a shows a simplified hook-up of a LS502, a D/A converter and a comparator arranged to convert an analog input voltage into an 8-bit binary number by the successive approximation technique. Figure b is an idealized graph showing the various values that the D/A converter output voltage can assume in the course of the conversion. The vertical axis is calibrated in fractions of the full-scale output capability of the D/A converter and the horizontal axis represents the successive states of the Truth Table. At time t1, Q7 is LOW and Q6-Q0 are HIGH, causing the D/A output to be one-half of full scale. If the analog input voltage is greater than this voltage the comparator output (hence the D input of the LS502) will be LOW, and at times t2 the D/A output will rise to three-fourths of full scale because Q7 will remain LOW and contribute 50% while Q6 is forced LOW and contributes another 25%. On the other hand, if the analog input voltage is less than one-half of full scale, the comparator output will be HIGH and Q7 will go HIGH at t2, Q6 will still be forced LOW at t2, and the D/A output will decrease to 25% of full scale. Thus with each successive clock, the D/A output will change by smaller increments. When the conversion is completed at 19, the binary number represented by the register outputs will be the numerator of the fraction n/256, representing the analog input voltage as a fraction of the full scale output D/A converter.

# **Truth Table**

| T-46- | 09- | 05 |

|-------|-----|----|

|-------|-----|----|

| Time | Inp | uts | Outputs |    |    |    |    |    |    |    |    |    |

|------|-----|-----|---------|----|----|----|----|----|----|----|----|----|

| tn   | D   | S   | $Q_{D}$ | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | CC |

| 0    | Х   | L   | X       | X  | X  | X  | Х  | Х  | Х  | Х  | Х  | х  |

| 1    | D7  | н   | х       | L  | Н  | Н  | Н  | Н  | Н  | Н  | Н  | н  |

| 2    | D6  | Н   | D7      | D7 | L  | Н  | Н  | Н  | H  | Н  | Н  | н  |

| 3    | D6  | Н   | D6      | D7 | D6 | L  | Н  | Н  | Н  | Н  | Н  | Н  |

| 4    | D4  | Н   | D5      | D7 | D6 | D5 | L  | Н  | Н  | Н  | Н  | н  |

| 5    | D3  | н   | D4      | D7 | D6 | D5 | D4 | L  | Н  | Н  | н  | н  |

| 6    | D2  | Н   | D3      | D7 | D6 | D5 | D4 | D3 | L  | Н  | Н  | н  |

| 7    | D1  | Н   | D2      | D7 | D6 | D5 | D4 | D3 | D2 | L, | Н  | н  |

| 8    | D0  | Н   | D1      | D7 | D6 | D5 | D4 | D3 | D2 | D1 | L  | H' |

| 9    | х   | Н   | D0      | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | L  |

| 10   | Х   | Н   | Х       | D7 | D6 | D5 | D4 | D3 | D2 | Ď1 | D0 | L  |

- H = HIGH Voltage Level L = LOW Voltage Level X = Immalerial

## **Logic Diagram**

Note: Cell logic is repeated for register stages Q5 to Q1.