# MPQ4482-Q

All-In-One QC3.0 USB Charging Port, Support 36Vin, 5V@3A Type-C AEC-Q100 Qualified

#### DESCRIPTION

The MPQ4482-Q integrates a monolithic stepdown switch-mode converter with a single USB current-limit switch and a Type-C 5V@3A mode configuration channel for the USB port. It achieves a 3A output current over a wide input supply range with excellent load and line regulation.

The output of the USB switch is current-limited. The USB port supports QC3.0 mode. It is backward compatible with DCP schemes for battery charging specification (BC1.2), the divider mode, and 1.2V/1.2V mode, without requiring outside user interaction. The USB port also supports USB Type-C 5V@3A DFP mode.

Fault protections include hiccup current limiting, and thermal shutdown (TSD).

The MPQ4482-Q requires a minimal number of readily available, external components. It is available in a QFN-22 (4mmx4mm) package.

## **FEATURES**

- DP/DM Support Quick Charge 3.0 Mode-Class A

- Backward Compatible for DCP Schemes: BC1.2 Short mode, Divider Mode, 1.2V/1.2V Mode

- Supports USB Type-C 5V@3A DFP Mode

- I/O pins (DP, DM, CC1 and CC2) Support Short to Battery Protection

- USB\_OUT Short to Battery Protection when VBUS is Enabled

- Wide 4V to 36V Operating Input Range

- 450kHz/280kHz Selectable Frequency

- 3A Output Current

- Line Drop Compensation

- Accurate USB Current Limit

- Forced CCM Operation

- Frequency Sync from 250kHz to 2.2MHz (Recommended: <15% of SYNC IN Duty Cycle)

- Load Shedding vs. Temperature

- Hiccup Current Limit for Buck and USB

- ±8KV HBM ESD Rating for CC1, CC2 and USB OUT to GND

- ±2.5kV HBM ESD Rating for DM, DP to GND

- Available in a QFN-22 (4mmx4mm)

Package with Wettable Flanks

- Available in AEC-Q100 Grade 1

### **APPLICATIONS**

- Automotive QC3.0 Charging Ports

- Automotive USB Type-C Charging Ports

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

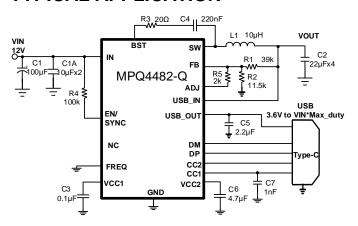

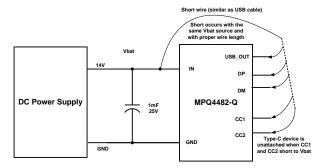

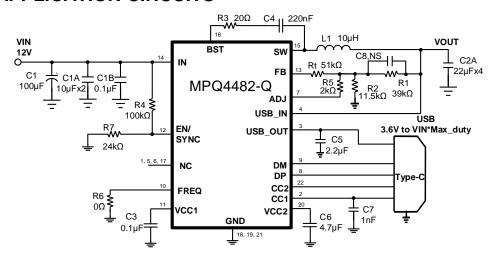

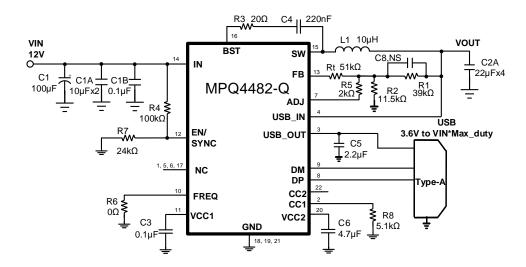

# TYPICAL APPLICATION

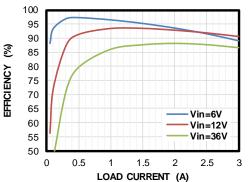

# Efficiency vs. Load Current

$V_{\text{OUT}} = 5.1V$ ,  $f_{\text{SW}} = 450kHz$ ,  $L = 10\mu H$ ,  $DCR = 69m\Omega$

## ORDERING INFORMATION

| Part Number*     | Package          | Top Marking | MSL Rating |

|------------------|------------------|-------------|------------|

| MPQ4482GR-Q-AEC1 | QFN-22 (4mmx4mm) | See Below   | 1          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ4482GR-Q-AEC1-Z).

## **TOP MARKING**

MPSYWW MP4482 LLLLLL

MPS: MPS prefix Y: Year code WW: Week code MP4482: Part number LLLLL: Lot number Q: Part number suffix

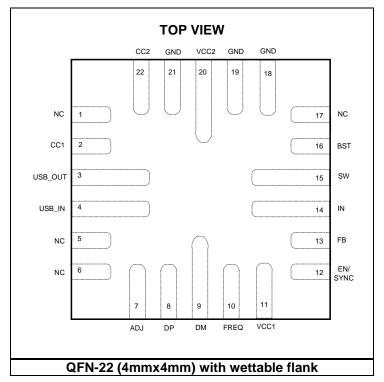

## **PACKAGE REFERENCE**

3

# **PIN FUNCTIONS**

| QFN 4x4<br>Pin # | Name    | Description                                                                                                                                                                                                                                                                                                 |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 6, 17      | NC      | No connection. Can tie to GND.                                                                                                                                                                                                                                                                              |

| 2                | CC1     | <b>Configuration channel.</b> CC1 detects connections and configures the interface across the USB Type-C cables and connectors. Once a connection is established, CC1 or CC2 is reassigned to provide power over the VCONN pin of the plug.                                                                 |

| 3                | USB_OUT | USB bus voltage output.                                                                                                                                                                                                                                                                                     |

| 4                | USB_IN  | USB bus voltage input                                                                                                                                                                                                                                                                                       |

| 7                | ADJ     | <b>Line drop compensation pin.</b> ADJ sinks a current from FB to ground to regulate the buck output voltage.                                                                                                                                                                                               |

| 8                | DP      | <b>D+ data line to USB connector</b> . DP is the input/output used for handshaking with portable devices.                                                                                                                                                                                                   |

| 9                | DM      | <b>D- data line to USB connector.</b> DM is the input/output used for handshaking with portable devices.                                                                                                                                                                                                    |

| 10               | FREQ    | <b>Frequency select pin.</b> Float or connect this pin to VCC1 to set the buck's switching frequency to 280kHz. Short this pin to ground to set the switching frequency to 450kHz.                                                                                                                          |

| 11               | VCC1    | Internal 4.8V LDO regulator output. Decouple VCC1 with a $0.1\mu F$ to $0.22\mu F$ capacitor. Select a capacitor that does not exceed $0.22\mu F$ .                                                                                                                                                         |

| 12               | EN/SYNC | <b>On/Off Control Input.</b> Internally pulled to ground by a $500k\Omega$ resistor. Apply an external CLK on this pin to sync up the switching frequency.                                                                                                                                                  |

| 13               | FB      | <b>Feedback.</b> To set the output voltage, connect FB to the tap of an external resistor divider from the output to GND. To prevent current limit runaway during a short-circuit fault condition, the frequency fold-back comparator lowers the oscillator frequency when the FB voltage drops below 400mV |

| 14               | IN      | <b>Supply voltage.</b> The MPQ4482-Q operates from a 4V to 36V input rail. Requires C1 to decouple the input rail. Connect using a wide PCB trace.                                                                                                                                                          |

| 15               | SW      | Switch output. Use a wide PCB trace to make the connection.                                                                                                                                                                                                                                                 |

| 16               | BST     | <b>Bootstrap.</b> A 220nF capacitor is connected between SW and BST to form a floating supply across the high-side switch driver. A $20\Omega$ resistor placed between the SW and BST capacitor is recommended to reduce SW voltage spikes.                                                                 |

| 18, 19, 21       | GND     | Power ground.                                                                                                                                                                                                                                                                                               |

| 20               | VCC2    | Internal 3.6V LDO regulator output. Decouple with a 4.7µF capacitor.                                                                                                                                                                                                                                        |

| 22               | CC2     | <b>Configuration channel.</b> CC2 detects connections and configures the interface across the USB Type-C cables and connectors. Once a connection is established, CC1 or CC2 is reassigned to provide power over the VCONN pin of the plug.                                                                 |

# **ABSOLUTE MAXIMUM RATINGS (1)** Supply voltage V<sub>IN</sub>.....-0.4V to +40V V<sub>SW</sub>.....-0.3V (-5V for <10ns) to $V_{IN} + 0.3V$ (43V for <10ns) CC1, CC2, DM, DP......-0.3V to +18V V<sub>BST</sub> ......V<sub>SW</sub> + 5.5V VEN/SYNC ......-0.3V to +6V (2) Vvcc2.....-0.3V to +4V Continuous power dissipation ( $T_A = 25^{\circ}C$ ) (3) (5) QFN-22 (4mmx4mm)......4.3W Junction temperature ...... 150°C Storage temperature......-65°C to +150°C ESD Rating Human-body model (HBM): ±8kV HBM ESD Rating for CC1, CC2 and USB OUT to GND: ±2.5kV HBM ESD rating for DM, DP to GND; other pins pass ±2kV Charged-device model (CDM) ..... .....all pins pass ±2kV Recommended Operating Conditions (4) Operation input voltage range...... 6V to 36V Output voltage range......3.6V to 12V or VINxMax duty Output current......3A Operating junction temp. (T<sub>J</sub>)...-40°C to +125°C

| Thermal Resistance      | $oldsymbol{	heta}$ JA | $\boldsymbol{\theta}$ JC |      |

|-------------------------|-----------------------|--------------------------|------|

| QFN-22 (4mmx4mm)        |                       |                          |      |

| EVQ4482-Q-R-00A (5)     | 29                    | 7                        | °C/W |

| JESD51-7 <sup>(6)</sup> | 44                    | 9                        | °C/W |

#### Notes:

- Exceeding these ratings may damage the device.

- See the EN Control section on page 12 for more details on the EN pin's ABS Max rating.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{\text{JA}},$  and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ (MAX) - T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on EVQ4482-Q-R-00A, 4-layer PCB, 57mmx57mm

- Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application

5

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                               | Symbol                  | Condition                                                   | Min  | Тур  | Max  | Units |

|---------------------------------------------------------|-------------------------|-------------------------------------------------------------|------|------|------|-------|

| Complete programme (Christolesses)                      |                         | V <sub>EN</sub> = 0V,T <sub>J</sub> = 25°C                  |      |      | 1    |       |

| Supply current (Shutdown)                               | lin                     | $V_{EN} = 0V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ |      |      | 8    | μA    |

| Buck_Supply current (Quiescent)                         | IQ_CL_VBUSDIS           | CC pin float, V <sub>FB</sub> = 1V                          |      | 600  | 900  | μA    |

| Overall_Supply current (Quiescent)                      | ΙQ                      | CC1 to ground with 5.1k $\Omega$ , V <sub>FB</sub> = 1V     |      | 800  | 1200 | μA    |

| EN rising threshold                                     | V <sub>EN_Rising</sub>  |                                                             | 1.15 | 1.4  | 1.65 | V     |

| EN falling threshold                                    | V <sub>EN_Falling</sub> |                                                             | 1.05 | 1.25 | 1.45 | V     |

| EN input ourrent                                        | l <sub>EN1</sub>        | V <sub>EN</sub> = 2V<br>V <sub>EN</sub> = 0                 |      | 4.5  | 6    |       |

| EN input current                                        | I <sub>EN2</sub>        |                                                             |      | 0    | 0.2  | μA    |

| Thermal shutdown (7)                                    | T <sub>STD</sub>        |                                                             |      | 165  |      | °C    |

| Thermal hysteresis (7)                                  | T <sub>STD_HYS</sub>    |                                                             |      | 20   |      | °C    |

| VCC1 regulator                                          | V <sub>CC1</sub>        | I <sub>CC</sub> = 0mA                                       | 4.6  | 4.8  | 5.1  | V     |

| VCC1 load regulation                                    | V <sub>CC1_LOG</sub>    | I <sub>CC</sub> = 5mA                                       |      | 1.5  | 5    | %     |

| VCC2 regulator                                          | V <sub>CC2</sub>        | Icc = 0mA                                                   | 3.3  | 3.6  | 3.7  | V     |

| Step-Down Converter                                     |                         |                                                             |      |      |      |       |

| V <sub>IN</sub> under-voltage lockout rising threshold  | V <sub>IN_UVLO</sub>    |                                                             | 3.3  | 3.5  | 3.7  | V     |

| V <sub>IN</sub> under-voltage lockout falling threshold | Vuvlo_fall              |                                                             | 3.1  | 3.3  | 3.5  | V     |

| HS switch-on resistance                                 | Rdson_hs                |                                                             |      | 85   | 150  | mΩ    |

| LS switch-on resistance                                 | RDSON_LS                |                                                             |      | 55   | 105  | mΩ    |

| Feedback voltage                                        | $V_{FB}$                |                                                             | 780  | 796  | 812  | mV    |

| Feedback current                                        | I <sub>FB</sub>         | V <sub>FB</sub> = 820mV                                     |      | 10   | 100  | nA    |

| Sync frequency range                                    | fsync                   |                                                             | 0.25 |      | 2.2  | MHz   |

| Oscillator frequency                                    | fsw <sub>1</sub>        | FREQ = GND                                                  | 350  | 440  | 530  | kHz   |

| Coomator requertoy                                      | fsw <sub>2</sub>        | FREQ = Float                                                | 210  | 280  | 350  | kHz   |

| Fold-back frequency                                     | f <sub>FВ</sub>         | V <sub>FB</sub> < 400mV                                     |      | 100  |      | kHz   |

| Maximum duty cycle                                      | D <sub>MAX</sub>        |                                                             | 94.5 | 96   |      | %     |

| Switch leakage                                          | SW <sub>LKG</sub>       | $V_{EN} = 0V$ , $V_{SW} = 36V$ , $T_J = 25$ °C              |      |      | 1    | μA    |

| Switch leakage                                          | OVVLKG                  | $V_{EN} = 0V$ , $V_{SW} = 36V$ , $T_{J} = -40$ °C to+125°C  |      |      | 5    | μΛ    |

| High-side current limit (7)                             | ILIMIT                  | Over 40% duty cycle                                         | 4.8  | 6.8  | 8.8  | Α     |

| Minimum on time (7)                                     | ton_min                 |                                                             |      | 70   |      | ns    |

| Soft start time                                         | tss                     | Output from 10% to 90%                                      | 0.4  | 1.5  | 2.55 | ms    |

| USB Switch                                              |                         |                                                             |      |      |      |       |

| Under-voltage lockout rising threshold                  | V <sub>USB_UVR</sub>    |                                                             | 2.6  | 2.8  | 3    | V     |

| Under-voltage lockout hysteresis threshold              | Vusb_uvhys              |                                                             |      | 370  |      | mV    |

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, Typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                         | Symbol                     | Condition                                                            | Min   | Тур   | Max   | Unit<br>s |  |

|-----------------------------------|----------------------------|----------------------------------------------------------------------|-------|-------|-------|-----------|--|

| Switch on resistance              | RDSON_SW                   |                                                                      |       | 20    | 45    | mΩ        |  |

| Output discharge resistance       | RDIS_USB                   |                                                                      | 150   | 200   | 250   | Ω         |  |

|                                   | V <sub>USB_OUT1</sub>      | Default                                                              | -3%   | 5.1   | +3%   | V         |  |

| USB output voltage                | Vusb_out2                  | QC 3.0, T <sub>J</sub> = 25°C                                        | -1.5% | 9     | +1.5% | V         |  |

|                                   | Vusb_out3                  | QC 3.0, T <sub>J</sub> = 25°C                                        | -1.5% | 12    | +1.5% | V         |  |

| Current limit                     | I <sub>Limit1</sub>        | V <sub>OUT</sub> drop 10%                                            | 3.18  | 3.55  | 3.93  | Α         |  |

| USB_OUT soft start time           | Tss                        | V <sub>OUT</sub> = 5V, from 10% to 90%                               | 0.2   | 0.45  | 0.7   | ms        |  |

| USB input OVP rising              | V <sub>USB_OV</sub>        | V <sub>OUT</sub> = 5V                                                | 5.5   | 5.75  | 6     | V         |  |

| USB input OVP recovery threshold  | Vov_Recovery               | V <sub>OUT</sub> = 5V                                                | 5.25  | 5.45  | 5.65  | V         |  |

| Hiccup mode on time               | T <sub>HICP_ON2</sub>      | Vout =5V, OC                                                         |       | 2     |       | ms        |  |

| Hiccup mode off time              | THICP_OFF                  | V <sub>OUT</sub> = 5V, V <sub>BUS</sub> connected to GND             |       | 2     |       | s         |  |

| Line drop compensation            | V <sub>IN_5_C</sub>        | Vout = 5V, Iout = 3A                                                 |       | 260   | 400   | mV        |  |

| BC1.2 DCP Mode                    |                            |                                                                      | •     | •     |       |           |  |

|                                   | R <sub>DP/DM_Short</sub>   | V <sub>DP</sub> = 0.8V, I <sub>DM</sub> = 1mA, T <sub>J</sub> = 25°C |       |       | 40    | Ω         |  |

| DP and DM short resistance        |                            | $V_{DP} = 0.8V$ , $I_{DM} = 1$ mA, $T_{J} = -40$ °C to $+125$ °C     |       |       | 45    |           |  |

| Divider Mode                      |                            |                                                                      |       |       |       |           |  |

| DP/DM output voltage              | V <sub>DP/DM_Divider</sub> | der V <sub>OUT</sub> = 5V                                            |       | 2.7   | 2.85  | V         |  |

| DD/DM output impedance            | RDP/DM_Divider             | T <sub>J</sub> = 25°C                                                | 20    | 25    | 30    | kΩ        |  |

| DP/DM output impedance            |                            | T <sub>J</sub> = -40°C to +125°C                                     | 18    | 25    | 32    | K12       |  |

| 1.2V/1.2V Mode                    |                            |                                                                      |       |       |       |           |  |

| DP/DM output voltage              | V <sub>DP/DM_1.2V</sub>    | V <sub>OUT</sub> = 5V                                                | 1.1   | 1.2   | 1.3   | V         |  |

| DP/DM output impedance            | R <sub>DP/DM_1.2V</sub>    |                                                                      | 200   | 300   | 400   | kΩ        |  |

| USB Type-C 5V@3A Mode -           | - CC1 and CO               | C2                                                                   |       |       |       |           |  |

| CC voltage to enable VCONN        | $V_{Ra}$                   |                                                                      |       |       | 0.75  | ٧         |  |

| CC voltage to enable Vbus         | $V_{Rd}$                   |                                                                      | 0.85  |       | 2.45  | V         |  |

| CC voltage at 5.1kΩ Rd            | Vcc_Rd                     | CC pin pull-down by 5.1kΩ                                            | 1.31  | 1.683 | 2.04  | V         |  |

| CC detach threshold               | Vopen                      |                                                                      | 2.75  |       |       | V         |  |

| CC voltage falling debounce timer | T <sub>CC_debounce</sub>   | VBUS enable deglitch                                                 | 100   | 150   | 200   | ms        |  |

| CC voltage rising debounce timer  | T <sub>PD_debounce</sub>   | VBUS disable deglitch                                                | 5     | 10    | 20    | ms        |  |

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, Typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                           | Symbol                      | Condition                                                | Min  | Тур | Max  | Units |

|-----------------------------------------------------|-----------------------------|----------------------------------------------------------|------|-----|------|-------|

| VCONN output power                                  | Pvconn                      | VCONN comes from buck output with some series resistance | 1    |     |      | W     |

| V <sub>BUS</sub> to ground impedance                | R <sub>BUS</sub>            | ype-C detach, after output discharge 72                  |      |     |      | kΩ    |

| Quick Charge 3.0 Mode                               |                             |                                                          |      |     |      |       |

| Data detect voltage                                 | V <sub>DAT_REF</sub>        |                                                          | 0.25 | 0.3 | 0.4  | V     |

| Output voltage select ref                           | V <sub>SEL_REF</sub>        |                                                          | 1.8  | 2   | 2.2  | V     |

| DP output impendence                                | R <sub>DP_QC</sub>          |                                                          | 300  | 400 | 1500 | kΩ    |

| DM output impendence                                | R <sub>DM_QC</sub>          |                                                          | 13   | 20  | 27   | kΩ    |

| DM low glitch time (7)                              | tGlitch_DM                  |                                                          |      | 10  |      | ms    |

| DP high glitch time                                 | tGlitch_DP                  |                                                          | 800  |     | 1600 | ms    |

| Output voltage change glitch time                   | t <sub>Glitch_V_Chang</sub> |                                                          | 20   | 40  | 60   | ms    |

| Bus voltage step                                    | V <sub>BUS_CONT_S</sub>     |                                                          | 150  | 200 | 250  | mV    |

| Time for VBUS to discharge to 5V when DP < 0.6V (7) | tv_unplug                   |                                                          |      |     | 500  | ms    |

#### Notes

<sup>7)</sup> Guaranteed by engineering sample characterization

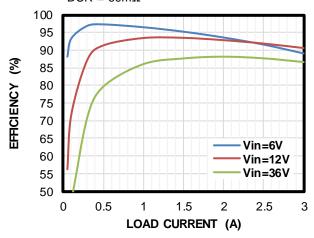

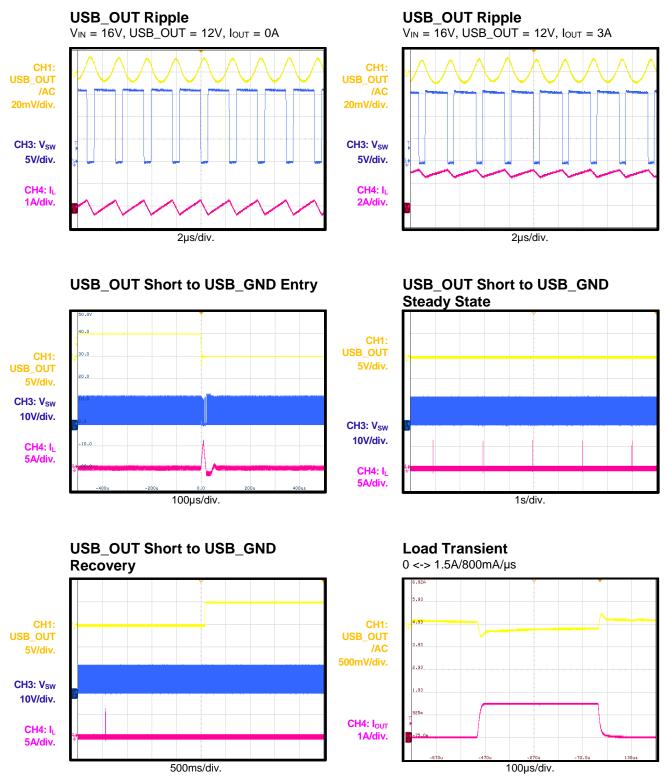

## TYPICAL CHARACTERISTICS

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10 $\mu$ H,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$  resistor,  $T_A$  = 25°C, unless otherwise noted.

**Efficiency vs. Load Current**

$V_{OUT} = 5.1V$ ,  $F_S = 450kHz$ ,  $L = 10\mu H$ ,  $DCR = 69m\Omega$

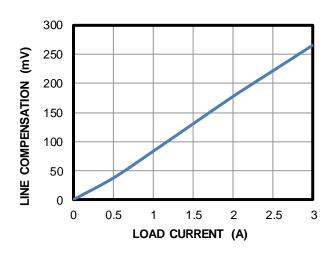

# Line Drop Compensation vs. Load Current

9

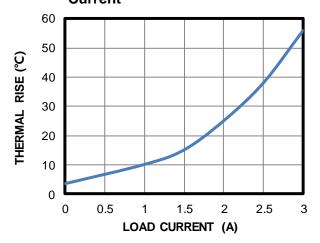

# Case Temperature Rise vs. Load Current

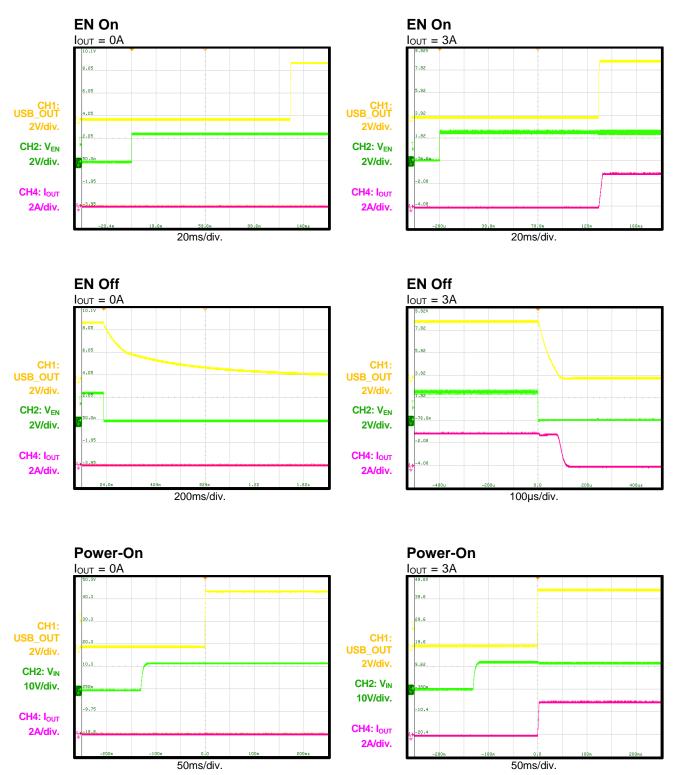

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10µH,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$  resistor,  $T_A$  = 25°C, unless otherwise noted.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10µH,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$  resistor,  $T_A$  = 25°C, unless otherwise noted.

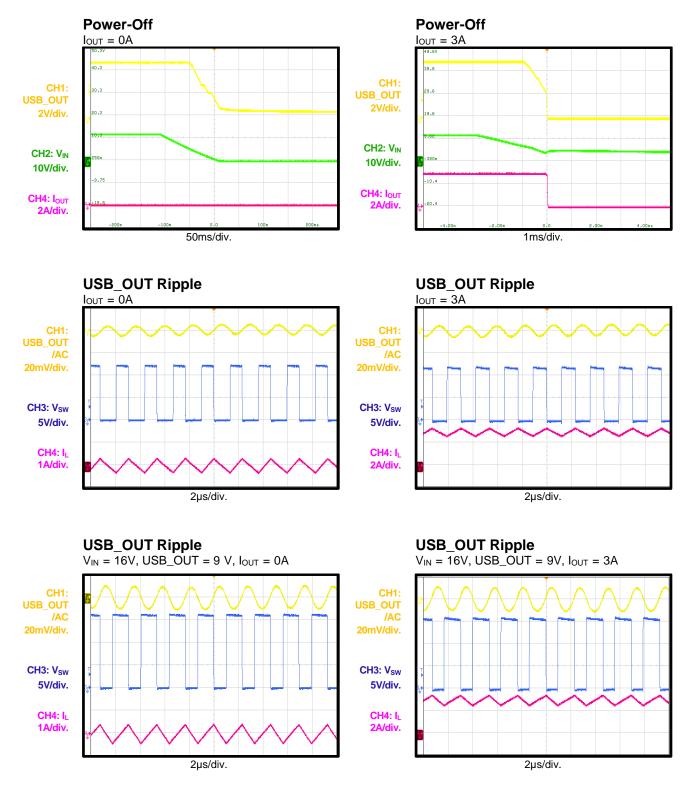

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10 $\mu$ H,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$ resistor,  $T_A = 25$ °C, unless otherwise noted.

© 2019 MPS. All Rights Reserved.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10 $\mu$ H,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$  resistor,  $T_A$  = 25°C, unless otherwise noted.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10 $\mu$ H,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$  resistor,  $T_A$  = 25°C, unless otherwise noted.

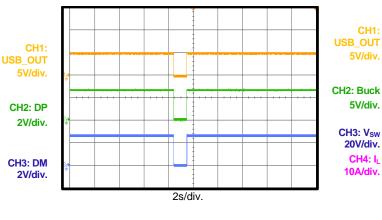

100ms/div.

2s/div.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, L = 10 $\mu$ H,  $f_{SW}$  = 450kHz, Type-C mode, CC1 to ground with a 5.1k $\Omega$ resistor,  $T_A = 25$ °C, unless otherwise noted.

CH1:

5V/div.

5V/div.

20V/div. CH4: I<sub>L</sub>

10A/div.

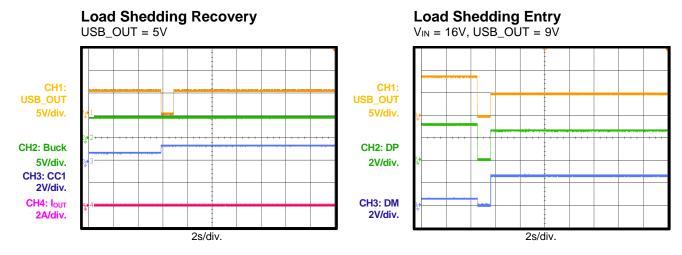

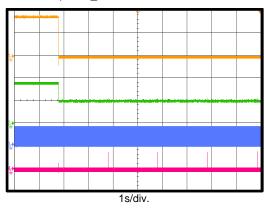

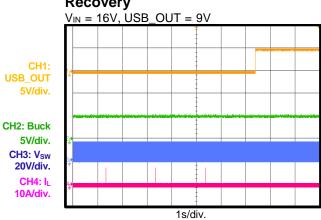

# **Load Shedding Recovery**

V<sub>IN</sub> = 16V, USB\_OUT = 9V

## **USB\_OUT Short to USB\_GND Entry**

V<sub>IN</sub> = 16V, USB\_OUT = 9V

## **USB\_OUT Short to USB\_GND** Recovery

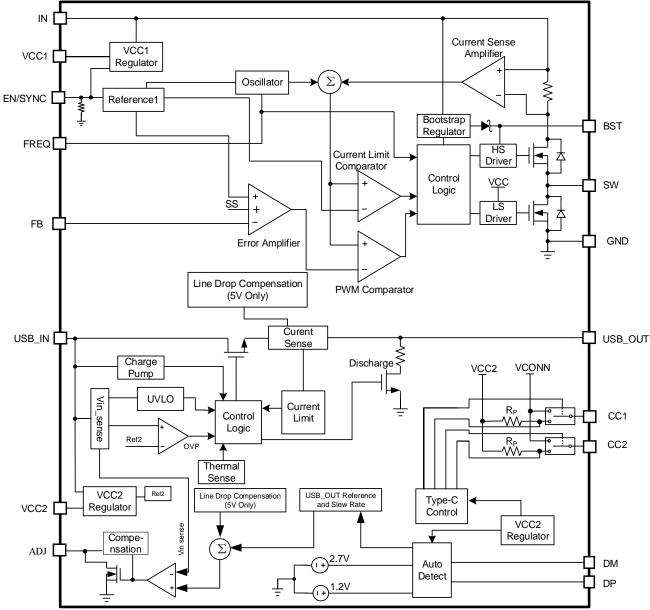

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **OPERATION**

#### **Buck Converter**

The MPQ4482-Q integrates a monolithic synchronous, rectified, step-down, switch-mode converter with internal power MOSFETs and a USB current-limit switch with charging port auto detection. It offers a compact solution to achieve 3A of continuous output current over a wide input supply range with excellent load and line regulation.

The MPQ4482-Q operates in a fixed-frequency, peak current control mode to regulate the output voltage. The internal clock initiates the PWM cycle, which turns on the integrated high-side power MOSFET. The high-side MOSFET remains on until its current reaches the value set by the COMP voltage. When the power switch is off, it remains off until the next clock cycle begins.

## **Error Amplifier (EA)**

The error amplifier (EA) compares the internal feedback voltage ( $V_{FB}$ ) against the internal 0.8V reference ( $V_{REF}$ ) and outputs a COMP voltage. This COMP voltage controls the power MOSFET current. The optimized, internal compensation network minimizes the external component count and simplifies the control loop design.

### **Internal VCC1 Regulator**

The 4.8V internal regulator powers most of the internal circuitries of the buck converter. This regulator takes the  $V_{\rm IN}$  and operates in the full  $V_{\rm IN}$  range. When  $V_{\rm IN}$  exceeds 4.8V, the output of the regulator is in full regulation. If  $V_{\rm IN}$  is below 4.8V, the output decreases with the  $V_{\rm IN}$ . The VCC requires an external 0.1µF ceramic decoupling capacitor.

#### **Internal VCC2 Regulator**

The 3.6V internal regulator powers most of the USB switch's internal circuitries. The VCC2 requires an external  $4.7\mu F$  ceramic decoupling capacitor.

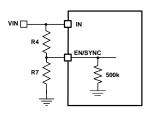

#### **EN/SYNC Control**

The MPQ4482-Q has an enable control pin (EN). Pull EN high to enable the IC; pull EN low to disable the IC. An internal  $500k\Omega$  resistor from EN/SYNC to GND allows EN/SYNC to be floated to shut down the chip.

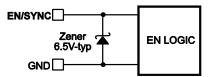

EN/SYNC is clamped internally using a 6.5V series Zener diode (see Figure 2). Connect the EN/SYNC input through a pull-up resistor to any voltage connected to VIN. The pull-up resistor limits the EN/SYNC input current below 100μA. For example, when 12V is connected to VIN,  $R_{PULLUP} \ge (12V - 6.5V) / 100μA = 55kΩ$ .

Connecting EN/SYNC directly to a voltage source without a pull-up resistor requires limiting the voltage amplitude below or equal to 6V to prevent damage to the Zener diode.

Figure 2: 6.5V-Type Zener Diode

To use the synchronous function, connect an external clock within the range 250kHz to 2.2MHz to EN/SYNC. The external clock should be connected at least 2ms after the output voltage is set. The internal clock rising edge is synchronized to the external clock rising edge when the external clock is connected. The pulse width of the external clock signal should be shorter than 1.7 $\mu$ s. The SYNC input signal typically has a 15% duty cycle when V<sub>IN</sub> = 12V.

### Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The UVLO comparator monitors the input voltage. The UVLO rising threshold is 3.5V, and its falling threshold is 3.3V.

### **Internal Soft Start (SS)**

The soft start (SS) prevents the converter output voltage from overshooting during start-up. When the chip starts up, the internal circuitry generates a SS voltage that ramps up from 0V to 5V. When SS is below  $V_{\text{REF}}$ , the error amplifier uses SS as the reference. When SS is above  $V_{\text{REF}}$ , the error amplifier uses  $V_{\text{REF}}$  as the reference. The SS time is internally set to 1.5ms.

If the output of the MPQ4482-Q is pre-biased to a certain voltage during start-up, the IC disables the switching of both the high-side and low-side

switches until the voltage on the internal SS capacitor exceeds the internal feedback voltage.

### **Buck Over-Current Protection (OCP)**

The MPQ4482-Q has a cycle-by-cycle over-current limit when the inductor peak current exceeds the current-limit threshold, and  $V_{FB}$  drops below the under-voltage (UV) threshold (about 50% below the reference). Once UV triggers, the MPQ4482-Q enters hiccup mode to re-start the part periodically. This protection mode is especially useful when the output is dead-shorted to ground. This greatly reduces the average short-circuit current, alleviates thermal issues, and protects the regulator. The MPQ4482-Q exits hiccup mode once the over-current condition is removed.

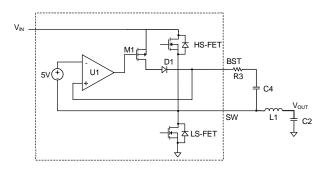

## Floating Driver and Bootstrap Charging

An external bootstrap capacitor powers the floating power MOSFET driver. This floating driver has its own UVLO protection. The UVLO's rising threshold is 2.2V with a hysteresis of 150mV. The bootstrap capacitor voltage is regulated internally by VIN through D1, M1, C4, L1 and C2 (see Figure 3). If the difference between  $V_{\text{BST}}$  and  $V_{\text{SW}}$  exceeds 5V, U1 regulates M1 to maintain a 5V BST voltage across C4. To reduce SW spike voltage, place a  $20\Omega$  resistor between SW and the BST capacitor.

Figure 3: Internal Bootstrap Charging Circuit

#### Start-Up and Shutdown

If both VIN and EN exceed their respective thresholds, the chip enables. The reference block starts by generating a stable reference voltage and current. Next, the internal regulator enables. The regulator provides a stable supply for the remaining circuitries.

Several events can shut down the chip: when EN is low, when VIN is low, and thermal shutdown triggers. In shutdown, the signaling path is blocked to avoid any fault triggering. Then the COMP voltage and the internal supply rail are pulled down. The floating driver is not subject to this shutdown command.

# USB Charging Port Controller Section Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at insufficient supply voltage. If the input voltage exceeds the USB's SW UVLO threshold, the power MOSFET turns on with a controlled slew rate after a fixed delay.

#### **Internal Soft Start**

The internal soft start prevents the output voltage from overshooting during start-up and inrush current.

#### **Line Drop Compensation**

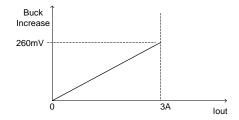

The MPQ4482-Q compensates for an output voltage drop, such as high impedance caused by a long trace, to maintain a 5.1V load-side voltage. The line drop compensation is only active when  $V_{\text{IN}}$  equals 5.1V. The line drop compensation is realized through the ADJ pin.

The MPQ4482-Q increases USB input voltage by 260mV at a 3A output current (see Figure 4).

Figure 4: Increasing USB Input Voltage

The ADJ pin slowly sinks a controlled current. The line drop compensation amplitude linearly increases as the load current increases.

If the USB input voltage is below 5.1V in a no load condition, the ADJ pin sinks a current to regulate the upstream regulator's output voltage to 5.1V. If the USB input voltage exceeds 5.1V, the MPQ4482-Q does not regulate the input voltage. To maintain a 3.6V to 12V output voltage range, configure R1/R2 to let default output voltage to remain below 3.6V. It is

recommended to set the buck to 3.5V, meaning R1 is  $39k\Omega$ , and R2 is  $11.5k\Omega$ .

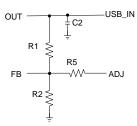

Figure 5 shows the typical schematic for ADJ usage. The ADJ pin sink current capability is 500uA. The feedback current through R1 must remain below 500uA. R1 can be calculated with Equation (1):

$$R1(k\Omega) > \frac{\Delta V(V)}{0.5}$$

(1)

Where  $\Delta V$  is the output differential voltage value between the QC3.0 max voltage and the voltage buck sets.

Figure 5: ADJ Configuration

To limit the maximum output current,  $V_{ADJ}$  can also be configured by inserting R5 between the FB pin and the ADJ pin. With R5, the maximum output voltage can be estimated with Equation (2):

$$V_{OUT\_Max}(V) = \frac{R_1 + R_2 // R_5}{R_2 // R_5} \times V_{FB}(V)$$

(2)

After adding R5, the maximum ADJ sink current can be calculated with Equation (3):

$$I_{ADJ\_Max} (\mu A) = \frac{V_{FB} - V_{OFFSET}(mV)}{R_{\epsilon}(k\Omega)}$$

(3)

Where VOFFSET is about 100mV.

#### **USB Input Over-Voltage and Discharge**

To protect downstream devices from overvoltage, the MPQ4482-Q provides a USB input OVP discharge function. The device has a smart OVP threshold for different Vouts. IC dynamically sets the OVP threshold to 115% of the  $V_{\text{OUT}}$  target value.

An accurate and fast comparator monitors the over-voltage condition of the USB input. If the input voltage rises above the threshold, the USB discharge path turns on. When input

voltage falls below 5.45V, the IC exits OVP mode.

#### **Output Discharge**

When the Type-C device plugs out, both input and output discharge resistors activate for 30ms, and then turn-off. After turn-off, the in and out to ground resistance is high (>72.4k $\Omega$ ).

#### **Over-Current Protection**

Once the device reaches its current limit threshold, the internal circuit regulates the gate voltage to hold the current in the power FET constant.

If an over-current (OC) condition lasts 2ms or the USB output voltage falls below 3V, the MPQ4482-Q enters hiccup mode.

In hiccup mode, the MPQ4482-Q turns off the power MOSFET. The hiccup signal resets the QC mode to 5V. ADJ changes  $V_{\text{IN}}$  to 5V. After two seconds (hiccup off-timer), the MPQ4482-Q restarts to check the OC state. If the OC remains, the MPQ4482-Q follows the previous operation. If the OC has been removed, the MPQ4482-Q recovers to normal operation in 5V mode.

#### **USB Short-Circuit Protection**

If the load current increases rapidly due to a short circuit, the current may exceed the current limit threshold before the control loop can respond. If the current reaches an internal secondary current limit level (about 9A), a fast turn-off circuit activates to turn off the power FET. This limits the peak current through the switch to limit the input voltage drop. The fast-off response time is about 300ns. If fast-off works, the device enters hiccup mode directly. After the short-circuit condition is removed, the MPQ4482-Q recovers automatically.

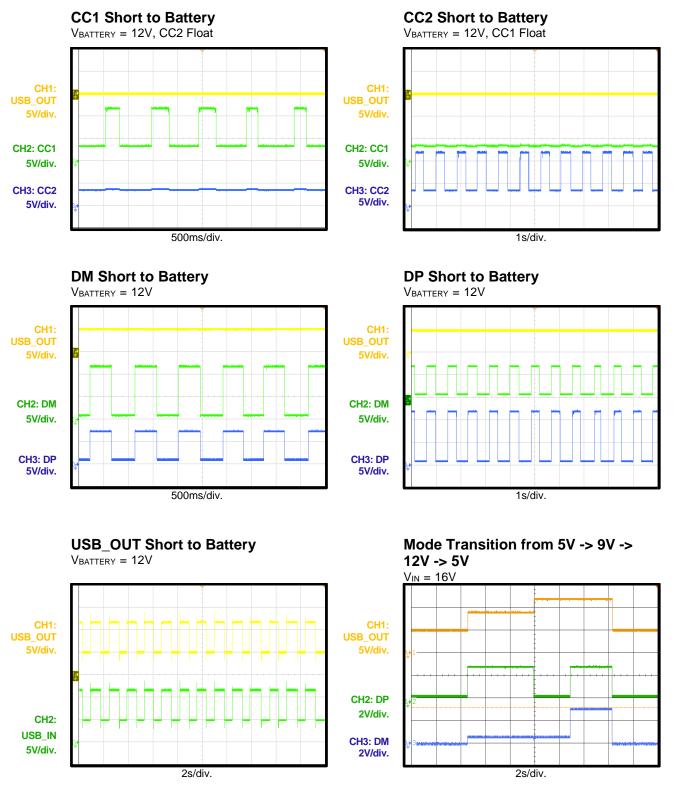

#### **Short to Battery Protection**

The MPQ4482-Q provides USB\_OUT, CC1, CC2, DP and DM short to battery protections when the IC is enabled and VBUS is on.

During USB output short to battery condition, the USB input rises up to trigger OVP. The USB input discharge path turns on. Meanwhile, the buck regulator discharges the buck output voltage by turning on the low-side switch periodically.

During DP, DM, CC1, or CC2 shorts to battery condition, the MPQ4482-Q can withstand the high voltage for the internal components. The ESD breakdown voltage exceeds the battery voltage.

If a CC1 or CC2 short to battery should occur when the Type-C port is connected but there is no sink, the device is unattached (see Figure 6).

Figure 6: Short to Battery Set-Up

#### **Auto Detection**

The MPQ4482-Q integrates the USB-dedicated charging port auto-detect function. This function recognizes most mainstream portable devices. It supports the following charging schemes:

- USB Battery Charging Specification BC1.2/ Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider mode

- 1.2V/1.2V mode

- USB Type-C 5V@3A mode

- Quick Charge 3.0 mode Class A

The auto-detect function is a state machine that supports all of the DCP charging schemes above.

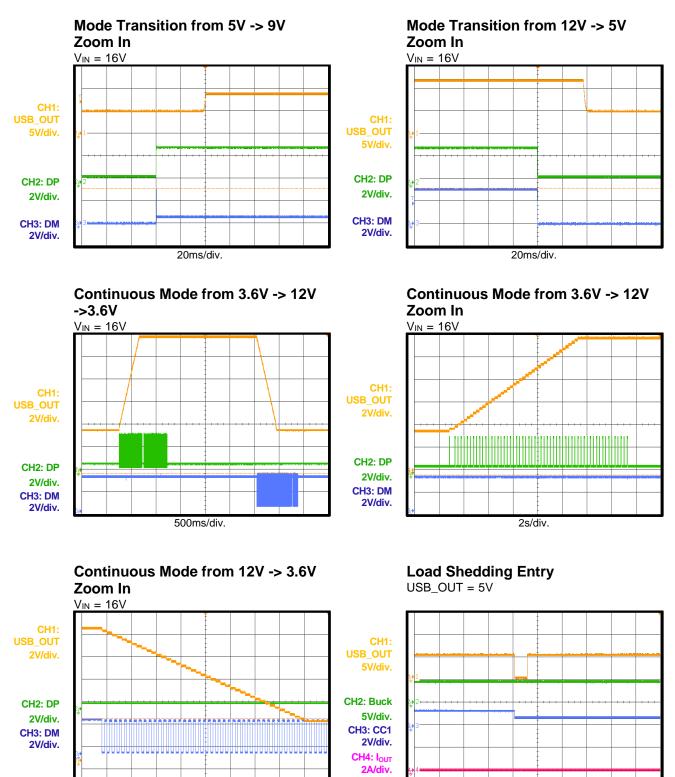

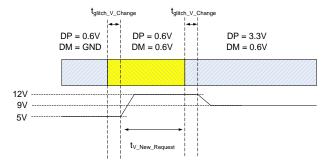

#### QC Mode Voltage Transition - Class A

If the downstream device supports the QC specification, the device requires an output above voltage 5V by DM and communication (see Table 1). If a higher USB bus voltage is required, the ADJ pin must be used. The ADJ pin is usually connected to the upstream voltage converter's feedback pin. After the handshake, ADJ adjusts V<sub>OUT</sub> within the range 9V to 12V or another voltage 200mV step-by-step (see Figure 7). Due to smart controller mode, only one ADJ pin can be set to a different, high voltage that meets the QC

specification. The output transition is smooth and does not have an undershoot or overshoot.

**Table 1: QC Mode Definition**

| Portable Device |      | USB Bus Voltage                           |  |

|-----------------|------|-------------------------------------------|--|

| DP              | DM   | OSB Bus Vollage                           |  |

| 0.6V            | 0.6V | 12V                                       |  |

| 3.3V            | 0.6V | 9V                                        |  |

| 0.6V            | 3.3V | 3.6V to 12V/200mV step according to QC3.0 |  |

| 3.3V            | 3.3V | No action                                 |  |

| 0.6V            | GND  | 5V                                        |  |

When the downstream device is removed, the output voltage automatically returns to a default 5V. The input to ground discharge resistor helps this procedure quickly.

Figure 7: QC Mode Transition

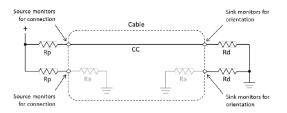

#### **USB Type-C Mode and VCONN**

For the USB Type-C solution, two pins on the connector, CC1 and CC2, establish and manage the source-to-sink connection. The general concept for setting up a valid connection between a source and sink is based on being able to detect terminations residing in the product being attached. To define the functional behavior of CC, a pull-up (Rp) and pull-down (Rd  $5.1k\Omega$ ) termination model is used based on a pull-up resistor and pull-down resistor (see Figure 8).

10/15/2019

Figure 8: Current Source/Pull-Down CC Model

Initially, a Source exposes independent Rp terminations on its CC1 and CC2 pins, and a sink exposes independent Rd terminations on its CC1 and CC2 pins, the source-to-sink circuit configuration combination of this represents a valid connection. To detect this, the source monitors CC1 and CC2 for a voltage lower than its unterminated voltage. Rp is designated as a function of the pull-up termination voltage and the source's detection circuit. This indicates that either a sink, a powered cable, or a sink connected via a powered cable has been attached.

Two special termination combinations on the CC pins as seen by a source are defined for directly attached accessory modes: Ra/Ra for audio adapter accessory mode and Rd/Rd for debug accessory mode. V<sub>BUS</sub> disables for those two cases.

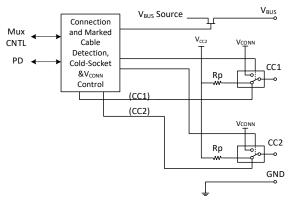

Figure 9: CC Pin Functional Block

- 1. The Source uses an FET to enable or disable power delivery across  $V_{\text{BUS}}$  when the source is initially disabled.

- 2. The Source supplies pull-up resistors (Rp) on CC1 and CC2 and monitors both pins to detect a sink. The presence of an Rd pull-down resistor on either pin indicates that a sink is being attached. The value of Rp indicates the initial USB Type-C current level supported by

the host. The MPQ4482-Q's default Rp is  $4.7k\Omega$  and represents a 3A current level.

- 3. The source uses the CC pin pull-down function to detect and determine which CC pin is intended for supplying VCONN (when Ra is discovered).

- 4. Once a sink is detected, the source enables VBUS and VCONN.

- 5. The source dynamically adjusts the value of Rp to indicate a change in available USB Type-C current to a dink. (e.g at high temperatures, the MPQ4482-Q changes Rp to  $12k\Omega$  to indicate a 1.5A current ability).

- 6. The source monitors the continued presence of Rd to detect sink detaches. When a detach event is detected, the source removes. VBUS and VCONN return to step 2.

#### Type-C Load Shedding versus Temperature

When the sensed temperature exceeds 120°C, the USB port's CC pin pull-up resistance Rp changes to  $12k\Omega$  to advertise its source capability changes to 1.5A. The internal Rd detection threshold also changes from 0.4V to 1.6V. The Ra detection threshold becomes lower than 0.4V. If the sensed temperature exceeds 85°C and lasts 16s, the USB type-C current capability changes back to 3A (Rp =  $4.7k\Omega$ ).

In QC3.0 charging mode, the VBUS restarts to 5V in DCP charging mode if load shedding occurs. When the device exits load shedding, the VBUS restarts and QC3.0 enables.

The load shedding function works when USB IN > UVLO.

#### System

## Thermal Shutdown (TSD)

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 165°C, it shuts down the entire chip. When the temperature falls below its lower threshold, (about 145°C), the chip enables.

#### APPLICATION INFORMATION

# Design example for the ADJ resistor, R1, R2 and RT resistors

The resistors of the ADJ resistor, R1 and R2, are limited by the ADJ sink capability and maximum output voltage.

The ADJ pin's sink current capability is  $500\mu A$ . To achieve a 12V output voltage during QC 3.0 mode and let the feedback current flowing through R1 remain below  $500\mu A$ , R1 should meet the below equation.  $\Delta V$  is the output differential voltage value set by subtracting the voltage buck sets from the QC3.0 max voltage. If the buck set output is 3.5V, R1 can be estimated with Equation (4):

R1(k\O) >

$$\frac{\Delta V(V)}{0.5} = \frac{12 - 3.5}{0.5} = 17k\Omega$$

(4)

R1 must remain greater than  $17k\Omega$  to provide an 8.5V buck output voltage change. If R1 equals  $39k\Omega$ . R2 can be calculated with Equation (5):

$$R2(k\Omega) = \frac{V_{FB} \times R_1}{V_{RLICK} - V_{FB}}$$

(5)

Set  $V_{BUCK}$  to 3.5V, then R2 is 11.5k $\Omega$ .

When R1 and R2 are determined, the ADJ pin's current through the R1 at 12V<sub>OUT</sub> can be calculated with Equation (2):

$$I_{ADJ}(\mu A) = \frac{\Delta V(mV)}{R_{s}(k\Omega)} = \frac{8500}{39} = 218\mu A$$

R5's maximum value can be calculated with Equation (4):

$$R_{_{5}}(k\Omega) < \frac{V_{_{FB}} - V_{_{OFFSET}}(V)}{I_{_{AD,I}}} = \frac{0.796 - 0.1}{0.218} = 3.19k\Omega$$

Then select R5 to equal 2kΩ.

RT + R1 sets the loop bandwidth. The higher RT + R1, the lower the bandwidth. To ensure loop stability, it is recommended to limit the bandwidth between one fifth and one tenth of switching frequency. If R1 is  $39k\Omega$ , make RT  $51k\Omega$  or choose a higher resistance.

#### Selecting the Inductor

For most applications, use an inductor with a DC current rating at least 125% of the maximum load current. Select an inductor with

a small DC resistance for optimum efficiency. The inductor value can be calculated with Equation (6):

$$L_{1} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{I} \times f_{OSC}}$$

(6)

Where  $\Delta I_{\perp}$  is the inductor ripple current.

Choose the inductor ripple current at approximately 30% to 80% of the maximum load current. The maximum inductor peak current can be estimated with Equation (7):

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

(7)

Inductor peak current must be lower than buck peak current limit.

#### **Selecting Buck Input Capacitor**

The input current to the step-down converter is discontinuous, and requires a capacitor to supply the AC current while maintaining the DC input voltage. Use low ESR capacitors for optimum performance. Ceramic capacitors with X5R or X7R dielectrics are recommended because of their low ESR and small temperature coefficients. For automotive applications, it is recommended to use a 100µF electrolytic capacitor, two 10µF ceramic capacitors, and one 0.1µF ceramic capacitor.

The input capacitor (C1) absorbs the input switching current, and requires an adequate ripple-current rating. The RMS current in the input capacitor can be estimated with Equation (8):

$$I_{C1} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(8)

Equation (9) shows the worst case condition when  $V_{IN} = 2V_{OUT}$ , where:

$$I_{C1} = \frac{I_{LOAD}}{2} \tag{9}$$

For simplification, choose an input capacitor with a RMS current rating greater than half of the maximum load current.

The input capacitor can be electrolytic, tantalum or ceramic. When using an electrolytic capacitor, place two additional high-quality ceramic capacitors as close to IN as possible. The input

voltage ripple can be calculated with Equation (10):

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_{S} \times C1} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(10)

#### **Selecting a Buck Output Capacitor**

The device requires an output capacitor (C2) to maintain the DC output voltage. The output voltage ripple can be estimated with Equation (11):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L_{1}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C2}\right)$$

(11)

Where  $L_1$  is the inductor value and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of the output capacitor.

For an electrolytic capacitor, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be estimated with Equation (12):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L_{1}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times R_{\text{ESR}}$$

(12)

The characteristics of the output capacitor affect the stability of the regulatory system.

For applications, it is recommended to use a  $100\mu F$  electrolytic capacitor with low ESR and two  $10\mu F$  ceramic capacitors or four  $22\mu F$  ceramic capacitors.

#### **Other Considerations**

Add a 1nF capacitor to CC1 to ensure Type-C mode can be distinguished. See the typical schematic on page 2 for more information.

#### V<sub>IN</sub> Under-Voltage Lockout (UVLO) Setting

The MPQ4482-Q has an internal, fixed, undervoltage lockout (UVLO) threshold. The rising threshold is 3.5V, while its falling threshold is about 3.3V. To raise the UVLO point, place an external resistor divider between EN/SYNC and IN (see Figure 9).

Figure 9: Adjustable UVLO using EN/SYNC Divider

The UVLO threshold can be calculated with Equation (13) and Equation (14):

$$INUV_{RISING} = \left(1 + \frac{R4}{500k/R7}\right) \times V_{EN\_RISING}$$

(13)

$$INUV_{FALLING} = \left(1 + \frac{R4}{500k//R7}\right) \times V_{EN\_FALLING}$$

(14)

Where  $V_{\text{EN\_RISING}}$  is 1.4V and  $V_{\text{EN\_FALLING}}$  is 1.25V.

When selecting R4, ensure that it is large enough to limit the current flowing into EN/SYNC below 150µA.

When R4 =  $100k\Omega$ , and R7 =  $24k\Omega$ , the MPQ4482-Q powers up when  $V_{IN}$  exceeds 7.23V. The MPQ4482-Q powers off when  $V_{IN}$  drops below 6.2V.

When R4 =  $100k\Omega$ , and R7 =  $22k\Omega$ , the MPQ4482-Q powers up when Vin exceeds 7.76V. The MPQ4482-Q powers off when V<sub>IN</sub> drops below 6.65V.

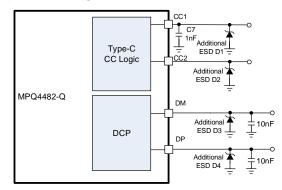

#### **ESD Protection for I/O Pins**

Consider high ESD levels for all USB I/O pins. To further extend the DP, DM, CC1, and CC2 pins' ESD level to cover complicated application environments, add an additional ESD diode to all pins (see Figure 10).

Figure 10: Recommended I/O Pins to Enhance ESD

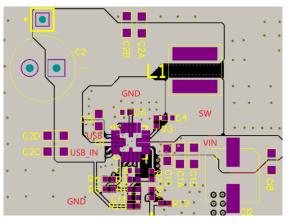

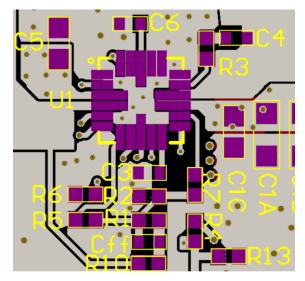

### PCB Layout (8)

Efficient PCB layout is critical for standard operation. Use 4 layers for the PCB to improve thermal performance and dissipation. For the best results, see Figure 11 and the PCB layout guidelines below:

- Place the ceramic input capacitor as close to IN and GND as possible, especially the small package size (0603) input bypass capacitor.

- 2. Keep the connection between the input capacitor and IN as short and wide as possible.

- 3. Place the VCC1/2 capacitor as close as possible to VCC1/2 and GND.

- 4. Make VCC1/2's trace length from the capacitor to GND as short as possible.

- 5. Use a large ground plane connected directly to GND.

- 6. Add vias near GND if the bottom layer is the ground plane.

- 7. Route SW and BST away from sensitive analog areas such as FB.

- 8. Place the T-type feedback resistor close to the chip to ensure that the trace connecting to FB is as short as possible.

- 9. Ensure the SW area is small to reduce EMC-radiated noise.

Top layer

Figure 11: PCB Layout

#### Notes:

8) The recommended layout is based on the typical application circuit (see Figure 12). Some of the resistor or capacitor names may be different.

10/15/2019

# TYPICAL APPLICATION CIRCUITS

Figure 12: 12Vin, USB Type-C 5V@3A DFP and QC3.0 mode

Figure 13: 12Vin, USB Type-A Port and QC3.0 mode

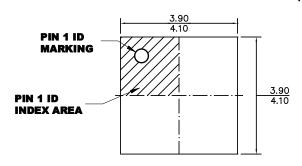

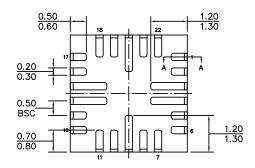

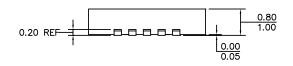

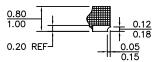

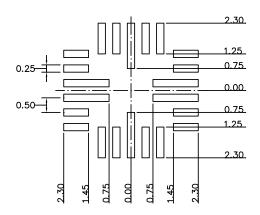

## **PACKAGE INFORMATION**

# QFN-22 (4mmx4mm)

#### **TOP VIEW**

**BOTTOM VIEW**

#### **SIDE VIEW**

**SECTION A-A**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITY SHOULD BE 0.08 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

**RECOMMENDED LAND PATTERN**

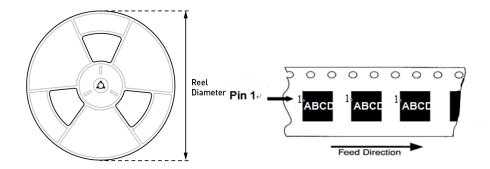

# **CARRIER INFORMATION**

| Part Number        | Package<br>Description | Quantity/<br>Reel | Quantity/Tube | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|--------------------|------------------------|-------------------|---------------|------------------|--------------------------|--------------------------|

| MPQ4482GR-Q-AEC1-Z | QFN 4x4                | 5000              | N/A           | 13in.            | 12mm                     | 8mm                      |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.