## Low Power PCIe to Gigabit Ethernet Controller with Integrated Ethernet MAC / PHY

#### Highlights

- Single Chip PCIe to 10/100/1000 Ethernet Controller with integrated:

- PCIe 3.1 PHY supporting 1 Lane at 2.5GT/s

- PCIe 3.1 Endpoint Controller Gigabit Ethernet PHY (LAN7430) RGMII v1.3 and v2.0 / MII (LAN7431)

- IEEE Std 1588<sup>™</sup>-2008 PTP

- Master and Slave Ordinary clock support

- End-to-end or peer-to-peer support

- PTP multicast and unicast message support

- PTP message transport over IPv4/v6, IEEE 802.3

- · Power Management

- PCI-PM and ASPM L0s and L1

- L1.1 and L1.2 PCIe sub-states support

- D3 hot / cold with VAUX detection for PME wakeup

- Wake on LAN support (WoL, AOAC)

- IEEE 802.3az Energy Efficient Ethernet (EEE) with 100BASE-TX/1000BASE-T Low Power Idle and 10BASE-Te TX Amplitude Reduction (LAN7430)

#### Target Applications

- Automotive Infotainment / Telematics

- PCIe to Gigabit Ethernet Adapter / Bridge

- PCIe to Gigabit Ethernet on Embedded System

- · Gigabit Backplane

- LTE Modem

- Networked Cameras

- Industrial PC (IPC)

- Test Instrumentation / Industrial

#### System Considerations

- Power and I/Os

- Single 3.3V supply operation with on-chip Switching and LDO Regulators for core and I/ Os

- GPIOs: 4 (LAN7430), 12 (LAN7431)

- Variable voltage I/O supply (1.8V, 2.5V, or 3.3V)

- Software Support

- Windows 7, 8, 8.1, 10, and OneCore drivers

- Linux driver

- Android driver

- Windows command line OTP / EEPROM

- programming and testing utility

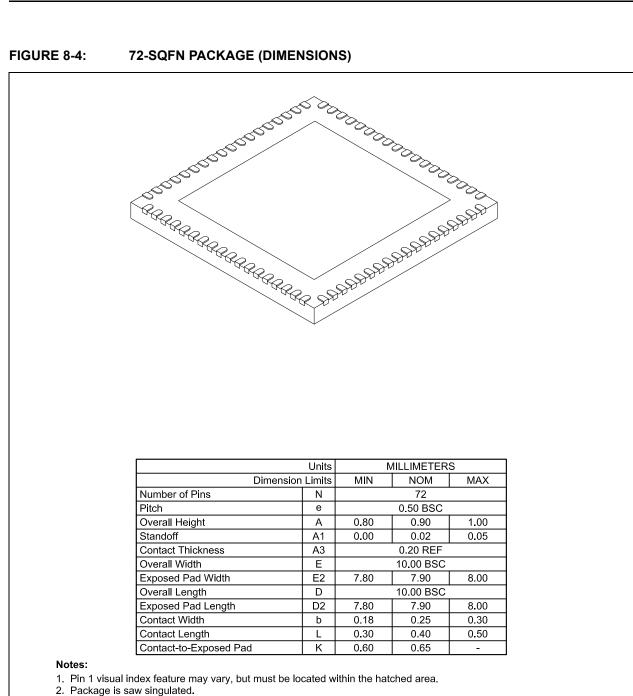

- Packaging

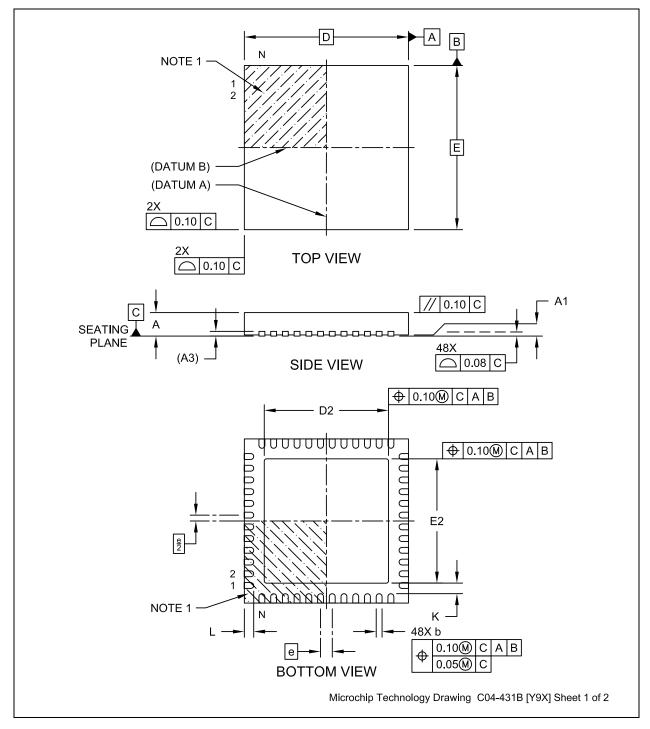

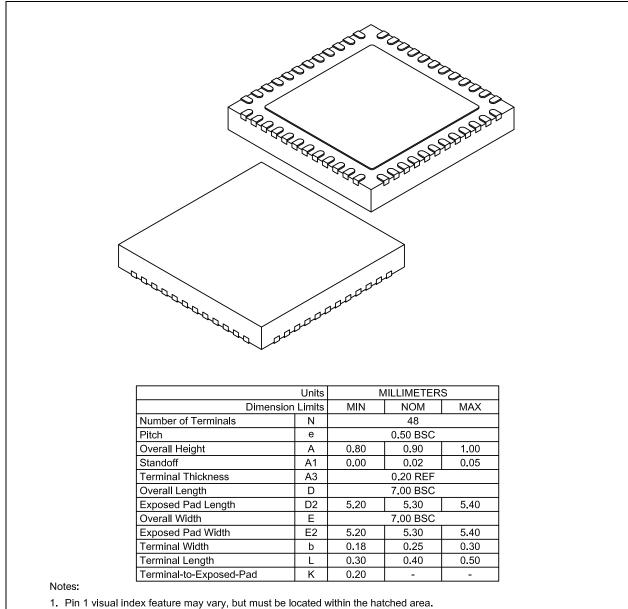

- LAN7430: 48-pin SQFN (7 x 7 mm)

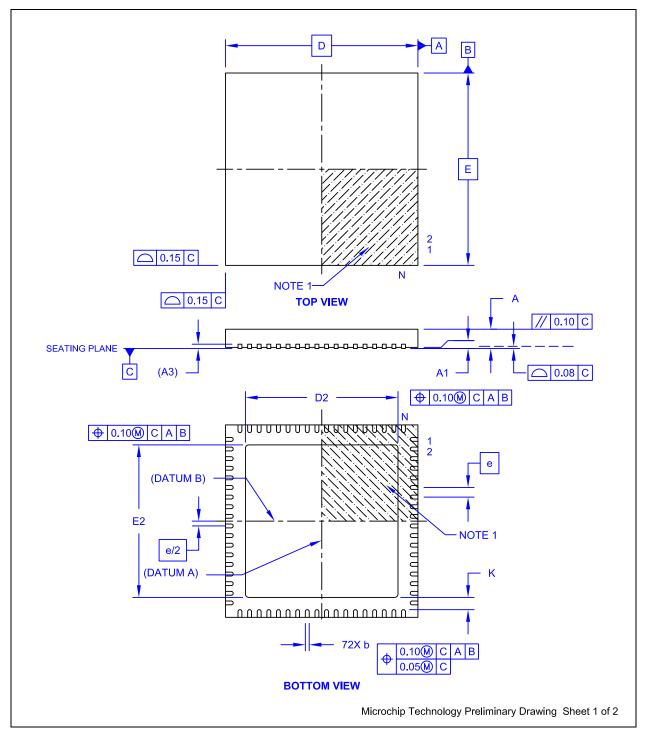

LAN7431: 72-pin SQFN (10 x 10 mm)

- Environmental

- Commercial temp. range (0°C to +70°C)

- Industrial temp. range (-40°C to +85°C)

- AEC-Q100 Grade 2 Automotive Qualified temp. range (-40°C to +105°C)

#### **Product Features**

- Gigabit Ethernet PHY (LAN7430)

- Auto-Negotiation and Auto-MDIX support

- On-chip termination resistors for differential pairs

- LinkMD<sup>®</sup> TDR-Based cable diagnostic to identify faulty copper cabling

- Signal Quality Indicator Quiet-WIRE<sup>®</sup> technology to reduce line emissions and enhance immunity for 100BASE-TX Programmable LED Outputs for Link, Activity,

- Speed

- Signal Quality Indicator (SQI) support IEEE 802.3az Energy Efficient Ethernet (EEE) -

- MAC with External Ethernet PHY (LAN7431)

- RGMII supporting Internal Delay, Non-Internal Delay and Hybrid modes

- MII supporting Fast Ethernet PHY

- Flexibility to operate at 1.8V, 2.5V, or 3.3V 9220 Byte Maximum Frame Size

- · Gigabit Ethernet MAC includes

- 10/100/1000Mbps half/full-duplex operation (only full-duplex operation at 1000Mbps)

- Flow control with pause frame for full-duplex mode

- 100/1000Mbps Low Power Idle for EEE

- MDC/MDIO management for external PHY

- RX frame, link status, EEE wakeup for WoL

- DMA Controller

- Scatter-gather based for efficient data transfer to/from multiple on-chip RAM locations

- Multi-channel for RX prioritization

- FIFO Controller

- Utilize internal SRAMs to buffer RX and TX traffic between PCIe and Ethernet

- TX LSO and TX Checksum Offload

- Receive Ethernet Packet Filtering

- IP, TCP/UDP, L3, ICMP/IGMP Checksum offload

- IEEE 802.1Q VLAN

- Unicast, Multicast, Broadcast

- Perfect / Hash Address

- Priority based channel selection

- Receive Side Scaling (RSS)

- PME Support

- PCIe WAKE# and Beaconing

- PCIe PME Messaging GPIO, Link Change, Ethernet Frame for wakeup

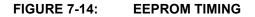

- EEPROM / OTP

- External EEPROM support for MAC address and PCIe configuration

- Integrated OTP memory for EEPROM displacement

- · 1149.1 (JTAG) boundary scan

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS300000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| .0 Preface                             | 4  |

|----------------------------------------|----|

| .0 Introduction                        | 8  |

| .0 Pin Descriptions and Configuration  | 12 |

| .0 Power Connectivity                  | 26 |

| .0 Device Configuration                | 30 |

| .0 Functional Descriptions             | 31 |

| 0 Operational Characteristics          | 48 |

| .0 Package Information                 | 69 |

| ppendix A: Data Sheet Revision History | 73 |

| Product Identification System          | 74 |

| he Microchip Web Site                  | 75 |

| Sustomer Change Notification Service   | 75 |

| Customer Support                       | 75 |

# 1.0 PREFACE

# 1.1 General Terms

## TABLE 1-1: GENERAL TERMS

| Term                       | Description                                                                                                                                                                                                       |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1000BASE-T                 | 1 Gbps Ethernet over twisted pair, IEEE 802.3 compliant                                                                                                                                                           |  |  |  |  |

| 100BASE-TX                 | 100 Mbps Ethernet over twisted pair, IEEE 802.3 compliant                                                                                                                                                         |  |  |  |  |

| 10BASE-T                   | 10 Mbps Ethernet over twisted pair, IEEE 802.3 compliant                                                                                                                                                          |  |  |  |  |

| ADC                        | Analog-to-Digital Converter                                                                                                                                                                                       |  |  |  |  |

| AFE                        | Analog Front End                                                                                                                                                                                                  |  |  |  |  |

| AN, ANEG                   | Auto-Negotiation                                                                                                                                                                                                  |  |  |  |  |

| AOAC                       | Always on Always Connected                                                                                                                                                                                        |  |  |  |  |

| ARP                        | Address Resolution Protocol                                                                                                                                                                                       |  |  |  |  |

| BELT                       | Best Effort Latency Tolerance                                                                                                                                                                                     |  |  |  |  |

| BYTE                       | 8-bits                                                                                                                                                                                                            |  |  |  |  |

| CSMA/CD                    | Carrier Sense Multiple Access/Collision Detect                                                                                                                                                                    |  |  |  |  |

| CSR                        | Control and Status Register                                                                                                                                                                                       |  |  |  |  |

| DA                         | Destination Address                                                                                                                                                                                               |  |  |  |  |

| DWORD                      | 32-bits                                                                                                                                                                                                           |  |  |  |  |

| EC                         | Embedded Controller                                                                                                                                                                                               |  |  |  |  |

| EEE                        | Energy Efficient Ethernet                                                                                                                                                                                         |  |  |  |  |

| FCS                        | Frame Check Sequence                                                                                                                                                                                              |  |  |  |  |

| FIFO                       | First In First Out buffer                                                                                                                                                                                         |  |  |  |  |

| FSM                        | Finite State Machine                                                                                                                                                                                              |  |  |  |  |

| FW                         | Firmware                                                                                                                                                                                                          |  |  |  |  |

| GMII                       | Gigabit Media Independent Interface                                                                                                                                                                               |  |  |  |  |

| GPIO                       | General Purpose I/O                                                                                                                                                                                               |  |  |  |  |

| HOST                       | External system (Includes processor, application software, etc.)                                                                                                                                                  |  |  |  |  |

| HW                         | Hardware. Refers to function implemented by digital logic.                                                                                                                                                        |  |  |  |  |

| IGMP                       | Internet Group Management Protocol                                                                                                                                                                                |  |  |  |  |

| LDO                        | Linear Drop-Out Regulator                                                                                                                                                                                         |  |  |  |  |

| Level-Triggered Sticky Bit | This type of status bit is set whenever the condition that it represents is asserted. The bit remains set until the condition is no longer true, and the status bit is cleared by writing a zero.                 |  |  |  |  |

| LFSR                       | Linear Feedback Shift Register                                                                                                                                                                                    |  |  |  |  |

| LPM                        | Link Power Management                                                                                                                                                                                             |  |  |  |  |

| lsb                        | Least Significant Bit                                                                                                                                                                                             |  |  |  |  |

| LSB                        | Least Significant Byte                                                                                                                                                                                            |  |  |  |  |

| LTM                        | Latency Tolerance Messaging                                                                                                                                                                                       |  |  |  |  |

| MAC                        | Media Access Controller                                                                                                                                                                                           |  |  |  |  |

| MDI                        | Medium Dependent Interface                                                                                                                                                                                        |  |  |  |  |

| MDIX                       | Media Independent Interface with Crossover                                                                                                                                                                        |  |  |  |  |

| MEF                        | Multiple Ethernet Frames                                                                                                                                                                                          |  |  |  |  |

| MII                        | Media Independent Interface                                                                                                                                                                                       |  |  |  |  |

| MLT-3                      | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0". |  |  |  |  |

| TABLE 1-1: GEN                                                                                   | ERAL TERMS (CONTINUED)                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Term                                                                                             | Description                                                                                                                                                                                                                                                                             |  |  |  |  |

| MSI / MSI-X                                                                                      | Message Signaled Interrupt                                                                                                                                                                                                                                                              |  |  |  |  |

| N/A                                                                                              | Not Applicable                                                                                                                                                                                                                                                                          |  |  |  |  |

| OTP                                                                                              | One Time Programmable                                                                                                                                                                                                                                                                   |  |  |  |  |

| PCS                                                                                              | Physical Coding Sublayer                                                                                                                                                                                                                                                                |  |  |  |  |

| PLL                                                                                              | Phase Locked Loop                                                                                                                                                                                                                                                                       |  |  |  |  |

| PMIC                                                                                             | Power Management IC                                                                                                                                                                                                                                                                     |  |  |  |  |

| POR                                                                                              | Power on Reset.                                                                                                                                                                                                                                                                         |  |  |  |  |

| PTP                                                                                              | Precision Time Protocol                                                                                                                                                                                                                                                                 |  |  |  |  |

| QWORD                                                                                            | 64-bits                                                                                                                                                                                                                                                                                 |  |  |  |  |

| RESERVED                                                                                         | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must<br>always be zero for write operations. Unless otherwise noted, values are not guaran-<br>teed when reading reserved bits. Unless otherwise noted, do not read or write to<br>reserved addresses. |  |  |  |  |

| RGMII                                                                                            | Reduced Gigabit Media Independent Interface                                                                                                                                                                                                                                             |  |  |  |  |

| RMII                                                                                             | Reduced Media Independent Interface                                                                                                                                                                                                                                                     |  |  |  |  |

| RMON                                                                                             | Remote Monitoring                                                                                                                                                                                                                                                                       |  |  |  |  |

| SA                                                                                               | Source Address                                                                                                                                                                                                                                                                          |  |  |  |  |

| SCSR                                                                                             | System Control and Status Registers                                                                                                                                                                                                                                                     |  |  |  |  |

| SEF                                                                                              | Single Ethernet Frame                                                                                                                                                                                                                                                                   |  |  |  |  |

| SFD Start of Frame Delimiter - The 8-bit value indicating the end of the pream<br>Ethernet frame |                                                                                                                                                                                                                                                                                         |  |  |  |  |

| SMNP                                                                                             | Simple Network Management Protocol                                                                                                                                                                                                                                                      |  |  |  |  |

| TMII                                                                                             | Turbo Media Independent Interface                                                                                                                                                                                                                                                       |  |  |  |  |

| UDP User Datagram Protocol - A connectionless protocol run on top of IP netwo                    |                                                                                                                                                                                                                                                                                         |  |  |  |  |

| WORD 16-bits                                                                                     |                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                                                                                  |                                                                                                                                                                                                                                                                                         |  |  |  |  |

#### TABLE 1-1: GENERAL TERMS (CONTINUED)

# 1.2 Buffer Types

#### TABLE 1-2: BUFFER TYPE DESCRIPTIONS

| Buffer  | Description                                                                                                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI      | Analog input                                                                                                                                                                                                                            |

| AO      | Analog output                                                                                                                                                                                                                           |

| AIO     | Analog bi-directional                                                                                                                                                                                                                   |

| ICLK    | Crystal oscillator input pin                                                                                                                                                                                                            |

| OCLK    | Crystal oscillator output pin                                                                                                                                                                                                           |

| RGMII_I | RGMII compliant input                                                                                                                                                                                                                   |

| RGMII_O | RGMII compliant output                                                                                                                                                                                                                  |

| IS      | Input with Schmitt trigger                                                                                                                                                                                                              |

| OD4     | Open-drain output with 4 mA sink                                                                                                                                                                                                        |

| VIS     | Variable voltage input with Schmitt trigger                                                                                                                                                                                             |

| VO8     | Variable voltage output with 8 mA sink and 8 mA source                                                                                                                                                                                  |

| VOD8    | Variable voltage open-drain output with 8 mA sink                                                                                                                                                                                       |

| VO12    | Variable voltage output with 12 mA sink and 12 mA source                                                                                                                                                                                |

| VOD12   | Variable voltage open-drain output with 12 mA sink                                                                                                                                                                                      |

| VOS12   | Variable voltage open-source output with 12 mA source                                                                                                                                                                                   |

| PU      | Internal pull-up with $47\mu A$ (typical @ 3.3V). Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                  |

|         | Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |

| PD      | Internal pull-down with $47\mu A$ (typical @ 3.3V). Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                              |

|         | Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |

| Р       | Power pin                                                                                                                                                                                                                               |

## 1.3 Register Bit Types

Table 1-3 describes the register but attributes used throughout this document.

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| W                          | Write: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                                                                            |  |  |  |

| W1S                        | Write One to Set: Writing a one sets the value. Writing a zero has no effect.                                                                                                                                                                                                                                                                                                  |  |  |  |

| W1C                        | Write One to Clear: Writing a one clears the value. Writing a zero has no effect.                                                                                                                                                                                                                                                                                              |  |  |  |

| WAC                        | Write Anything to Clear: Writing anything clears the value.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                                                                                                                      |  |  |  |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SC                         | <b>Self-Clearing:</b> Contents is self-cleared after being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                                                                           |  |  |  |

| RO/LH                      | <b>Read Only, Latch High:</b> This mode is used by the Ethernet PHY registers. Bits with this attribute will stay high until the bit is read. After it a read, the bit will remain high, but will change to low if the condition that caused the bit to go high is removed. If the bit has not been read the bit will remain high regardless of if its cause has been removed. |  |  |  |

| NALR                       | Not Affected by Lite Reset. The state of NALR bits does not change on assertion of a lite reset.                                                                                                                                                                                                                                                                               |  |  |  |

| NASR                       | <b>Not Affected by Software Reset.</b> The state of NASR bits does not change on assertion of a software reset.                                                                                                                                                                                                                                                                |  |  |  |

| STKY                       | This field is "Sticky" in that it is neither initialized nor modified by hot reset or Function Level Reset.                                                                                                                                                                                                                                                                    |  |  |  |

| RESERVED                   | <b>Reserved Field:</b> Reserved fields must be written with zeros, unless otherwise indi-<br>cated, to ensure future compatibility. The value of reserved bits is not guaranteed on a<br>read.                                                                                                                                                                                 |  |  |  |

#### TABLE 1-3: REGISTER BIT TYPES

## 1.4 Reference Documents

- 1. IEEE 802.3<sup>TM</sup>-2015 IEEE Standard for Ethernet, http://standards.ieee.org/about/get/802/802.3.html

- 2. IEEE 802.1D<sup>TM</sup>-2004 IEEE Standard for Local and Metropolitan Area Networks Media Access Control (MAC) Bridges, http://standards.ieee.org/about/get/802/802.1.html

- 3. IEEE 802.1Q<sup>TM</sup>-2014 IEEE Standard for Local and Metropolitan Area Networks Bridges and Bridged Networks, http://standards.ieee.org/about/get/802/802.1.html

- 4. *IEEE 1149.1-2013 IEEE Standard for Test Access Port and Boundary-Scan Architecture,* https://standards.ieee.org/findstds/standard/1149.1-2013.html

- 5. IEEE 1588-2008 IEEE Standard for Precision Clock Synchronization Protocol for Networked Measurement and Control Systems, https://standards.ieee.org/findstds/standard/1588-2008.html

- 6. Reduced Gigabit Media Independent Interface (RGMII) Specification Version 2.0, https://web.archive.org/web/20160303171328/http://www.hp.com/rnd/pdfs/RGMIIv2\_0\_final\_hp.pdf

- 7. PCI Express® Base Specification Revision 3.1a, https://pcisig.com/specifications

- 8. PCI Bus Power Management Interface Specification Revision 1.2, https://pcisig.com/specifications

# 2.0 INTRODUCTION

## 2.1 General Description

The LAN7430/LAN7431 is a highly integrated PCIe to Gigabit Ethernet Controller, with IEEE Std 1588<sup>TM</sup>-2008 and advanced power management features, that provides a high performance and cost effective PCIe/Ethernet bridging solution for automotive and industrial applications.

The PCIe 3.1 PHY supports 1 Lane at 2.5GT/s for chip-to-chip and card-to-card connectivity across a combination of printed circuit boards, connectors, backplane wirings, and cables.

The LAN7430 has an integrated 10/100/1000 Ethernet PHY port with IEEE 802.3az Energy Efficient Ethernet (EEE) and 10BASE-Te support, while the LAN7431 supports either a RGMII (v1.3 and v2.0) or a MII MAC port for direct connectivity to transceivers, such as 100BASE-T1 or HDBaseT.

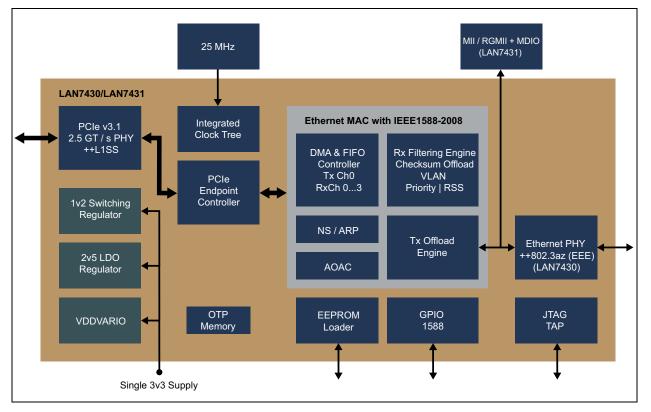

The LAN7430/LAN7431 further integrates PCIe Endpoint Controller, DMA Controller, Receive Filtering Engine, FIFO Controller, Ethernet MAC, EEPROM Controller, OTP Memory, TAP Controller, PME, and Clock/Reset/Power Management functions.

The IEEE1588-2008 PTP functions provide hardware support for the IEEE Std 1588-2008 (v2) Precision Time Protocol (PTP), allowing clock synchronization with remote Ethernet devices, packet time stamping, and time driven event generation. The device may function as a master or a slave clock per the IEEE Std 1588-2008 specification. End-to-end and peer-to-peer link delay mechanisms are supported as are one-step and two-step operations.

Power Management functions include:

- Enabling the host to place the device in a reduced power state, by selectively disabling internal clocks, placing it into EEE Low Power Idle mode, and powering down the Ethernet PHY (LAN7430 only).

- · Providing for detection of various wakeup events.

- Providing a host-readable READY flag which is set when the device is fully operational.

- · Controlling the loading of OTP or EEPROM values after a system reset.

- Supporting D0 and  $D3_{hot}$  and  $D3_{cold}$  states

- · Supporting L0s, L1 states and L1.1 and L1.2 Sub-states

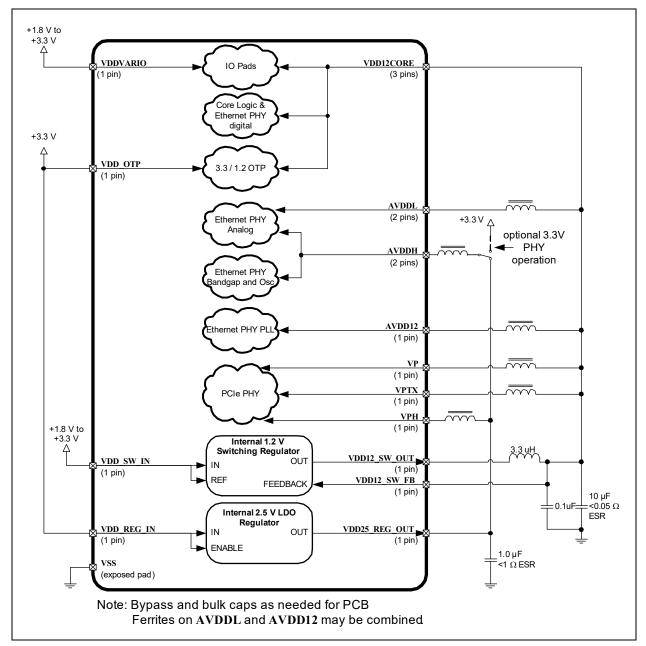

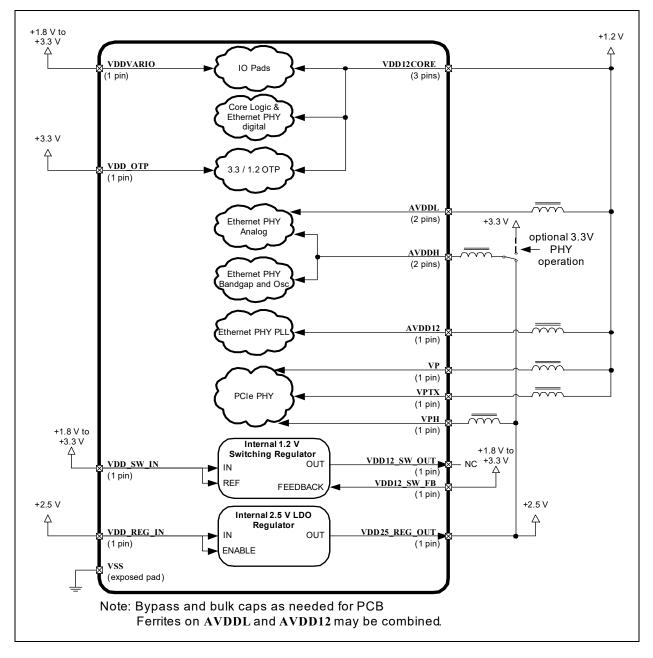

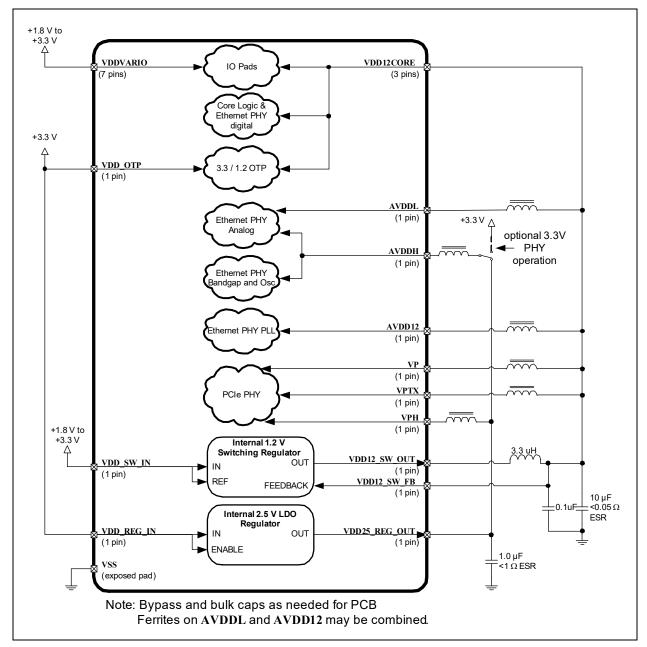

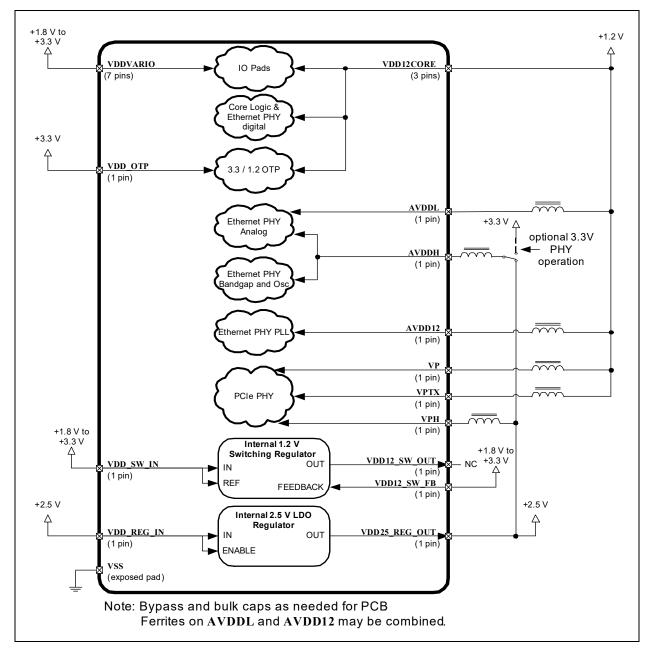

Single 3.3V supply operation is achieved by enabling the on-chip Switching and LDO Regulators to supply the core and I/O voltages.

An internal EEPROM controller exists to load PCIe and MAC Address configuration parameters. For EEPROM-less applications, the LAN7430/LAN7431 provides 1K Bytes of OTP memory that can be used to preload this same configuration data before enumeration.

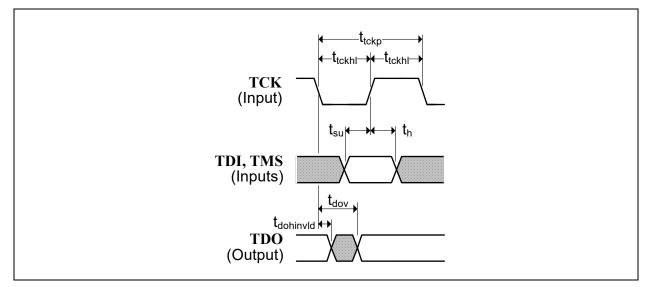

The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

Device specific features that do not pertain to the entire LAN7430/LAN7431 family are called out independently throughout this document. Table 2-1 provides a summary of the feature differences between family members:

| Part<br>Number | Package | Integrated PCIe PHY | Integrated PCIe<br>Endpoint Controller | Integrated Gigabit<br>Ethernet PHY | Integrated Gigabit<br>Ethernet MAC | MII Support | RGMII Support | IEEE 1588-2008 | Commercial Temp.<br>(0° to 70°C) | Industrial Temp.<br>(-40° to 85°C) | Automotive Temp.<br>(-40° to 105°C) |

|----------------|---------|---------------------|----------------------------------------|------------------------------------|------------------------------------|-------------|---------------|----------------|----------------------------------|------------------------------------|-------------------------------------|

| LAN7430        | 48-SQFN | Х                   | Х                                      | Х                                  | Х                                  |             |               | Х              | Х                                | Х                                  | Х                                   |

| LAN7431        | 72-SQFN | X                   | X                                      |                                    | X                                  | Х           | X             | X              | X                                | X                                  | Х                                   |

TABLE 2-1: LAN7430/LAN7431 FAMILY FEATURE MATRIX

An internal block diagram of the LAN7430/LAN7431 is shown in Figure 2-1.

## FIGURE 2-1: LAN7430/LAN7431 BLOCK DIAGRAM

The following system-level block diagrams detail the LAN7430/LAN7431 in typical applications.

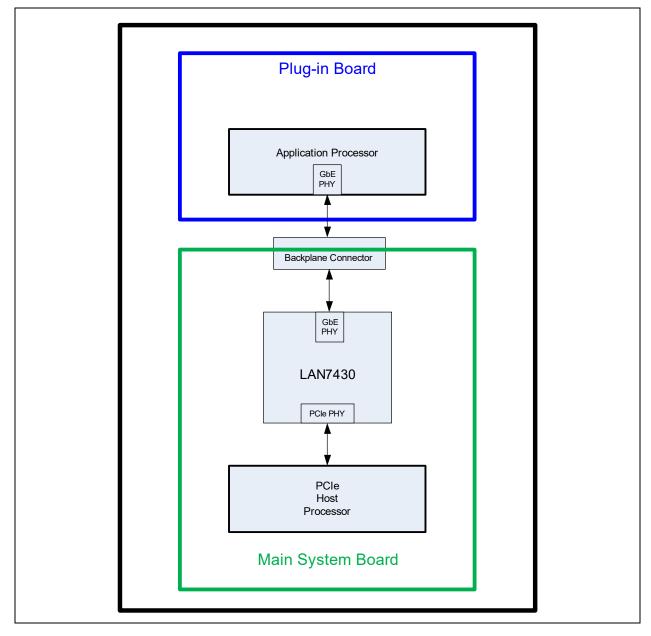

Figure 2-2 details the LAN7430's integrated Ethernet PHY port connected across a backplane to an application processor.

## FIGURE 2-2: LAN7430 CONNECTED ACROSS BACKPLANE TO APPLICATION PROCESSOR

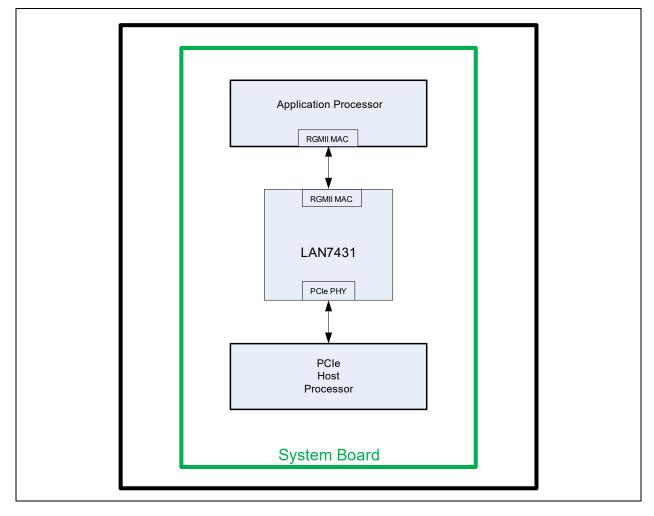

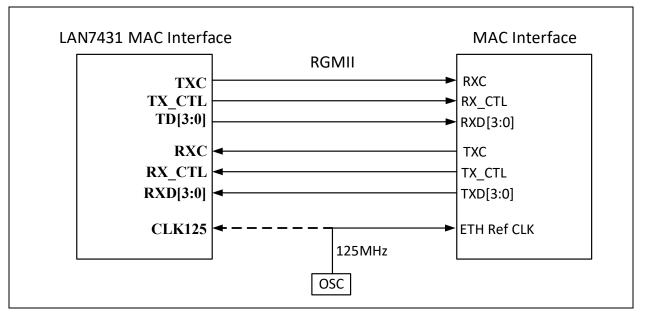

Figure 2-3 details the LAN7431's RGMII MAC port connected to the RGMII MAC of an application processor.

#### FIGURE 2-3: LAN7431 CONNECTED VIA RGMII TO APPLICATION PROCESSOR

# 3.0 PIN DESCRIPTIONS AND CONFIGURATION

The pin assignments for the LAN7430 are detailed in Section 3.1, "LAN7430 Pin Assignments". The pin assignments for the LAN7431 are detailed in Section 3.2, "LAN7431 Pin Assignments". Pin descriptions are provided in Section 3.3, "Pin Descriptions".

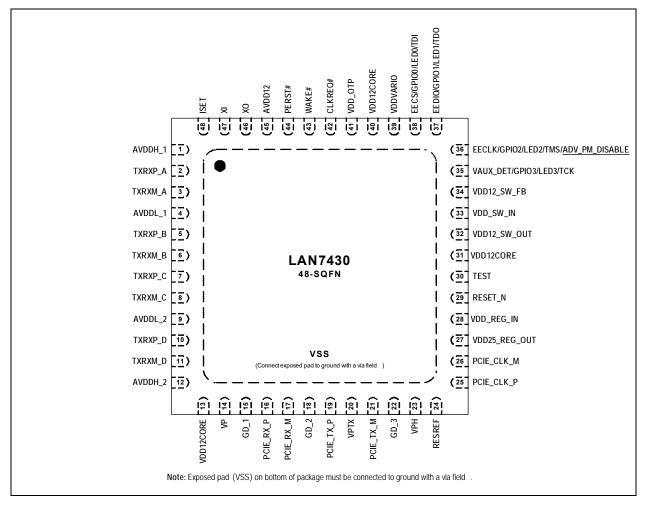

### 3.1 LAN7430 Pin Assignments

The device pin diagram for the LAN7430 can be seen in Figure 3-1. Table 3-1 provides a LAN7430 pin assignments table. Pin descriptions are provided in Section 3.3, "Pin Descriptions".

FIGURE 3-1: LAN7430 PIN ASSIGNMENTS

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load.

| Pin | Pin Name          | Pin                   | Pin Name                                |  |

|-----|-------------------|-----------------------|-----------------------------------------|--|

| 1   | AVDDH_1           | 25                    | PCIE_CLK_P                              |  |

| 2   | TXRXP_A           | TXRXP_A 26 PCIE_CLK_M |                                         |  |

| 3   | TXRXM_A           |                       |                                         |  |

| 4   | AVDDL_1           | 28                    | VDD_REG_IN                              |  |

| 5   | TXRXP_B           | 29                    | RESET_N                                 |  |

| 6   | TXRXM_B           | 30                    | TEST                                    |  |

| 7   | TXRXP_C           | 31                    | VDD12CORE                               |  |

| 8   | TXRXM_C           | 32                    | VDD12_SW_OUT                            |  |

| 9   | AVDDL_2           | 33                    | VDD_SW_IN                               |  |

| 10  | TXRXP_D           | 34                    | VDD12_SW_FB                             |  |

| 11  | TXRXM_D           | 35                    | VAUX_DET/GPIO3/LED3/TCK                 |  |

| 12  | AVDDH_2           | 36                    | EECLK/GPIO2/LED2/TMS/<br>ADV_PM_DISABLE |  |

| 13  | VDD12CORE         | 37                    | EEDIO/GPIO1/LED1/TDO                    |  |

| 14  | VP                | 38                    | EECS/GPIO0/LED0/TDI                     |  |

| 15  | GD_1              | 39                    | VDDVARIO                                |  |

| 16  | PCIE_RX_P         | 40                    | VDD12CORE                               |  |

| 17  | PCIE_RX_M         | 41                    | VDD_OTP                                 |  |

| 18  | GD_2              | 42                    | CLKREQ#                                 |  |

| 19  | PCIE_TX_P         | 43                    | WAKE#                                   |  |

| 20  | VPTX              | 44                    | PERST#                                  |  |

| 21  | PCIE_TX_M         | 45                    | AVDD12                                  |  |

| 22  | GD_3              | 46                    | ХО                                      |  |

| 23  | VPH               | 47                    | XI                                      |  |

| 24  | RESREF            | 48                    | ISET                                    |  |

|     | Exposed Pad (VSS) | must be connected     | to ground.                              |  |

TABLE 3-1: LAN7430 PIN ASSIGNMENTS

## 3.2 LAN7431 Pin Assignments

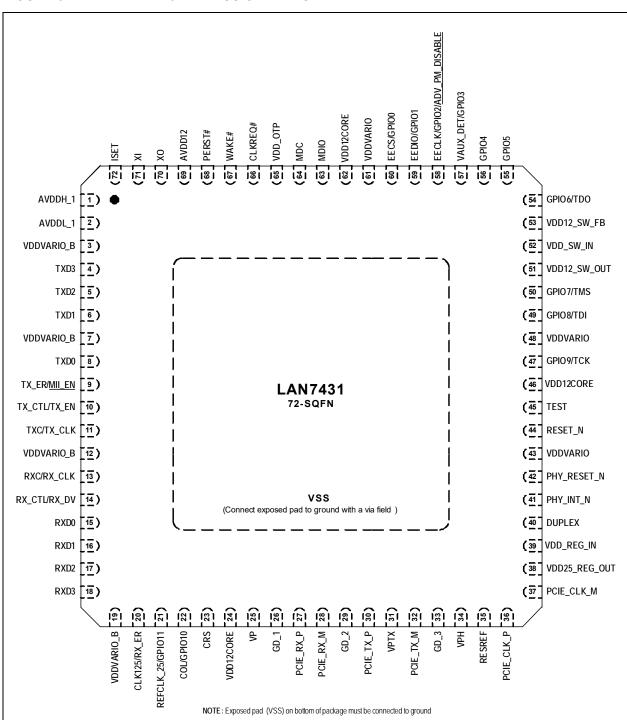

The device pin diagram for the LAN7431 can be seen in Figure 3-2. Table 3-2 provides a LAN7431 pin assignments table. Pin descriptions are provided in Section 3.3, "Pin Descriptions".

#### FIGURE 3-2: LAN7431 PIN ASSIGNMENTS

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load.

| Pin | Pin Name             | Pin | Pin Name                   |

|-----|----------------------|-----|----------------------------|

| 1   | AVDDH_1              | 37  | PCIE_CLK_M                 |

| 2   | AVDDL_1              | 38  | VDD25_REG_OUT              |

| 3   | VDDVARIO_B           | 39  | VDD_REG_IN                 |

| 4   | TXD3                 | 40  | DUPLEX                     |

| 5   | TXD2                 | 41  | PHY_INT_N                  |

| 6   | TXD1                 | 42  | PHY_RESET_N                |

| 7   | VDDVARIO_B           | 43  | VDDVARIO                   |

| 8   | TXD0                 | 44  | RESET_N                    |

| 9   | TX_ER/ <u>MII_EN</u> | 45  | TEST                       |

| 10  | TX_CTL/TX_EN         | 46  | VDD12CORE                  |

| 11  | TXC/TX_CLK           | 47  | GPIO9/TCK                  |

| 12  | VDDVADIO_B           | 48  | VDDVARIO                   |

| 13  | RXC/RX_CLK           | 49  | GPIO8/TDI                  |

| 14  | RX_CTL/RX_DV         | 50  | GPIO7/TMS                  |

| 15  | RXD0                 | 51  | VDD12_SW_OUT               |

| 16  | RXD1                 | 52  | VDD_SW_IN                  |

| 17  | RXD2                 | 53  | VDD12_SW_FB                |

| 18  | RXD3                 | 54  | GPIO6/TDO                  |

| 19  | VDDVARIO_B           | 55  | GPIO5                      |

| 20  | CLK125/RX_ER         | 56  | GPIO4                      |

| 21  | REFCLK_25/GPIO11     | 57  | VAUX_DET/GPIO3             |

| 22  | COL/GPIO10           | 58  | EECLK/GPIO2/ADV_PM_DISABLE |

| 23  | CRS                  | 59  | EEDIO/GPIO1                |

| 24  | VDD12CORE            | 60  | EECS/GPIO0                 |

| 25  | VP                   | 61  | VDDVARIO                   |

| 26  | GD_1                 | 62  | VDD12CORE                  |

| 27  | PCIE_RX_P            | 63  | MDIO                       |

| 28  | PCIE_RX_M            | 64  | MDC                        |

| 29  | GD_2                 | 65  | VDD_OTP                    |

| 30  | PCIE_TX_P            | 66  | CLKREQ#                    |

| 31  | VPTX                 | 67  | WAKE#                      |

| 32  | PCIE_TX_M            | 68  | PERST#                     |

| 33  |                      | 69  | AVDD12                     |

| 34  | VPH                  | 70  | ХО                         |

| 35  | RESREF               | 71  | XI                         |

| 36  | PCIE_CLK_P           | 72  | ISET                       |

TABLE 3-2: LAN7431 PIN ASSIGNMENTS

## 3.3 Pin Descriptions

This section provides descriptions of each individual pin function. Buffer type definitions are detailed in Table 1-2.

| Name                                    | Symbol  | Buffer | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | -       | Type   | nterface (LAN7430 only)                                                                                                                                                                                                                                                                                                                                                                        |

| Ethernet TX/RX<br>Positive<br>Channel A | TXRXP_A | AIO    | <ul> <li>Media Dependent Interface[0], positive signal of differential pair</li> <li>1000BT mode: TXRXP_A corresponds to BI_DA+ for MDI configuration and BI_DB+ for MDI-X configuration, respectively.</li> <li>10BT/100BT mode: TXRXP_A is the positive transmit signal (TX+) for MDI configuration and the positive receive signal (RX+) for MDI-X configuration, respectively.</li> </ul>  |

| Ethernet TX/RX<br>Negative<br>Channel A | TXRXM_A | AIO    | tively.<br>Media Dependent Interface[0], negative signal of differen-<br>tial pair<br>1000BT mode: TXRXM_A corresponds to BI_DA- for<br>MDI configuration and BI_DB- for MDI-X configuration,<br>respectively.<br>10BT/100BT-TX mode: TXRXM_A is the negative trans-<br>mit signal (TX-) for MDI configuration and the negative<br>receive signal (RX-) for MDI-X configuration, respectively. |

| Ethernet TX/RX<br>Positive<br>Channel B | TXRXP_B | AIO    | Media Dependent Interface[1], positive signal of differen-<br>tial pair<br>1000BT mode: TXRXP_B corresponds to BI_DB+ for<br>MDI configuration and BI_DA+ for MDI-X configuration,<br>respectively.<br>10BT/100BT mode: TXRXP_B is the positive receive sig-<br>nal (RX+) for MDI configuration and the positive transmit<br>signal (TX+) for MDI-X configuration, respectively.               |

| Ethernet TX/RX<br>Negative<br>Channel B | TXRXM_B | AIO    | Media Dependent Interface[1], negative signal of differen-<br>tial pair<br>1000BT mode: TXRXM_B corresponds to BI_DB- for<br>MDI configuration and BI_DA- for MDI-X configuration,<br>respectively.<br>10BT/100BT mode: TXRXP_B is the negative receive<br>signal (RX-) for MDI configuration and the negative trans-<br>mit signal (TX-) for MDI-X configuration, respectively.               |

| Ethernet TX/RX<br>Positive<br>Channel C | TXRXP_C | AIO    | Media Dependent Interface[2], positive signal of differen-<br>tial pair<br>1000BT mode: TXRXP_C corresponds to BI_DC+ for<br>MDI configuration and BI_DD+ for MDI-X configuration,<br>respectively.<br>10BT/100BT mode: TXRXP_C is not used.                                                                                                                                                   |

#### TABLE 3-3: PIN DESCRIPTIONS

| TABLE 3-3:         PIN DESCRIPTIONS (CONTINUED) |                              |                |                                                                                                                                                                                                                                              |  |

|-------------------------------------------------|------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                            | Symbol                       | Buffer<br>Type | Description                                                                                                                                                                                                                                  |  |

| Ethernet TX/RX<br>Negative<br>Channel C         | TXRXM_C                      | AIO            | Media Dependent Interface[2], negative signal of differen-<br>tial pair<br>1000BT mode: TXRXM_C corresponds to BI_DC- for<br>MDI configuration and BI_DD- for MDI-X configuration,<br>respectively.                                          |  |

|                                                 |                              |                | 10BT/100BT mode: TXRXM_C is not used.                                                                                                                                                                                                        |  |

| Ethernet TX/RX<br>Positive<br>Channel D         | TXRXP_D                      | AIO            | Media Dependent Interface[3], positive signal of differen-<br>tial pair<br>1000BT mode: TXRXP_D corresponds to BI_DD+ for<br>MDI configuration and BI_DC+ for MDI-X configuration,<br>respectively.<br>10BT/100BT mode: TXRXP_D is not used. |  |

| Ethernet TX/RX<br>Negative<br>Channel D         | TXRXM_D                      | AIO            | Media Dependent Interface[3], negative signal of differen-<br>tial pair<br>1000BT mode: TXRXM_D corresponds to BI_DD- for<br>MDI configuration and BI_DC- for MDI-X configuration,<br>respectively.                                          |  |

|                                                 |                              |                | 10BT/100BT mode: TXRXM_D is not used.                                                                                                                                                                                                        |  |

|                                                 | Ŭ                            |                | PHY RGMII (LAN7431 only)                                                                                                                                                                                                                     |  |

| Transmit Data                                   | TXD3<br>TXD2<br>TXD1<br>TXD0 | RGMII_O        | The MAC transmits data to the external Ethernet PHY using these signals.                                                                                                                                                                     |  |

| Transmit Control                                | TX_CTL                       | RGMII_O        | Indicates both the transmit data enable (TXEN) and transmit error (TXER) functions per the RGMII specification.                                                                                                                              |  |

| RGMII Transmit<br>Clock                         | TXC                          | RGMII_O        | Used to latch data from the MAC into the external Ether-<br>net PHY in RGMII mode.<br>1000BASE-T: 125MHz<br>100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz                                                                                            |  |

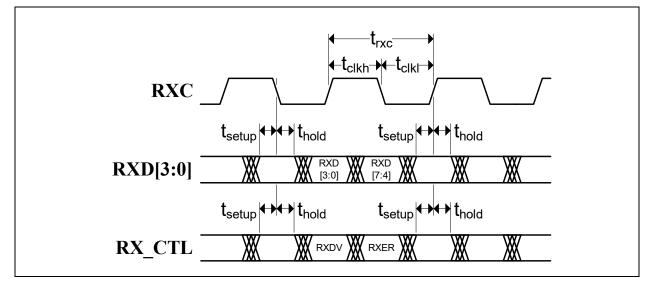

| Receive Data                                    | RXD3<br>RXD2<br>RXD1<br>RXD0 | RGMII_I        | The external Ethernet PHY transfers data to the MAC using these signals.                                                                                                                                                                     |  |

| Receive Control                                 | RX_CTL                       | RGMII_I        | Indicates both the receive data valid (RXDV) and receive error (RXER) functions per the RGMII specification.                                                                                                                                 |  |

| RGMII Receive<br>Clock                          | RXC                          | RGMII_I        | Used to transfer data from the external Ethernet PHY to<br>the MAC in RGMII mode.<br>1000BASE-T: 125MHz<br>100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz                                                                                             |  |

| 25 MHz Refer-<br>ence Clock                     | REFCLK_25                    | VO12           | 25 MHz reference clock to be provided to and used as a reference by the external Gigabit Ethernet PHY.                                                                                                                                       |  |

#### TABLE 3-3: PIN DESCRIPTIONS (CONTINUED)

| TABLE 3-3:                    | PIN DESCRIPTIONS (CO         |                |                                                                                                                                                                          |

|-------------------------------|------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                          | Symbol                       | Buffer<br>Type | Description                                                                                                                                                              |

| CLK125 MHz                    | CLK125                       | VIS            | Used as an input from external Ethernet PHY. This signal may be used by the controller to generate the RGMII TX clock.                                                   |

| PHY Interrupt                 | PHY_INT_N                    | VIS            | Interrupt from external Ethernet PHY.                                                                                                                                    |

| PHY Reset                     | PHY_RESET_N                  | VO12           | Reset to external Ethernet PHY.                                                                                                                                          |

| Duplex Mode                   | DUPLEX                       | VIS            | Duplex Mode. This signal connects to the Duplex Mode output from external Ethernet PHY.                                                                                  |

|                               |                              |                | When set the external Ethernet PHY is in Full Duplex mode.                                                                                                               |

|                               |                              |                | <b>Note:</b> If the Ethernet PHY does not have a duplex output signal, then it is recommended that this signal should be tied to VDDVARIO to force full duplex operation |

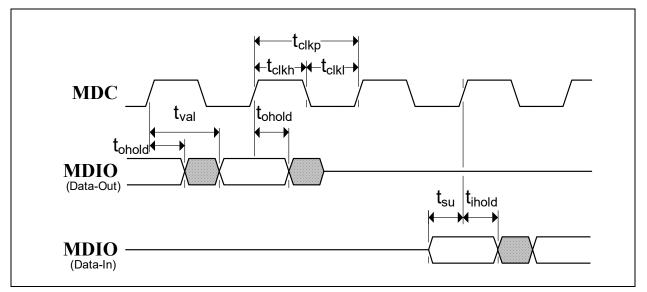

| Management<br>Interface Data  | MDIO                         | VIS/<br>VO8    | This is the management data to/from an external Ether-<br>net PHY.                                                                                                       |

|                               | (PU                          | (PU)           | <b>Note:</b> An external pull-up is required when the MII management interface is used, to ensure that the IDLE state of the MDIO signal is a logic one.                 |

|                               |                              |                | <b>Note:</b> An external pull-up is recommended when the MII management interface is not used, to avoid a floating signal.                                               |

| Management<br>Interface Clock | MDC                          | VO8            | This is the management clock output to an external<br>Ethernet PHY                                                                                                       |

|                               | External Fa                  | ast Ethernet I | PHY MII (LAN7431 only)                                                                                                                                                   |

| Transmit Data                 | TXD3<br>TXD2<br>TXD1<br>TXD0 | VO12           | The MAC transmits data to the external Ethernet PHY using these signals.                                                                                                 |

| Transmit Enable               |                              | VO12           | Indicates the presence of valid data on TXD[3:0]                                                                                                                         |

| Transmit Error                | TX ER                        | VO12           | Indicates a transmit error condition.                                                                                                                                    |

| Transmit Clock                | TX_CLK                       | VIS            | Used to transfer data from the MAC to the external Ether-<br>net PHY in MII mode.                                                                                        |

|                               |                              |                | 100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz                                                                                                                                    |

| Collision Detect              | COL                          | VIS            | Asserted by external Ethernet PHY to indicate detection of a collision condition.                                                                                        |

|                               |                              |                | Note: Used in half-duplex mode only.                                                                                                                                     |

| Carrier Sense                 | CRS                          | VIS            | Indicates detection of carrier by external Ethernet PHY.                                                                                                                 |

|                               |                              |                | Note: Used in half-duplex mode only.                                                                                                                                     |

| Receive Data                  | RXD3<br>RXD2<br>RXD1<br>RXD0 | VIS            | The external Ethernet PHY transfers data to the MAC using these signals.                                                                                                 |

| Receive Data<br>Valid         | RX_DV                        | VIS            | Indicates that recovered and decoded data is being pre-<br>sented on the receive data pins.                                                                              |

# TABLE 3-3: PIN DESCRIPTIONS (CONTINUED)

| TABLE 3-3:                    | PIN DESCRIPTIONS (C | ONTINUED            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------|---------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                          | Symbol              | Buffer<br>Type      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Receive Error                 | RX_ER               | VIS                 | Asserted to indicate an error has been detected in the frame presently being transferred from the external Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Receive Clock                 | RX_CLK              | VIS                 | Used to transfer data from the external Ethernet PHY to<br>the MAC in MII mode.<br>100BASE-TX: 25MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 25 MHz Refer-<br>ence Clock   | REFCLK_25           | VO12                | 10BASE-T: 2.5MHz<br>25 MHz reference clock to be provided to and used as a<br>reference by the external Fast Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PHY Interrupt                 | PHY_INT_N           | VIS                 | Interrupt from external Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PHY Reset                     | <br>PHY_RESET_N     | VO12                | Reset to external Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Duplex Mode                   | DUPLEX              | VIS                 | Duplex Mode. This signal connects to the Duplex Mode<br>output from external Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               |                     |                     | <ul> <li>When set the external Ethernet PHY is in Full Duplex mode.</li> <li>Note: If the external Ethernet PHY does not have a duplex output signal, then it is recommended that this signal should be tied to VDDVARIO to force full duplex operation</li> </ul>                                                                                                                                                                                                                                                                                                                              |

| Management<br>Interface Data  | MDIO                | VIS/<br>VO8<br>(PU) | <ul> <li>This is the management data to/from an external Ethernet PHY.</li> <li>Note: An external pull-up is required when the MII management interface is used, to ensure that the IDLE state of the MDIO signal is a logic one.</li> <li>Note: An external pull-up is recommended when the MII management interface is not used, to avoid a floating signal.</li> <li>APPLICATION NOTE: A pull-up (internal or external) will result in a return value of FFFFh when a non-existent or non-addressed PHY is read. If a value of 0000h is desired instead, a pull-down may be used.</li> </ul> |

| Management<br>Interface Clock | MDC                 | VO8                 | This is the management clock output to an external<br>Ethernet PHY<br>Cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TX Positive                   | PCIE TX P           | AO                  | PCIe Serial Data Output positive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                               |                     |                     | Serial differential output link in the PCIe interface running at 2.5 GT/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               |                     |                     | A series capacitor in the range of 100nF to 200nF is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TABLE 3-3: PIN DESCRIPTIONS (CONTINUED) |

|-----------------------------------------|

|-----------------------------------------|

| TABLE 3-3: PI          | ABLE 3-3: PIN DESCRIPTIONS (CONTINUED) |                |                                                                                                                                                         |  |

|------------------------|----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|