### 1 Msps/500 kSPS 16/14/12-Bit Differential Input SAR ADC

#### Features

- Sample Rate (Throughput):

- MCP33131D/21D/11D-10: 1 Msps

- MCP33131D/21D/11D-05: 500 kSPS

- 16/14/12-Bit Resolution with No Missing Codes

- No Latency Output

- Wide Operating Voltage Range:

- Analog Supply Voltage (AV<sub>DD</sub>): 1.8V

- Digital Input/Output Interface Voltage (DV<sub>IO</sub>): 1.7V - 5.5V

- External Reference (V<sub>REF</sub>): 2.5V 5.1V

- Differential Input Operation

- Input Full-Scale Range: -V<sub>REF</sub> to +V<sub>REF</sub>

- Ultra Low Current Consumption (typical):

- During Input Acquisition (Standby): ~ 0.8 μA

- During Conversion: MCP33131D/21D/11D-10: ~1.6 mA MCP33131D/21D/11D-05: ~1.4 mA

- SPI-Compatible Serial Communication:

- SCLK Clock Rate: up to 100 MHz

- ADC Self-Calibration for Offset, Gain, and Linearity Errors:

- During Power-Up (automatic)

- On-Demand via user's command during normal operation

- AEC-Q100 Qualified:

- Temperature Grade 1: -40°C to +125°C

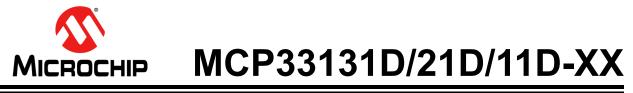

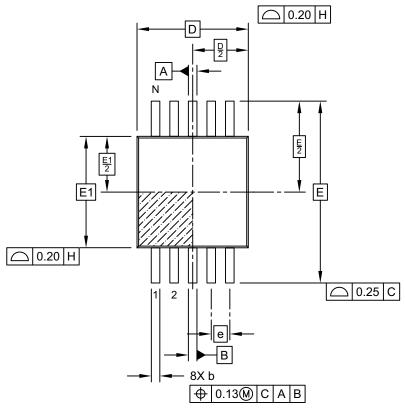

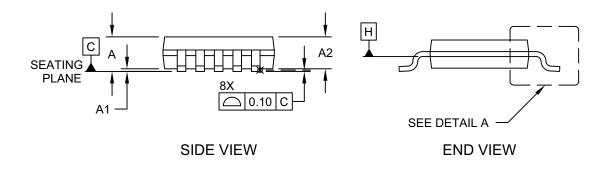

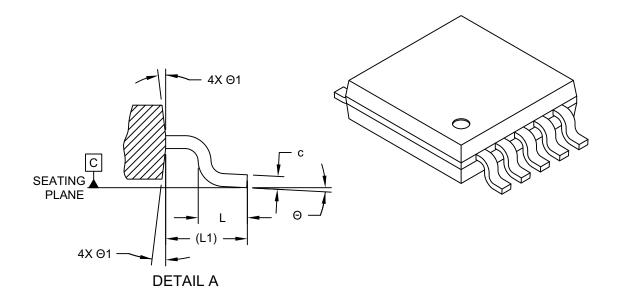

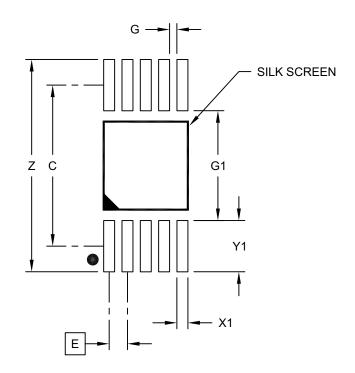

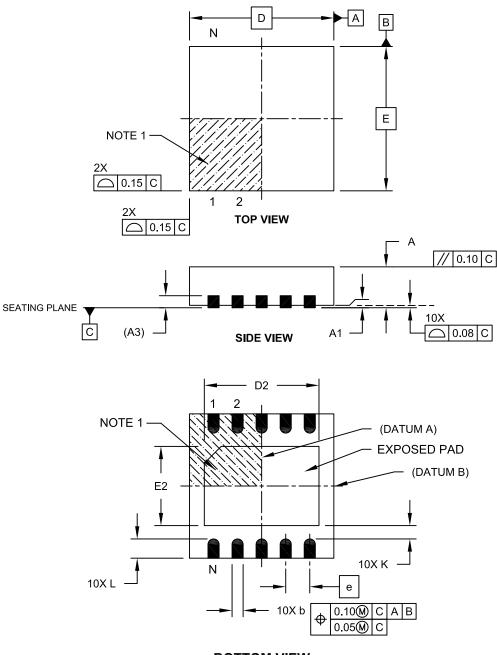

- Package Options: MSOP-10 and TDFN-10

### **Typical Applications**

- High-Precision Data Acquisition

- Medical Instruments

- Test Equipment

- Electric Vehicle Battery Management Systems

- Motor Control Applications

- Switch-Mode Power Supply Applications

- Battery-Powered Equipment

### System Design Supports

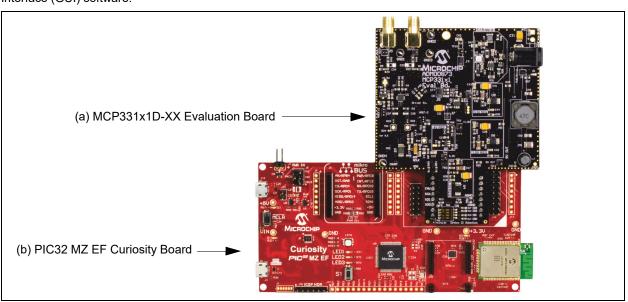

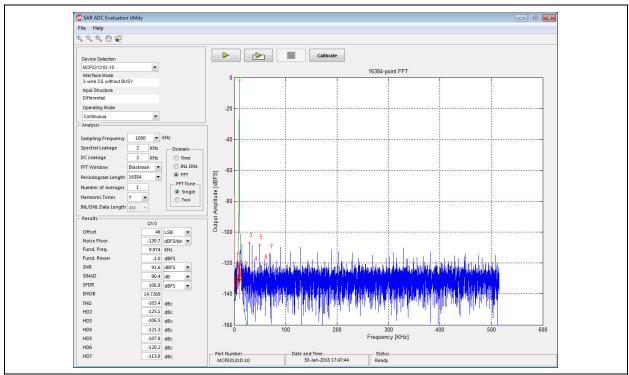

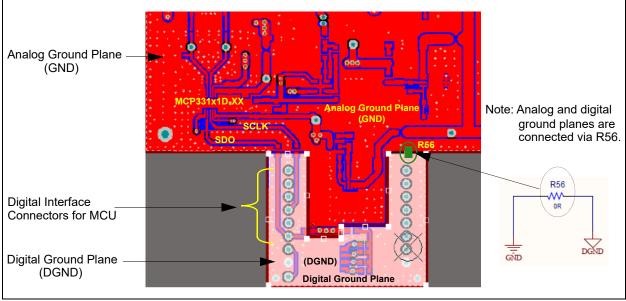

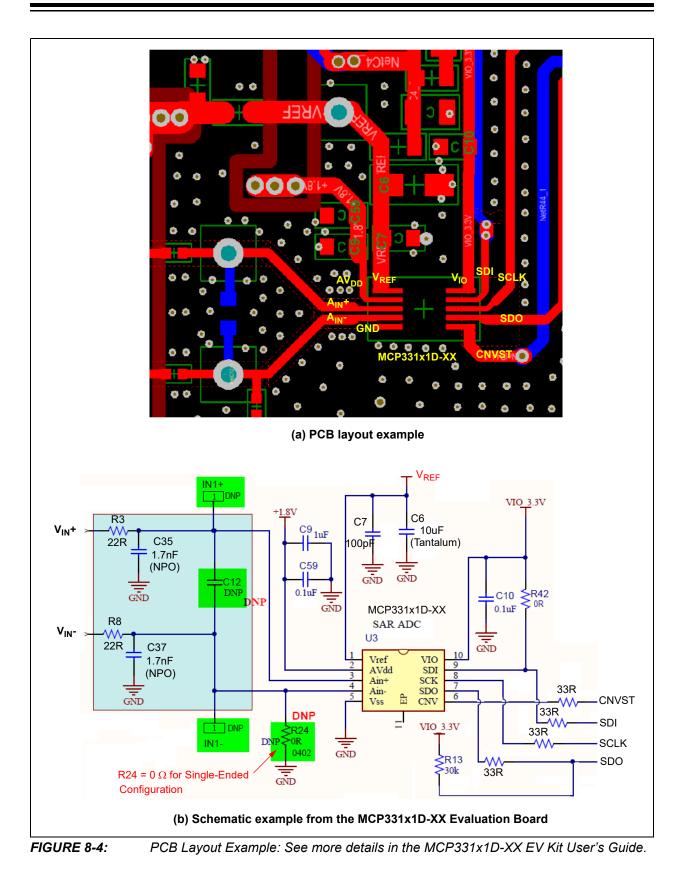

The MCP331x1D-XX Evaluation Kit demonstrates the performance of the MCP331x1D-XX SAR ADC family devices. The evaluation kit includes: (a) MCP331x1D Evaluation Board, (b) PIC32MZ EF Curiosity Board for data collection, and (c) SAR ADC Utility PC GUI.

Contact Microchip Technology Inc. for the evaluation tools and the PIC32 MCU firmware example codes.

#### **Package Types**

|              |            | 0              |              | Input Range<br>(Differential) | Performance (Typical) |              |             |              |              |  |

|--------------|------------|----------------|--------------|-------------------------------|-----------------------|--------------|-------------|--------------|--------------|--|

| Part Number  | Resolution | Sample<br>Rate | Input Type   |                               | SNR<br>(dBFS)         | SFDR<br>(dB) | THD<br>(dB) | INL<br>(LSB) | DNL<br>(LSB) |  |

| MCP33131D-10 | 16-bit     | 1 Msps         | Differential | ±5.1V                         | 91.3                  | 103.5        | -99.3       | ±2           | ±0.8         |  |

| MCP33121D-10 | 14-bit     | 1 Msps         | Differential | ±5.1V                         | 85.1                  | 103.5        | -99.2       | ±0.5         | ±0.25        |  |

| MCP33111D-10 | 12-bit     | 1 Msps         | Differential | ±5.1V                         | 73.9                  | 99.3         | -96.7       | ±0.12        | ±0.06        |  |

| MCP33131D-05 | 16-bit     | 500 kSPS       | Differential | ±5.1V                         | 91.3                  | 103.5        | -99.3       | ±2           | ±0.8         |  |

| MCP33121D-05 | 14-bit     | 500 kSPS       | Differential | ±5.1V                         | 85.1                  | 103.5        | -99.2       | ±0.5         | ±0.25        |  |

| MCP33111D-05 | 12-bit     | 500 kSPS       | Differential | ±5.1V                         | 73.9                  | 99.3         | -96.7       | ±0.12        | ±0.06        |  |

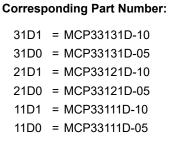

### MCP331x1D-XX Device Offering (Note 1):

Note 1: SNR, SFDR, and THD are measured with  $f_{IN}$  = 10 kHz,  $V_{IN}$  = -1 dBFS,  $V_{REF}$  = 5.1V.

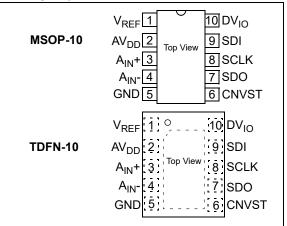

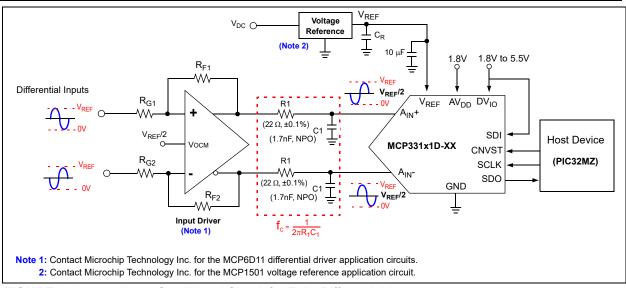

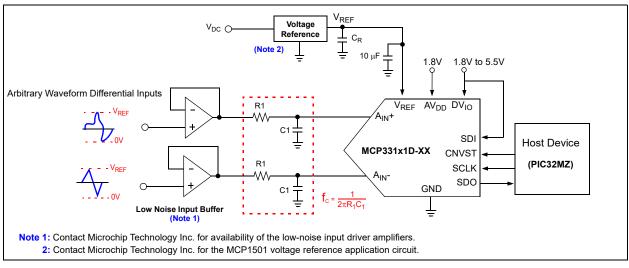

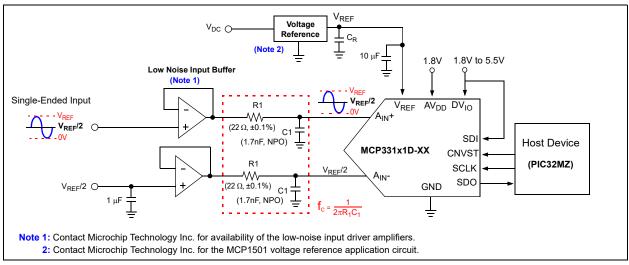

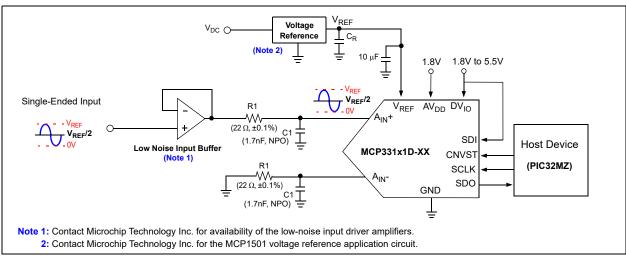

### **Application Diagram**

### Description

The MCP33131D/MCP33121D/MCP33111D-10 and MCP33131D/MCP33121D/MCP33111D-05 are fully-differential 16, 14, and 12-bit, single-channel 1 Msps and 500 kSPS ADC family devices, respectively, featuring low power consumption and high performance, using a successive approximation register (SAR) architecture.

The device operates with a 2.5V to 5.1V external reference (V<sub>REF</sub>), which supports a wide range of input full-scale range from -V<sub>REF</sub> to +V<sub>REF</sub>. The reference voltage setting is independent of the analog supply voltage (AV<sub>DD</sub>) and is higher than AV<sub>DD</sub>. The conversion output is available through an easy-to-use simple SPI- compatible 3-wire interface.

The device requires a 1.8V analog supply voltage  $(AV_{DD})$  and a 1.7V to 5.5V digital I/O interface supply voltage  $(DV_{IO})$ . The wide digital I/O interface supply  $(DV_{IO})$  range (1.7V - 5.5V) allows the device to interface with most host devices (Master) available in the current industry such as the PIC32 microcontrollers, without using external voltage level shifters.

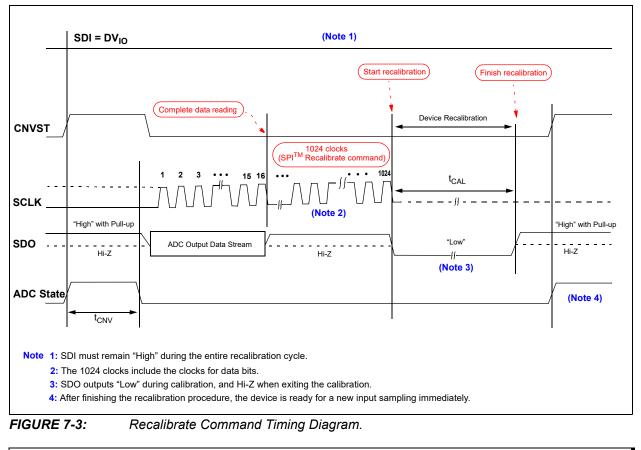

When the device is first powered-up, it performs a self-calibration to minimize offset, gain and linearity errors. The device performance stays stable across the specified temperature range. However, when extreme changes in the operating environment, such as in the reference voltage, are made with respect to the initial conditions (e.g. the reference voltage was not fully settled during the initial power-up sequence), the user may send a recalibrate command anytime to initiate another self-calibration to restore optimum performance.

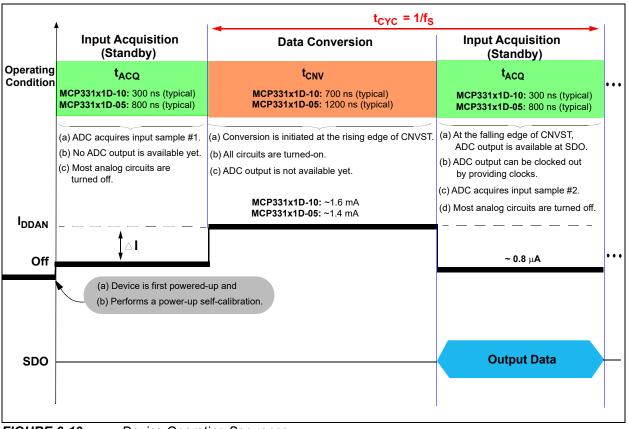

When the initial power-up sequence is completed, the device enters a low-current input acquisition mode, where sampling capacitors are connected to the input pins. This mode is called Standby.

During Standby, most of the internal analog circuitry is shutdown in order to reduce current consumption. Typically, the device consumes less than 1  $\mu$ A during Standby. A new conversion is started on the rising edge of CNVST. When the conversion is complete and the host lowers CNVST, the output data is presented on SDO, and the device enters Standby to begin acquiring the next input sample. The user can clock out the ADC output data using the SPI-compatible serial clock during Standby.

The ADC system clock is generated by the internal on-chip clock, therefore the conversion is performed independent of the SPI serial clock (SCLK).

This device can be used for various high-speed and high-accuracy analog-to-digital data conversion applications, where design simplicity, low power, and no output latency are needed.

The device is AEC-Q100 qualified for automotive applications and operates over the extended temperature range of -40°C to +125°C. The available package options are Pb-free small 3 mm x 3 mm TDFN-10 and MSOP-10.

### 1.0 KEY ELECTRICAL CHARACTERISTICS

#### 1.1 Absolute Maximum Ratings†

| External Analog Supply Voltage (AV_DD)0.3V to 2.0V                      |

|-------------------------------------------------------------------------|

| External Digital Supply Voltage (DV_{IO})                               |

| External Reference Voltage (V_{REF})0.3V to $5.8V$                      |

| Analog Inputs w.r.t GND0.3V to $V_{\mbox{\scriptsize REF}}\mbox{+}0.3V$ |

| Current at Input Pins±2 mA                                              |

| Current at Output and Supply Pins±250 mA                                |

| Storage Temperature65°C to +150°C                                       |

| Maximum Junction Temperature (T <sub>J</sub> )+150°C                    |

| ESD protection on all pins ≤2kV HBM, ≤200V MM, ≤2kV CDM                 |

**†Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 1.2 Electrical Specifications

### TABLE 1-1: KEY ELECTRICAL CHARACTERISTICS

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ ,

- $\label{eq:GND} \begin{array}{l} {\sf GND} = 0{\sf V}, \mbox{ Differential Analog Input (V_{IN})} = -1 \mbox{ dBFS sine wave, } f_{IN} = 10 \mbox{ kHz}, \mbox{ C}_{LOAD\_SDO} = 20 \mbox{ pF} \end{array}$

- MCP331x1D-05: Sample Rate  $(f_S) = 10$  MSPS, SPI Clock Input (SCLK) = 00 MHz. • MCP331x1D-05: Sample Rate  $(f_S) = 500$  kSPS, SPI Clock Input (SCLK) = 30 MHz.

| Parameters                                                                                      | Sym.                                              | Min.         | Тур.                     | Max.       | Units                | Conditions                                                                                                                 |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------|--------------------------|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Power Supply Requirements                                                                       |                                                   |              |                          |            | ·                    | ·                                                                                                                          |  |

| Analog Supply Voltage Range                                                                     | AV <sub>DD</sub>                                  | 1.7          | 1.8                      | 1.9        | V                    | (Note 3)                                                                                                                   |  |

| Digital Input/Output Interface Voltage<br>Range                                                 | DV <sub>IO</sub>                                  | 1.7          | —                        | 5.5        | V                    | (Note 3)                                                                                                                   |  |

| Analog Supply Current at AV <sub>DD</sub> pin:<br>During Conversion<br>During Standby           | I <sub>DDAN</sub>                                 | _            | 1.6<br>1.4<br>0.8        | 2.4<br>2.0 | mA<br>mA<br>μA       | $f_s = 1 \text{ Msps} (MCP331x1D-10)$<br>$f_s = 500 \text{ kSPS} (MCP331x1D-05)$<br>During input acquisition ( $t_{ACO}$ ) |  |

| • •                                                                                             | IDDAN_STBY                                        |              | 0.0                      |            | μΑ                   | During input acquisition (t <sub>ACQ</sub> )                                                                               |  |

| Digital Supply Current At DV <sub>DD</sub> pin:<br>During Output Data Reading<br>During Standby | I <sub>IO_DATA</sub>                              |              | 290<br>200<br>30         |            | μA<br>μA<br>nA       | $f_s = 1$ Msps (MCP331x1D-10)<br>$f_s = 500$ kSPS (MCP331x1D-05)<br>During input acquisition ( $t_{ACQ}$ )                 |  |

| External Reference Voltage Inp                                                                  | _                                                 |              |                          |            |                      |                                                                                                                            |  |

| Reference Voltage<br>(Note 2), (Note 3)                                                         | V <sub>REF</sub>                                  | 2.5<br>2.7   |                          | 5.1<br>5.1 | V                    | -40°C ≤ T <sub>A</sub> ≤ 85°C<br>85°C < T <sub>A</sub> ≤ 125°C                                                             |  |

| Reference Load Current at V <sub>REF</sub> pin:<br>During Conversion<br>During Standby          | I <sub>REF</sub>                                  |              | 450<br>220<br>240        | 600<br>360 | μA<br>μA<br>nA       | $f_s = 1 \text{ Msps} (MCP331x1D-10)$<br>$f_s = 500 \text{ kSPS} (MCP331x1D-05)$<br>During input cognisition (t            |  |

| • •                                                                                             |                                                   |              | -                        | _          | IIA                  | During input acquisition (t <sub>ACQ</sub> )                                                                               |  |

| Total Power Consumption (Incl                                                                   | uaing Av <sub>DD</sub> , Dv                       | 10, VREF pin | 5)                       |            |                      |                                                                                                                            |  |

| MCP331x1D-10                                                                                    |                                                   |              |                          |            | _                    |                                                                                                                            |  |

| at 1 Msps<br>at 500 kSPS<br>at 100 kSPS<br>During Standby                                       | P <sub>DISS_TOTAL</sub>                           | <br>         | 6.2<br>3.1<br>0.6<br>2.6 |            | mW<br>mW<br>mW<br>μW | Averaged power for $t_{ACQ} + t_{CNV}$<br>During input acquisition ( $t_{ACQ}$ )                                           |  |

| <b>č</b> ,                                                                                      | P <sub>DISS_STBY</sub>                            |              | 2.0                      |            | μvv                  | During input acquisition (t <sub>ACQ</sub> )                                                                               |  |

| MCP331x1D-05                                                                                    |                                                   |              |                          |            |                      |                                                                                                                            |  |

| at 500 kSPS<br>at 100 kSPS<br>During Standby                                                    | P <sub>DISS_TOTAL</sub><br>P <sub>DISS_STBY</sub> |              | 4.2<br>0.8<br>2.6        |            | mW<br>mW<br>μW       | Averaged power for $t_{ACQ} + t_{CNV}$<br>During input acquisition ( $t_{ACQ}$ )                                           |  |

**Note** 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

3: Decoupling capacitor is recommended on the following pins:

(a) AV<sub>DD</sub> pin: 1 µF ceramic capacitor, (b) DV<sub>IO</sub> pin: 0.1 µF ceramic capacitor, (c) V<sub>REF</sub> pin: 10 µF tantalum capacitor.

4: Differential Input Full-Scale Range (FSR) = 2 x V<sub>REF</sub>

5: PSRR (dB) = -20 log ( $D_{VOUT}/AV_{DD}$ ), where  $D_{VOUT}$  = change in conversion result.

#### TABLE 1-1: KEY ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input ( $V_{IN}$ ) = -1 dBFS sine wave,  $f_{IN} = 10$  kHz,  $C_{LOAD SDO} = 20$  pF

MCP331x1D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.

MCP331x1D-10: Sample Rate (f<sub>S</sub>) = 500 kCP3 SPI Clock Input (SCLK) = 60 MHz.

| MCP331x1D-05: Sample Rate (f <sub>S</sub> ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz. |                    |                   |                     |                       |                    |                                                                |  |  |  |

|------------------------------------------------------------------------------------------|--------------------|-------------------|---------------------|-----------------------|--------------------|----------------------------------------------------------------|--|--|--|

| Parameters                                                                               | Sym.               | Min.              | Тур.                | Max.                  | Units              | Conditions                                                     |  |  |  |

| Analog Inputs                                                                            |                    |                   |                     |                       |                    |                                                                |  |  |  |

| Input Voltage Range                                                                      | V <sub>IN+</sub>   | -0.1              | -                   | V <sub>REF</sub> +0.1 | V                  | Differential Input:                                            |  |  |  |

| (Note 2)                                                                                 | V <sub>IN-</sub>   | -0.1              | _                   | V <sub>REF</sub> +0.1 | V                  | $V_{\rm IN} = (V_{\rm IN+} - V_{\rm IN-})$                     |  |  |  |

| Input Full-Scale Voltage Range                                                           | FSR                | -V <sub>REF</sub> | —                   | +V <sub>REF</sub>     | V <sub>PP</sub>    | Differential Input (Note 2), (Note 4)                          |  |  |  |

| Input Common-Mode Voltage Range                                                          | V <sub>CM</sub>    | 0                 | V <sub>REF</sub> /2 | V <sub>REF</sub>      |                    | (Note 2)                                                       |  |  |  |

| Input Sampling Capacitance                                                               | Cs                 | —                 | 31                  | —                     | pF                 | (Note 1)                                                       |  |  |  |

| -3dB Input Bandwidth                                                                     | BW <sub>-3dB</sub> | _                 | 25                  | _                     | MHz                | (Note 1)                                                       |  |  |  |

| Aperture Delay<br>(Note 1)                                                               |                    | —                 | 2.5                 | —                     | ns                 | Time delay between CNVST rising edge and when input is sampled |  |  |  |

| Leakage Current at Analog Input Pin                                                      | ILEAK_AN_INPUT     | _                 | ±2                  | ±200                  | nA                 | During input acquisition (t <sub>ACQ</sub> )                   |  |  |  |

| System Performance                                                                       |                    |                   |                     |                       |                    |                                                                |  |  |  |

| Sample Rate                                                                              | f <sub>s</sub>     | _                 | _                   | 1                     | Msps               | MCP331x1D-10                                                   |  |  |  |

| (Throughput rate)                                                                        |                    | _                 | _                   | 500                   | kSPS               | MCP331x1D-05                                                   |  |  |  |

| Resolution                                                                               |                    | 16                | —                   | _                     | Bits               | MCP33131D-10 and MCP33131D-05                                  |  |  |  |

| (No Missing Codes)                                                                       |                    | 14                | _                   | _                     | Bits               | MCP33121D-10 and MCP33121D-05                                  |  |  |  |

|                                                                                          |                    | 12                | —                   |                       | Bits               | MCP33111D-10 and MCP33111D-05                                  |  |  |  |

| Integral Nonlinearity                                                                    | INL                | -6                | ±2                  | +6                    | LSB                | MCP33131D-10 and MCP33131D-05                                  |  |  |  |

|                                                                                          |                    | -1.5              | ±0.5                | +1.5                  | LSB                | MCP33121D-10 and MCP33121D-05                                  |  |  |  |

|                                                                                          |                    |                   | ±0.12               |                       | LSB                | MCP33111D-10 and MCP33111D-05                                  |  |  |  |

| Differential Nonlinearity                                                                | DNL                | -0.98             | ±0.8                | +1.8                  | LSB                | MCP33131D-10 and MCP33131D-05                                  |  |  |  |

|                                                                                          |                    | -0.8              | ±0.25               | +0.8                  | LSB                | MCP33121D-10 and MCP33121D-05                                  |  |  |  |

|                                                                                          |                    | -0.3              | ±0.06               | +0.3                  | LSB                | MCP33111D-10 and MCP33111D-05                                  |  |  |  |

| Offset Error                                                                             |                    |                   | ±0.1                | ±2.3                  | mV                 | MCP33131D-10 and MCP33131D-05                                  |  |  |  |

|                                                                                          |                    | —                 | ±0.125              | ±3                    | mV                 | MCP33121D-10 and MCP33121D-05                                  |  |  |  |

|                                                                                          |                    | —                 | ±0.8                | ±3.66                 | mV                 | MCP33111D-10 and MCP33111D-05                                  |  |  |  |

| Offset Error Drift with Temperature                                                      |                    | —                 | ±0.8                | —                     | μV/ºC              |                                                                |  |  |  |

| Gain Error                                                                               | G <sub>ER</sub>    | —                 | ±2                  | —                     | LSB                | MCP33131D-10 and MCP33131D-05                                  |  |  |  |

|                                                                                          |                    | _                 | ±0.5                | —                     | LSB                | MCP33121D-10 and MCP33121D-05                                  |  |  |  |

|                                                                                          |                    | —                 | ±0.1                | —                     | LSB                | MCP33111D-10 and MCP33111D-05                                  |  |  |  |

| Gain Error Drift with temperature                                                        |                    | _                 | ±0.35               | _                     | μV/ <sup>o</sup> C |                                                                |  |  |  |

| Input common-mode rejection ratio                                                        | CMRR               | _                 | 84                  | _                     | dB                 |                                                                |  |  |  |

| Power Supply Rejection Ratio                                                             | PSRR               | _                 | 70                  | _                     | dB                 | (Note 5)                                                       |  |  |  |

Note 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

Decoupling capacitor is recommended on the following pins:

(a) AV<sub>DD</sub> pin: 1 μF ceramic capacitor, (b) DV<sub>IO</sub> pin: 0.1 μF ceramic capacitor, (c) V<sub>REF</sub> pin: 10 μF tantalum capacitor.

4: Differential Input Full-Scale Range (FSR) = 2 x V<sub>REF</sub>

5: PSRR (dB) = -20 log ( $D_{VOUT}/AV_{DD}$ ), where  $D_{VOUT}$  = change in conversion result.

#### TABLE 1-1: KEY ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input ( $V_{IN}$ ) = -1 dBFS sine wave,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF

- MCP331x1D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.

- MCP331x1D-05: Sample Rate (f<sub>S</sub>) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

| Parameters                        | Sym.  | Min. Typ. Max. Units Conditions           |      |              |          |                                                   |  |  |

|-----------------------------------|-------|-------------------------------------------|------|--------------|----------|---------------------------------------------------|--|--|

| amic Performance                  |       |                                           |      |              |          |                                                   |  |  |

| Signal-to-Noise Ratio             | SNR   | MCP33131D-10 and MCP33131D-05: 16-bit ADC |      |              |          |                                                   |  |  |

|                                   |       |                                           | 91.6 | —            | dBFS     | $V_{REF}$ = 5V, f <sub>IN</sub> = 1 kHz           |  |  |

|                                   |       | _                                         | 86.6 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |

|                                   |       | 88.7                                      | 91.3 | _            |          | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 10 kHz   |  |  |

|                                   |       | _                                         | 86.6 | _            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |

|                                   |       |                                           | MCP3 | 3121D-10 and | MCP33121 | D-05: 14-bit ADC                                  |  |  |

|                                   |       |                                           | 85.2 | _            | dBFS     | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |

|                                   |       |                                           | 83.5 | _            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |

|                                   |       | 81.7                                      | 85.1 | —            | ]        | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 10 kHz   |  |  |

|                                   |       | _                                         | 83.5 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |

|                                   |       |                                           | MCP3 | 3111D-10 and | MCP33111 | D-05: 12-bit ADC                                  |  |  |

|                                   |       | _                                         | 73.9 | _            | dBFS     | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |

|                                   |       | _                                         | 73.8 | _            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |

|                                   |       | 71.1                                      | 73.9 | —            |          | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 10 kHz   |  |  |

|                                   |       |                                           | 73.8 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |

| nal-to-Noise and Distortion Ratio | SINAD |                                           | MCP3 | 3131D-10 and | MCP33131 | D-05: 16-bit ADC                                  |  |  |

| (Note 6)                          |       |                                           | 91.5 | _            | dBFS     | $V_{REF}$ = 5V, $f_{IN}$ = 1 kHz                  |  |  |

|                                   |       |                                           | 86.6 | —            |          | $V_{REF}$ = 2.5V, f <sub>IN</sub> = 1 kHz         |  |  |

|                                   |       |                                           | 91   | _            |          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |

|                                   |       |                                           | 86.2 | —            |          | $V_{REF}$ = 2.5V, f <sub>IN</sub> = 10 kHz        |  |  |

|                                   |       | MCP33121D-10 and MCP33121D-05: 14-bit ADC |      |              |          |                                                   |  |  |

|                                   |       |                                           | 85.2 | —            | dBFS     | $V_{REF}$ = 5V, $f_{IN}$ = 1 kHz                  |  |  |

|                                   |       |                                           | 83.5 | —            |          | $V_{REF}$ = 2.5V, f <sub>IN</sub> = 1 kHz         |  |  |

|                                   |       | _                                         | 85   | _            |          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |

|                                   |       | _                                         | 83.3 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |

|                                   |       |                                           | MCP3 | 3111D-10 and | MCP33111 | D-05: 12-bit ADC                                  |  |  |

|                                   |       |                                           | 73.9 | —            | dBFS     | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |

|                                   |       |                                           | 73.8 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |

|                                   |       | —                                         | 73.9 | —            |          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |

|                                   |       | —                                         | 73.8 | —            |          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |

**Note** 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

3: Decoupling capacitor is recommended on the following pins:

(a) AV<sub>DD</sub> pin: 1 μF ceramic capacitor, (b) DV<sub>IO</sub> pin: 0.1 μF ceramic capacitor, (c) V<sub>REF</sub> pin: 10 μF tantalum capacitor.

4: Differential Input Full-Scale Range (FSR) = 2 x V<sub>REF</sub>

5: PSRR (dB) = -20 log (D<sub>VOUT</sub>/AV<sub>DD</sub>), where D<sub>VOUT</sub> = change in conversion result.

#### TABLE 1-1: KEY ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}$ C to +125°C,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input ( $V_{IN}$ ) = -1 dBFS sine wave,  $f_{IN} = 10$  kHz,  $C_{LOAD SDO} = 20$  pF

MCP331x1D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.

| MCP331x1D-05: Sample Rate (f <sub>S</sub> ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz. |      |                                           |        |              |                          |                                                   |  |  |  |

|------------------------------------------------------------------------------------------|------|-------------------------------------------|--------|--------------|--------------------------|---------------------------------------------------|--|--|--|

| Parameters                                                                               | Sym. | Min.                                      | Тур.   | Max.         | Units                    | Conditions                                        |  |  |  |

| Spurious Free Dynamic Range                                                              | SFDR | MCP33131D-10 and MCP33131D-05: 16-bit ADC |        |              |                          |                                                   |  |  |  |

|                                                                                          |      | —                                         | 103.7  | —            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | —                                         | 98     | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | —                                         | 103.5  | —            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | _                                         | 97.5   | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |  |

|                                                                                          |      |                                           | MCP3   | 3121D-10 and | MCP33121                 | D-05: 14-bit ADC                                  |  |  |  |

|                                                                                          |      | —                                         | 103.6  | —            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | —                                         | 98     | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | —                                         | 103.5  | —            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | —                                         | 97.4   | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |  |

|                                                                                          |      |                                           | MCP3   | 3111D-10 and | MCP33111                 | D-05: 12-bit ADC                                  |  |  |  |

|                                                                                          |      | —                                         | 99.3   | —            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | —                                         | 97.7   | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | —                                         | 99.3   | —            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | —                                         | 97.2   | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |  |

| Total Harmonic Distortion                                                                | THD  | MCP33131D-10 and MCP33131D-05: 16-bit ADC |        |              |                          |                                                   |  |  |  |

| (first five harmonics)                                                                   |      | _                                         | -100.4 | _            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | —                                         | -95.4  | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | _                                         | -99.3  | _            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | _                                         | -95.4  | —            |                          | $V_{REF}$ = 2.5V, $f_{IN}$ = 10 kHz               |  |  |  |

|                                                                                          |      |                                           | MCP3   | 3121D-10 and | MCP33121D-05: 14-bit ADC |                                                   |  |  |  |

|                                                                                          |      | _                                         | -100.1 | _            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | _                                         | -95.3  | _            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | —                                         | -99.2  | —            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | —                                         | -95.3  | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |  |

|                                                                                          |      |                                           | MCP3   | 3111D-10 and | MCP33111                 | D-05: 12-bit ADC                                  |  |  |  |

|                                                                                          |      | —                                         | -97.5  | —            | dBc                      | V <sub>REF</sub> = 5V, f <sub>IN</sub> = 1 kHz    |  |  |  |

|                                                                                          |      | —                                         | -94.4  | —            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 1 kHz  |  |  |  |

|                                                                                          |      | _                                         | -96.7  | —            |                          | $V_{REF}$ = 5V, $f_{IN}$ = 10 kHz                 |  |  |  |

|                                                                                          |      | _                                         | -94.4  | _            |                          | V <sub>REF</sub> = 2.5V, f <sub>IN</sub> = 10 kHz |  |  |  |

**Note** 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

3: Decoupling capacitor is recommended on the following pins:

(a) AV<sub>DD</sub> pin: 1 μF ceramic capacitor, (b) DV<sub>IO</sub> pin: 0.1 μF ceramic capacitor, (c) V<sub>REF</sub> pin: 10 μF tantalum capacitor.

4: Differential Input Full-Scale Range (FSR) = 2 x V<sub>REF</sub>

5: PSRR (dB) = -20 log ( $D_{VOUT}/AV_{DD}$ ), where  $D_{VOUT}$  = change in conversion result.

#### **TABLE 1-1: KEY ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C,  $AV_{DD} = 1.8$ V,  $DV_{IO} = 3.3$ V,  $V_{REF} = 5$ V, GND = 0V, Differential Analog Input (V<sub>IN</sub>) = -1 dBFS sine wave,  $f_{IN}$  = 10 kHz,  $C_{LOAD\_SDO}$  = 20 pF

- MCP331x1D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.

| Parameters                                               | Sym.                   | Min.                   | Тур.                   | Max.                   | Units  | Conditions                                         |

|----------------------------------------------------------|------------------------|------------------------|------------------------|------------------------|--------|----------------------------------------------------|

| System Self-Calibration                                  |                        |                        |                        |                        |        |                                                    |

| Self-Calibration Time                                    | t <sub>CAL</sub>       | _                      | 500                    | 650                    | ms     | (Note 2)                                           |

| Number of SCLK Clocks for<br>Recalibrate Command         | ReCal <sub>NSCLK</sub> | —                      | 1024                   |                        | clocks | Includes clocks for data bits                      |

| Serial Interface Timing Informa                          | tion: See Table        | 1-2                    |                        |                        |        |                                                    |

| Digital Inputs/Outputs                                   |                        |                        |                        |                        |        |                                                    |

| High-level Input voltage                                 | V <sub>IH</sub>        | 0.7 * DV <sub>IO</sub> | —                      | DV <sub>IO</sub> + 0.3 | V      | DV <sub>IO</sub> ≥2.3V                             |

|                                                          |                        | 0.9 * DV <sub>IO</sub> | —                      | DV <sub>IO</sub> + 0.3 | V      | DV <sub>IO</sub> < 2.3V                            |

| Low-level input voltage                                  | V <sub>IL</sub>        | -0.3                   | _                      | 0.3 * DV <sub>IO</sub> | V      | $DV_{IO} \ge 2.3V$                                 |

|                                                          |                        | -0.3                   | _                      | 0.2 * DV <sub>IO</sub> | V      | DV <sub>IO</sub> < 2.3V                            |

| Hysteresis of Schmitt Trigger Inputs                     | V <sub>HYST</sub>      | _                      | 0.2 * DV <sub>IO</sub> | _                      | V      | All digital inputs                                 |

| Low-level output voltage                                 | V <sub>OL</sub>        | _                      | _                      | 0.2 * DV <sub>IO</sub> | V      | I <sub>OL</sub> = 500 μA (sink)                    |

| High-level output voltage                                | V <sub>OH</sub>        | 0.8 * DV <sub>IO</sub> | _                      | -                      | V      | I <sub>OL</sub> = - 500 μA (source)                |

| Input leakage current                                    | ILI                    | _                      | _                      | ±1                     | μA     | CNVST/SDI/SCLK = GND or DVIO                       |

| Output leakage current                                   | I <sub>LO</sub>        | _                      | _                      | ±1                     | μA     | Output is high-Z, SDO = GND or<br>DV <sub>IO</sub> |

| Internal capacitance<br>(all digital inputs and outputs) | C <sub>INT</sub>       | —                      | 7                      | —                      | pF     | T <sub>A</sub> = 25°C (Note 1)                     |

Note 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

3: Decoupling capacitor is recommended on the following pins:

(a) AV<sub>DD</sub> pin: 1 µF ceramic capacitor, (b) DV<sub>IO</sub> pin: 0.1 µF ceramic capacitor, (c) V<sub>REF</sub> pin: 10 µF tantalum capacitor.

4: Differential Input Full-Scale Range (FSR) = 2 x V<sub>REF</sub>

5: PSRR (dB) = -20 log ( $D_{VOUT}/AV_{DD}$ ), where  $D_{VOUT}$  = change in conversion result.

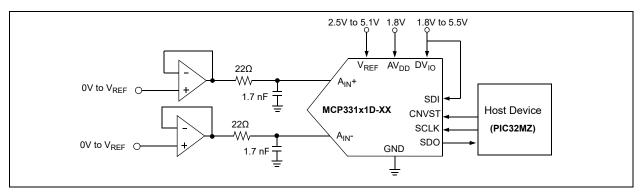

#### TABLE 1-2: SERIAL INTERFACE TIMING SPECIFICATIONS

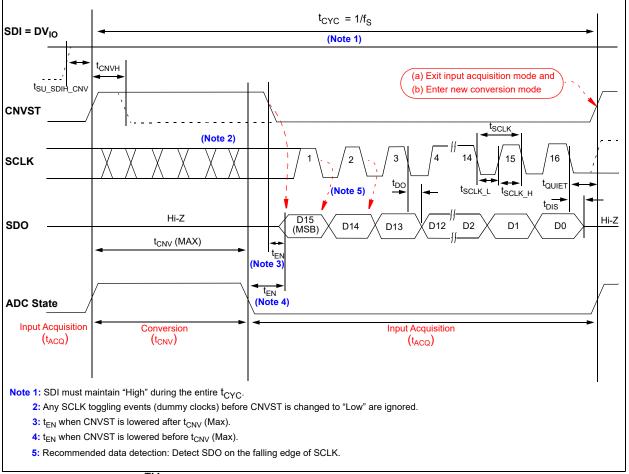

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input ( $V_{IN}$ ) = -1 dBFS sine wave,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.  $+25^{\circ}C$  is applied for typical value. All timings are measured at 50%. See Figure 1-1 for timing diagram.

MCP331x1D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.

MCP331x1D-05: Sample Rate (f<sub>S</sub>) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

| Parameters                         | Symbol                   | Min.       | Тур. | Max.       | Units | Conditions                                                     |

|------------------------------------|--------------------------|------------|------|------------|-------|----------------------------------------------------------------|

| Serial Clock frequency             | f <sub>SCLK</sub>        | _          | —    | 100        | MHz   | See t <sub>SCLK</sub> specification                            |

| SCLK Period                        | t <sub>SCLK</sub>        | 10         | _    | _          | ns    | DV <sub>IO</sub> ≥ 3.3V, f <sub>SCLK</sub> = 100 MHz (Max)     |

|                                    |                          | 12         | —    | _          | ns    | DV <sub>IO</sub> ≥ 2.3V, f <sub>SCLK</sub> = 83.3 MHz (Max)    |

|                                    |                          | 16         | -    | _          | ns    | DV <sub>IO</sub> ≥ 1.7V, f <sub>SCLK</sub> = 62.5 MHz (Max)    |

| SCLK Low Time                      | t <sub>SCLK_L</sub>      | 3          | _    | —          | ns    | DV <sub>IO</sub> ≥ 2.3V                                        |

|                                    |                          | 4.5        | —    | —          | ns    | DV <sub>IO</sub> ≥ 1.7V                                        |

| SCLK High Time                     | t <sub>SCLK_H</sub>      | 3          | —    | —          | ns    | $DV_{IO} \ge 2.3V$                                             |

|                                    |                          | 4.5        | _    | _          | ns    | DV <sub>IO</sub> ≥ 1.7V                                        |

| Output Valid from SCLK Low         | t <sub>DO</sub>          | _          | _    | 9.5        | ns    | DV <sub>IO</sub> ≥ 3.3V                                        |

|                                    |                          | _          | _    | 12         | ns    | DV <sub>IO</sub> ≥ 2.3V                                        |

|                                    |                          | —          | _    | 16         | ns    | DV <sub>IO</sub> ≥ 1.7V                                        |

| Quiet time                         | t <sub>QUIET</sub>       | 10         | —    | —          | ns    | (Note 2)                                                       |

| 3-Wire Operation:                  |                          |            |      |            |       |                                                                |

| SDI Valid Setup time               | t <sub>SU_SDIH_CNV</sub> | 5          | _    | —          | ns    | SDI High to CNVST Rising Edge                                  |

| CNVST Pulse Width High Time        | t <sub>CNVH</sub>        | 10         | _    | —          | ns    |                                                                |

| Output Enable Time                 | t <sub>EN</sub>          | —          | —    | 10         | ns    | $DV_{1O} \ge 2.3V$                                             |

|                                    |                          | —          | —    | 15         | ns    | DV <sub>IO</sub> ≥ 1.7V                                        |

| Output Disable Time                | t <sub>DIS</sub>         | —          | —    | 15         | ns    | (Note 2)                                                       |

| MCP331x1D-10                       |                          |            |      |            |       |                                                                |

| Sample Rate                        | f <sub>s</sub>           | —          | —    | 1          | Msps  | Throughput rate                                                |

| Input Acquisition Time<br>(Note 2) | t <sub>ACQ</sub>         | 290<br>250 | 300  | _          | ns    | -40°C ≤ T <sub>A</sub> ≤ 85°C<br>85°C < T <sub>A</sub> ≤ 125°C |

| Data Conversion Time               | t <sub>CNV</sub>         | _          | 700  | 710<br>750 | ns    | -40°C ≤ T <sub>A</sub> ≤ 85°C<br>85°C < T <sub>A</sub> ≤ 125°C |

| Time between Conversions           | t <sub>CYC</sub>         | 1          | _    | _          | μs    | $t_{CYC} = t_{ACQ} + t_{CNV}, f_S = 1 \text{ Msps}$            |

| MCP331x1D-05                       |                          |            |      |            |       |                                                                |

| Sample Rate                        | fs                       | _          | _    | 500        | kSPS  | Throughput rate                                                |

| Input Acquisition Time (Note 2)    | t <sub>ACQ</sub>         | 700        | 800  |            | ns    | -40°C ≤ T <sub>A</sub> ≤ 125°C                                 |

| Data Conversion Time               | t <sub>CNV</sub>         | _          | 1200 | 1300       | ns    | -40°C ≤ T <sub>A</sub> ≤ 125°C                                 |

| Time between Conversions           | t <sub>CYC</sub>         | 2          | _    | _          | μs    | $t_{CYC} = t_{ACQ} + t_{CNV}, f_S = 500 \text{ kSPS}$          |

Note 1: This parameter is ensured by design and not 100% tested.

2: This parameter is ensured by characterization and not 100% tested.

### TABLE 1-3:TEMPERATURE CHARACTERISTICS

| Parameters                  | Symbol                     | Min. | Тур. | Max. | Units | Conditions |  |  |  |  |

|-----------------------------|----------------------------|------|------|------|-------|------------|--|--|--|--|

| Temperature Ranges          |                            |      |      |      |       |            |  |  |  |  |

| Operating Temperature Range | Τ <sub>Α</sub>             | -40  | _    | +125 | °C    | (Note 1)   |  |  |  |  |

| Storage Temperature Range   | Τ <sub>Α</sub>             | -65  | _    | +150 | °C    | (Note 1)   |  |  |  |  |

| Thermal Package Resistance  | Thermal Package Resistance |      |      |      |       |            |  |  |  |  |

| Thermal Resistance, MSOP-10 | $\theta_{JA}$              | _    | 202  | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, TDFN-10 | $\theta_{JA}$              | -    | 68   | —    | °C/W  |            |  |  |  |  |

Note 1: The internal junction temperature (T<sub>i</sub>) must not exceed the absolute maximum specification of +150°C.

**FIGURE 1-1:** Interface Timing Diagram. CNVST is used as chip select. See Figure 7-2 for more details.

NOTES:

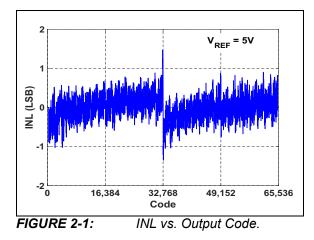

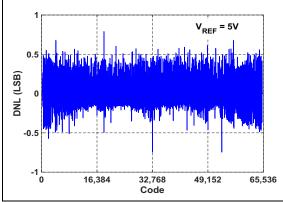

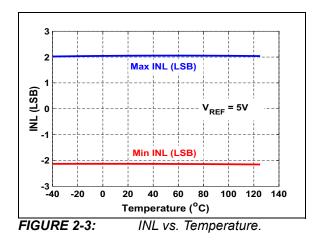

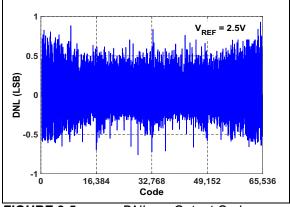

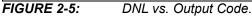

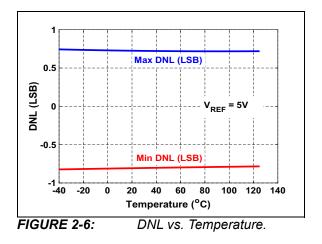

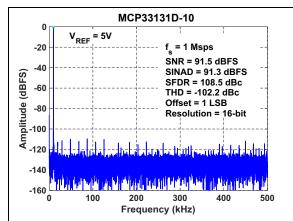

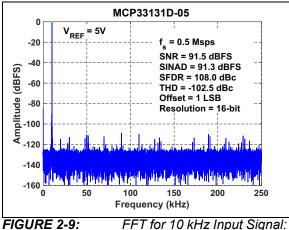

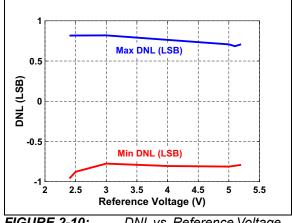

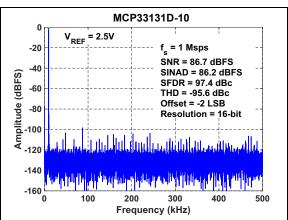

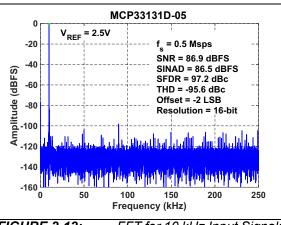

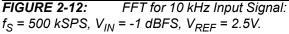

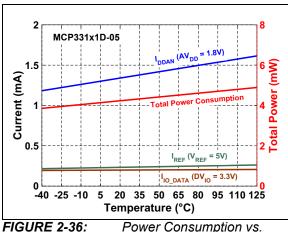

### 2.0 TYPICAL PERFORMANCE CURVES FOR 16-BIT DEVICES (MCP33131D-XX)

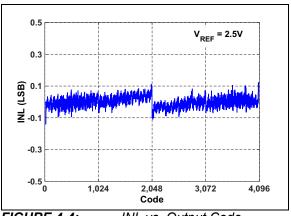

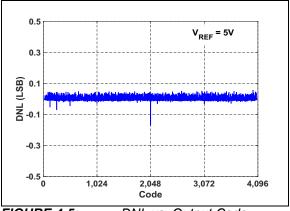

- **Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

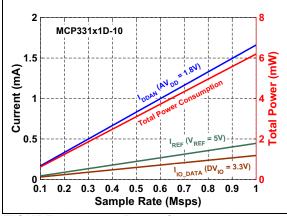

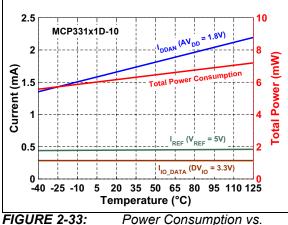

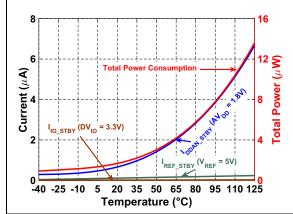

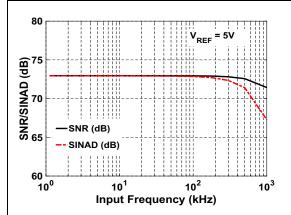

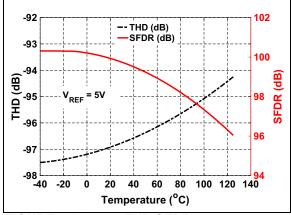

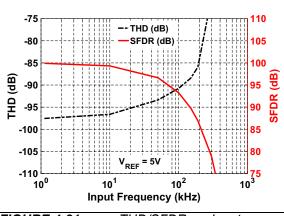

- Note: Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF. MCP33131D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33131D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

FIGURE 2-2:

DNL vs. Output Code.

FIGURE 2-4: INL vs. Output Code.

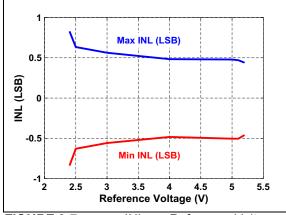

Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ , Note: V<sub>REF</sub> = 5V, GND = 0V, Differential Analog Input (VIN) = -1 dBFS, f<sub>IN</sub> = 10 kHz, C<sub>LOAD SDO</sub> = 20 pF. MCP33131D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33131D-05: Sample Rate (f<sub>S</sub>) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

FIGURE 2-7: INL vs. Reference Voltage.

FIGURE 2-8: FFT for 10 kHz Input Signal:  $f_{\rm S}$  = 1 Msps,  $V_{\rm IN}$  = -1 dBFS,  $V_{\rm REF}$  = 5V.

$f_{\rm S}$  = 500 kSPS,  $V_{\rm IN}$  = -1 dBFS,  $V_{\rm REF}$  = 5V.

FIGURE 2-11: FFT for 10 kHz Input Signal:  $f_{\rm S} = 1 \text{ Msps}, V_{\rm IN} = -1 \text{ dBFS}, V_{\rm RFF} = 2.5V.$

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10 \text{ kHz}$ ,  $C_{LOAD\_SDO} = 20 \text{ pF}$ .<br/>MCP33131D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33131D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

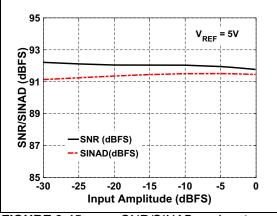

FIGURE 2-14: SNR/SINAD vs. Temperature: V<sub>REF</sub> = 5V.

**FIGURE 2-15:** SNR/SINAD vs. Input Amplitude:  $F_{IN}$  = 10 kHz.

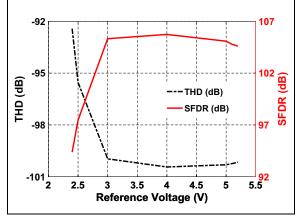

FIGURE 2-16: SFDR/THD vs. V<sub>REF</sub>

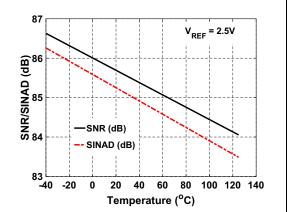

**FIGURE 2-17:** SNR/SINAD vs. Temperature: V<sub>REF</sub> = 2.5V.

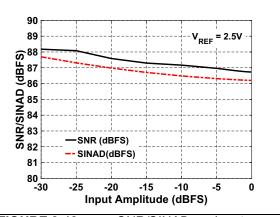

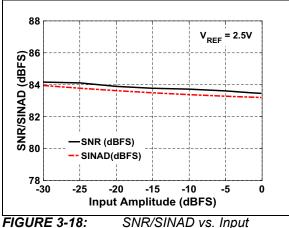

**FIGURE 2-18:** SNR/SINAD vs. Input Amplitude:  $F_{IN} = 10 \text{ kHz}$ .

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33131D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33131D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

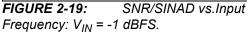

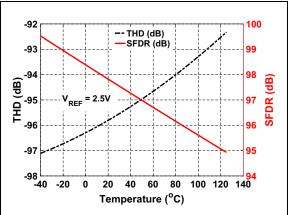

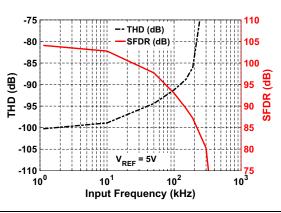

**FIGURE 2-20:** THD/SFDR vs. Temperature: V<sub>REF</sub> = 5V.

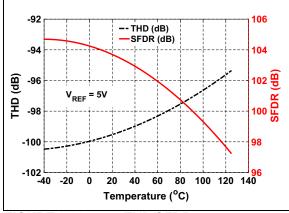

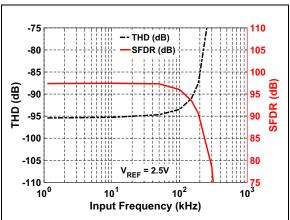

FIGURE 2-21: THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 5V.

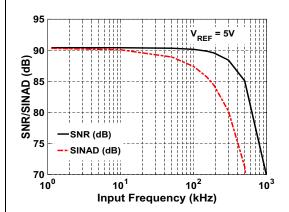

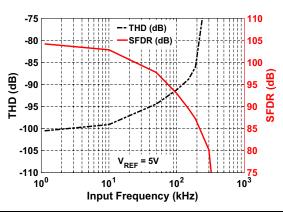

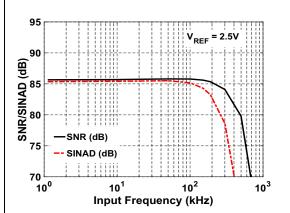

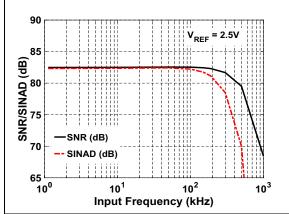

**FIGURE 2-22:** SNR/SINAD vs.Input Frequency:  $V_{IN} = -1$  dBFS.

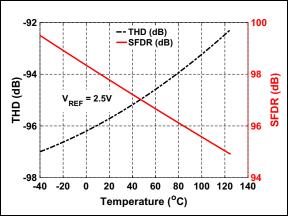

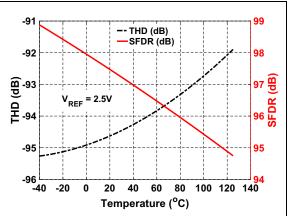

**FIGURE 2-23:** THD/SFDR vs. Temperature:  $V_{RFF}$  = 2.5V.

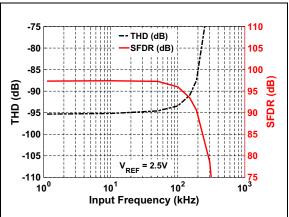

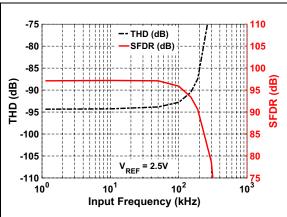

**FIGURE 2-24:** THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 2.5V.

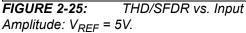

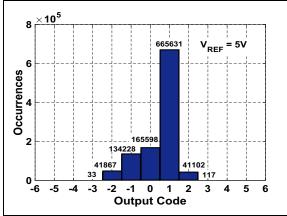

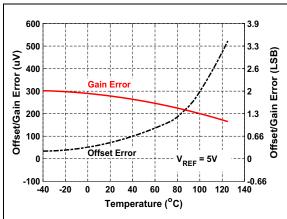

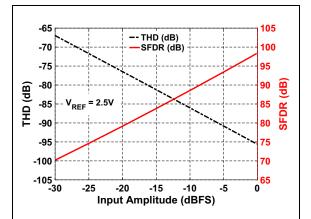

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10 \text{ kHz}$ ,  $C_{LOAD\_SDO} = 20 \text{ pF}$ .<br/>MCP33131D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33131D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

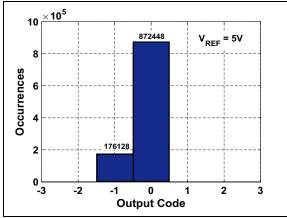

**FIGURE 2-26:** Shorted Input Histogram: V<sub>RFF</sub> = 5V.

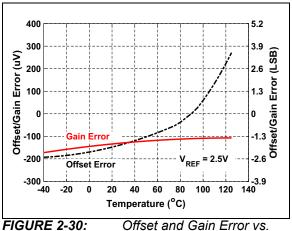

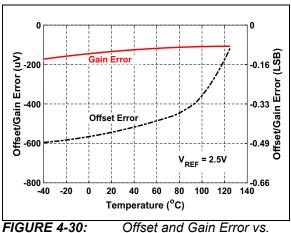

**FIGURE 2-27:** Offset and Gain Error vs. Temperature: V<sub>REF</sub> = 5V.

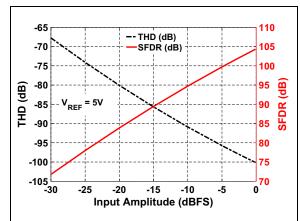

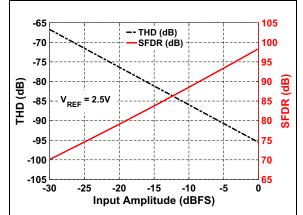

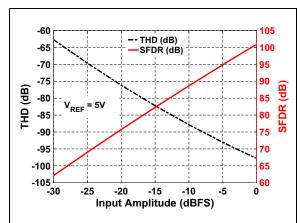

**FIGURE 2-28:** THD/SFDR vs. Input Amplitude:  $V_{REF} = 2.5V$ .

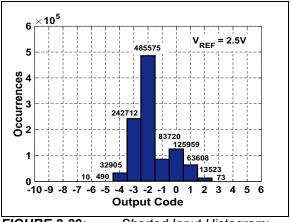

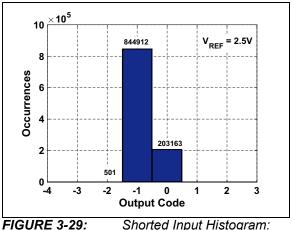

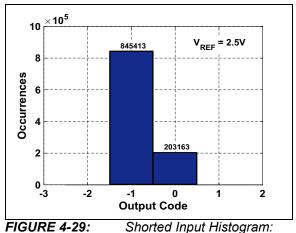

**FIGURE 2-29:** Shorted Input Histogram:  $V_{RFF} = 2.5V.$

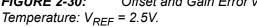

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33131D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33131D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

**FIGURE 2-31:** CMRR vs. Input Frequency: V<sub>REF</sub> = 5V.

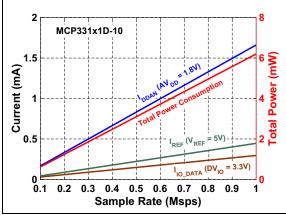

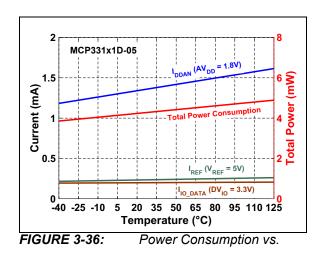

**FIGURE 2-32:** Power Consumption vs. Sample Rate: C<sub>LOAD</sub> <sub>SDO</sub> = 20 pF.

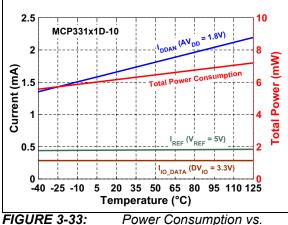

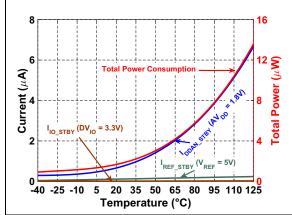

Temperature:  $C_{LOAD\_SDO} = 20 \text{ pF.}$

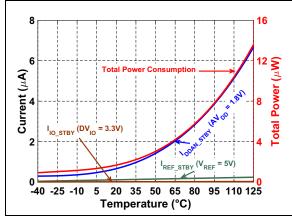

**FIGURE 2-34:** Power Consumption vs. Temperature during Shutdown.

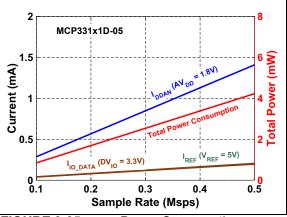

FIGURE 2-35:Power Consumption vs.Sample Rate:  $C_{LOAD\_SDO} = 20 \text{ pF.}$

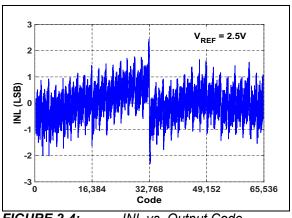

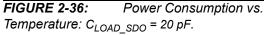

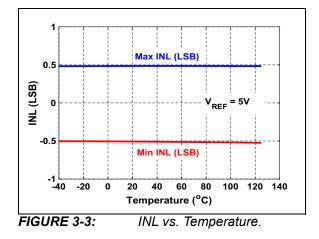

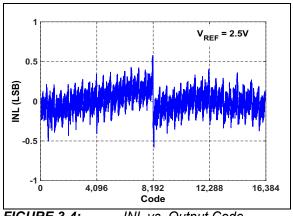

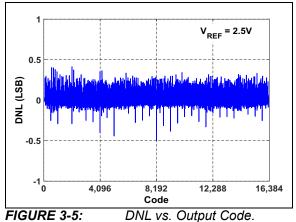

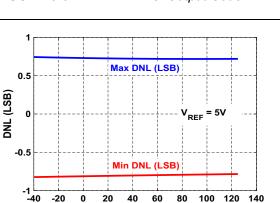

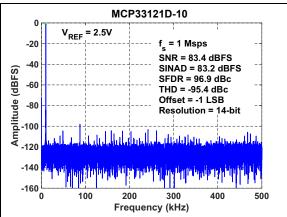

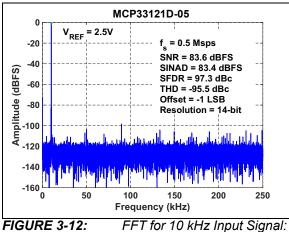

### 3.0 TYPICAL PERFORMANCE CURVES FOR 14-BIT DEVICES (MCP33121D-XX)

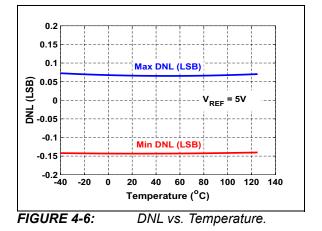

- **Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

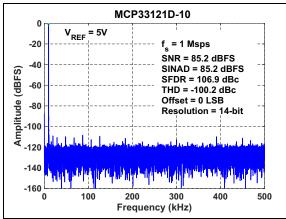

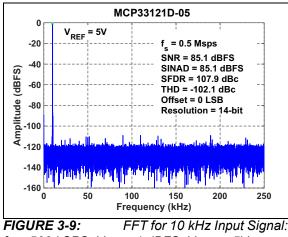

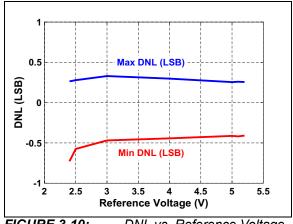

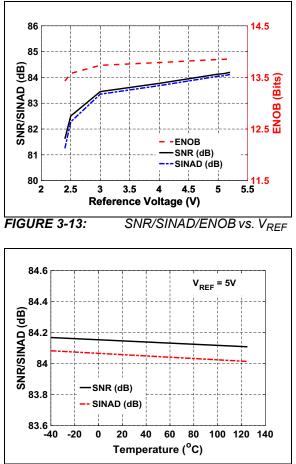

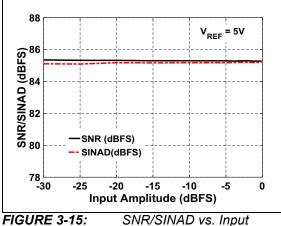

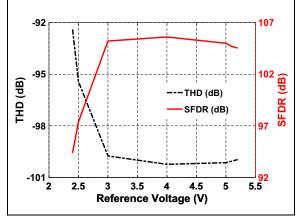

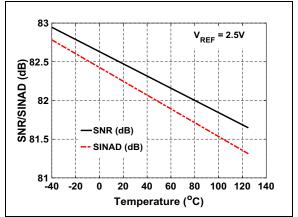

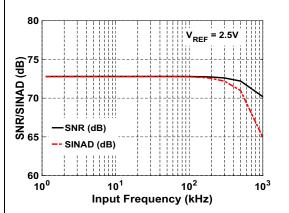

- Note: Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF. MCP33121D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33121D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

DNL vs. Output Code.

FIGURE 3-4: INL vs. Output Code.

Temperature (°C)

DNL vs. Temperature.

FIGURE 3-6:

Note: Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ , V<sub>REF</sub> = 5V, GND = 0V, Differential Analog Input (VIN) = -1 dBFS, f<sub>IN</sub> = 10 kHz, C<sub>LOAD SDO</sub> = 20 pF. MCP33121D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33121D-05: Sample Rate (fs) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

FIGURE 3-7: INL vs. Reference Voltage.

FIGURE 3-8: FFT for 10 kHz Input Signal:  $f_{\rm S}$  = 1 Msps,  $V_{\rm IN}$  = -1 dBFS,  $V_{\rm RFF}$  = 5V.

FFT for 10 kHz Input Signal:  $f_{\rm S}$  = 500 kSPS,  $V_{\rm IN}$  = -1 dBFS,  $V_{\rm REF}$  = 5V.

FIGURE 3-11: FFT for 10 kHz Input Signal:  $f_{\rm S}$  = 1 Msps,  $V_{\rm IN}$  = -1 dBFS,  $V_{\rm REF}$  = 2.5V.

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10 \text{ kHz}$ ,  $C_{LOAD\_SDO} = 20 \text{ pF}$ .<br/>MCP33121D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33121D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

**FIGURE 3-14:** SNR/SINAD vs. Temperature: V<sub>REF</sub> = 5V.

**FIGURE 3-15:** SNR/SINAD vs. Inpu Amplitude:  $F_{IN}$  = 10 kHz.

FIGURE 3-16: SFDR/THD vs. V<sub>REF</sub>

**FIGURE 3-17:** SNR/SINAD vs. Temperature: V<sub>REF</sub> = 2.5V.

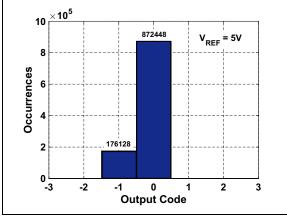

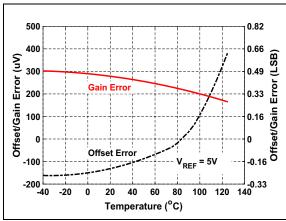

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33121D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33121D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

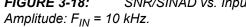

**FIGURE 3-19:** SNR/SINAD vs.Input Frequency: V<sub>IN</sub> = -1 dBFS.

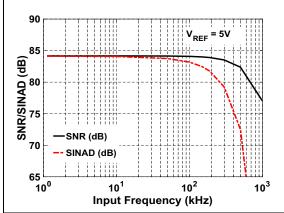

FIGURE 3-20: THD/SFDR vs. Temperature: V<sub>REF</sub> = 5V.

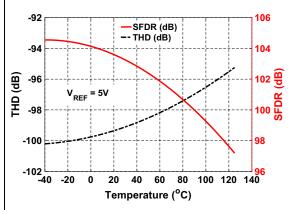

FIGURE 3-21: THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 5V.

**FIGURE 3-22:** SNR/SINAD vs.Input Frequency:  $V_{IN}$  = -1 dBFS.

**FIGURE 3-23:** THD/SFDR vs. Temperature:  $V_{REF} = 2.5V$ .

**FIGURE 3-24:** THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 2.5V.

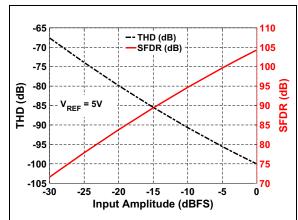

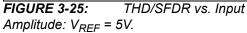

Note: Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ , V<sub>REF</sub> = 5V, GND = 0V, Differential Analog Input (VIN) = -1 dBFS, f<sub>IN</sub> = 10 kHz, C<sub>LOAD SDO</sub> = 20 pF. MCP33121D-10: Sample Rate (f<sub>S</sub>) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33121D-05: Sample Rate (f<sub>S</sub>) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

FIGURE 3-26: Shorted Input Histogram:  $V_{RFF} = 5V.$

**FIGURE 3-27:** Offset and Gain Error vs. Temperature:  $V_{RFF} = 5V$ .

**FIGURE 3-28:** THD/SFDR vs. Input Amplitude:  $V_{REF} = 2.5V$ .

$V_{RFF} = 2.5V.$

Shorted Input Histogram:

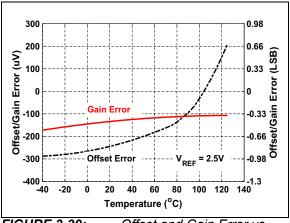

**FIGURE 3-30:** Offset and Gain Error vs. Temperature:  $V_{REF} = 2.5V$ .

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33121D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33121D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

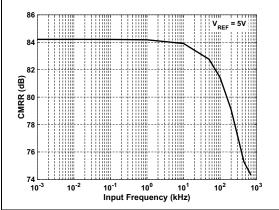

**FIGURE 3-31:** CMRR vs. Input Frequency: V<sub>REF</sub> = 5V.

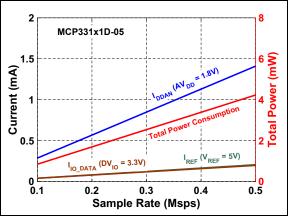

**FIGURE 3-32:** Power Consumption vs. Sample Rate:  $C_{LOAD SDO} = 20 \text{ pF.}$

Temperature:  $C_{LOAD\_SDO} = 20 \ pF.$

**FIGURE 3-34:** Power Consumption vs. Temperature during Shutdown.

**FIGURE 3-35:** Power Consumption vs. Sample Rate:  $C_{LOAD SDO} = 20 \text{ pF.}$

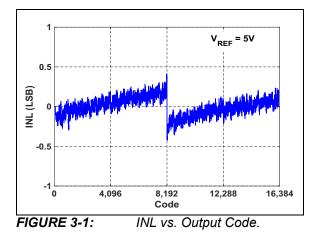

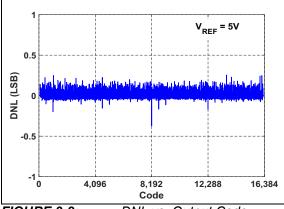

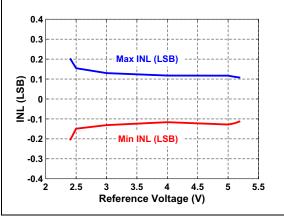

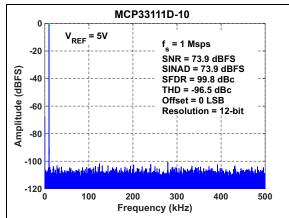

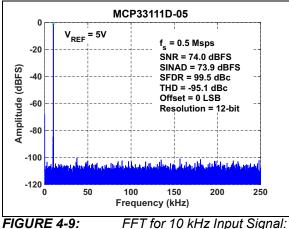

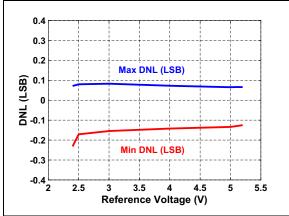

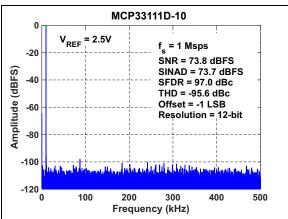

### 4.0 TYPICAL PERFORMANCE CURVES FOR 12-BIT DEVICES (MCP33111D-XX)

- **Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

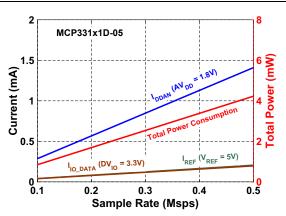

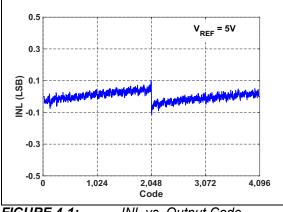

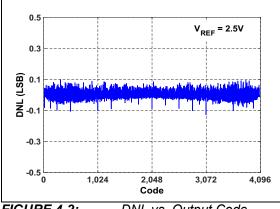

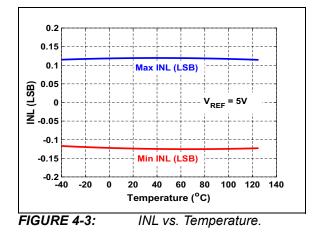

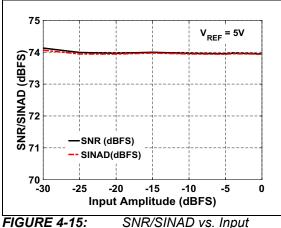

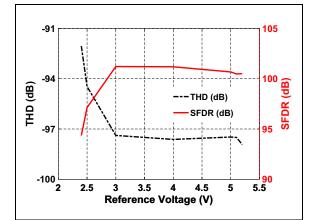

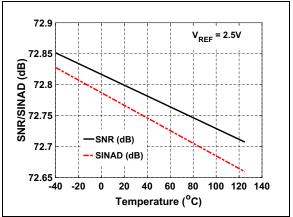

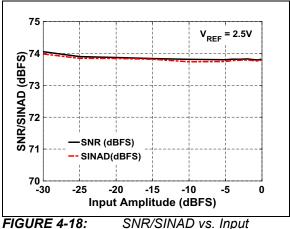

- Note: Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF. MCP33111D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. MCP33111D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

FIGURE 4-1: INL vs. Output Code.

DNL vs. Output Code.

FIGURE 4-4: INL vs. Output Code.

FIGURE 4-5: DNL vs. Output Code.

FIGURE 4-7: INL vs. Reference Voltage.

**FIGURE 4-8:** FFT for 10 kHz Input Signal:  $f_S = 1 Msps, V_{IN} = -1 dBFS, V_{REF} = 5V.$

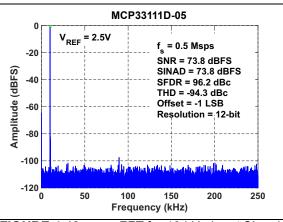

$f_S = 500 \text{ kSPS}, V_{IN} = -1 \text{ dBFS}, V_{REF} = 5V.$

FIGURE 4-10: DNL vs. Reference Voltage.

**FIGURE 4-11:** FFT for 10 kHz Input Signal:  $f_S = 1 Msps, V_{IN} = -1 dBFS, V_{REF} = 2.5V.$

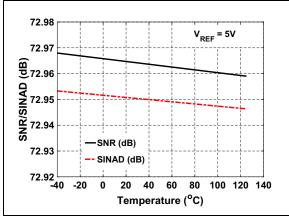

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10 \text{ kHz}$ ,  $C_{LOAD\_SDO} = 20 \text{ pF}$ .<br/>MCP33111D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33111D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

**FIGURE 4-14:** SNR/SINAD vs. Temperature: V<sub>REF</sub> = 5V.

FIGURE 4-15: SNR/SINAD vs. Inpu Amplitude: F<sub>IN</sub> = 10 kHz.

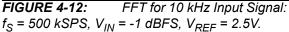

FIGURE 4-16: SFDR/THD vs. V<sub>REF</sub>

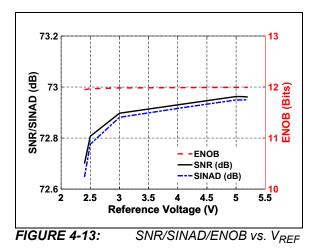

**FIGURE 4-17:** SNR/SINAD vs. Temperature: V<sub>REF</sub> = 2.5V.

**FIGURE 4-18:** SNR/SINAD vs. Inpu Amplitude:  $F_{IN}$  = 10 kHz.

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33111D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33111D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

**FIGURE 4-19:** SNR/SINAD vs. Input Frequency: V<sub>IN</sub> = -1 dBFS

**FIGURE 4-20:** THD/SFDR vs. Temperature: V<sub>REF</sub> = 5V.

FIGURE 4-21: THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 5V.

**FIGURE 4-22:** SNR/SINAD vs. Input Frequency:  $V_{IN} = -1$  dBFS.

**FIGURE 4-23:** THD/SFDR vs. Temperature:  $V_{RFF}$  = 2.5V.

**FIGURE 4-24:** THD/SFDR vs. Input Frequency: V<sub>REF</sub> = 2.5V.

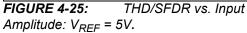

**Note:** Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,  $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF. **MCP33111D-10**: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz. **MCP33111D-05**: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

**FIGURE 4-26:** Shorted Input Histogram: V<sub>REF</sub> = 5V.

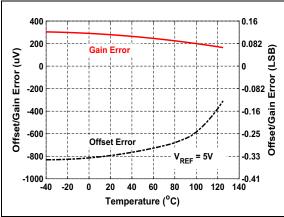

**FIGURE 4-27:** Offset and Gain Error vs. Temperature: V<sub>REF</sub> = 5V.

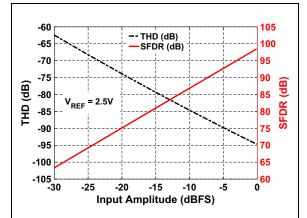

**FIGURE 4-28:** THD/SFDR vs. Input Amplitude: V<sub>REF</sub> = 2.5V.

$V_{REF} = 2.5V.$

**FIGURE 4-30:** Oπset and Gain Error V Temperature: V<sub>REF</sub> = 2.5V.

Note:Unless otherwise specified, all parameters apply for  $T_A = +25^{\circ}C$ ,  $AV_{DD} = 1.8V$ ,  $DV_{IO} = 3.3V$ ,<br/> $V_{REF} = 5V$ , GND = 0V, Differential Analog Input (VIN) = -1 dBFS,  $f_{IN} = 10$  kHz,  $C_{LOAD\_SDO} = 20$  pF.<br/>MCP33111D-10: Sample Rate ( $f_S$ ) = 1 Msps, SPI Clock Input (SCLK) = 60 MHz.<br/>MCP33111D-05: Sample Rate ( $f_S$ ) = 500 kSPS, SPI Clock Input (SCLK) = 30 MHz.

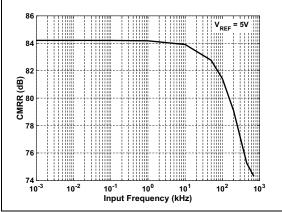

**FIGURE 4-31:** CMRR vs. Input Frequency: V<sub>REF</sub> = 5V.

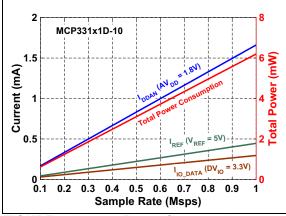

**FIGURE 4-32:** Power Consumption vs. Sample Rate:  $C_{LOAD SDO} = 20 \text{ pF.}$

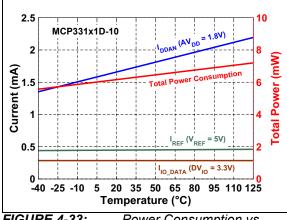

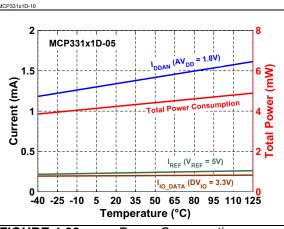

**FIGURE 4-33:** Power Consumption vs. Temperature:  $C_{LOAD SDO} = 20 \text{ pF.}$

**FIGURE 4-34:** Power Consumption vs. Temperature during Shutdown.

**FIGURE 4-35:** Power Consumption vs. Sample Rate:  $C_{LOAD\_SDO} = 20 \text{ pF.}$

FIGURE 4-36:Power Consumption vs.Temperature: $C_{LOAD\_SDO} = 20 \text{ pF.}$

### 5.0 PIN FUNCTION DESCRIPTIONS

| Pin Number | Pin Name          | Function                                                                                                                                                                                                                  |

|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>REF</sub>  | Reference voltage input (2.5V - 5.1V). This pin should be decoupled with a 10 $\mu F$ tantalum capacitor.                                                                                                                 |

| 2          | $AV_{DD}$         | DC supply voltage input for analog section (1.8V). This pin should be decoupled with a 1 $\mu$ F ceramic capacitor.                                                                                                       |

| 3          | A <sub>IN</sub> + | Differential positive analog input.                                                                                                                                                                                       |

| 4          | A <sub>IN</sub> - | Differential negative analog input.                                                                                                                                                                                       |

| 5          | GND               | Power supply ground reference. This pin is a common ground for both the analog power supply $(AV_{DD})$ and digital I/O supply $(DV_{IO})$ .                                                                              |

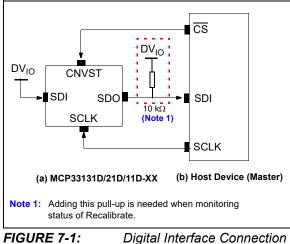

| 6          | CNVST             | Conversion-start control and active-low SPI chip-select digital input.<br>A new conversion is started on the rising edge of CNVST.<br>When the conversion is complete, output data is available at SDO by lowering CNVST. |

| 7          | SDO               | SPI-compatible serial digital data output: ADC conversion data is shifted out by SCLK clock, with MSB first.                                                                                                              |

| 8          | SCLK              | SPI-compatible serial data clock digital input.<br>The ADC output is synchronously shifted out by this clock.                                                                                                             |

| 9          | SDI               | SPI-compatible serial data digital input. Tie to DV <sub>IO</sub> for normal operation.                                                                                                                                   |

| 10         | DV <sub>IO</sub>  | DC supply voltage for digital input/output interface (1.7V - 5.5V). This pin should be decoupled with a 0.1 $\mu$ F ceramic capacitor.                                                                                    |

#### TABLE 5-1: PIN FUNCTION TABLE

### 5.1 Supply Voltages and Reference Voltage

The device has two power supply pins:

- a) Analog power supply (AV<sub>DD</sub>): 1.8V

- b) Digital input/output interface power supply (DV<sub>IO</sub>): 1.7V to 5.5V.

The large supply voltage range of DVIO allows the device to interface with various host devices that are operating with different supply voltages. See Table 1-2 for timing specifications for I/O interface signal parameters depending on DVIO voltage.

Note: Proper decoupling capacitors (1  $\mu$ F to AV<sub>DD</sub>, 0.1  $\mu$ F to DV<sub>IO</sub>) should be mounted as close as possible to the respective pins.

### 5.2 Reference Voltage (V<sub>REF</sub>)

The device requires a single-ended external reference voltage (V<sub>REF</sub>). The external input reference range is from 2.5V to 5.1V. This reference voltage sets the input full-scale range from 0V to V<sub>REF</sub>. See Figure 6-2 to Figure 6-8 for example application circuits and reference voltage settings.

| Note: | The reference pin needs a tantalum             |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | decoupling capacitor (10 $\mu$ F, 10V rating). |  |  |  |  |  |  |  |  |  |

|       | Additional multiple ceramic capacitors can     |  |  |  |  |  |  |  |  |  |

|       | be added in parallel to decouple               |  |  |  |  |  |  |  |  |  |

|       | high-frequency noises.                         |  |  |  |  |  |  |  |  |  |

Note: During the initial power-up sequence, the reference voltage (V<sub>REF</sub>) must be provided prior to supplying AV<sub>DD</sub> or within about 64 ms after supplying AV<sub>DD</sub>. Otherwise, it is strongly recommended to send a recalibrate command. See **Section 7.1 "Recalibrate Command**" for more details.

#### 5.2.1 VOLTAGE REFERENCE SELECTION

The performance of the voltage reference has a large impact on the accuracy of high-precision data acquisition systems. The voltage reference should have high-accuracy, low-noise, and low-temperature drift. A  $\pm 0.1\%$  output accuracy of the reference directly corresponds to  $\pm 0.1\%$  absolute accuracy of the ADC output. The RMS output noise voltage of the reference should be less than 1/2 LSB of the ADC.

### 6.0 DEVICE OVERVIEW

When the MCP33131D/MCP33121D/MCP33111D-XX is first powered-up, it performs a self-calibration and enters a low current input acquisition mode (Standby) by itself.

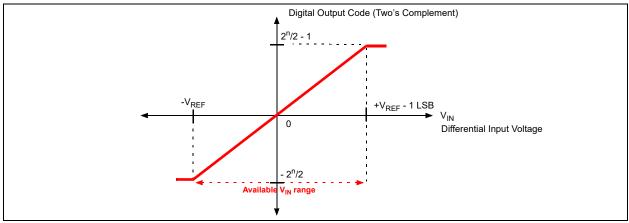

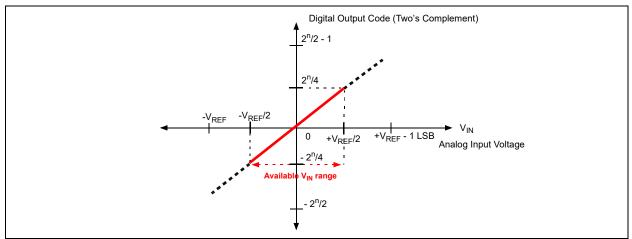

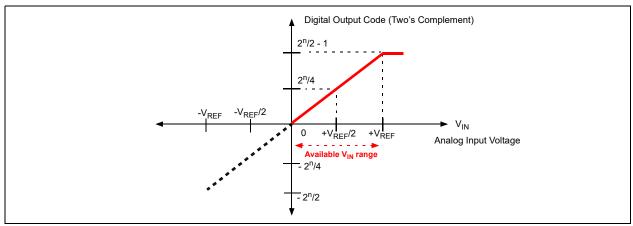

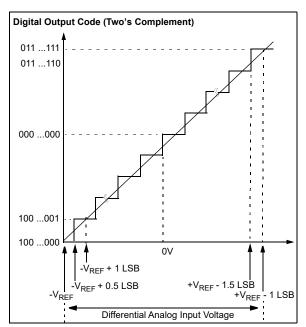

The external reference voltage (V<sub>REF</sub>) ranging from 2.5V to 5.1V sets the differential input full-scale range (FSR) from -V<sub>REF</sub> to +V<sub>REF</sub>.

The differential input signal needs an appropriate input common-mode voltage from 0V to V<sub>REF</sub>, depending on the input signal condition. V<sub>REF</sub>/2 is typically used for a symmetric differential input.

During input acquisition (Standby), the internal input sampling capacitors are connected to the input signal, while most of the internal analog circuits are shutdown to save power. During this input acquisition time ( $t_{ACQ}$ ), the device consumes less than 1  $\mu$ A.

The user can operate the device with an easy-to-use SPI-compatible 3-wire interface.

The device initiates data conversion on the rising edge of the conversion-start control (CNVST). The data conversion time ( $t_{CNV}$ ) is set by the internal clock. Once the conversion is complete and the host lowers CNVST, the output data is available on SDO and the device starts the next input acquisition by itself. During this input acquisition time ( $t_{ACQ}$ ), the user can clock out the output data by providing the SPI-compatible serial clock (SCLK).

The device provides conversion data with no missing codes. This ADC device family has a large input full-scale range, high precision, high throughput with no output latency, and is an ideal choice for various ADC applications.

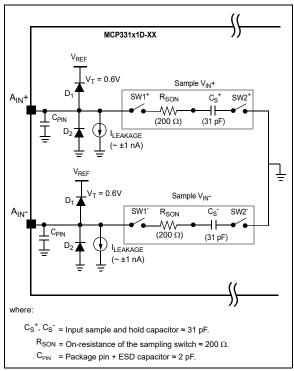

### 6.1 Analog Inputs

Figure 6-1 shows a simplified equivalent circuit of the differential input architecture with a switched capacitor input stage. The input sampling capacitors ( $C_S^+$  and  $C_S^-$ ) are about 31 pF each. The back-to-back diodes ( $D_1 - D_2$ ) at each input are ESD protection diodes. Note that these ESD diodes are tied to V<sub>REF</sub>, so that each input signal can swing from 0V to +V<sub>REF</sub> and from -V<sub>REF</sub> to +V<sub>REF</sub> differentially.

During input acquisition (Standby), the sampling switches are closed and each input sees the sampling capacitor ( $\approx$  31 pF) in series with the on-resistance of the sampling switch, R<sub>SON</sub> ( $\approx$  200 $\Omega$ ).

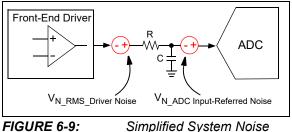

For high-precision data conversion applications, the input voltage needs to be fully settled within 1/2 LSB during the input acquisition period ( $t_{ACQ}$ ). The settling time is directly related to the source impedance: A lower impedance source results in faster input settling time. Although the device can be driven directly with a low impedance source, using a low noise input driver is highly recommended.

### FIGURE 6-1: Simplified Equivalent Analog Input Circuit.

#### 6.1.1 ABSOLUTE MAXIMUM INPUT VOLTAGE RANGE

The input voltage at each input pin (A\_{\rm IN}^+ and A\_{\rm IN}^-) must meet the following absolute maximum input voltage limits:

- $(V_{IN}+, V_{IN}-) < V_{REF} + 0.1V$

- (V<sub>IN</sub>+, V<sub>IN</sub>-) > GND 0.1V

- Note: The ESD diodes at the analog input pins are biased from V<sub>REF</sub>. Any input voltage outside the absolute maximum range can turn on the input ESD protection diodes and results in input leakage current which may cause conversion errors and permanent damage to the device. Care must be taken in setting the input voltage ranges so that the input voltage does not exceed the absolute maximum input voltage range.

### 6.1.2 INPUT VOLTAGE RANGE

The differential input (V\_{IN}) and common-mode voltage (V\_{CM}) at the input pins are defined by:

#### EQUATION 6-1: DIFFERENTIAL INPUT

$$V_{IN} = V_{IN^{+}} - V_{IN^{-}}$$

$$V_{CM} = \frac{V_{IN^{+}} + V_{IN^{-}}}{2}$$