### **Product Change Notification - SYST-03FYTJ911**

Date:

04 Jan 2019

**Product Category:**

**Ethernet Switches**

Affected CPNs:

#### **Notification subject:**

ERRATA - KSZ9563R Silicon Errata and Data Sheet Clarification Errata Document Revision

#### **Notification text:**

SYST-03FYTJ911

Microchip has released a new DeviceDoc for the KSZ9563R Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at KSZ9563R Silicon Errata and Data Sheet Clarification.

**Notification Status:** Final

Description of Change: - Removed module: "PTP messages get dropped in PTP 2-Step Mode" - Added new module 9

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

**Change Implementation Status: Complete**

Date Document Changes Effective: 04 Jan 2019

**NOTE:** Please be advised that this is a change to the document only the product has not been changed...

Markings to Distinguish Revised from Unrevised Devices:N/A

Attachment(s):

KSZ9563R Silicon Errata and Data Sheet Clarification

Please contact your local <u>Microchip sales office</u> with questions or concerns regarding this notification.

#### **Terms and Conditions:**

If you wish to receive Microchip PCNs via email please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to change your PCN profile, including opt out, please go to the PCN home page select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

Affected Catalog Part Numbers (CPN)

KSZ9563RNXC KSZ9563RNXC-TR KSZ9563RNXI KSZ9563RNXI-TR

Date: Thursday, January 03, 2019

# **KSZ9563R**

# KSZ9563R Silicon Errata and Data Sheet Clarification

This document describes known silicon errata for the Microchip KSZ9563R. The silicon errata discussed in this document are for silicon revisions as listed in Table 1. The silicon revision can be determined by the device's top marking. A summary of KSZ9563R silicon errata is provided in Table 2.

#### TABLE 1: AFFECTED SILICON REVISIONS

| Part Number | Silicon Revision |

|-------------|------------------|

| KSZ9563RNX  | B2               |

#### TABLE 2: SILICON ISSUE SUMMARY

| Item<br>Number | Silicon Issue Summary                                                             | Affected Silicon<br>Revisions |

|----------------|-----------------------------------------------------------------------------------|-------------------------------|

| 1.             | When tail tag is enabled, frame length field check fails for 802.3 frames         | B2                            |

| 2.             | Port based priority remapping is not supported                                    | B2                            |

| 3.             | 1000BASE-T PMA-EEE fails to meet the IEEE Refresh Time specification              | B2                            |

| 4.             | 1000BASE-T Master Mode may not link up successfully on the first attempt          | B2                            |

| 5.             | 1000BASE-T Transmit Output Voltage may fail to meet IEEE compliance specification | B2                            |

| 6.             | 1000BASE-T Transmitter Distortion fails to meet IEEE compliance specification     | B2                            |

| 7.             | Transmission halt with late collisions                                            | B2                            |

| 8.             | LEDx_0 in Single-LED Mode does not indicate link activity                         | B2                            |

| 9.             | GPIO_2 does not function properly                                                 | B2                            |

#### Silicon Errata Issues

#### Module 1: When tail tag is enabled, frame length field check fails for 802.3 frames

#### DESCRIPTION

The comparison of the length field of the Ethernet frame with the actual length of the data field portion of the frame fails for the ingress packets with tail tag. This issue is not applicable to packets with the type field in the frame.

#### **END USER IMPLICATIONS**

The packets will be dropped when length check fails for the packet.

#### **Work Around**

Disable the length check in bit 3 of the register 0x0330 (Global Switch MAC Control Register 0). The Microchip provided driver disables the length check.

#### **PLAN**

#### Module 2: Port based priority remapping is not supported

#### DESCRIPTION

The 802.1Q-2014 Clause 6 (6.9.4 Regenerating priority) describes the Priority Regeneration Table for the reception port, which is required to support an AVB boundary port. The boundary port in the AVB domain needs to remap the priority field of the incoming traffic.

Since the device do not support port based priority remapping, the port cannot be used as a boundary port.

This erratum is not applicable if all the device ports are AVB domain ports.

#### **END USER IMPLICATIONS**

The device port cannot be used as an AVB domain boundary port to networks that utilize the scheduler.

#### **Work Around**

A software workaround is available to remap the priority of all the incoming traffic to the port. The workaround uses an ACL (Access Control List) mechanism to remap the priority of the incoming traffic to 0. With the workaround, there is no impact on AVB traffic. If the incoming traffic uses QoS, priorities are also remapped to 0. This may have a minor impact on the QoS traffic (i.e., all the QoS traffic uses one egress queue instead of using the two queues available in the device). The workaround is available in Microchip provided driver software.

Software Workaround:

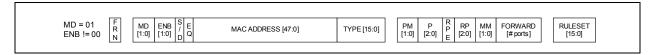

Program the ACL rule to remap all the incoming layer 2 packets to priority 0 (ACL rule format shown in Figure 1).

#### FIGURE 1: ACL RULE FORMAT

#### Rule Description:

MD = 01 : Layer 2

ENB = 10 : Comparison on EtherType value

EQ = 0 & TYPE = 0 : I.e., all packets (condition is when EtherType != 0)

PM = 11 : Always change priority to P[2:0]

P = 0 : Priority value to be changed

#### **PLAN**

#### Module 3: 1000BASE-T PMA-EEE fails to meet the IEEE Refresh Time specification

#### DESCRIPTION

The device's 1000BASE-T Transmit Refresh Time for Waketx time (Full) is approximately 1.47-1.48µs, versus the <1.40µs indicated in the IEEE specification.

#### **END USER IMPLICATIONS**

With the default setting, the Refresh Time is slightly outside the specification, and the transmitter is not fully compliant with the IEEE standard. This may degrade performance with some 1000BASE-T EEE PHY link partners.

#### Work Around

Write to the following MMD register for each PHY port [1-2] to set the Refresh Time to 0.85µs:

| [MMD] | [register] | [data] |

|-------|------------|--------|

| 0x3   | 0xE        | 0x0021 |

#### **PLAN**

This erratum will not be corrected in a future revision.

#### Module 4: 1000BASE-T Master Mode may not link up successfully on the first attempt

#### DESCRIPTION

The device's first 1000BASE-T link-up attempt when in Master Mode may drop link immediately before always linking successfully and maintaining link on the second attempt. This behavior occurs mainly at long cable lengths (~100 meters).

#### **END USER IMPLICATIONS**

When the device operates in 1000BASE-T Master Mode, the system application needs to account for a possible second link-up attempt, especially with long cable.

#### **Work Around**

None.

#### **PLAN**

#### Module 5: 1000BASE-T Transmit Output Voltage may fail to meet IEEE compliance specification

#### **DESCRIPTION**

The device's 1000BASE-T Transmit Output Voltage Template may fail to meet the following IEEE specifications when operating at low voltage (-5% of nominal for AVDDH and core supply voltages) and high temperature (+85°C).

- 1. Percent difference between Points A, B may slightly exceed the <1.0% per the IEEE specification.

- Peak Voltage for Points A, B, C, D, F, H may slightly touch the voltage template defined per the IEEE specification.

#### **END USER IMPLICATIONS**

It is unlikely the marginal specification failures will impact system performance. Extensive testing has been performed to ensure the device can inter-operate with different Gigabit PHY link partners.

#### **Work Around**

None.

#### **PLAN**

#### Module 6: 1000BASE-T Transmitter Distortion fails to meet IEEE compliance specification

#### DESCRIPTION

The device's 1000BASE-T Transmitter Distortion is approximately 40mV, versus the <10mV indicated in the IEEE specification.

#### **END USER IMPLICATIONS**

It is unlikely this specification failure will impact system performance. The following link to the Gigabit Transmit Distortion Testing document on the IEEE802.org website also questions the validity of this measurement:

http://www.ieee802.org/3/axay/public/may\_07/sefidvash\_1\_0507.pdf

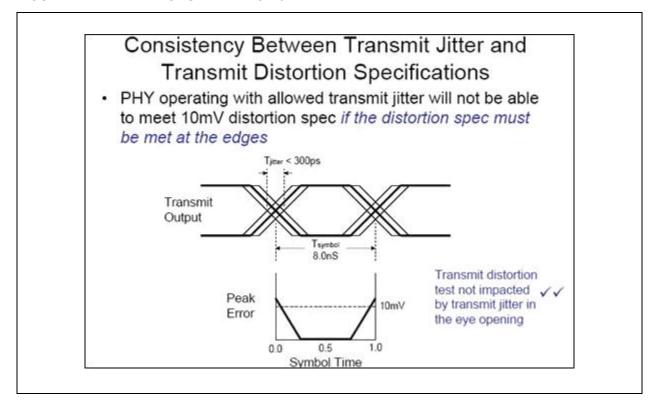

IEEE testing calls for <10mV peak transmitter distortion for at least 60% of the UI within the eye opening. However, this measurement might not be valid, as the transmit distortion test is sensitive to transmit jitter. Refer to the explanation below, taken from the aforementioned IEEE document.

The Gigabit Transmit Distortion Testing document indicates:

• On page 6, a contradiction between Transmit Jitter and Transmit Distortion requirements:

#### FIGURE 2: IEEE DOCUMENT PAGE 6

- · On page 7:

- The transmit distortion test is sensitive to transmit clock jitter during the rise/fall time.

- It is recommended to change the requirement to use at least 30%, instead of at least 60%, of the UI within the eye opening for the <10mV peak transmitter distortion.

#### FIGURE 3: IEEE DOCUMENT PAGE 7

# Defining the "Settled" Interval for Transmit Distortion Testing

- Currently defined transmit distortion test is sensitive to transmit clock jitter during the rise/fall time of the transmitter

- Error voltage will be contaminated by jitter during transitions

- Portion of error contributed by distortion cannot be determined during transitions

- Appropriate place to apply test is after the rise/fall time where the waveform has settled to it's final value

- Clause 40.6.1.2.3 specifies a 5ns rise/fall time (note #3)

- 3ns of 8ns (37.5%) of UI will be free from effects of jitter

- Recommend to use 30% for ease of testing

- le: measure error voltage at 10 phases, require 3 of these measurements to be below 10mW

Extensive testing has been performed to ensure the device can inter-operate with different Gigabit PHY link partners.

#### **Work Around**

None.

#### **PLAN**

#### Module 7: Transmission halt with late collisions

#### DESCRIPTION

Section 4 of the IEEE 802.3 Specification details Carrier Sense Multiple Access / Collision Detection (CSMA/CD) parameters when operating in half-duplex mode. The first 512 bit times are designated as the slotTime, which is the maximum amount of time allowed for a collision to occur. If a link partner is configured incorrectly, where the PHY is linking in half-duplex mode but the MAC is configured in full-duplex mode, there is a chance that the link partner will generate a collision after the first 512 bit times, violating the IEEE 802.3 specification. These late collisions, combined with other factors, can cause the switch port transmitter to lock up and stop sending packets. The receiver will still function.

#### **END USER IMPLICATIONS**

If this erratum occurs, the switch will stop transmitting data to the half-duplex port, making it seem the half-duplex link partner has stopped communicating to the network. The more traffic there is, the greater the risk of the violating link partner generating a late collision that will affect the port.

#### **Work Around**

Ideally, the link partner that is violating the specification would need to be updated so the MAC and PHY are correctly configured to the same duplex setting. If the link partner cannot be modified to conform to the IEEE 802.3 specification, the switch can be re-configured to full-duplex when late collisions are detected to avoid a lock up condition. Of note, each switch port functions independently. Therefore, any work around must be implemented separately for each port.

#### Method 1:

To avoid transmitter lock up, when a port is linked in half-duplex mode, the software should monitor the TxLateCollision MIB counter (MIB Index 0x16). If the number is ever non-zero, the software should force the link to function in full-duplex mode by disabling auto-negotiation and setting full-duplex and the appropriate speed in the PHY Basic Control Registers (addresses 0xN100 - 0xN101).

#### Method 2:

To detect transmitter lock up, the software should monitor the TxByteCnt (MIB Index 0x81) and the RxByteCnt (MIB Index 0x80). If the RxByteCnt is incrementing but the TxByteCnt remains the same, the software should perform a hard reset of the switch.

#### **PLAN**

This erratum will not be corrected in a future revision.

#### Module 8: LEDx\_0 in Single-LED Mode does not indicate link activity

#### DESCRIPTION

The PHY Port (1-2) LEDx 0 does not go low in the presence of link activity when in Single-LED Mode.

#### **END USER IMPLICATIONS**

Link activity cannot be determined in Single-LED Mode. However, LEDx\_1 will indicate if the link is up or down. The lack of status lends to uncertainty that traffic is passing through the port.

#### **Work Around**

No work around exists for Single-LED Mode. Both PHY port LEDs work properly in Tri-Color Dual-LED Mode, which is the default LED mode.

#### **PLAN**

#### Module 9: GPIO\_2 does not function properly

#### **DESCRIPTION**

Pins GPIO\_1 and GPIO\_2 are intended to output programmed signals that are timed to the internal clock. They may also be used for timestamping of input signals. GPIO\_1 functions as intended, but GPIO\_2 does not. GPIO\_2 outputs a 25MHz clock when link is up on either of the two PHY ports, preventing it's use as a GPIO. If a second GPIO output pin is needed, the LED2\_1 pin can be re-assigned for this purpose.

#### **END USER IMPLICATIONS**

GPIO\_2 cannot be used for input timestamping or for outputting programmed signals. The 25MHz clock output on GPIO\_2 cannot be disabled, so it is best to leave the pin unconnected on board designs. LED2\_1 can be assigned to take the place of GPIO\_2 for output functionality, but this displaces the LED functionality of LED2\_1.

There is no alternative for input timestamping on GPIO\_2. Input timestamping is available only on GPIO\_1, not on any other pins.

#### **Work Around**

The output functionality of GPIO\_2 can be routed to LED2\_1 by setting bit 3 in the LED2\_0/LED2\_1 Source Register at address 0x0128 - 0x012B.

No other changes are required. When setting up the trigger output units, any output programmed to go to GPIO\_2 will output on LED2\_1 if the above bit is set. Any of the three trigger units can be used.

#### **PLAN**

## APPENDIX A: DOCUMENT REVISION HISTORY

| Revision Level & Date  | Section/Figure/Entry                                        | Correction                    |

|------------------------|-------------------------------------------------------------|-------------------------------|

| DS80000786C (12-04-18) | Module 9.                                                   | Added new errata.             |

|                        | Module: "PTP messages<br>get dropped in PTP 2-Step<br>Mode" | Removed errata from document. |

| DS80000786B (08-17-18) | Modules 7., 8.                                              | Added new errata.             |

| DS80000786A (04-05-18) | All                                                         | Initial release.              |

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at <a href="www.microchip.com">www.microchip.com</a>. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2018, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 9781522439356

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY

Tel: 631-435-6000 **San Jose, CA** Tel: 408-735-9110

Tel: 408-436-4270 **Canada - Toronto**Tel: 905-695-1980

Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan

Tel: 86-27-5980-5300 China - Xian

Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770

**Korea - Daegu** Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok

Tel: 66-2-694-1351 Vietnam - Ho Chi Minh

Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820