### MAX15157D

## 60V Current-Mode Buck Controller with Lossless Current Sense

### **General Description**

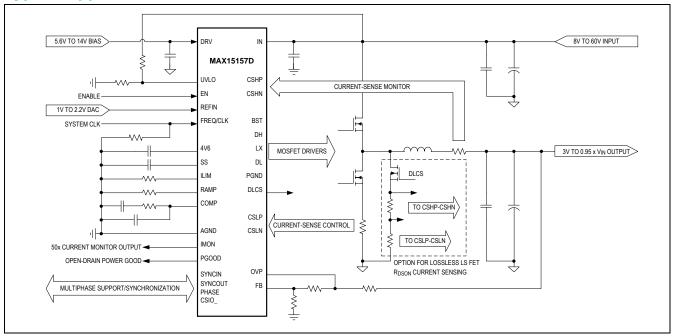

The MAX15157D is the evolution of the MAX15157B HV buck controller family. The MAX15157D implements a single-phase, PWM valley current-mode controller and drives two external power MOSFETs in a buck configuration. The output voltage can be dynamically set through the 1V to 2.2V reference input (REFIN) for modular design support.

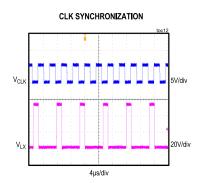

The switching frequency is controlled either through external resistor that sets the internal oscillator, or by synchronizing the regulator to an external clock. The device is designed to support 60kHz to 1MHz switching frequencies. The controller has a dedicated undervoltage lockout pin (UVLO) and an accurate enable input threshold for flexible power sequence configuration. The controller also has multiple fault-protection circuits to protect against overcurrent (OCP) adjustable through the ILIM pin, output overvoltage (OVP), input undervoltage (UVLO), and thermal shutdown.

The MAX15157D features an adjustable internal compensation ramp. The device incorporates an accurate current-sense amplifier that reports output current through an analog output (IMON).

The MAX15157D features lossless LS FET R<sub>DSON</sub> or resistor current sensing. The device allows programmable single-phase or multiphase operation, up to eight interleaved phases, and implements an accurate current balance scheme. The MAX15157D can operate with either discrete inductors or coupled inductors in case of multiphase operation.

The device is available in a 5mm  $\times$  5mm, 32-pin TQFN package and supports a -40°C to +125°C junction temperature range.

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- Wide Operating Range Reduces Development Time

- 8V to 60V Input Voltage Range

- 3V to 0.95 x V<sub>IN</sub> Output Voltage Range

- · 60kHz to 1MHz Switching Frequency Range

- Interleaved 1/2/3/4/6/8-Phase Operation

- -40°C to +125°C Temperature Range

- Integration Reduces Design Footprint

- · Internal LDO for Bias Supply Generation

- · Synchronization Input

- · Current Monitor Output

- · Internal 2V Precision Reference

- $2\Omega$  Pullup and  $0.6\Omega$  Pulldown Fast Power FET Drivers

- Accurate MOSFET Dead Time Adaptive Control

- Robust Fault Protection Improves Quality and Simplifies System Design

- · Adjustable Input Undervoltage Lockout

- Adjustable Input EN

- Adjustable Cycle-by-Cycle Overcurrent Protection

- Input Undervoltage Fault Protection

- Multiple Levels of Overvoltage Protection

- Thermal Shutdown

- Flexible, Simple System Design

- Adjustable Slope Compensation

- Discrete Inductor or Compact Coupled Inductor Architecture

- Lossless R<sub>DSON</sub> or Resistor Current Sensing

- Small 5mm × 5mm, 32-Pin TQFN, 0.5mm Pitch

## **Applications**

- Datacenter

- Industrial

- Automotive

- Multiphase Buck

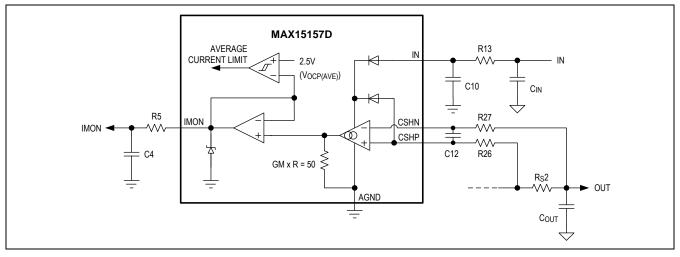

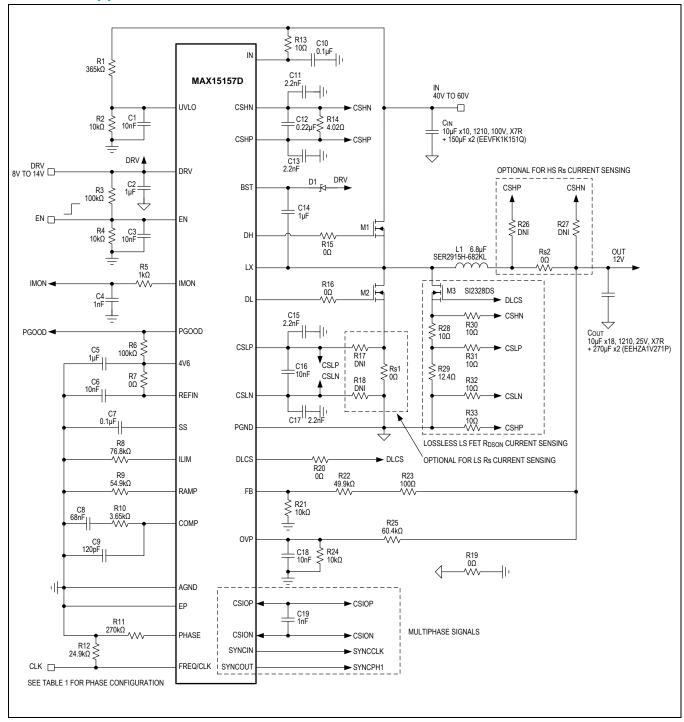

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| IN to PGND                | 0.3V to +65V                      |

|---------------------------|-----------------------------------|

| CSLP, CSLN to PGND        | -0.3V to +0.3V                    |

| CSLP to CSLN              | -0.3V to +0.3V                    |

| CSHP, CSHN to PGND        | 0.3V to +76V                      |

| CSHP to CSHN              | -0.3V to +0.3V                    |

| LX to PGND                | -1V to +76V                       |

| LX + DRV                  |                                   |

| LX to PGND less than 50ns | 2V                                |

| BST to PGND               | 0.3V to +80V                      |

| BST to LX                 | 0.3V to +16V                      |

| DH to LX                  | 0.3V to (V <sub>BST</sub> + 0.3V) |

| DL, DLCS to PGND          | 0.3V to (V <sub>DRV</sub> + 0.3V) |

| DRV to PGND               | -0.3V to +16V                     |

| 4V6 to AGND               | -0.3V to +6V                      |

| DRV to 4V6                | -0.3V to +16V                     |

|                           |                                   |

| EN, FB, PGOOD, REFIN to AGND0.3V to +6\                     |

|-------------------------------------------------------------|

| UVLO, OVP, FREQ/CLK, SYNCIN to AGND0.3V to +6\              |

| COMP, SS, IMON, RAMP to AGND0.3V to (V $_{ m 4V6}$ + 0.3V   |

| SYNCOUT, PHASE, ILIM to AGND0.3V to (V $_{4V6}$ + 0.3V      |

| CSION, CSIOP to AGND0.3V to (V $_{4V6}$ + 0.3V              |

| PGND to AGND0.3V to +0.3V                                   |

| Maximum Current out of 4V6 100m/                            |

| Operating Temperature Range40°C to +125°C                   |

| Continuous Power Dissipation ( $T_A = +70$ °C) TQFN (derate |

| 34.5mW/°C above +70°C)                                      |

| Junction Temperature+150°C                                  |

| Storage Temperature Range40°C to +150°C                     |

| Lead Temperature (soldering, 10s)+300°C                     |

| Soldering Temperature (reflow)+240°C                        |

|                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

| Package Code                           | T3255+4        |  |  |  |  |  |

|----------------------------------------|----------------|--|--|--|--|--|

| Outline Number                         | <u>21-0140</u> |  |  |  |  |  |

| Land Pattern Number                    | 90-0012        |  |  |  |  |  |

| Thermal Resistance, Four-Layer Board   |                |  |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | +29°C/W        |  |  |  |  |  |

| Junction to Case $(\theta_{JC})$       | +1.7°C/W       |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="http://www.maximintegrated.com/packages">http://www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://www.maximintegrated.com/thermal-tutorial">http://www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{IN}=35\text{V}, V_{DRV}=9\text{V}, V_{EN}=3.3\text{V}, V_{UVLO}=3.3\text{V}, \text{OVP}=0\text{V}, \text{REFIN}=4\text{V6}, \text{R}_{FREQ}=100\text{k}\Omega \text{ (600kHz)}, \text{C}_{4\text{V6}}=4.7\mu\text{F}, \text{C}_{SS}=10\text{nF}, \text{C}_{A}=10\text{N}$

| PARAMETER                   | SYMBOL                 | CONDITIONS                                              | MIN   | TYP   | MAX   | UNITS |

|-----------------------------|------------------------|---------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUPPLIES              |                        |                                                         |       |       |       |       |

| IN Operating Range          | V <sub>IN</sub>        |                                                         | 8     |       | 60    | V     |

| DRV Operating Range         | $V_{DRV}$              |                                                         | 5.6   |       | 14    | V     |

| IN Quiescent Current        | I <sub>IN</sub>        | Not switching, including current-reporting bias current |       | 504   | 950   | μA    |

| IN Shutdown Current         | I <sub>IN(SHDN)</sub>  | EN = AGND                                               |       | 2.8   | 8.0   | μA    |

| DRV Quiescent Current       | I <sub>DRV</sub>       | Not switching                                           |       | 4.8   | 8.0   | mA    |

| DRV Shutdown Current        |                        | EN = AGND                                               |       | 16    | 35    | μΑ    |

|                             |                        | V <sub>IN</sub> rising, single phase                    | 5.04  | 5.2   | 5.35  |       |

| IN Undervoltage-            | .,                     | V <sub>IN</sub> falling, single phase                   | 4.85  | 5     | 5.2   | V     |

| Lockout Threshold           | V <sub>IN(UVLO)</sub>  | V <sub>IN</sub> rising, multiphase                      | 7.3   | 7.5   | 7.7   |       |

|                             |                        | V <sub>IN</sub> falling, multiphase                     | 7.05  | 7.25  | 7.45  |       |

| DRV Undervoltage-           | V                      | V <sub>DRV</sub> rising                                 | 4.9   | 5.06  | 5.22  | V     |

| Lockout Threshold VDRV(UV   |                        | V <sub>DRV</sub> falling                                | 4.8   | 4.97  | 5.1   | V     |

| 4V6 BIAS LINEAR REGU        | JLATOR                 |                                                         |       |       |       |       |

| Bias LDO Output<br>Voltage  | V <sub>4V6</sub>       | No load                                                 | 4.42  | 4.5   | 4.56  | V     |

| Bias LDO Current Limit      |                        |                                                         | 33    | 51    | 75    | mA    |

| 4V6 Undervoltage-           | V                      | V <sub>4V6</sub> rising                                 | 4.12  | 4.25  | 4.38  | V     |

| Lockout Threshold           | V <sub>4V6(UVLO)</sub> | V <sub>4V6</sub> falling                                | 4.08  | 4.2   | 4.3   | V     |

| CONTROLLER ENABLE           |                        |                                                         |       |       |       |       |

| ENT. C. Thomas at a         | .,                     | EN rising                                               | 0.67  | 0.7   | 0.74  |       |

| EN Logic Threshold          | V <sub>EN</sub>        | EN falling, after LDO in regulation                     | 0.51  | 0.54  | 0.58  | V     |

| EN Input-Leakage<br>Current | I <sub>EN</sub>        | V <sub>EN</sub> = 0 to 5V                               | -1    |       | +1    | μΑ    |

|                             | V <sub>UVLO</sub>      | V <sub>UVLO</sub> rising                                | 0.965 | 1.000 | 1.035 | V     |

$(V_{IN}=35V, V_{DRV}=9V, V_{EN}=3.3V, V_{UVLO}=3.3V, OVP=0V, REFIN=4V6, R_{FREQ}=100k\Omega \ (600kHz), C_{4V6}=4.7\mu F, C_{SS}=10nF, C_{AVS}=100k\Omega \ (600kHz), C_{AVS}=100k\Omega \ (6$

| PARAMETER                                                              | SYMBOL                       | CONDITIONS                                                             | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------|-------|-------|-------|-------|

| UVLO Adjustable<br>Undervoltage-Lockout<br>Threshold                   |                              | V <sub>UVLO</sub> falling                                              | 0.865 | 0.900 | 0.935 |       |

| UVLO Input-Leakage<br>Current                                          | I <sub>UVLO</sub>            | V <sub>UVLO</sub> = 0 to 4.6V                                          | -200  |       | +200  | nA    |

| UVLO Deglitch Time                                                     |                              |                                                                        |       | 20    | 35    | μs    |

| CONTROL LOOP                                                           |                              | 1                                                                      | L     |       |       |       |

| FB Regulation                                                          |                              | REFIN = 4V6                                                            | 1.98  | 2.00  | 2.02  |       |

| Threshold (Preset<br>Mode)                                             | $V_{FB}$                     | REFIN = 4V6, T <sub>J</sub> = +25°C                                    | 1.996 | 2.000 | 2.004 | V     |

| FB-to-REFIN Offset<br>Voltage (Tracking<br>Mode)                       |                              | V <sub>FB</sub> - V <sub>REFIN</sub> , V <sub>REFIN</sub> = 1V to 2.2V | -4.5  |       | +4.5  | mV    |

| REFIN Input-Voltage<br>Range                                           | V <sub>REFIN</sub>           | (Note 2)                                                               | 1     |       | 2.2   | V     |

| Preset Mode REFIN                                                      |                              | REFIN rising                                                           | 2.33  | 2.36  | 2.4   |       |

| Threshold                                                              |                              | REFIN falling                                                          | 2.22  | 2.26  | 2.29  | V     |

| FB Input-Leakage<br>Current                                            | I <sub>FB</sub>              | V <sub>FB</sub> = 0 to 2.2V                                            | -200  |       | +200  | nA    |

| REFIN Input-Leakage<br>Current                                         | I <sub>REFIN</sub>           | V <sub>REFIN</sub> = 1V to 2.2V                                        | -100  |       | +100  | nA    |

| Low-Side Current-<br>Sense Differential<br>Voltage Range               | $\Delta V_{	extsf{CSL}_{-}}$ | V <sub>CSLP</sub> - V <sub>CSLN</sub>                                  |       | ±200  |       | mV    |

| Low-Side Current-<br>Sense Common-Mode<br>Voltage Range                | V <sub>CSL</sub> _           | With respect to AGND                                                   |       | ±300  |       | mV    |

| CSL_ Input-Leakage<br>Current                                          | I <sub>CSL_</sub>            |                                                                        | -0.8  |       | +0.8  | μΑ    |

| CSL_ Current-Sense<br>Amplifier Gain                                   | A <sub>CSL</sub>             |                                                                        |       | 4.2   |       | V/V   |

| Error-Amplifier<br>Transconductance                                    | G <sub>MEA</sub>             |                                                                        | 0.83  | 1.1   | 1.4   | mS    |

| Internal Slope-<br>Compensation Ramp-<br>Amplitude Adjustable<br>Range | $V_{RAMP}$                   |                                                                        | 380   |       | 1200  | mV    |

| RAMP Pin Input-Voltage<br>Range                                        | V <sub>RAMP_PIN</sub>        |                                                                        | 120   |       | 380   | mV    |

| V <sub>RAMP</sub> -to-V <sub>RAMP</sub> PIN<br>Ratio                   |                              | V <sub>RAMP_PIN</sub> = 0.3V                                           |       | 3.18  |       | V/V   |

| RAMP Bias Current                                                      | I <sub>RAMP</sub>            | V <sub>RAMP_PIN</sub> = 0V                                             | 5.4   | 6.0   | 6.6   | μA    |

| SWITCHING FREQUENC                                                     |                              |                                                                        | •     |       |       | •     |

| Preset Switching<br>Frequency                                          | f <sub>SW</sub>              | R <sub>FREQ</sub> = open, R <sub>PHASE</sub> = 270kΩ                   | 293   | 300   | 307   | kHz   |

| Adjustable Switching                                                   | f <sub>SW</sub>              | $R_{FREQ} = 10k\Omega$ , $R_{PHASE} = 270k\Omega$                      | 48    | 56    | 68    | kHz   |

| Frequency                                                              | 3**                          | $R_{FREQ} = 25k\Omega$ , $R_{PHASE} = 270k\Omega$                      | 135   | 145   | 156   |       |

$(V_{IN}=35\text{V}, V_{DRV}=9\text{V}, V_{EN}=3.3\text{V}, V_{UVLO}=3.3\text{V}, \text{OVP}=0\text{V}, \text{REFIN}=4\text{V6}, \text{R}_{FREQ}=100\text{k}\Omega \text{ (600kHz)}, \text{C}_{4\text{V6}}=4.7\mu\text{F}, \text{C}_{SS}=10\text{nF}, \text{C}_{AVG}=4.7\mu\text{F}, \text$

| PARAMETER SYMBOL CONDITIONS                                  |                                         |                                                                                                                           | MIN       | TYP    | MAX  | UNITS                                 |

|--------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|---------------------------------------|

|                                                              |                                         | $R_{FREQ}$ = 100kΩ, $R_{PHASE}$ = 270kΩ                                                                                   | 550       | 592    | 642  |                                       |

| Synchronization Range                                        | f <sub>SW</sub>                         | FREQ/CLK driven by external clock                                                                                         | 60        |        | 1000 | kHz                                   |

| CLK Frequency-<br>Detection Range                            | f <sub>CLK</sub>                        |                                                                                                                           | 0.12      |        | 6.00 | MHz                                   |

| LK Logic Level V <sub>CLK</sub>                              |                                         | Logic-high (rising)                                                                                                       |           | 1.8    | 1.9  | V                                     |

| CLN Logic Level                                              | V CLK                                   | Logic-low (falling)                                                                                                       | 1.52      | 1.6    |      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| FREQ/CLK Input Bias<br>Current                               | ICLK                                    | V <sub>FREQ/CLK</sub> = AGND                                                                                              | -10.5     | -9.8   | -9.2 | μA                                    |

|                                                              |                                         | R <sub>PHASE</sub> = 270kΩ (1 phase)                                                                                      |           | 2      |      |                                       |

| CLK Switching                                                |                                         | R <sub>PHASE</sub> = 133kΩ (2 phases)                                                                                     |           | 2      |      | Ī "                                   |

| Frequency-Divider Ratio                                      | f <sub>CLK</sub> /f <sub>SW</sub>       | $R_{PHASE}$ = 169kΩ (3, 6 phases)                                                                                         |           | 6      |      | kHz/kHz                               |

|                                                              |                                         | $R_{\text{PHASE}} = 210$ kΩ (4, 8 phases)                                                                                 |           | 4      |      |                                       |

| SYNCHRONIZATION AN                                           | ID PHASE                                | TYPHASE 2 TOTAL (1, 0 phases)                                                                                             |           | •      |      |                                       |

| SYNCOUT Output-                                              | V <sub>SYNCOUT</sub> - V <sub>4V6</sub> | Logic-high, I <sub>SOURCE</sub> = 10mA                                                                                    | 4V6 - 0.4 |        |      | V                                     |

| Voltage Level                                                | V <sub>SYNCOUT</sub>                    | Logic-low, I <sub>SINK</sub> = 10mA                                                                                       |           |        | 0.4  | 1                                     |

| PHASE Source Current                                         | I <sub>PHASE</sub>                      |                                                                                                                           | 9.2       | 10     | 10.8 | μA                                    |

| OUTPUT-FAULT PROTE                                           |                                         | 1                                                                                                                         |           |        |      | 1                                     |

| ILIM Bias Current                                            | I <sub>ILIM</sub>                       | ILIM = 0.615V                                                                                                             | 8.8       | 9.8    | 10.8 | μA                                    |

| ILIM Voltage Range                                           | V <sub>ILIM</sub>                       |                                                                                                                           | 0.35      |        | 1.95 | ·                                     |

| ILIM to CSLP-CSLN<br>Voltage Ratio                           | ILIIVI                                  | ILIM = 0.615V, low-side FET ON, cycle-<br>by-cycle  40mV  typ. threshold                                                  |           | 15.375 |      | V/V                                   |

| CSLP-CSLN Cycle-by-<br>Cycle Current-Limit<br>Threshold      |                                         | Low-side FET ON,  ADJ range                                                                                               | 21        |        | 124  | mV                                    |

| CSLP-CSLN Hiccup<br>Current-Limit Threshold                  |                                         | Low-side FET ON,  ADJ range                                                                                               | 31.5      |        | 186  | mV                                    |

| CSLP-CSLN POCP<br>Cycle-by-Cycle Current-<br>Limit Threshold |                                         | Low-side FET ON, ILIM = BIAS                                                                                              | -43       | -40    | -37  | mV                                    |

| CSLP-CSLN NOCP<br>Cycle-by-Cycle Current-<br>Limit Threshold |                                         | Low-side FET ON, ILIM = BIAS                                                                                              | 30        | 40     | 50   | mV                                    |

| CSLP-CSLN POCP<br>Hiccup Current-Limit<br>Threshold          |                                         | Low-side FET ON, ILIM = BIAS                                                                                              | -69       | -60    | -50  | mV                                    |

| CSLP-CSLN NOCP Hiccup Current-Limit Threshold                |                                         | Low-side FET ON, ILIM = BIAS                                                                                              | 50        | 60     | 69   | mV                                    |

| Minimum REFIN and SS<br>Voltage for Valid FB<br>Faults       |                                         | REFIN = SS, 80mV hysteresis                                                                                               | 0.998     | 1.02   | 1.03 | V                                     |

| FB Undervoltage<br>Threshold (Preset<br>Mode)                | FB_UV                                   | Measured with respect to target voltage (REFIN = 4V6 and V <sub>REFIN</sub> = 2V), V <sub>FB</sub> falling, 3% hysteresis | -8        | -9     | -10  | %                                     |

$(V_{IN}=35\text{V}, V_{DRV}=9\text{V}, V_{EN}=3.3\text{V}, V_{UVLO}=3.3\text{V}, \text{OVP}=0\text{V}, \text{REFIN}=4\text{V6}, \text{R}_{FREQ}=100\text{k}\Omega \text{ (600kHz)}, \text{C}_{4\text{V6}}=4.7\mu\text{F}, \text{C}_{SS}=10\text{nF}, \text{C}_{AVG}=4.7\mu\text{F}, \text$

| with respect to target voltage 1.2V), V <sub>FB</sub> falling, 3%  with respect to target voltage 4V6 and V <sub>REFIN</sub> = 2V), V <sub>FB</sub> hysteresis with respect to target voltage 1.2V), V <sub>FB</sub> falling, 3%  g ng to 4.6V  ang, 2.9V hysteresis g edge | -8<br>+8<br>+8<br>1.96<br>1.87<br>-200                                                    | -9<br>+9<br>+9<br>2.00<br>1.90                                              | -10<br>+10<br>+10<br>2.04<br>1.94                                                                                               | %<br>%<br>V                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4V6 and V <sub>REFIN</sub> = 2V), V <sub>FB</sub> hysteresis with respect to target voltage 1.2V), V <sub>FB</sub> falling, 3%  g ng to 4.6V  ling, 2.9V hysteresis g edge                                                                                                  | +8<br>1.96<br>1.87<br>-200                                                                | +9<br>2.00                                                                  | +10<br>2.04<br>1.94                                                                                                             | %                                                                                                                                                  |

| 1.2V), V <sub>FB</sub> falling, 3% g ng to 4.6V ing, 2.9V hysteresis                                                                                                                                                                                                        | 1.96<br>1.87<br>-200                                                                      | 2.00                                                                        | 2.04                                                                                                                            |                                                                                                                                                    |

| to 4.6V<br>ing, 2.9V hysteresis                                                                                                                                                                                                                                             | 1.87                                                                                      |                                                                             | 1.94                                                                                                                            | - V                                                                                                                                                |

| to 4.6V<br>ing, 2.9V hysteresis                                                                                                                                                                                                                                             | -200                                                                                      | 1.90                                                                        |                                                                                                                                 | 7 v                                                                                                                                                |

| ing, 2.9V hysteresis                                                                                                                                                                                                                                                        |                                                                                           |                                                                             | _                                                                                                                               | 1                                                                                                                                                  |

| g edge                                                                                                                                                                                                                                                                      | 63.5                                                                                      |                                                                             | +200                                                                                                                            | nA                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                           | 65.4                                                                        | 67.5                                                                                                                            | V                                                                                                                                                  |

| ı odao                                                                                                                                                                                                                                                                      |                                                                                           | 34                                                                          |                                                                                                                                 | lie.                                                                                                                                               |

| ı edge                                                                                                                                                                                                                                                                      |                                                                                           | 20                                                                          |                                                                                                                                 | μs                                                                                                                                                 |

| ve cycle-by-cycle CSL_<br>it events                                                                                                                                                                                                                                         |                                                                                           | 4                                                                           |                                                                                                                                 | cycles                                                                                                                                             |

| ), EXT OVLO                                                                                                                                                                                                                                                                 |                                                                                           | 28                                                                          |                                                                                                                                 | μs                                                                                                                                                 |

| rage OCP                                                                                                                                                                                                                                                                    |                                                                                           | 32                                                                          |                                                                                                                                 | cycles                                                                                                                                             |

| B_UV                                                                                                                                                                                                                                                                        |                                                                                           | 32                                                                          |                                                                                                                                 | CLK<br>cycles                                                                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                           | 64                                                                          |                                                                                                                                 | CLK<br>cycles                                                                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                           | 38                                                                          | 85                                                                                                                              | mV                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                           |                                                                             | 2                                                                                                                               | μA                                                                                                                                                 |

| eresis                                                                                                                                                                                                                                                                      |                                                                                           | 165                                                                         |                                                                                                                                 | °C                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                           |                                                                             |                                                                                                                                 | _                                                                                                                                                  |

|                                                                                                                                                                                                                                                                             | 4.8                                                                                       | 5.0                                                                         | 5.2                                                                                                                             | μA                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             | -5.5                                                                                      | -5.0                                                                        | -4.2                                                                                                                            | μΑ                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                           | 5                                                                           |                                                                                                                                 | Ω                                                                                                                                                  |

| PWM enabled                                                                                                                                                                                                                                                                 | 41                                                                                        | 50                                                                          | 59                                                                                                                              | mV                                                                                                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                           | 32,768                                                                      |                                                                                                                                 | CLK<br>cycles                                                                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                           |                                                                             |                                                                                                                                 |                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                           | 2                                                                           |                                                                                                                                 |                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                           | 0.6                                                                         |                                                                                                                                 | Ω                                                                                                                                                  |

|                                                                                                                                                                                                                                                                             |                                                                                           | 6                                                                           |                                                                                                                                 |                                                                                                                                                    |

|                                                                                                                                                                                                                                                                             |                                                                                           |                                                                             |                                                                                                                                 | _ ^                                                                                                                                                |

|                                                                                                                                                                                                                                                                             |                                                                                           | 1.8                                                                         |                                                                                                                                 | Ω                                                                                                                                                  |

|                                                                                                                                                                                                                                                                             | D, EXT OVLO rage OCP  B_UV  nA  IN (PGOOD in high-impedance GOOD = 5V eresis  PWM enabled | rage OCP  B_UV  nA  IN (PGOOD in high-impedance GOOD = 5V eresis  4.8  -5.5 | rage OCP 32  B_UV 32  64  nA 38  IN (PGOOD in high-impedance GOOD = 5V eresis 165  4.8 5.0 -5.5 -5.0  PWM enabled 41 50  32,768 | rage OCP 32  B_UV 32  64  nA 38 85  IN (PGOOD in high-impedance GOOD = 5V eresis 165  4.8 5.0 5.2  -5.5 -5.0 -4.2  5  PWM enabled 41 50 59  32,768 |

$(V_{IN}=35\text{V}, V_{DRV}=9\text{V}, V_{EN}=3.3\text{V}, V_{UVLO}=3.3\text{V}, \text{OVP}=0\text{V}, \text{REFIN}=4\text{V6}, R_{FREQ}=100\text{k}\Omega \text{ (600kHz)}, C_{4\text{V6}}=4.7\mu\text{F}, C_{SS}=10\text{nF}, C_{SS}=$

| PARAMETER                                                        | SYMBOL                | COND                                   | MIN                        | TYP  | MAX  | UNITS |     |

|------------------------------------------------------------------|-----------------------|----------------------------------------|----------------------------|------|------|-------|-----|

| DL Minimum On-Time                                               | t <sub>DL</sub>       | (Note 3)                               |                            |      | 72   |       | ns  |

| Driver Rise Time                                                 |                       | C <sub>LOAD</sub> = 3nF                |                            |      | 20   |       | ns  |

| Driver Fall Time                                                 |                       | C <sub>LOAD</sub> = 3nF                |                            |      | 10   |       | ns  |

| DH-to-DL Dead-Time<br>Delay                                      |                       | C <sub>LOAD</sub> = 3nF                |                            |      | 20   |       | ns  |

| DL-to-DH Dead-Time<br>Delay                                      |                       | C <sub>LOAD</sub> = 3nF                |                            |      | 20   |       | ns  |

| DL to DLCS Delay                                                 |                       |                                        |                            |      | 40   |       | ns  |

| BST-to-LX Operating Range                                        | V <sub>BST</sub>      |                                        |                            | 4.5  |      | 14    | V   |

| BST Quiescent Current                                            | I <sub>BST</sub>      | EN = AGND, LX = P                      | GND, V <sub>BST</sub> = 9V |      | 35   | 55    | μA  |

| CURRENT MONITOR                                                  |                       | •                                      |                            |      |      |       |     |

| CSH_ High-Side<br>Current-Sense<br>Common-Mode Voltage<br>Range  | V <sub>CSH</sub>      | With respect to AGN                    | ID                         | 0    |      | 60    | V   |

| CSH_ High-Side<br>Current-Sense<br>Differential Voltage<br>Range | ΔV <sub>CSH</sub> _   | Current-monitor rang                   | 0                          |      | 50   | mV    |     |

| CSHP Input Bias                                                  |                       | V <sub>CSHP</sub> = 60V                |                            |      | 72   | 120   |     |

| Current                                                          | I <sub>CSHP</sub>     | V <sub>CSHP</sub> = 0V                 |                            |      | 136  | 260   | μA  |

| CSHN Input Bias                                                  |                       | V <sub>CSHN</sub> = 60V                |                            |      | 52   | 95    |     |

| Current                                                          | ICSHN                 | V <sub>CSHN</sub> = 0V                 |                            |      | 144  | 260   | μΑ  |

| Current-Monitor<br>Amplifier Gain                                | A <sub>CSH</sub> _    | V <sub>IMON</sub> /ΔV <sub>CSH</sub> _ |                            |      | 50   |       | V/V |

| Current-Monitor<br>Amplifier Accuracy                            | V <sub>IMON</sub>     | V <sub>CSH</sub> _ = 48V               | ΔV <sub>CSH</sub> _ = 30mV | 1.41 | 1.50 | 1.63  | V   |

| IMON Average Current-<br>Limit Threshold                         | V <sub>OCP(AVE)</sub> |                                        |                            | 2.45 | 2.50 | 2.55  | V   |

| IMON Amplifier Output<br>Capacitive Load<br>Stability            | C <sub>IMON</sub>     | No sustained oscilla                   | tions                      |      | 200  |       | pF  |

Note 1: Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.

Note 2: Operating REFIN below 1V is not recommended due to disabled fault protection.

Note 3: Not tested, guaranteed by design.

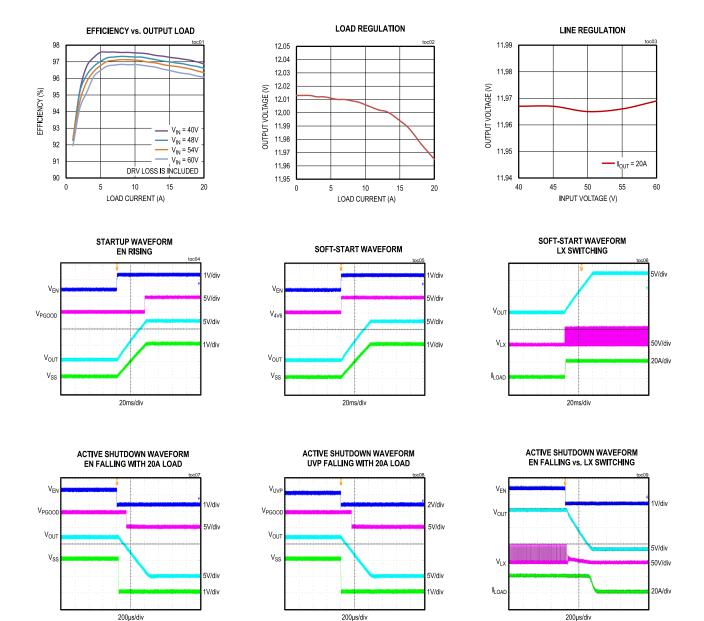

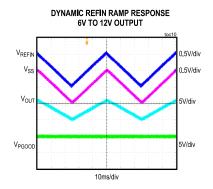

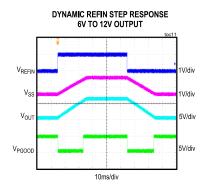

## **Typical Operating Characteristics**

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN} = 54V, V_{OUT} = 12V, unless otherwise noted. See the <u>Standard Application Circuit.</u>)$

(T<sub>A</sub> = -40°C to +125°C, V<sub>IN</sub> = 54V, V<sub>OUT</sub> = 12V, unless otherwise noted. See the <u>Standard Application Circuit.</u>)

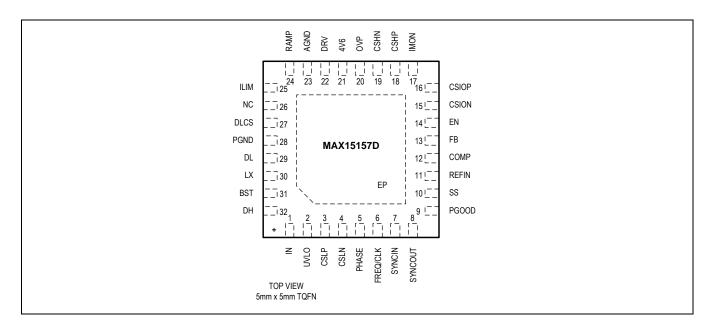

## **Pin Configurations**

## **Pin Descriptions**

| PIN | NAME         | FUNCTION                                                                                                                                                                                                     |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |              | Primary Input Supply. Connect IN to the 8V to 60V high-voltage system supply used to deliver power to                                                                                                        |

| 1   | IN           | the step-down power stage. IN serves as the system supply for the current-monitor amplifier and                                                                                                              |

|     |              | provides input undervoltage sensing.                                                                                                                                                                         |

| 2   | UVLO         | Adjustable Undervoltage-Lockout Input. When the UVLO voltage is below 0.9V, the device disables the controller. Connect UVLO to the center of a resistive-divider between the input and ground to adjust the |

| 2   | UVLO         | undervoltage-lockout voltage, as shown in the <u>Standard Application Circuit</u> .                                                                                                                          |

|     |              | Positive Low-Side Differential Current-Sense Input. The device uses the CSL_ differential current-sense                                                                                                      |

| 3   | CSLP         | signal in the current-mode control loop. See the <u>Standard Application Circuit</u> for CSLP connection.                                                                                                    |

|     |              | Negative Low-Side Differential Current-Sense Input. The device uses the CSL_ differential current-sense                                                                                                      |

| 4   | CSLN         | signal in the current-mode control loop. See the <u>Standard Application Circuit</u> for CSLN connection.                                                                                                    |

|     |              | Synchronized Phase Selection. Connect to the 4V6 for single-phase operating or refer to <u>Table 1</u> for                                                                                                   |

| 5   | PHASE        | multiphase settings.                                                                                                                                                                                         |

|     |              | Frequency Selection/Clock Synchronization Input. The device supports switching frequencies between                                                                                                           |

|     | EDE 0/01     | 60kHz to 1MHz. Set the switching frequency by either selecting the appropriate external resistor to use                                                                                                      |

| 6   | FREQ/CL<br>K | the internal oscillator frequency, or by synchronizing the regulator to an external system clock (see <u>Table</u>                                                                                           |

|     | r.           | 1). Leave FREQ/CLK unconnected to select the preset 300kHz switching frequency. For multiphase                                                                                                               |

|     |              | applications, FREQ/CLK serves as the master clock input.                                                                                                                                                     |

|     |              | Synchronization Input/Clock Output for Multiphase Configurations. Connect SYNCIN to the SYNCOUT                                                                                                              |

| 7   | SYNCIN       | signal of the previous phase for multiphase synchronization. For the master phase, SYNCIN serves as                                                                                                          |

| ,   | OTIVOIN      | the master clock output and should be connected to the FREQ/CLK input of all the power-stage phases                                                                                                          |

|     |              | (see <u>Figure 5</u> ).                                                                                                                                                                                      |

| 8   | SYNCOUT      | Multiphase Synchronization Output. Connect to the next phase when used in multiphase configurations                                                                                                          |

|     |              | (see <u>Figure 5</u> ). For single-phase operation, leave SYNCOUT unconnected.                                                                                                                               |

|     |              | Open-Drain Power-Good Output. The device pulls PGOOD low when the output voltage exceeds the                                                                                                                 |

| 9   | PGOOD        | OVP threshold, or below the output undervoltage-protection threshold, during soft-start and shutdown                                                                                                         |

|     |              | (EN pulled low). The PGOOD output goes high impedance when the controller completes soft-start and                                                                                                           |

|     |              | remains in regulation.                                                                                                                                                                                       |

|    |       | In multiphase operation, the PGOOD output of the slave ICs is always pulled low; do not tie the PGOOD output of the slave ICs and master IC together. Use the PGOOD output of the master IC for the system sequencing, if needed.                                                                                              |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | SS    | Soft-Start Control. The capacitance (C <sub>SS</sub> ) between SS and AGND sets the startup period. An internal pulldown MOSFET holds SS low until the controller begins the startup sequence.                                                                                                                                 |

| 11 | REFIN | External Reference Input. REFIN sets the feedback regulation voltage when supplied with a voltage between 0.4V and 2.2V. Operation between 0.4V < REFIN < 1V is possible, but the FB_OV and FB_UV fault functions are disabled.                                                                                                |

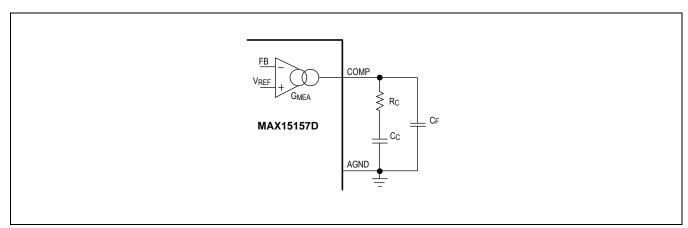

| 12 | COMP  | Compensation Amplifier Output. COMP is the output of the internal transconductance error amplifier.  Connect a type-II compensation network, as shown in <i>Figure 2</i> .                                                                                                                                                     |

| 13 | FB    | Feedback Input. Connect FB to the center of a resistive-divider between the output and AGND. FB regulates to the preset 2V feedback threshold (REFIN = 4V6), or tracks the REFIN voltage (REFIN between 0.4V and 2.2V). Operation between 0.4V < REFIN < 1V is possible, but the FB_OV and FB_UV fault functions are disabled. |

| 14 | EN    | Enable Control Input. Pull EN below 0.54V to place the device into its low-power shutdown state.  When disabled, the controller pulls PGOOD low, pulls all the driver outputs low, and turns off the bias regulator.                                                                                                           |

| 15 | CSION | Negative Input of Multiphase Current-Sense Signal. The device uses a differential current-sense signal to ensure proper startup and current-balance behavior in multiphase configurations.                                                                                                                                     |

| 16 | CSIOP | Positive Input of Multiphase Current-Sense Signal. The device uses a differential current-sense signal to ensure proper startup and current-balance behavior in multiphase configurations.                                                                                                                                     |

| 17 | IMON  | High-Side Current-Sense Amplifier Output. IMON amplifies the voltage sensed from CSHP to CSHN.                                                                                                                                                                                                                                 |

| 18 | CSHP  | Positive High-Side Differential Current-Sense Input. See the <u>Standard Application Circuit</u> for CSHP connection.  The controller amplifies this differential signal to generate the IMON current-monitor output voltage.                                                                                                  |

| 19 | CSHN  | Negative High-Side Differential Current-Sense Input. See the <u>Standard Application Circuit</u> for CSHN connection. The controller amplifies this differential signal to generate the IMON current-monitor output voltage.                                                                                                   |

| 20 | OVP   | Adjustable Output Overvoltage-Protection Threshold. Connect OVP to the center of an external resistive-divider network between the output and AGND to set the output overvoltage-protection limit.                                                                                                                             |

| 21 | 4V6   | 4.6V Linear Regulator Output and Controller Bias Supply. Bypass to AGND with a 2.2μF or greater ceramic capacitor.                                                                                                                                                                                                             |

| 22 | DRV   | Driver Supply Voltage Input. Provides a 5.6V to 14V supply to power the low-side MOSFET gate drivers.                                                                                                                                                                                                                          |

| 23 | AGND  | Analog Ground                                                                                                                                                                                                                                                                                                                  |

| 24 | RAMP  | Slope Compensation Input. A resistor connected from RAMP to AGND programs the amount of slope compensation. See the <u>Adjustable Slope Compensation</u> section.                                                                                                                                                              |

| 25 | ILIM  | Adjustable CSLP-CSLN Cycle-by-Cycle/Hiccup Current-Limit Threshold. Leave floating for internal current-limit threshold or connect a resistor from ILIM to AGND to program the adjustable current-limit threshold.                                                                                                             |

| 26 | NC    | Not Connected                                                                                                                                                                                                                                                                                                                  |

| 27 | DLCS  | External Low-Side Cascade MOSFET Gate Driver. DLCS switches between DRV and PGND.                                                                                                                                                                                                                                              |

| 28 | PGND  | Power Ground. Connect PGND directly to the system ground plane.                                                                                                                                                                                                                                                                |

| 29 | DL    | External Low-Side MOSFET Gate Driver. DL switches between DRV and PGND.                                                                                                                                                                                                                                                        |

| 30 | LX    | Inductor Switch Node                                                                                                                                                                                                                                                                                                           |

| 31 | BST   | Boost Flying-Capacitor Connection. BST serves as the supply for the high-side driver. Connect to a Schottky diode from DRV to BST and an external 0.22nF, 25V ceramic capacitor between BST and LX, as shown in the <u>Standard Application Circuit</u> .                                                                      |

| 32 | DH    | External High-Side MOSFET Gate Driver. DH switches between BST and LX. The controller pulls DH low whenever the controller is disabled.                                                                                                                                                                                        |

| _  | EP    | Exposed Pad. Connect EP to AGND.                                                                                                                                                                                                                                                                                               |

|    |       |                                                                                                                                                                                                                                                                                                                                |

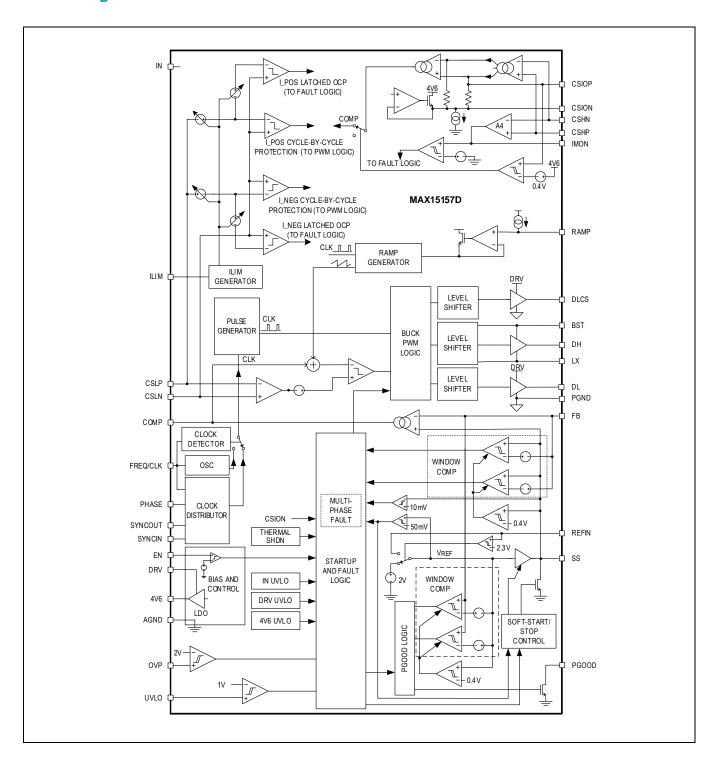

## **Block Diagram**

### **Detailed Description**

The MAX15157D fixed-frequency, current-mode PWM controller drives two power MOSFETs in buck configuration, allowing the regulator to operate as a step-down regulator.

The switching frequency is controlled either through an external resistor setting the internal oscillator frequency, or by synchronizing the regulator to an external clock. The device is designed to support 60kHz to 1MHz switching frequencies.

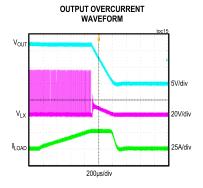

The controller has a dedicated input undervoltage-lockout input (UVLO) and an accurate enable-input threshold for flexible power-sequence configuration. The regulator also has multiple fault-protection circuits to protect against overcurrent, output overvoltage, output undervoltage, and thermal shutdown. The MAX15157D monitors CSHN and latches off immediately when the voltage exceeds 65V.

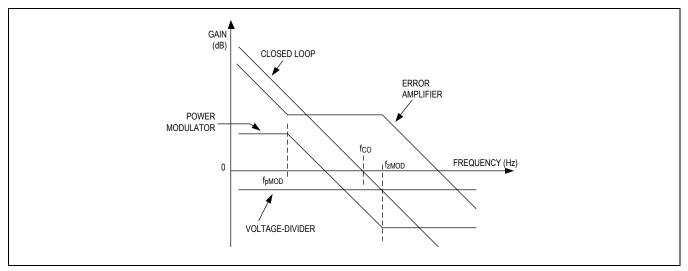

### **Current-Mode Control Loop**

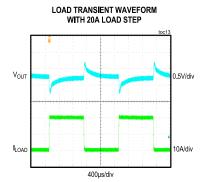

The controller relies on a fixed-frequency, current-mode architecture to regulate the output. By using two MOSFETs and a single inductor, the buck configuration shown in the <u>Typical Application Circuit</u> allows the controller to regulate output voltages below the input voltage. The control loop uses a valley current-mode architecture to optimize performance with low duty cycles and provides the shortest possible minimum on-time.

The controller drives on the low-side MOSFET (DL driven high) on each clock edge. When the PWM comparator detects that the amplified low-side current-sense signal (CSLP to CSLN) and slope compensation have fallen below the COMP voltage, the controller pulls DL low and drives DH high.

### **Driver Supply (DRV)**

In addition to the system input supply, the device requires an external driver supply. The MOSFET drivers require a 5.6V to 14V supply capable of supporting the supply current needed to drive the MOSFETs. The power loss through an internal linear regulator would be significant, so the driver supply typically comes from the regulated 12V system supply. The maximum current required is determined by the switching frequency ( $f_{SW}$ ) and gate-charge of each MOSFET ( $Q_G$ ):

$$I_{DRV} = 2 \times f_{SW} \times Q_G$$

#### Bias Regulator (4V6)

The controller includes an internal linear regulator that generates a regulated 4.6V bias supply to power the internal analog and digital control circuitry. Bypass the regulator with a  $1\mu\text{F}$  or greater ceramic capacitor to maintain noise immunity and stability. The DRV input supply powers the bias linear regulator to reduce the power loss, as shown in the <u>Block Diagram</u>. The 4V6 bias regulator provides up to 30mA of load current and the controller requires up to 5mA, so the remaining load capability can be used to support pullup resistors.

The 4V6 bias linear regulator and internal reference power up only when DRV exceeds its undervoltage-lockout threshold and EN is driven high.

#### Input Undervoltage Lockout

The controller has input undervoltage-lockout thresholds on IN and DRV. The undervoltage-protection circuits inhibit switching until IN and DRV rise above their respective undervoltage thresholds.

If either supply drops below its undervoltage threshold, the controller determines that there is insufficient supply voltage to make valid control decisions. To protect the regulator and the output, the controller immediately pulls PGOOD low, disables the drivers (all driver outputs pulled low), and discharges the SS capacitor through an internal  $5\Omega$  discharge MOSFET, placing the regulator into a high-impedance output state, so the output capacitance passively discharges through the load current.

### **Undervoltage-Lockout Pin (UVLO)**

The external UVLO sense pin allows the input voltage operating range to be externally adjusted for power-sequence control. Either the input power source (IN) or driver supply (DRV) can be monitored. As long as UVLO exceeds and remains above 1V, the controller will power up and remain active. Once UVLO drops below 0.9V (typ), the controller pulls PGOOD low, disables the drivers (all driver outputs pulled low), and discharges the SS capacitor through an internal  $5\Omega$  discharge MOSFET.

The system can use the UVLO input as a secondary enable control pin; however, the controller remains powered (linear regulator and control circuitry biased) as long as the primary EN input remains high. Since the UVLO detection places the regulator into a high-impedance output state, the output capacitance passively discharges through the load current.

UVLO has a 6V absolute maximum voltage rating. Do not connect it directly to the high-voltage input power or driver supplies; short UVLO to the 4V6 bias supply if unused.

#### Soft-Start/Shutdown

The controller begins the startup sequence when both IN and DRV exceed their respective undervoltage-lockout thresholds, and after EN is driven high. With the controller enabled, the bias regulator and internal reference power up. Once the reference stabilizes, the regulator checks the UVLO input to determine if it exceeds 1V, checks the PHASE configuration, and determines if any preset settings are selected. During this initialization period, the controller pulls SS low through a  $5\Omega$  discharge MOSFET.

The regulator charges the SS capacitor with a constant  $5\mu$ A current source until the SS voltage reaches either the preset 2V target voltage (REFIN = 4V6), or the externally driven REFIN voltage (V<sub>REFIN</sub> = 0.4V to 2.2V). The drivers start switching once SS exceeds 50mV and the controller detects that FB voltage is below the SS voltage. The controller enables the fault-protection circuitry when SS exceeds 1V.

At shutdown, once EN drops below 0.54V or UVLO drops below 0.9V, the controller pulls SS low, stops switching, and enters a low-power shutdown state.

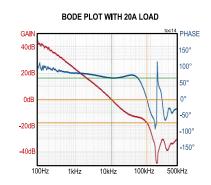

### **Adjustable Slope Compensation (RAMP)**

When the MAX15157D operates at a duty cycle of less than 50%, additional slope compensation is required to prevent the subharmonic instability that occurs naturally in valley-current-mode-controlled converters.

The MAX15157D provides RAMP input to select the internal compensation ramp within a range of 380mV to 1200mV.

By connecting a resistor ( $R_{RAMP}$ ) between RAMP and AGND, internal compensation ramp voltage  $V_{RAMP}$  is calculated as follows:

$$V_{RAMP} = 3.18 \times I_{RAMP} \times R_{RAMP}$$

where I<sub>RAMP</sub> is the current sourced from RAMP to AGND (6µA, typ).

To guarantee stable, jitter-free operation, it is suggested to select R<sub>RAMP</sub> so that:

$$R_{RAMP} \ge \frac{A_{CSL} \times R_{SENSE} \times V_{IN(MAX)}}{3.18 \times I_{RAMP} \times f_{SW} \times L}$$

where:

V<sub>IN(MAX)</sub> = Maximum input voltage

A<sub>CSL</sub> = Current-sense amplifier gain (4.2V/V, typ)

R<sub>SENSE</sub> = Value of equivalent current-sense resistor between CSLP and CSLN

f<sub>SW</sub> = Switching frequency

L = Value of inductor

#### Switching Frequency (FREQ/CLK)

The controller supports 60kHz to 1MHz switching frequencies. Leave FREQ/CLK unconnected to select the preset 300kHz switching frequency. To adjust the switching frequency, either place an external resistor from FREQ/CLK to AGND, or drive FREQ/CLK with an external system clock (see <u>Table 1</u>). The resistively programmable switching frequency is determined by:

$$f_{SW} = \frac{R_{FREQ}}{R_{INT}} \times 600 kHz$$

where  $R_{INT}$  is an internal resistor. With a different  $R_{PHASF}$ , the resistance of  $R_{INT}$  is also a little bit different (see <u>Table 1</u>).

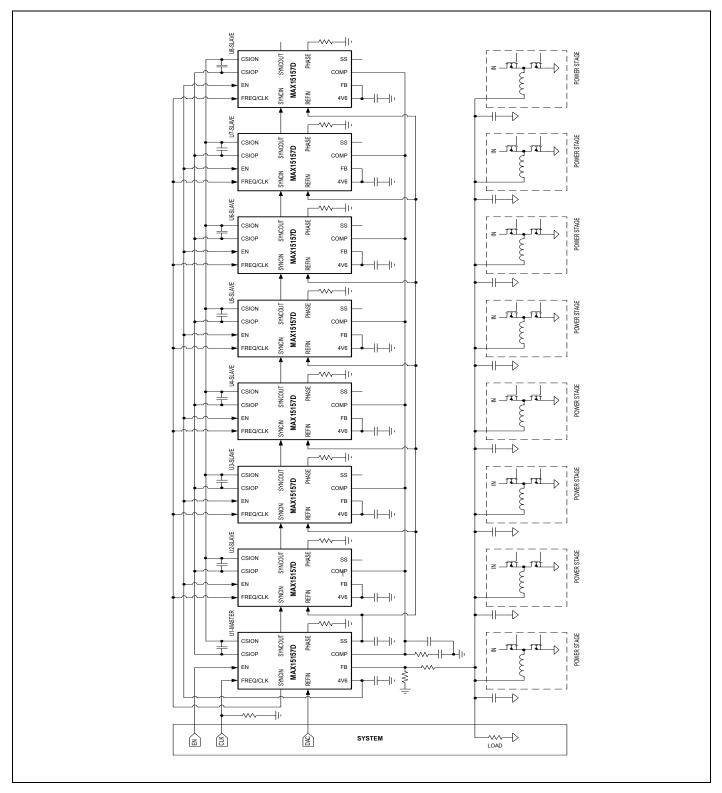

### **Multiphase Synchronization**

The MAX15157D can be configured in single-phase or multiphase operation by selecting the resistor at the PHASE pin. The PHASE setting communicates the master SYNCIN signal frequency and the clock count needed to maintain out-of-phase operation. See <u>Table 1</u> and <u>Figure 5</u> for the R<sub>PHASE</sub> (1% tolerance resistor) selection and the phase shift of each phase.

For proper synchronization between phases in a multiphase configuration, the SYNCIN of the master device acts as a master clock. Connect this SYNCIN output to the FREQ/CLK signals of all the slave devices (see *Figure 5*).

Additionally, the interleaved phase control is communicated by connecting the SYNCOUT signal to the SYNCIN input of the next phase (see *Figure 5*). The daisy-chained signal ensures that the phases run out of phase.

**Table 1. PHASE Configuration**

|                    | able in this be defining an action |              |              |              |              |              |              |              |                    |                  |                     |

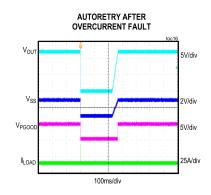

|--------------------|------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------------|------------------|---------------------|