# 8Gb (x16 x 2 channel) Mobile LPDDR4/LPDDR4X

# PRELIMINARY INFORMATION JULY 2022

#### **FEATURES**

- · Configuration:

- 256Mb x16 x 2 channels

- 8 internal banks per channel

- · Low-voltage Core and I/O Power Supplies

VDD1 = 1.70-1.95V

VDD2 = 1.06-1.17V

VDDQ = 1.06-1.17V (LPDDR4)

VDDQ = 0.57-0.65V (LPDDR4X)

- LVSTL(Low Voltage Swing Terminated Logic) I/O Interface

- Internal VREF and VREF Training

- · Dynamic ODT:

DQ ODT: VSSQ Termination

**CA ODT: VSS Termination**

- Max. Clock Frequency: 2133MHz (4266Mbps)

- 16n Pre-fetch DDR architecture

- Single data rate (multiple cycles) command/ address bus

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable and on-the-fly burst lengths (BL=16, 32)

- ZQ Calibration

- · Operation Temperature

Industrial (Tc = -40°C to 95°C)

Automotive, A1 ( $T_C = -40^{\circ}C$  to 95°C)

Automotive, A2 ( $T_C = -40^{\circ}C$  to  $105^{\circ}C$ )

Automotive, A3 (Tc = -40°C to 125°C)

Clock-Stop capability

#### **DESCRIPTION**

The IS43/46LQ32256B and IS43/46LQ32256BL are 8Gbit CMOS LPDDR4 SDRAM. The device is organized as 2 channels per device, and individual channel is 8-banks and 16-bits. This product uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 16N prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. This product offers fully synchronous operations referenced to both rising and falling edges of the clock. The data paths are internally pipelined and 16n bits prefetched to achieve very high bandwidth.

- On-chip temperature sensor whose status can be read from MR4

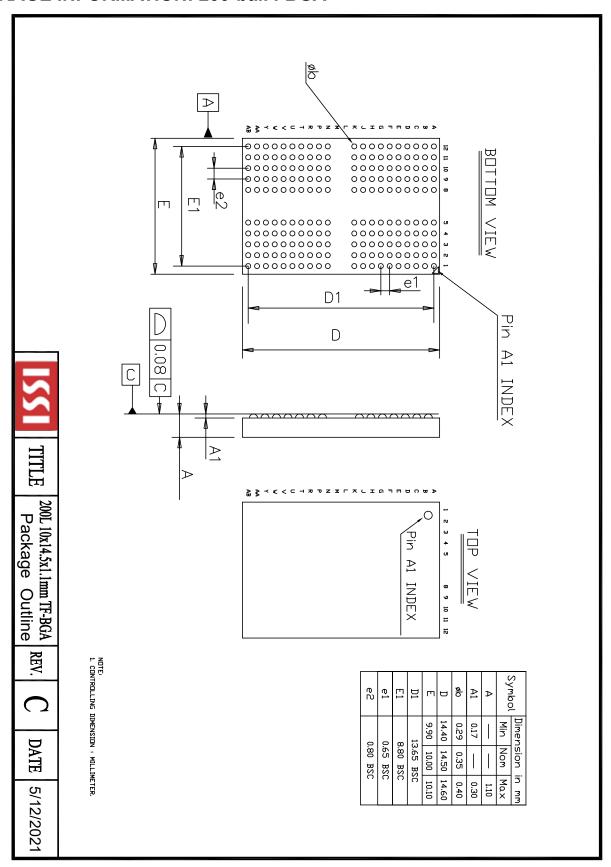

- 200-ball x32 BGA Package (10x14.5 mm)

#### **ADDRESS TABLE**

| 2       |

|---------|

| R0-R14  |

| C0-C9   |

| BA0-BA2 |

|         |

Note: Address information is per channel base.

#### **KEY TIMING PARAMETERS**

|   | Speed | Freq. | Data           |     | rite<br>ency | Re:<br>Late |     |

|---|-------|-------|----------------|-----|--------------|-------------|-----|

|   | Grade | (MHz) | Rate<br>(Mb/s) | Set | Set          | DBI         | DBI |

|   |       |       | (1115/0)       | Α   | В            | OFF         | ON  |

| ĺ | -046  | 2133  | 4266           | 18  | 34           | 36          | 40  |

|   | -053  | 1866  | 3733           | 16  | 30           | 32          | 36  |

|   | -062  | 1600  | 3200           | 14  | 26           | 28          | 32  |

**Note**: Other clock frequencies/data rates supported; please refer to AC timing tables.

Copyright © 2022 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution. Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

## 1. BALL ASSIGNMENTS AND DESCRIPTIONS

## 200-ball x32 Discrete Package, 0.80mm x 0.65mm using MO-311

|                         | 1    | 2                | 3            | 4      | 5    | 6 7          | 8      | 9      | 10           | 11      | 12   |

|-------------------------|------|------------------|--------------|--------|------|--------------|--------|--------|--------------|---------|------|

| Α                       | DNU  | DNU              | vss          | VDD2   | ZQ0  | 0.80mm Pitch | NC     | VDD2   | vss          | DNU     | DNU  |

| В                       | DNU  | DQ0_A            | VDDQ         | DQ7_A  | VDDQ |              | VDDQ   | DQ15_A | VDDQ         | DQ8_A   | DNU  |

| С                       | vss  | DQ1_A            | DMI0_A       | DQ6_A  | vss  |              | vss    | DQ14_A | DMI1_A       | DQ9_A   | vss  |

| D                       | VDDQ | vss              | DQS0_T_A     | vss    | VDDQ |              | VDDQ   | vss    | DQS1_T_A     | vss     | VDDQ |

| E                       | vss  | DQ2_A            | DQS0_C_<br>A | DQ5_A  | vss  |              | vss    | DQ13_A | DQS1_C_<br>A | DQ10_A  | vss  |

| F                       | VDD1 | DQ3_A            | VDDQ         | DQ4_A  | VDD2 |              | VDD2   | DQ12_A | VDDQ         | DQ11_A  | VDD1 |

| G                       | vss  | ODT_CA_<br>A (3) | vss          | VDD1   | vss  |              | vss    | VDD1   | vss          | NC      | VSS  |

| н                       | VDD2 | CA0_A            | NC           | CS0_A  | VDD2 |              | VDD2   | CA2_A  | CA3_A        | CA4_A   | VDD2 |

| J                       | vss  | CA1_A            | vss          | CKE0_A | NC   |              | CK_t_A | CK_c_A | vss          | CA5_A   | vss  |

| itch<br>×               | VDD2 | vss              | VDD2         | vss    | NC   |              | NC     | vss    | VDD2         | vss     | VDD2 |

| 0.65mm Pitch<br>≥ ≤ ⊓ × |      |                  |              |        |      |              |        |        |              |         |      |

| 0.65<br>z               | VDD2 | vss              | VDD2         | vss    | NC   |              | NC     | vss    | VDD2         | vss     | VDD2 |

| Р                       | vss  | CA1_B            | vss          | CKE0_B | NC   |              | CK_T_B | CK_C_B | vss          | CA5_B   | vss  |

| R                       | VDD2 | CA0_B            | NC           | CS0_B  | VDD2 |              | VDD2   | CA2_B  | CA3_B        | CA4_B   | VDD2 |

| т                       | vss  | ODT_CA_<br>B (3) | vss          | VDD1   | vss  |              | vss    | VDD1   | vss          | RESET_N | vss  |

| U                       | VDD1 | DQ3_B            | VDDQ         | DQ4_B  | VDD2 |              | VDD2   | DQ12_B | VDDQ         | DQ11_B  | VDD1 |

| V                       | vss  | DQ2_B            | DQS0_C_<br>B | DQ5_B  | vss  |              | vss    | DQ13_B | DQS1_C_<br>B | DQ10_B  | vss  |

| w                       | VDDQ | vss              | DQS0_T_B     | vss    | VDDQ |              | VDDQ   | vss    | DQS1_T_B     | vss     | VDDQ |

| Y                       | vss  | DQ1_B            | DMI0_B       | DQ6_B  | vss  |              | vss    | DQ14_B | DMI1_B       | DQ9_B   | vss  |

| AA                      | DNU  | DQ0_B            | VDDQ         | DQ7_B  | VDDQ |              | VDDQ   | DQ15_B | VDDQ         | DQ8_B   | DNU  |

| АВ                      | DNU  | DNU              | vss          | VDD2   | vss  |              | vss    | VDD2   | vss          | DNU     | DNU  |

NOTE 1 0.8mm pitch (X-axis), 0.65mm pitch (Y-axis), 22 rows.

NOTE 2 Top View, A1 in top left corner.

NOTE 3 The ODT\_CA pin is ignored by LPDDR4X devices.

## 2. INPUT/OUTPUT FUNTIONAL DESCRIPTION

## 2.1 PAD DEFINITION AND DESCRIPTION

Table 2.1 — Pad Definition and Description

| Symbol                                                        | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t_A,<br>CK_c_A,<br>CK_t_B,<br>CK_c_B                       | Input     | Clock: CK_t and CK_c are differential clock inputs. All address, command, and control input signals are sampled on the crossing of the positive edge of CK_t and the negative edge of CK_c. AC timings for CA parameters are referenced to CK. Each channel (A & B) has its own clock pair.                                                                                                                             |

| CKE_A<br>CKE_B                                                | Input     | Clock Enable: CKE HIGH activates and CKE LOW deactivates the internal clock circuits, input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions. CKE is part of the command code. Each channel (A & B) has its own CKE signal.                                                                                                                                                   |

| CS_A<br>CS_B                                                  | Input     | <b>Chip Select:</b> CS is part of the command code. Each channel (A & B) has its own CS signal.                                                                                                                                                                                                                                                                                                                         |

| CA[5:0]_A<br>CA[5:0]_B                                        | Input     | <b>Command/Address Inputs:</b> CA signals provide the Command and Address inputs according to the Command Truth Table. Each channel (A&B) has its own CA signals.                                                                                                                                                                                                                                                       |

| ODT_CA_A<br>ODT_CA_B                                          | Input     | LPDDR4 CA ODT Control: The ODT_CA pin is used in conjunction with the Mode Register to turn on/off the On-Die-Termination for CA pins.  LPDDR4X CA ODT Control: The ODT_CA pin is ignored by LPDDR4X devices. CA ODT is fully controlled through MR11 and MR22. The ODT_CA pin shall be connected to either VDD2 or VSS.                                                                                                |

| DQ[15:0]_A,<br>DQ[15:0]_B                                     | I/O       | Data Input/Output: Bi-direction data bus.                                                                                                                                                                                                                                                                                                                                                                               |

| DQS[1:0]_t_A, DQS[1:0]_c_A, DQS[1:0]_t_B, DQS[1:0]_c_B        | I/O       | <b>Data Strobe:</b> DQS_t and DQS_c are bi-directional differential output clock signals used to strobe data during a READ or WRITE. The Data Strobe is generated by the DRAM for a READ and is edge-aligned with Data. The Data Strobe is generated by the Memory Controller for a WRITE and must arrive prior to Data. Each byte of data has a Data Strobe signal pair. Each channel (A & B) has its own DQS strobes. |

| DMI[1:0]_A,<br>DMI[1:0]_B                                     | I/O       | <b>Data Mask Inversion:</b> DMI is a bi-directional signal which is driven HIGH when the data on the data bus is inverted, or driven LOW when the data is in its normal state. Data Inversion can be disabled via a mode register setting. Each byte of data has a DMI signal. Each channel (A & B) has its own DMI signals.                                                                                            |

| ZQ                                                            | Reference | <b>Calibration Reference:</b> Used to calibrate the output drive strength and the termination resistance. There is one ZQ pin per die. The ZQ pin shall be connected to $V_{DD}Q$ through a 240 $\Omega$ ± 1% resistor.                                                                                                                                                                                                 |

| V <sub>DD</sub> Q,<br>V <sub>DD</sub> 1,<br>V <sub>DD</sub> 2 | Supply    | Power Supplies: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub> , V <sub>SS</sub> Q                           | GND       | Ground Reference: Power supply ground reference                                                                                                                                                                                                                                                                                                                                                                         |

| RESET_n                                                       | Input     | <b>RESET:</b> When asserted LOW, the RESET_n signal resets both channels of the die.                                                                                                                                                                                                                                                                                                                                    |

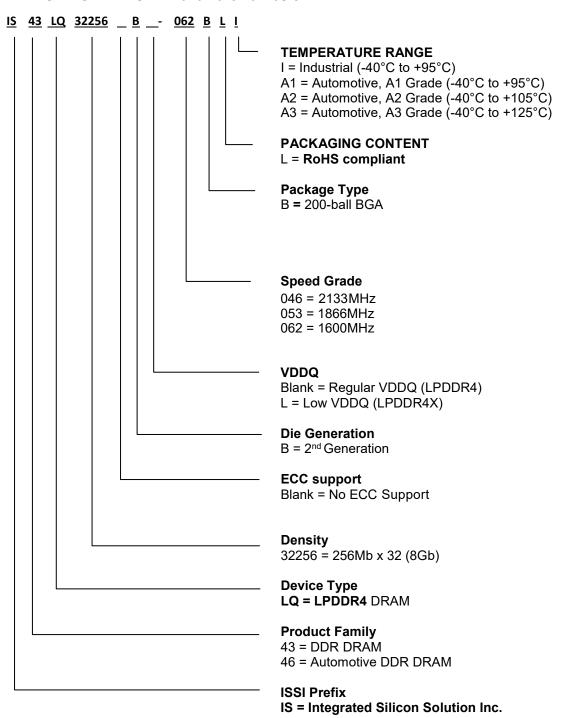

#### ORDERING INFORMATION – Valid Part Numbers

# ORDERING INFORMATION, 256Mb x 32 LPDDR4

Industrial Range:  $T_c = -40^{\circ}C$  to  $+95^{\circ}C$

| Clock    | Speed Grade | Order Part No.      | Package                  |

|----------|-------------|---------------------|--------------------------|

| 1600 MHz | -062        | IS43LQ32256B-062BLI | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS43LQ32256B-053BLI | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS43LQ32256B-046BLI | 200 ball FBGA, lead free |

Automotive, A1 Range: Tc = -40°C to +95°C

| Clock    | Speed Grade | Order Part No.       | Package                  |

|----------|-------------|----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256B-062BLA1 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256B-053BLA1 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256B-046BLA1 | 200 ball FBGA, lead free |

Automotive, A2 Range: Tc = -40°C to +105°C

| Clock    | Speed Grade | Order Part No.       | Package                  |

|----------|-------------|----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256B-062BLA2 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256B-053BLA2 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256B-046BLA2 | 200 ball FBGA, lead free |

Automotive, A3 Range: Tc = -40°C to +125°C

| Clock    | Speed Grade | Order Part No.       | Package                  |

|----------|-------------|----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256B-062BLA3 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256B-053BLA3 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256B-046BLA3 | 200 ball FBGA, lead free |

# ORDERING INFORMATION, 256Mb x 32 LPDDR4X

Industrial Range: T<sub>c</sub> = -40°C to +95°C

| Clock    | Speed Grade | Order Part No.       | Package                  |

|----------|-------------|----------------------|--------------------------|

| 1600 MHz | -062        | IS43LQ32256BL-062BLI | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS43LQ32256BL-053BLI | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS43LQ32256BL-046BLI | 200 ball FBGA, lead free |

Automotive, A1 Range:  $T_c = -40^{\circ}C$  to  $+95^{\circ}C$

| Clock    | Speed Grade | Order Part No.        | Package                  |

|----------|-------------|-----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256BL-062BLA1 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256BL-053BLA1 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256BL-046BLA1 | 200 ball FBGA, lead free |

Automotive, A2 Range: Tc = -40°C to +105°C

| Clock    | Speed Grade | Order Part No.        | Package                  |

|----------|-------------|-----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256BL-062BLA2 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256BL-053BLA2 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256BL-046BLA2 | 200 ball FBGA, lead free |

Automotive, A3 Range: Tc = -40°C to +125°C

| Clock    | Speed Grade | Order Part No.        | Package                  |

|----------|-------------|-----------------------|--------------------------|

| 1600 MHz | -062        | IS46LQ32256BL-062BLA3 | 200 ball FBGA, lead free |

| 1866 MHz | -053        | IS46LQ32256BL-053BLA3 | 200 ball FBGA, lead free |

| 2133 MHz | -046        | IS46LQ32256BL-046BLA3 | 200 ball FBGA, lead free |

# **PACKAGE INFORMATION: 200-ball FBGA**