## 82433LX/82433NX LOCAL BUS ACCELERATOR (LBX)

- Supports the Full 64-bit Pentium® Processor Data Bus at Frequencies up to 66 MHz (82433LX and 82433NX)

- Drives 3.3V Signal Levels on the CPU Data and Address Buses (82433NX)

- Provides a 64-Bit Interface to DRAM and a 32-Bit Interface to PCI

- Five Integrated Write Posting and Read Prefetch Buffers Increase CPU and PCI Performance

- CPU-to-Memory Posted Write Buffer

4 Qwords Deep

- -- PCI-to-Memory Posted Write Buffer Two Buffers, 4 Dwords Each

- PCI-to-Memory Read Prefetch Buffer

4 Qwords Deep

- -- CPU-to-PCI Posted Write Buffer 4 Dwords Deep

- CPU-to-PCI Read Prefetch Buffer

4 Dwords Deep

- CPU-to-Memory and CPU-to-PCI Write Posting Buffers Accelerate Write Performance

- Dual-Port Architecture Allows

Concurrent Operations on the Host and

PCI Buses

- Operates Synchronously to the CPU and PCI Clocks

- Supports Burst Read and Writes of Memory from the Host and PCI Buses

- Sequential CPU Writes to PCI Converted to Zero Wait-State PCI Bursts with Optional TRDY # Connection

- Byte Parity Support for the Host and Memory Buses

- Optional Parity Generation for Host to Memory Transfers

- Optional Parity Checking for the Secondary Cache

- Parity Checking for Host and PCI Memory Reads

- Parity Generation for PCI to Memory Writes

- 160-Pin QFP Package

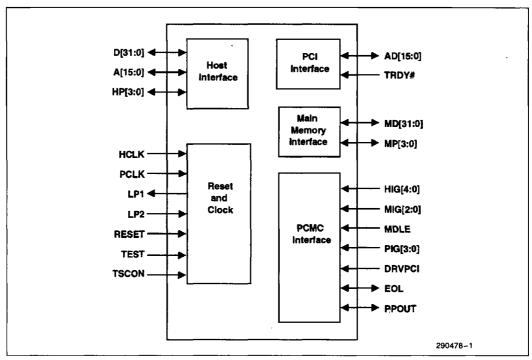

Two 82433LX or 82433NX Local Bus Accelerator (LBX) components provide a 64-bit data path between the host CPU/Cache and main memory, a 32-bit data path between the host CPU bus and PCI Local Bus, and a 32-bit data path between the PCI Local Bus and main memory. The dual-port architecture allows concurrent operations on the host and PCI Buses. The LBXs incorporate three write posting buffers and two read prefetch buffers to increase CPU and PCI performance. The LBX supports byte parity for the host and main memory buses. The 82433NX is intended to be used with the 82434NX PCI/Cache/Memory Controller (PCMC). The 82433LX is intended to be used with the 82434LX PCMC. During bus operations between the host, main memory and PCI, the PCMC commands the LBXs to perform functions such as latching address and data, merging data, and enabling output buffers. Together, these three components form a "Host Bridge" that provides a full function dual-port data path interface, linking the host CPU and PCI bus to main memory.

This document describes both the 82433LX and 82433NX. Shaded areas, like this one, describe the 82433NX operations that differ from the 82433LX.

**LBX Simplified Block Diagram**