# **Intelligent Digital Amplifier and Sound Processor**

#### D2-926xx

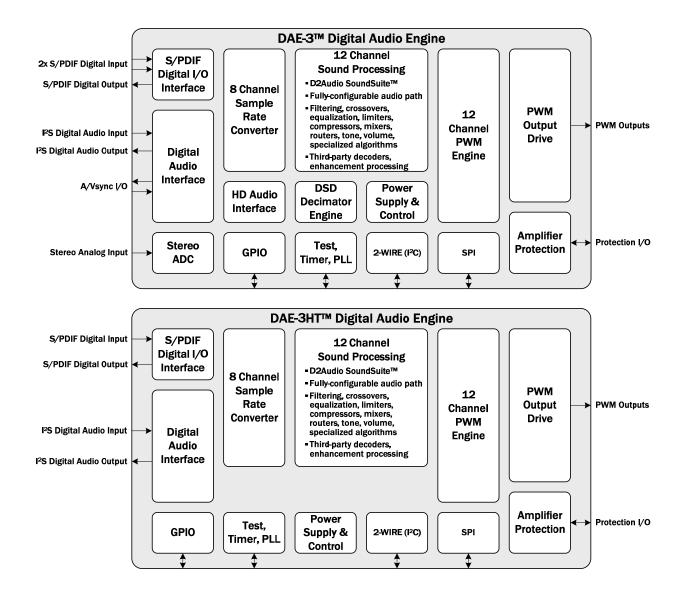

The D2-926xx family of the DAE-3™ and DAE-3HT™ Digital Audio Engine™ devices are complete System-on Chip (SoC) multi-channel digital sound processors and Class-D amplifier controllers.

The integrated DSP provides efficient and configurable audio signal path processing including equalization, dynamic range compression, mixing, and filtering that is completely configurable via the Audio Canvas™ III high level programming interface. The integrated PWM engine supports programmable and dynamic control of audio output, enabling a variety of multi-channel output configurations and output power capacity. Internal noise shaping, an embedded asynchronous sample rate converter, dynamic level-dependent timing, and high resolution operation supports power stage audio performances with SNR >110dB and THD+N < 0.01%.

The D2-926xx devices are provided in two package and feature configurations which include the 128-pin DAE-3, and the72-pin DAE-3HT. Both the DAE-3 and DAE-3HT provide identical performance and enable an extremely flexible platform for feature rich and cost-affordable quality audio solutions, which benefit from the addition of Class-D amplifiers and DSP audio processing.

The 12 integrated digital PWM controllers can be used in a variety of multi-channel audio system configurations, supporting powered as well as line outputs. Fully protected amplifier control provides efficient and clean Class-D power output support.

1

# **Applications**

- · DTV and Blu-ray Soundbar

- DVD and Blu-ray Home Theater Systems

- Home Theater in a Box (HTiB)

- Audio Video Receiver (AVR)

- Multi-Channel Multi-Media (MM) Systems

- · Multi-Room Distributed Audio (MRDA)

- · Powered Speaker Systems

- Automotive Trunk/Amplified Solutions

#### **Features**

- Advanced DAE-3<sup>™</sup> Digital Audio Engine<sup>™</sup> IC Family

- DAE-3™ Pin Compatible and Function/Feature Compatible with the D2Audio™ DAE-6™ Device Family

- DAE-3HT™ Identical DAE-3 performance, in 72-QFN package

- Integrated DSP Digital Sound Processing

- Customizable audio path sound processing

- Fully configurable and routable audio signal paths and hardware function assignment

- Fully Supported with Audio Canvas™ III Design Tool

- . Flexible Audio Input and Output Configurations

- 12 Independent PWM Engine Channels

- 4 Independent Asynchronous I<sup>2</sup>S Digital Inputs

- Integrated high-performance stereo ADC (DAE-3 only)

- S/PDIF™ Digital Audio Inputs supporting Linear IEC-61958 PCM or Compressed IEC-61937 Audio

- S/PDIF Digital Audio PCM Output

- Embedded 8-Channel Sample Rate Converter

- · Real-Time Amplifier Control and Monitoring

- Supports Bridged, Half-Bridged, and Bridge-Tied Load (BTL)

Topologies, Using Discrete or Integrated Power Stages

- Complete Fault Protection with Automatic Recovery

- D2Audio<sup>™</sup> SoundSuite<sup>™</sup> Enhancement and Virtualization

- Enhanced Audio Processing Decoders And Virtualization

- Dolby® Digital/AC3

- Dolby<sup>®</sup> Pro Logic IIx

- Dolby® Virtual Speaker

- DTS®(SRS) TruSurround HD4™, DTS®(SRS) WOW HD™, DTS®(SRS) TruVolume™

## **Ordering Information**

| PART<br>NUMBER<br>(Notes 3, 4) | DAE DEVICE<br>FAMILY | PART<br>MARKING | AUDIO PROCESSING<br>FEATURE SET SUPPORT<br>(Note 1) | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|--------------------------------|----------------------|-----------------|-----------------------------------------------------|---------------------|-----------------------------|----------------|

| D2-92633-LR                    | DAE-3                | D2-92633-LR     | Refer to Table 1                                    | -10 to +85          | 128 Ld LQFP                 | Q128.14x14     |

| D2-92634-LR                    | DAE-3                | D2-92634-LR     | Refer to Table 1                                    | -10 to +85          | 128 Ld LQFP                 | Q128.14x14     |

| D2-92683-QR (Note 2)           | DAE-3HT              | D2-92683-QR     | Refer to Table 1                                    | -10 to +85          | 72 Ld QFN                   | L72.10x10F     |

| D2-92684-QR ( <u>Note 2</u> )  | DAE-3HT              | D2-92684-QR     | Refer to Table 1                                    | -10 to +85          | 72 Ld QFN                   | L72.10x10F     |

#### NOTES:

- 1. The D2-926xx devices support multiple audio processing algorithms and decoders, and support is device-dependent. Refer to <a href="Table 1 on page 3">Table 1 on page 3</a> for the supported features for each device part number.

- 2. Add "-T" suffix for 3k unit Tape and Reel option. Please refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see product information page for <u>D2-92633</u>, <u>D2-92634</u>, <u>D2-92683</u>, <u>D2-92684</u>. For more information on MSL, please see tech brief <u>TB363</u>.

Submit Document Feedback 2 intersil FN6787.3 May 17, 2016

# **DAE-3 Device Feature Set Offering**

The D2-926xx family has specific part numbers to specify the features and algorithms supported in the device. All devices of the DAE-3 family include 8 audio input processing channels, up to 12 PWM output channels, an embedded 8-channel Sample Rate Converter (SRC), and are fully supported with the Audio Canvas III™ design tool software. Additional features within each DAE-3 family part number are shown in Table 1.

**TABLE 1. DAE-3 DEVICE PART NUMBERS AND FEATURES**

| PART NUMBER | DAE FAMILY                | FEATURES                                                                                                                                                                                                                                                                                        | LICENSED ALGORITHM SUPPORT (Note 5)                                                    |

|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| D2-92633-LR | DAE-3<br>128-Pin Package  | 8 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Inputs<br>8 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Outputs<br>2 S/PDIF Digital Inputs<br>1 S/PDIF Digital Output<br>2 ADC Analog Audio Inputs                                                | D2Audio™ SoundSuite™ DTS®(SRS) TruSurround HD4™ DTS®(SRS) WOWHD4™ DTS®(SRS) TruVolume™ |

| D2-92634-LR | DAE-3<br>128-Pin Package  | 8 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Inputs<br>8 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Outputs<br>2 S/PDIF Digital Inputs<br>1 S/PDIF Digital Output<br>2 ADC Analog Audio Inputs                                                | D2Audio™ SoundSuite™<br>Dolby® Digital/AC3 Decoder<br>Dolby® Pro Logic IIx Surround    |

| D2-92683-QR | DAE-3HT<br>72-Pin Package | 8 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Inputs, or 6 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Inputs plus 2 Channels of I <sup>2</sup> S or Left Justified Serial Digital Audio Outputs 1 S/PDIF Digital Input 1 S/PDIF Digital Output | D2Audio™ SoundSuite™ DTS®(SRS) TruSurround HD4™ DTS®(SRS) WOWHD4™ DTS®(SRS) TruVolume™ |

| D2-92684-QR | DAE-3HT<br>72-Pin Package | 8 Channels of $I^2S$ or Left Justified Serial Digital Audio Inputs, or 6 Channels of $I^2S$ or Left Justified Serial Digital Audio Inputs plus 2 Channels of $I^2S$ or Left Justified Serial Digital Audio Outputs 1 S/PDIF Digital Input 1 S/PDIF Digital Output                               | D2Audio™ SoundSuite™<br>Dolby® Digital/AC3 Decoder<br>Dolby® Pro Logic IIx Surround    |

#### NOTE:

# **Device Designations**

This datasheet applies to all of the DAE-3 device family, which includes both the DAE-3 and DAE-3HT. Functional specifications apply to both designations of this family unless otherwise indicated.

Throughout this document the device names apply to all part numbers of their respective names as follows:

| DAE DEVICE NAME | DAE DEVICE PART NUMBERS  | PACKAGE PINS    |

|-----------------|--------------------------|-----------------|

| DAE-3           | D2-92633-LR, D2-92634-LR | 128-Pin Package |

| DAE-3HT         | D2-92683-QR, D2-92684-QR | 72-Pin Package  |

Submit Document Feedback 3 intersil FN6787.3 May 17, 2016

<sup>5.</sup> All DAE-3 family devices support D2Audio™ SoundSuite™ Audio Processing algorithms, and with license agreements executed with DTS®(SRS) Labs, also support DTS®(SRS) TruSurround HD4™, DTS®(SRS) WOW HD™, and DTS®(SRS) TruVolume™

# **D2-926xx**

# **Table of Contents**

| Ordering Information                                         |      |

|--------------------------------------------------------------|------|

| Device Designations                                          | 8    |

| Absolute Maximum Ratings                                     |      |

| Thermal Information                                          | 5    |

| Recommended Operating Conditions                             | Ę    |

| Electrical Specifications                                    |      |

| Serial Audio Interface Port Timing                           | 7    |

| Two-Wire (I <sup>2</sup> C) Interface Port Timing            | 8    |

| SPI™ Interface Port Timing                                   |      |

| Pin Configuration DAE-3 (128-Pin Package)                    |      |

| Pin Configuration DAE-3HT (72-Pin Package)                   |      |

| Pin Description, DAE-3 (128-Pin)                             |      |

| Pin Description DAE-3HT (72-Pin)                             |      |

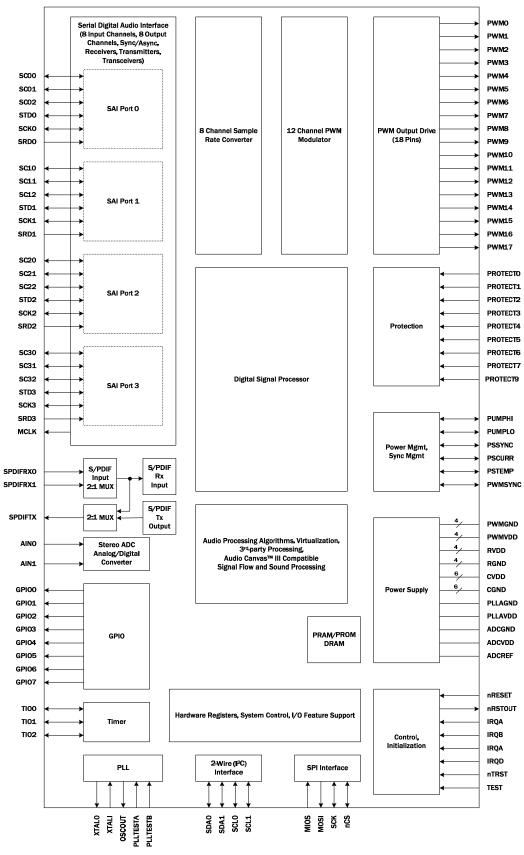

| Functional Block Diagram - DAE-3                             |      |

|                                                              |      |

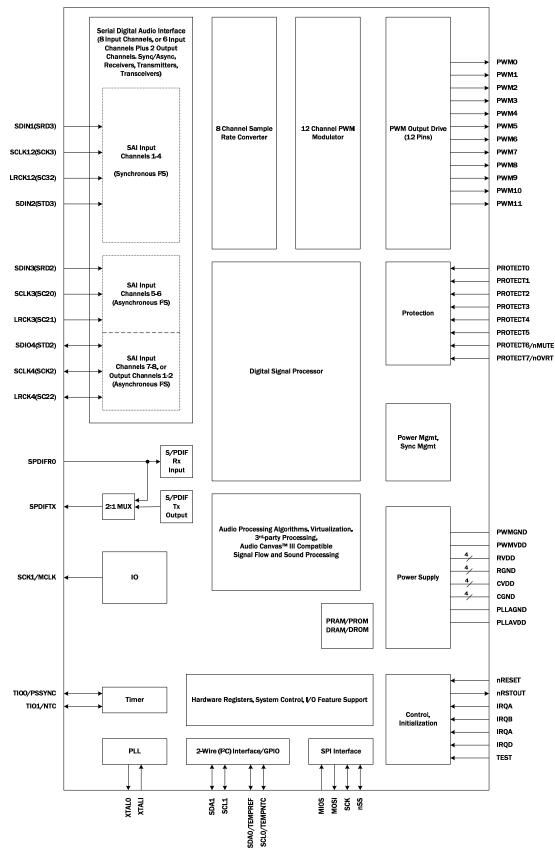

| Functional Block Diagram - DAE-3HT                           |      |

| Functional Description                                       |      |

| Sample Rate Converters (SRC)                                 |      |

| Serial Digital Audio Interface                               |      |

| S/PDIF Digital Audio Interface                               |      |

| ADC input (DAE-3 Devices Only).                              |      |

| PWM Audio Amplifier Outputs                                  |      |

| Amplifier Protection                                         |      |

| Clocks And PLL                                               |      |

| Reset and Initialization                                     |      |

| Power Sequencing                                             |      |

| Reset                                                        |      |

| Control Interfaces                                           |      |

| Reading and Writing Control Registers.                       |      |

| Audio Processing Algorithms                                  |      |

| SoundSuite™ Processing                                       |      |

| Third Party Virtualization and Enhancements                  |      |

| Dynamic Register Addressing Architecture                     |      |

| Hardware Feature Functions                                   |      |

| DAE-3 And DAE-3HT Differences                                | . 32 |

| Pin Function Mapping Between Devices                         |      |

| I/O Pin Function Assignment Comparison                       | . 33 |

| Revision History                                             | . 34 |

| About Intersil                                               | . 34 |

| Disclaimer for DTS®(SRS) Technology License Required Notice: | . 35 |

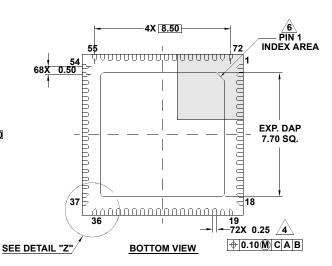

| Package Outline Drawing                                      | . 36 |

| L72.10x10F                                                   |      |

| Q128.14x14                                                   |      |

#### Absolute Maximum Ratings (Note 10)

| Supply Voltage                                                                        |

|---------------------------------------------------------------------------------------|

| RVDD, PWMVDD, ADCVDD0.3V to 4.0V                                                      |

| CVDD, PLLVDD0.3V to 2.4V                                                              |

| Input Voltage                                                                         |

| Any Input but XTALI0.3V to RVDD +0.3V                                                 |

| XTALI0.3V to PLLVDD +0.3V                                                             |

| Input Current, Any Pin but Supplies ±10mA                                             |

| ESD Rating                                                                            |

| Human Body Model (Tested per JESD22-A114F)2000V                                       |

| Machine Model (Tested per JESD22-A115C) 200V                                          |

| Charged Device Model (Tested per JESD22-C101E)750V                                    |

| Latch-Up                                                                              |

| (Pins 2, 4, 6, 7, 8, 9, 37 (72 Ld Package only) Tested per JESD78D Class II, Level B) |

| (All other pine rected per sees class in Ector A) Leonia                              |

#### **Thermal Information**

| Thermal Resistance (Typical)     | θ <sub>JA</sub> (°C/W) | $\theta_{JC}$ (°C/W) |

|----------------------------------|------------------------|----------------------|

| 128 Ld LQFP Package (Notes 6, 8) | 39                     | 6.5                  |

| 72 Ld QFN Package (Notes 7, 9)   | 22                     | 0.80                 |

| Maximum Storage Temperature      | 5                      | 55°C to +150°C       |

| Pb-Free Reflow Profile           |                        | see <u>TB493</u>     |

### **Recommended Operating Conditions**

| Temperature Range                  | 10°C to +85°C |

|------------------------------------|---------------|

| Digital I/O Supply Voltage, PWMVDD | 3.3V          |

| Core Supply Voltage, CVDD          | 1.8V          |

| Analog Supply Voltage, PLLVDD      | 1.8V          |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 6.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 7.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board with direct attach of exposed pad to PCB.

- 8. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

- 9. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" is measured on bottom of exposed pad.

- 10. Absolute Maximum parameters are not tested in production.

**Electrical Specifications**  $T_A = +25$ ° C, CVDD = PLLVDD = 1.8V  $\pm 5\%$ , RVDD = PWMVDD = 3.3V  $\pm 10\%$ . All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic. Minimum supply currents are measured in full power down configuration.

| SYMBOL             | PARAMETER                                                                                                                                                                                             | TEST<br>CONDITIONS | MIN<br>( <u>Note 14</u> ) | TYP | MAX<br>( <u>Note 14</u> ) | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|-----|---------------------------|------|

| V <sub>IH</sub>    | Digital Input High Logic Level (Note 11)                                                                                                                                                              | Relative to RVDD   | 2.0                       | -   | -                         | V    |

| V <sub>IL</sub>    | Digital Input Low Logic Level (Note 11)                                                                                                                                                               | Relative to RVDD   | -                         | -   | 0.8                       | V    |

| V <sub>OH</sub>    | High Level Output Drive Voltage I <sub>OUT</sub> at - Pin Drive Strength Current. See <u>"Pin Description, DAE-3 (128-Pin)" on page 12</u> , and <u>"Pin Description DAE-3HT (72-Pin)" on page 17</u> |                    | RVDD - 0.4                | -   | -                         | V    |

| V <sub>OL</sub>    | Low Level Output Drive Voltage I <sub>OUT</sub> at + Pin Drive Strength Current. See <u>"Pin Description, DAE-3 (128-Pin)" on page 12</u> , and <u>"Pin Description DAE-3HT (72-Pin)" on page 17</u>  |                    | -                         | -   | 0.4                       | V    |

| VIHX               | High Level Input Drive Voltage XTALI Pin                                                                                                                                                              |                    | 0.7                       | -   | PLLVDD                    | V    |

| VILX               | Low Level Input Drive Voltage XTALI Pin                                                                                                                                                               |                    | -                         | -   | 0.3                       | ٧    |

| I <sub>IN</sub>    | Input Leakage Current (Note 12)                                                                                                                                                                       |                    | -                         | -   | ±10                       | μΑ   |

| C <sub>IN</sub>    | Input Capacitance                                                                                                                                                                                     |                    | -                         | 9   | -                         | pF   |

| vоно               | High Level Output Drive Voltage OSCOUT Pin                                                                                                                                                            |                    | PLLVDD - 0.3              | -   | -                         | V    |

| VOLO               | Low Level Output Drive Voltage OSCOUT Pin                                                                                                                                                             |                    | -                         | -   | 0.3                       | V    |

| C <sub>OUT</sub>   | Output Capacitance                                                                                                                                                                                    |                    | -                         | 9   | -                         | pF   |

| t <sub>RST</sub>   | nRESET Pulse Width                                                                                                                                                                                    |                    | -                         | 10  | -                         | ns   |

| R <sub>VDD</sub>   | Typical Digital I/O Pad Ring Supply (Voltage)                                                                                                                                                         |                    | 3.0                       | 3.3 | 3.6                       | V    |

|                    | (Current, Active)                                                                                                                                                                                     |                    | -                         | 10  | -                         | mA   |

|                    | (Current, Power-Down)                                                                                                                                                                                 |                    | -                         | <1  | -                         | mA   |

| PWM <sub>VDD</sub> | Typical PWM I/O Pad Ring Supply (Voltage)                                                                                                                                                             |                    | 3.0                       | 3.3 | 3.6                       | V    |

|                    | (Current, Active)                                                                                                                                                                                     |                    | -                         | 5   | -                         | mA   |

|                    | (Current, Power-Down)                                                                                                                                                                                 |                    | -                         | <1  | -                         | mA   |

Submit Document Feedback 5 Intersil 5 FN6787.3 May 17, 2016

### **D2-926xx**

**Electrical Specifications**  $T_A = +25$ °C, CVDD = PLLVDD = 1.8V  $\pm 5\%$ , RVDD = PWMVDD = 3.3V  $\pm 10\%$ . All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic. Minimum supply currents are measured in full power down configuration. **(Continued)**

| SYMBOL             | PARAMETER                                                                                                                                                                                                          | TEST<br>CONDITIONS                                                 | MIN<br>( <u>Note 14</u> ) | TYP     | MAX<br>( <u>Note 14</u> ) | UNIT |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------|---------|---------------------------|------|

| CVDD               | Typical Core Supply (Voltage)                                                                                                                                                                                      |                                                                    | 1.7                       | 1.8     | 1.9                       | ٧    |

|                    | (Current, Active)                                                                                                                                                                                                  |                                                                    | -                         | 300     | -                         | mA   |

|                    | (Current, Power-Down)                                                                                                                                                                                              |                                                                    | -                         | 15      | -                         | mA   |

| PLLVDD             | Typical PLL Analog Supply (Voltage)                                                                                                                                                                                |                                                                    | 1.7                       | 1.8     | 1.9                       | ٧    |

|                    | (Current, Active)                                                                                                                                                                                                  |                                                                    | -                         | 25      | -                         | mA   |

|                    | (Current, Power-Down)                                                                                                                                                                                              |                                                                    | -                         | 10      | -                         | mA   |

| ADCVDD             | Typical ADC Analog Supply (Voltage)                                                                                                                                                                                |                                                                    | 3.0                       | 3.3     | 3.6                       | ٧    |

|                    | (Current, Active, Power-Down)                                                                                                                                                                                      |                                                                    | •                         | 12      | -                         | mA   |

| CRYSTAL (          | DSCILLATOR                                                                                                                                                                                                         |                                                                    |                           |         |                           |      |

| Хо                 | Crystal Frequency (Fundamental Mode Crystal)                                                                                                                                                                       |                                                                    | 20                        | 24.576  | 24.822<br>(24.576 + 1%)   | MHz  |

| Dt                 | Duty Cycle                                                                                                                                                                                                         |                                                                    | 40                        | -       | 60                        | %    |

| <sup>t</sup> START | Start-Up Time (Start-Up Time is Oscillator Enabled (with Valid Supply) to Stable Oscillation)                                                                                                                      |                                                                    | -                         | 5       | 20                        | ms   |

| PLL                |                                                                                                                                                                                                                    | 1                                                                  |                           | - 1     |                           |      |

| F <sub>VCO</sub>   | VCO Frequency                                                                                                                                                                                                      |                                                                    | 80.00                     | 294.912 | 297.86                    | MHz  |

| F <sub>IN</sub>    | Input Reference Frequency                                                                                                                                                                                          |                                                                    | 20                        | -       | 24.822<br>(24.576 + 1%)   | MHz  |

|                    | Feedback Dividers (Integer)                                                                                                                                                                                        |                                                                    | 4                         | 12      | 15                        |      |

|                    | PLL Lock Time from any Input Change                                                                                                                                                                                |                                                                    | -                         | 2       | -                         | ms   |

| 1.8V POW           | ER-ON RESET                                                                                                                                                                                                        |                                                                    |                           |         | I                         | I.   |

| V <sub>EN</sub>    | Reset Enabled Voltage Level                                                                                                                                                                                        |                                                                    | 0.9                       | 1.1     | 1.4                       | V    |

| t <sub>REJ</sub>   | POR Pulse Width Rejection (Note 14)                                                                                                                                                                                |                                                                    |                           | 150     | 500                       | μs   |

| t <sub>DIS</sub>   | POR Minimum Output Pulse Width                                                                                                                                                                                     |                                                                    |                           | 5       | -                         | μs   |

| 1.8V BRO\          | WNOUT DETECTION                                                                                                                                                                                                    |                                                                    |                           |         | I                         | I.   |

|                    | Detect Level                                                                                                                                                                                                       |                                                                    | 1.4                       | 1.5     | 1.6                       | ٧    |

| t <sub>BOD1</sub>  | Pulse Width Rejection                                                                                                                                                                                              |                                                                    |                           | 100     | -                         | ns   |

| t <sub>01</sub>    | Minimum Output Pulse Width                                                                                                                                                                                         |                                                                    | 20                        | -       | -                         | ns   |

| 3.3V BROV          | WNOUT DETECTION                                                                                                                                                                                                    |                                                                    |                           | 1       |                           |      |

|                    | Detect Level                                                                                                                                                                                                       |                                                                    | 2.5                       | 2.7     | 2.9                       | ٧    |

| t <sub>BOD3</sub>  | Pulse Width Rejection                                                                                                                                                                                              |                                                                    |                           | 100     | -                         | ns   |

| t <sub>03</sub>    | Minimum Output Pulse Width                                                                                                                                                                                         |                                                                    | 20                        | -       | -                         | ns   |

| ADC PERF           | ORMANCE SPECIFICATIONS (DAE-3 only)                                                                                                                                                                                | 1                                                                  |                           |         | I.                        | I.   |

| V <sub>REF</sub>   | ADCREF DC Level                                                                                                                                                                                                    |                                                                    | 1.3                       | 1.4     | 1.5                       | ٧    |

| I <sub>REF</sub>   | ADCREF Load Current                                                                                                                                                                                                |                                                                    |                           | -       | ±20                       | μΑ   |

| V <sub>AIN</sub>   | Analog Input Level                                                                                                                                                                                                 |                                                                    | V <sub>REF</sub> - 0.6    | -       | V <sub>REF</sub> + 0.6    | ٧    |

|                    | ADC Dynamic Range and SNR ( <u>Note 15</u> ) (ADC + ADC Decimator performance only, DSP inactive, no digital audio processing, PWM outputs off, no pPWM switching)                                                 | 1.0 V <sub>P-P</sub> 1kHz<br>sine wave input<br>reference level,   | -                         | 94      | -                         | dB   |

|                    | ADC Dynamic Range and SNR ( <u>Note 15</u> ) (DSP active and processing audio data, PWM active and driving audio outputs, measurements using typical system-level amplifier equivalent as measurement environment) | using firmware<br>from Audio<br>Canvas III™ rev<br>3.1.4 or newer. | -                         | 83      | -                         | dB   |

Submit Document Feedback 6 Intersil\* FN6787.3

May 17, 2016

**Electrical Specifications**  $T_A = +25$ °C, CVDD = PLLVDD = 1.8V  $\pm 5$ %, RVDD = PWMVDD = 3.3V  $\pm 10$ %. All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic. Minimum supply currents are measured in full power down configuration. (Continued)

| SYMBOL | PARAMETER              | TEST<br>CONDITIONS | MIN<br>(Note 14) | TYP | MAX<br>(Note 14) | UNIT |

|--------|------------------------|--------------------|------------------|-----|------------------|------|

|        | THD+N                  |                    | -                | -80 | -                | dB   |

|        | Gain Mismatch          |                    | -                | 0.1 | -                | dB   |

|        | Crosstalk              |                    | -                | -80 | -                | dB   |

|        | Power Supply Rejection |                    | -                | -70 | -                | dB   |

#### NOTES:

- 11. All input pins except XTALI.

- 12. Input leakage applies to all pins except XTALO.

- 13. Power-down is with device in reset and clocks stopped.

- 14. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 15. Analog performance is system-design dependent and is affected by factors that include PCB layout, shielding and routing of analog traces, additional components within the analog input path, and power supply isolation.

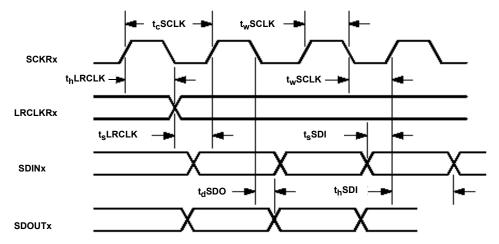

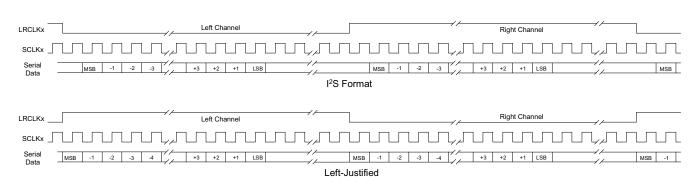

Serial Audio Interface Port Timing (Figure 1) TA = +25 °C, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. AII grounds at 0.0V. All voltages referenced to ground.

| SYMBOL              | DESCRIPTION                                     | MIN<br>( <u>Note 14</u> ) | TYP | MAX<br>( <u>Note 14</u> ) | UNIT |

|---------------------|-------------------------------------------------|---------------------------|-----|---------------------------|------|

| tc <sub>SCLK</sub>  | SCKRx Frequency - SCKR0, SCKR1                  |                           |     | 12.5                      | MHz  |

| tw <sub>SCLK</sub>  | SCKRx Pulse Width (High and Low) - SCKR0, SCKR1 | 40                        |     |                           | ns   |

| ts <sub>LRCLK</sub> | LRCKRx Set-Up to SCLK Rising - LRCKR0, LRCKR1   | 20                        |     |                           | ns   |

| th <sub>LRCLK</sub> | LRCKRx Hold from SCLK Rising - LRCKR0, LRCKR1   | 20                        |     |                           | ns   |

| ts <sub>SDI</sub>   | SDINx Set-Up to SCLK Rising - SDIN0, SDIN1      | 20                        |     |                           | ns   |

| th <sub>SDI</sub>   | SDINx Hold from SCLK Rising - SDIN0, SDIN1      | 20                        |     |                           | ns   |

| t <sub>dSD0</sub>   | SDOUTx Delay from SCLK Falling                  |                           |     | 20                        | ns   |

FIGURE 1. SERIAL AUDIO INTERFACE PORT TIMING

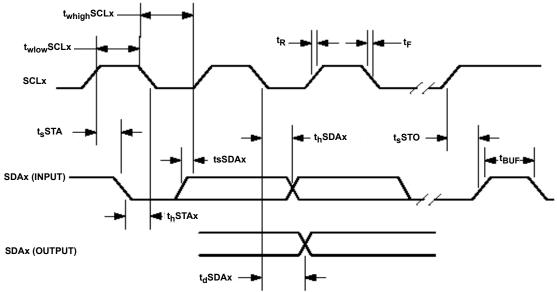

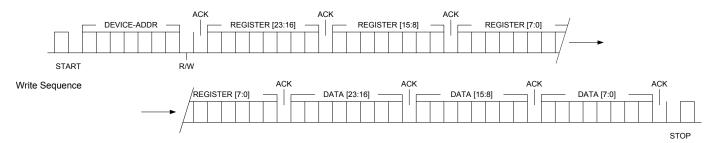

Two-Wire (I<sup>2</sup>C) Interface Port Timing (Figure 2)  $T_A = +25$  °C, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL                 | DESCRIPTION                            | MIN<br>( <u>Note 14</u> ) | MAX<br>( <u>Note 14</u> ) | UNIT |

|------------------------|----------------------------------------|---------------------------|---------------------------|------|

| f <sub>SCL</sub>       | SCL Frequency                          |                           | 100                       | kHz  |

| t <sub>buf</sub>       | Bus Free Time Between Transmissions    | 4.7                       |                           | μs   |

| tw <sub>lowSCLx</sub>  | SCL Clock Low                          | 4.7                       |                           | μs   |

| tw <sub>highSCLx</sub> | SCL Clock High                         | 4.0                       |                           | μs   |

| ts <sub>STA</sub>      | Set-Up Time For a (Repeated) Start     | 4.7                       |                           | μs   |

| th <sub>STA</sub>      | Start Condition Hold Time              | 4.0                       |                           | μs   |

| th <sub>SDAx</sub>     | SDA Hold From SCL Falling (Note 16)    | 0                         |                           | μs   |

| ts <sub>SDAx</sub>     | SDA Set-Up Time to SCL Rising          | 250                       |                           | ns   |

| td <sub>SDAx</sub>     | SDA Output Delay Time From SCL Falling |                           | 3.5                       | μs   |

| t <sub>r</sub>         | Rise Time of Both SDA and SCL          |                           | 1                         | μs   |

| t <sub>f</sub>         | Fall Time of Both SDA and SCL          |                           | 300                       | ns   |

| ts <sub>STO</sub>      | Set-Up Time For a Stop Condition       | 4.7                       |                           | μs   |

#### NOTE:

16. Data must be held sufficient time to bridge the 300ns transition time of SCL.

FIGURE 2. I<sup>2</sup>C INTERFACE TIMING

8

## **D2-926xx**

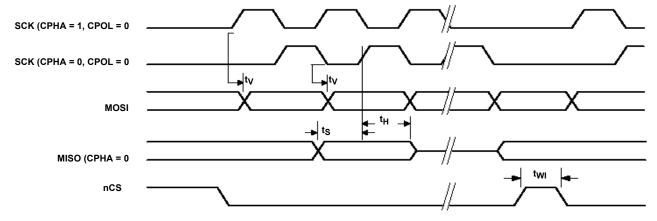

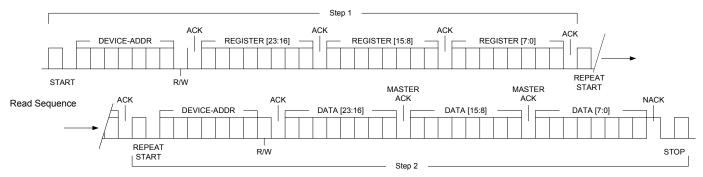

**SPITM Interface Port Timing** (Figure 3)  $T_A = +25$  °C, CVDD = PLLVDD = 1.8V  $\pm 5$ %, RVDD = PWMVDD = 3.3V  $\pm 10$ %. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL         | DESCRIPTION                | MIN<br>( <u>Note 14</u> ) | MAX<br>( <u>Note 14</u> ) | UNIT                     |

|----------------|----------------------------|---------------------------|---------------------------|--------------------------|

| SPI MASTER MO  | DE TIMING                  |                           |                           | *                        |

| t <sub>V</sub> | MOSI Valid From Clock Edge |                           | 8                         | ns                       |

| t <sub>S</sub> | MISO Set-Up to Clock Edge  | 2                         |                           | ns                       |

| t <sub>H</sub> | MISO Hold From Clock Edge  | 2                         |                           | ns                       |

| twi            | nCS Minimum Width          | 3                         |                           | 3 system clocks<br>+ 2ns |

| SPI SLAVE MOD  | E TIMING                   |                           |                           |                          |

| t <sub>V</sub> | MISO Valid From Clock Edge |                           | 8                         | ns                       |

| t <sub>S</sub> | MOSI Set-Up to Clock Edge  | 2                         |                           | ns                       |

| t <sub>H</sub> | MOSI Hold From Clock Edge  | 2                         |                           | ns                       |

| twi            | nCS Minimum Width          | 3                         |                           | 3 system clocks<br>+ 2ns |

FIGURE 3. SPI TIMING

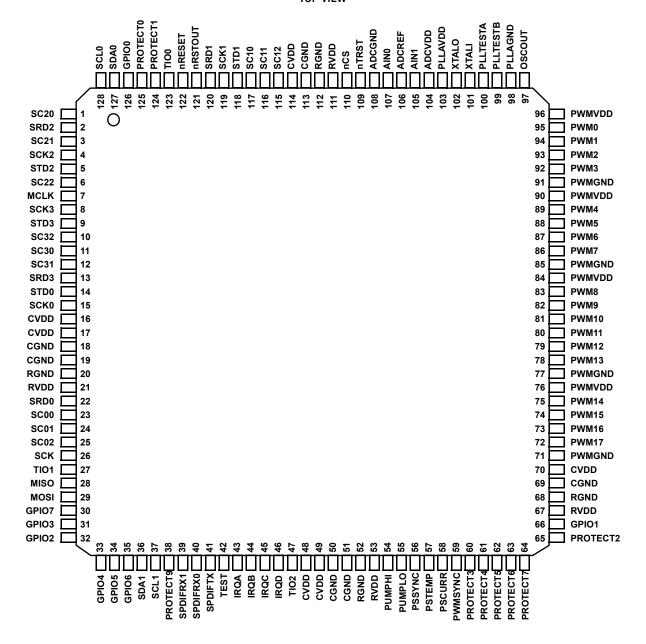

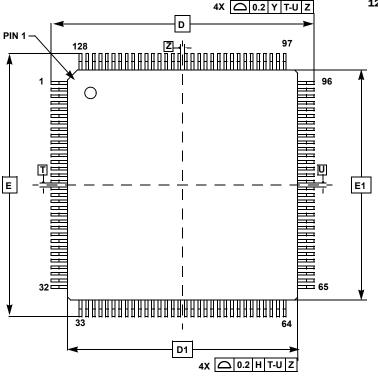

## Pin Configuration DAE-3 (128-Pin Package)

D2-92633, D2-92634 (128 LD LQFP) TOP VIEW

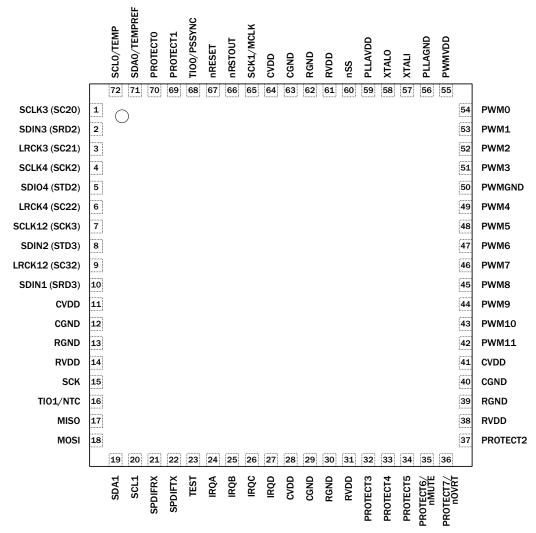

# Pin Configuration DAE-3HT (72-Pin Package)

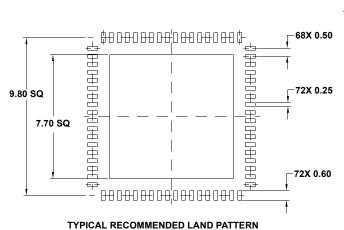

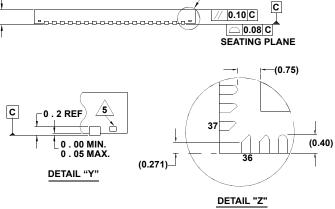

D2-92683, D2-92684 (72 LD QFN) TOP VIEW

NOTE:

17. All pins pass Jedec II 100mA at  $+85\,^{\circ}$ C, with exception of pins 2, 4, 6, 7, 8, 9, 37, which pass 50mA at  $+85\,^{\circ}$ C

# Pin Description, DAE-3 (128-Pin)

| PIN | PIN<br>NAME<br>(Note 18) | TYPE | VOLTAGE<br>LEVEL<br>(V) | DRIVE<br>STRENGTH<br>(mA) | DESCRIPTION                                                                                                                                                           |  |

|-----|--------------------------|------|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | SC20                     | 1/0  | 3.3                     | 8                         | Serial Audio Interface 2, I <sup>2</sup> S0 SCLK                                                                                                                      |  |

| 2   | SRD2                     | 1/0  | 3.3                     | 4                         | Serial Audio Interface 2, 1 <sup>2</sup> S0 SDIN                                                                                                                      |  |

| 3   | SC21                     | 1/0  | 3.3                     | 8                         | Serial Audio Interface 2, I <sup>2</sup> SO LRCK                                                                                                                      |  |

| 4   | SCK2                     | 1/0  | 3.3                     | 8                         | Serial Audio Interface 2, I <sup>2</sup> S1 SCLK                                                                                                                      |  |

| 5   | STD2                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 2, I <sup>2</sup> S1 SDIN                                                                                                                      |  |

| 6   | SC22                     | I/O  | 3.3                     | 4                         | Serial Audio Interface 2, I <sup>2</sup> S1 LRCK                                                                                                                      |  |

| 7   | MCLK                     | 0    | 3.3                     | 16                        | I <sup>2</sup> S Serial Audio Master Clock output for external ADC/DAC components, drives low on reset and is enabled by firmware assignment.                         |  |

| 8   | SCK3                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 3, I <sup>2</sup> S3 SCLK                                                                                                                      |  |

| 9   | STD3                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 3, I <sup>2</sup> S3 SDIN                                                                                                                      |  |

| 10  | SC32                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 3, I <sup>2</sup> S3 LRCK                                                                                                                      |  |

| 11  | SC30                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 3, I <sup>2</sup> S2 SCLK                                                                                                                      |  |

| 12  | SC31                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 3, I <sup>2</sup> S2 LRCK                                                                                                                      |  |

| 13  | SRD3                     | I/O  | 3.3                     | 4                         | Serial Audio Interface 3, I <sup>2</sup> S2 SDIN                                                                                                                      |  |

| 14  | STD0                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 0, 1 <sup>2</sup> S SDAT0                                                                                                                      |  |

| 15  | SCK0                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 0, I <sup>2</sup> S LRCK0                                                                                                                      |  |

| 16  | CVDD                     | Р    | 3.3                     |                           | Core power, 1.8V                                                                                                                                                      |  |

| 17  | CVDD                     | Р    | 3.3                     |                           | Core power, 1.8V                                                                                                                                                      |  |

| 18  | CGND                     | Р    | 3.3                     |                           | Core ground                                                                                                                                                           |  |

| 19  | CGND                     | Р    | 3.3                     |                           | Core ground                                                                                                                                                           |  |

| 20  | RGND                     | Р    | 3.3                     |                           | Digital pad ring ground. Internally connected to PWMGND.                                                                                                              |  |

| 21  | RVDD                     | Р    | 3.3                     |                           | Digital pad ring power, 3.3V. This 3.3V supply is used for all the digital I/O pad drivers and receivers, except for the analog pads. Internally connected to PWMVDD. |  |

| 22  | SRD0                     | I/O  | 3.3                     | 4                         | Serial Audio Interface 0, SDIO, Defaults to input, and may be configured as GPIO by firmware.                                                                         |  |

| 23  | SC00                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 0, SDIO, Defaults to input, and may be configured as GPIO by firmware.                                                                         |  |

| 24  | SC01                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 0, I <sup>2</sup> S SDAT1                                                                                                                      |  |

| 25  | SC02                     | I/O  | 3.3                     | 8                         | Serial Audio Interface 0, I <sup>2</sup> S LRCK1                                                                                                                      |  |

| 26  | SCK                      | I/O  | 3.3                     | 4                         | SPI clock I/O with hysteresis input.                                                                                                                                  |  |

| 27  | TIO1                     | 1/0  | 3.3                     | 16                        | Timer I/O Port 1. Operation and assignment is controlled by firmware. Leave unconnected when not in use.                                                              |  |

| 28  | MISO                     | I/O  | 3.3                     | 4                         | SPI master input, slave output data signal.                                                                                                                           |  |

| 29  | MOSI                     | I/O  | 3.3                     | 4                         | SPI master output, slave input data signal.                                                                                                                           |  |

| 30  | GPI07                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)            |  |

| 31  | GPI03                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)            |  |

| 32  | GPI02                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)            |  |

| 33  | GPI04                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)            |  |

Submit Document Feedback 12 intersil FN6787.3 May 17, 2016

| PIN | PIN<br>NAME<br>(Note 18) | TYPE | VOLTAGE<br>LEVEL<br>(V) | DRIVE<br>STRENGTH<br>(mA) | DESCRIPTION                                                                                                                                                                                                    |  |

|-----|--------------------------|------|-------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 34  | GPI05                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)                                                     |  |

| 35  | GPI06                    | 1/0  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)                                                     |  |

| 36  | SDA1                     | I/O  | 3.3                     | 8 - OD                    | Two-Wire Serial data Port 1. Bidirectional signal used by both the master and slave controllers for data transport.                                                                                            |  |

| 37  | SCL1                     | 1/0  | 3.3                     | 8 - OD                    | Two-Wire Serial clock Port 1. Bidirectional signal is used by both the master and slave controllers for clock signaling.                                                                                       |  |

| 38  | PROTECT9                 | 1/0  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                                                           |  |

| 39  | SPDIFRX1                 | I    | 3.3                     |                           | S/PDIF Digital audio data input 1                                                                                                                                                                              |  |

| 40  | SPDIFRX0                 | I    | 3.3                     |                           | S/PDIF Digital audio data input 0                                                                                                                                                                              |  |

| 41  | SPDIFTX                  | 0    | 3.3                     | 4                         | S/PDIF Digital audio output. (Audio content and audio processing signal flow is dependent upon firmware, driving stereo output up to 192kHz.)                                                                  |  |

| 42  | TEST                     | ı    | 3.3                     |                           | Factory test use only. Must be tied low.                                                                                                                                                                       |  |

| 43  | IRQA                     | I    | 3.3                     |                           | Interrupt request Port A, Boot Mode Select. One of 4 IRQ pins. Connects to logic high (3.3V) or to ground and High/Low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle. |  |

| 44  | IRQB                     | I    | 3.3                     |                           | Interrupt request Port B, Boot Mode Select. One of 4 IRQ pins. Connects to logic high (3.3V) or to ground and High/Low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle. |  |

| 45  | IRQC                     | I    | 3.3                     |                           | Interrupt request Port C, Boot Mode Select. One of 4 IRQ pins. Connects to logic high (3.3V) or to ground and High/Low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle. |  |

| 46  | IRQD                     | I    | 3.3                     |                           | Interrupt request Port D, Boot Mode Select. One of 4 IRQ pins. Connects to logic high (3.3V) or to ground and High/Low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle. |  |

| 47  | TIO2                     | 1/0  | 3.3                     | 16                        | Timer I/O Port 2. Operation and assignment is controlled by firmware. Leave unconnected when not in use.                                                                                                       |  |

| 48  | CVDD                     | Р    | 3.3                     |                           | Core power, 1.8V                                                                                                                                                                                               |  |

| 49  | CVDD                     | Р    | 3.3                     |                           | Core power, 1.8V                                                                                                                                                                                               |  |

| 50  | CGND                     | Р    | 3.3                     |                           | Core ground                                                                                                                                                                                                    |  |

| 51  | CGND                     | Р    | 3.3                     |                           | Core ground                                                                                                                                                                                                    |  |

| 52  | RGND                     | Р    | 3.3                     |                           | Digital pad ring ground. Internally connected to PWMGND.                                                                                                                                                       |  |

| 53  | RVDD                     | Р    | 3.3                     |                           | Digital pad ring power, 3.3V. This 3.3V supply is used for all the digital I/O pad drivers and receivers, except for the analog pads. Internally connected to PWMVDD.                                          |  |

| 54  | PUMPHI                   | I/O  | 3.3                     | 16                        | Assignable I/O. Function and operation defined by firmware.                                                                                                                                                    |  |

| 55  | PUMPLO                   | I/O  | 3.3                     | 16                        | Assignable I/O. Function and operation defined by firmware.                                                                                                                                                    |  |

| 56  | PSSYNC                   | I/O  | 3.3                     | 16                        | Synchronizing output signal to switching power supply. (Operates under specification of firmware and resets to high impedance inactive state when not used.)                                                   |  |

| 57  | PSTEMP                   | I/0  | 3.3                     | 4                         | Assignable I/O. Function and operation defined by firmware.                                                                                                                                                    |  |

| 58  | PSCURR                   | I/O  | 3.3                     | 4                         | Assignable I/O. Function and operation defined by firmware.                                                                                                                                                    |  |

| 59  | PWMSYNC                  | I/O  | 3.3                     | 16                        | PWM synchronization port. (Function and operation is defined by firmware.)                                                                                                                                     |  |

| 60  | PROTECT3                 | 1/0  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                                                           |  |

Submit Document Feedback 13 intersil FN6787.3 May 17, 2016

| PIN | PIN<br>NAME<br>(Note 18) | TYPE | VOLTAGE<br>LEVEL<br>(V) | DRIVE<br>STRENGTH<br>(mA) | DESCRIPTION                                                                                                                                                           |  |

|-----|--------------------------|------|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 61  | PROTECT4                 | 1/0  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                  |  |

| 62  | PROTECT5                 | I/O  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                  |  |

| 63  | PROTECT6                 | I/O  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                  |  |

| 64  | PROTECT7                 | I/0  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                  |  |

| 65  | PROTECT2                 | I/O  | 3.3                     | 4                         | PWM protection input with hysteresis. (One of 9 protection inputs. Specific function and channel assignment is defined by firmware.)                                  |  |

| 66  | GPI01                    | I/O  | 3.3                     | 16                        | General purpose I/O Bidirectional GPIO port. (One of 8 GPIO. Resets to input port. Operation and assignment is defined by product application's firmware.)            |  |

| 67  | RVDD                     | Р    | 3.3                     |                           | Digital pad ring power, 3.3V. This 3.3V supply is used for all the digital I/O pad drivers and receivers, except for the analog pads. Internally connected to PWMVDD. |  |

| 68  | RGND                     | Р    | 3.3                     |                           | Digital pad ring ground. Internally connected to PWMGND.                                                                                                              |  |

| 69  | CGND                     | Р    | 3.3                     |                           | Core ground                                                                                                                                                           |  |

| 70  | CVDD                     | Р    | 3.3                     |                           | Core power, 1.8V                                                                                                                                                      |  |

| 71  | PWMGND                   | Р    | 3.3                     |                           | PWM output pin ground. Internally connected to RGND.                                                                                                                  |  |

| 72  | PWM17                    | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 73  | PWM16                    | I/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 74  | PWM15                    | 1/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 75  | PWM14                    | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 76  | PWMVDD                   | Р    | 3.3                     |                           | PWM output pin power. This 3.3V supply is used for the PWM pad drivers. Internally connected to RVDD.                                                                 |  |

| 77  | PWMGND                   | Р    | 3.3                     |                           | PWM output pin ground. Internally connected to RGND.                                                                                                                  |  |

| 78  | PWM13                    | 1/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 79  | PWM12                    | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 80  | PWM11                    | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 81  | PWM10                    | 1/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 82  | PWM9                     | I/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 83  | PWM8                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

| 84  | PWMVDD                   | Р    | 3.3                     |                           | PWM output pin power. This 3.3V supply is used for the PWM pad drivers. Internally connected to RVDD.                                                                 |  |

| 85  | PWMGND                   | Р    | 3.3                     |                           | PWM output pin ground. Internally connected to RGND.                                                                                                                  |  |

| 86  | PWM7                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                 |  |

Submit Document Feedback 14 intersil FN6

| PIN | PIN<br>NAME<br>(Note 18) | TYPE | VOLTAGE<br>LEVEL<br>(V) | DRIVE<br>STRENGTH<br>(mA) | DESCRIPTION                                                                                                                                                                                  |  |

|-----|--------------------------|------|-------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |                          |      |                         | , ,                       |                                                                                                                                                                                              |  |

| 87  | PWM6                     | 1/0  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 88  | PWM5                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 89  | PWM4                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 90  | PWMVDD                   | Р    | 3.3                     |                           | PWM output pin power. This 3.3V supply is used for the PWM pad drivers. Internally connected to RVDD.                                                                                        |  |

| 91  | PWMGND                   | Р    | 3.3                     |                           | PWM output pin ground. Internally connected to RGND.                                                                                                                                         |  |

| 92  | PWM3                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 93  | PWM2                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 94  | PWM1                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 95  | PWM0                     | I/O  | 3.3                     | 8 or 16                   | PWM output pin. (One of 18 PWM output pins. Channel and operation assignment is defined by firmware.)                                                                                        |  |

| 96  | PWMVDD                   | Р    | 3.3                     |                           | PWM output pin power. This 3.3V supply is used for the PWM pad drivers. Internally connected to RVDD.                                                                                        |  |

| 97  | OSCOUT                   | Р    | 1.8                     |                           | Analog oscillator output to slave D2-926xx devices. OSCOUT drives a buffered version of the crystal oscillator signal from the XTALI pin.                                                    |  |

| 98  | PLLAGND                  | Р    | 1.8                     |                           | PLL Analog ground                                                                                                                                                                            |  |

| 99  | PLLTESTB                 | 0    | 1.8                     |                           | Factory test use only. Must be tied low.                                                                                                                                                     |  |

| 100 | PLLTESTA                 | 0    | 1.8                     |                           | Factory test use only. Must be tied low.                                                                                                                                                     |  |

| 101 | XTALI                    | Р    | 1.8                     |                           | Crystal oscillator analog input port. An external clock source would be driven into the this port. In multi-D2-926xx systems, the OSCOUT from the master D2-926xx would drive the XTALI pin. |  |

| 102 | XTALO                    | Р    | 1.8                     |                           | Crystal oscillator analog output port. When using an external clock source, this pin must be open. XTALO does not have a drive strength specification.                                       |  |

| 103 | PLLAVDD                  | Р    | 1.8                     |                           | PLL Analog power, 1.8V                                                                                                                                                                       |  |

| 104 | ADCVDD                   | Р    | 3.3                     |                           | Analog power for internal ADC, 3.3V                                                                                                                                                          |  |

| 105 | AIN1                     | ı    | 3.3                     |                           | Analog input 1 to internal ADC                                                                                                                                                               |  |

| 106 | ADCREF                   | 0    | 3.3                     |                           | Analog voltage reference output. Must be de-coupled to analog ground with 1µF capacitor.                                                                                                     |  |

| 107 | AINO                     | ı    | 3.3                     |                           | Analog input 0 to internal ADC                                                                                                                                                               |  |

| 108 | ADCGND                   | Р    | 3.3                     |                           | Analog ground for internal ADC                                                                                                                                                               |  |

| 109 | nTRST                    | ı    | 3.3                     |                           | Factory test only. Must be tied high at all times.                                                                                                                                           |  |