## 8-Channel 6.25Gbps Serial RapidIO™ Signal Repeater

## 89HP0608R Data Sheet

#### Device Overview

The IDT 89HP0608R (P0608R) is a 1.25Gbps to 6.25Gbps Repeater IC that reconditions high-speed serial data streams. The device features IDT EyeBoost™ technology that compensates for cable and board trace attenuations and ISI jitter, thereby extending connection reach. The device is optimized for Serial RapidIO (SRIO) high-speed, serial differential data streams and contains eight data channels, each able to process up to 6.25Gbps transmission rates. Each channel consists of an input equalizer and amplifier, signal detection with glitch filter, as well as programmable output swing, slew rate, and de-emphasis with delay control. Since all of these features are user programmable, they allow for application specific optimization.

Besides the per channel programmable features, the P0608R provides global programmable settings - termination resistance values and transfer modes. The P0608R, with its many programmable receiver and transmitter features, is ideal for applications using any combination of cables and board trace materials.

All modes of active data transfer are designed with minimized power consumption. Also, a wide selection of power reducing modes allows the user to eliminate power of unused blocks, including a shutdown mode. In full shutdown mode, the part consumes less than 80mW in worst case environmental conditions.

## **Applications**

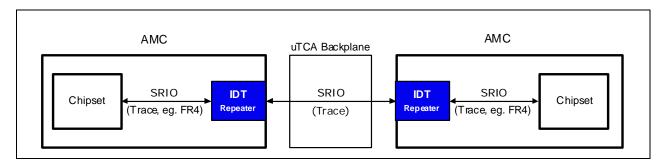

- ♦ ATCA, μTCA

- Military, industrial, and imaging systems

- ◆ Open VPX and VITA 41/46 systems

#### **Features**

- Compensates for cable and PCB trace attenuation and ISI iitter

- Programmable receiver equalization up to 30db

- Programmable de-emphasis up to -8.5dB

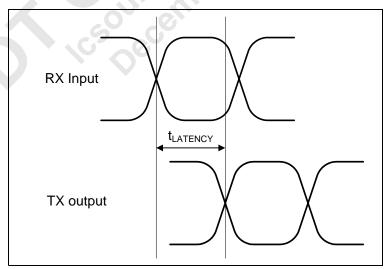

- Minimized in-out latency of 300ps typical

- Recovers data stream even when the differential signal eye is completely closed due to trace attenuation and ISI jitter

- ◆ Full SRIO protocol support

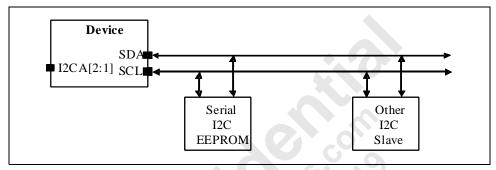

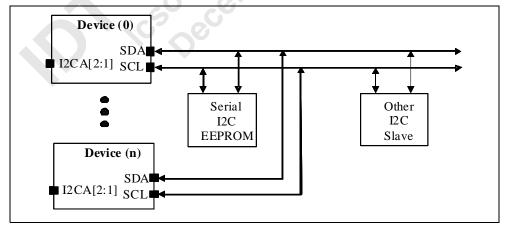

- ◆ Configurable via I<sup>2</sup>C interface

- Supports automatic download of configuration from external EEPROM with a single or multiple repeaters on I2C bus

- Leading edge power minimization in active and shutdown modes

- No external bias resistors or reference clocks required

- Channel mux mode, demux mode, 1 to 2 channels multicast, and Z-switch function mode

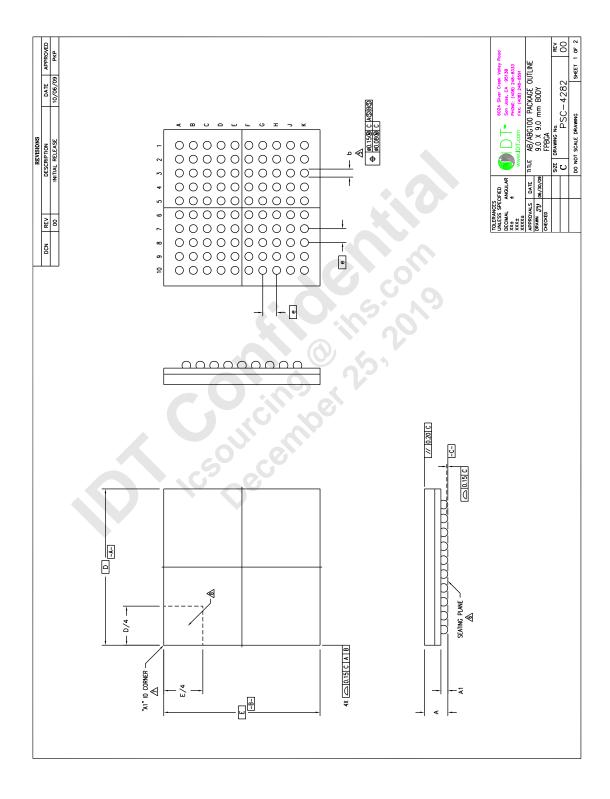

- ◆ Available in a 9x9mm 100-ball FPBGA package

#### Benefits

- Extends maximum cable length to over 10 meters and trace length over 65 inches in SRIO applications (short/medium/ long range and beyond long range)

- Speeds up system design time by allowing usage of longer trace and cable lengths

- Minimizes BER

## Typical Application

Figure 1 IDT Repeaters in µTCA

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

## P0608R SRIO Compliance

The device was designed to provide end users with features needed to comply with SRIO system application requirements. It meets SRIO 2.1 specifications for DC and AC requirements as detailed in the Electrical Specifications section.

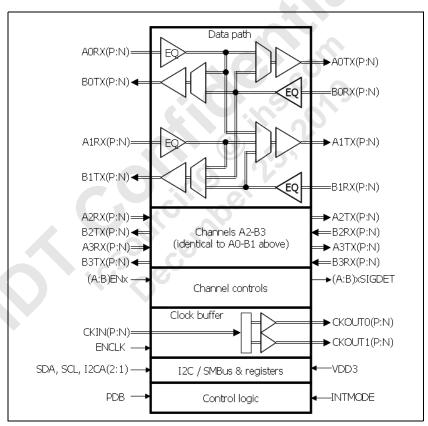

## P0608R Block Diagram

The P0608R contains eight high speed channels as shown in Figure 2. Each channel can routed to different outputs. Depending on user configuration via mode selections, input traffic can be muxed, demuxed, or looped back. Please, refer to modes of operation chapter for details. To facilitate buffering of system clocks, the repeater provides 1:2 clock buffer as shown in the figure below. Powerdown (PDB) and Channel Enable (AEN0, etc.) pins are provided for easy state and channel control. Status output pins are available for monitoring critical states, such as the detection of high speed input signals (A0SIGDET, etc.).

Each channel's configuration and performance can be optimized via the I<sup>2</sup>C interface (SCL, SDA). The programming option allows the user to optimize the repeater's performance in a wide range of applications, making it an ideal solution for most applications requiring cancellation of trace or cable attenuation and ISI jitter.

Figure 2 P0608R Block Diagram

# **Table of Contents**

| Device Overview                                       |    |

|-------------------------------------------------------|----|

| Applications                                          |    |

| Features                                              | 1  |

| Benefits                                              | 1  |

| Typical Application                                   | 1  |

| P0608R SRIO Compliance                                | 2  |

| P0608R Block Diagram                                  |    |

| Data Units                                            |    |

| Register Terminology                                  | 5  |

| Functional Description                                |    |

| Power-Up                                              |    |

| Power-Up/Power-Down Sequencing                        |    |

| IDT EyeBoost™ Technology                              | 7  |

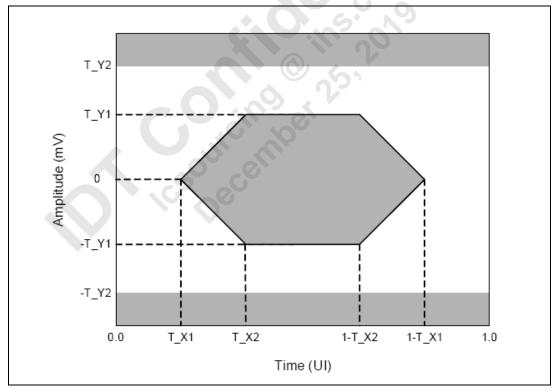

| Eye Diagram Parameters                                | 8  |

| Modes of Operation                                    |    |

| Channel Muxing                                        |    |

| I2C Registers                                         |    |

| I2C Register Description Summary                      |    |

| Global Control Register (address offset=12h)          |    |

| Test Control Register — Reserved (address offset=13h) |    |

| I2C Status Register (I2CSTS) (address offset=14h)     |    |

| I2C Control Register (I2CCTL) (address offset=15h)    |    |

| EEPROM Control Register (address offset=16h)          |    |

| Serial Interface                                      |    |

| I2C Slave Mode                                        |    |

| I2C Master Interface                                  |    |

| Electrical Specifications                             |    |

| Absolute Maximum Ratings                              |    |

| Recommended Operating Conditions                      |    |

| Power Consumption                                     |    |

| Package Thermal Considerations                        |    |

| DC Specifications                                     |    |

| AC Specifications                                     |    |

| Reference Clock Specifications                        |    |

| I2C Specifications                                    |    |

| Pin Description                                       |    |

| Package Pinout — 100-BGA Signal Pinout for the P0608R |    |

| P0608R Pin Diagram                                    |    |

| FPBGA Package Dimension                               |    |

| FPBGA Package Dimension — Page Two                    |    |

| Revision History                                      |    |

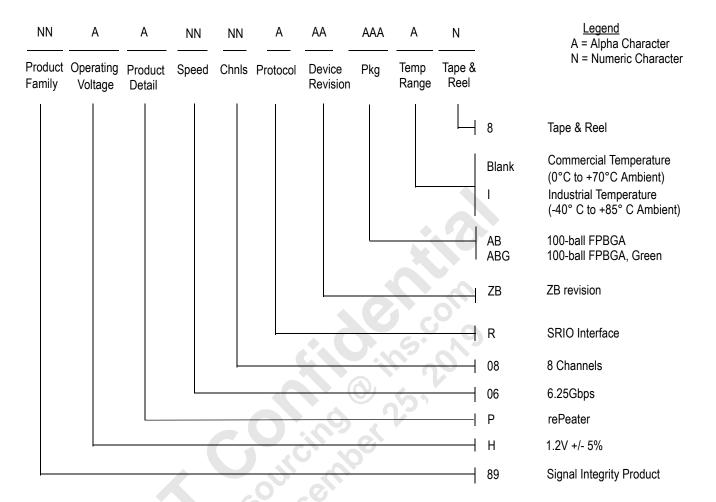

| Ordering Information                                  | 55 |

PAGE INTENTIONALLY LEFT BLANK

### Data Units

The following data unit terminology is used in this document.

| Term               | Words | Bytes | Bits |

|--------------------|-------|-------|------|

| Byte               | 1/2   | 1     | 8    |

| Word               | 1     | 2     | 16   |

| Doubleword (DWord) | 2     | 4     | 32   |

Table 1 Data Unit Terminology

In doublewords, bit 31 is always the most significant bit and bit 0 is the least significant bit. In words, bit 15 is always the most significant bit and bit 0 is the least significant bit. In bytes, bit 7 is always the most significant bit and bit 0 is the least significant bit.

## Register Terminology

Software in the context of this register terminology refers to modifications made by PCI Express root configuration writes, writes to registers made through the slave SMBus interface, or serial EEPROM register initialization. See Table 2.

| Туре                 | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Initialized | HWINIT       | Register bits are initialized by firmware or hardware mechanisms such as pin strapping or serial EEPROM. (System firmware hardware initialization is only allowed for system integrated devices.) Bits are read-only after initialization and can only be reset (for write-once by firmware) with reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Read Only and Clear  | RC           | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bit to be reset to zero. Writing to a RC location has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Read Clear and Write | RCW          | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bits to be reset to zero. Writes cause the register/bits to be modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Reserved             | Reserved     | The value read from a reserved register/bit is undefined. Thus, software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions are preserved. That is, the values for other bit positions and then written back.  In addition to reserved registers, some valid register fields have encodings marked as reserved. Such register fields must never be written with a value corresponding to an encoding marked as reserved. Violating this rule produces undefined operation in the device. |

| Read Only            | RO           | Software can only read registers/bits with this attribute. Contents are hardwired to a constant value or are status bits that may be set and cleared by hardware. Writing to a RO location has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 2 Register Terminology (Part 1 of 2)

| Туре                         | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read and Write               | RW           | Software can both read and write bits with this attribute.                                                                                                                                                                                                                                                                                                     |

| Read and Write Clear         | RW1C         | Software can read and write to registers/bits with this attribute. However, writing a value of zero to a bit with this attribute has no effect. A RW1C bit can only be set to a value of 1 by a hardware event. To clear a RW1C bit (i.e., change its value to zero) a value of one must be written to the location. An RW1C bit is never cleared by hardware. |

| Read and Write when Unlocked |              | Software can read the register/bits with this attribute. Writing to register/bits with this attribute will only cause the value to be modified if the REGUNLOCK bit in the SWCTL register is set. When the REGUNLOCK bit is cleared, writes are ignored and the register/bits are effectively read-only.                                                       |

Table 2 Register Terminology (Part 2 of 2)

## **Functional Description**

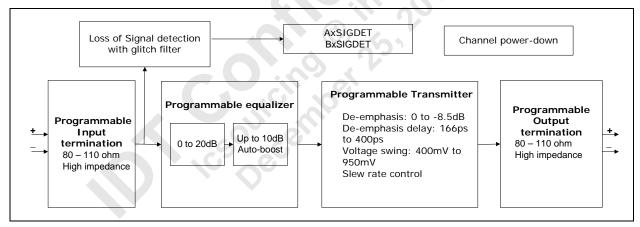

The P0608R has 8 channels, each with the individually programmable features listed below. Figure 3 diagrams the channel and Tables 3 and 4 summarize key configuration options.

Figure 3 Channel Block Diagram with Channel Features

- ◆ Per-channel programmable features used at the RX side (ranges refer to I<sup>2</sup>C programming method).

- Input equalization with 11 levels: 0 to 20dB compensation for high frequency signal attenuation due to cables and board traces. Additionally, up to 10dB boost is added automatically by the equalizer for applications using long cables. The total equalization range is between 0dB and 30dB.

- Input amplifier DC gain with 7 levels: -2dB to -14dB plus 4 levels for further tuning: -3db to 3dB. The total DC gain is the sum of 7-level gain and 3-level gain controls. This function can be useful for input signals with large swing.

- Input loss of signal detection with 8 levels: 50mV pk-pk to 170mV pk-pk. Measures the envelope of the incoming differential signal (peak-to-peak) and puts the device in loss of signal mode when the envelope has fallen below a programmable threshold. In loss of signal mode, the transmitter stops toggling, and maintains its common-mode voltage level.

Note: It is recommended to disable the Loss of Signal for typical SRIO applications not requiring loss-of-signal detection by programming both SIG PD TRANDET and SIG PD LVLDET bits to 1.

- Input loss of signal detection glitch filter with 4 levels: 2.6ns to 4ns negative glitch removal avoids detection of extremely short spurious signal losses. This is an advanced feature with suggested default setting for most users.

- Input high impedance control via channel enable: disabled (active mode) and hi-Z (power-down).

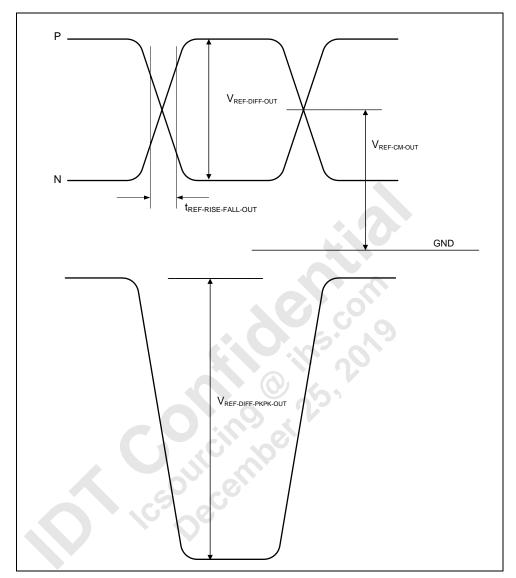

- Per-channel programmable features used at the TX side.

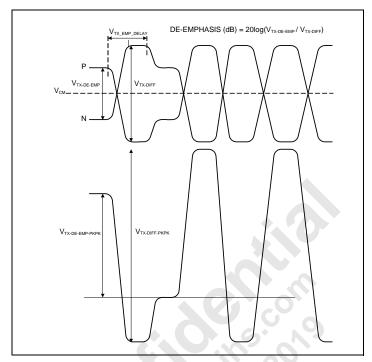

- Output de-emphasis with 8 levels: 0 to -8.5dB. The de-emphasis boosts the magnitude of higher frequencies sent by the transmitter to compensate for high frequency losses travelling through output side cable or output side board traces. This ensures that the final received signal has a wider eye opening.

- Output differential swing with 8 levels: 0.4V to 0.95V (peak-to-peak).

- Output slew rate with 4 levels: 45ps to 150ps.

- Output de-emphasis delay control with 4 levels: 166ps to 400ps. When used, this feature should be set to a value of 1UI, which is 166ps for 6Gbps rate, 200ps for 5Gbps rate, 333ps for 3Gbps rate, and 400ps for 2.5Gbps.

- Individual channel power-down (includes Rx and Tx power-down).

In addition, the device contains global programmable settings:

- Input and output differential termination resistance with 4 levels: 80 ohm, 90 ohm, 100 ohm, 110 ohm.

- Transfer modes: direct connect, cross-connect, multicast, and loopback.

#### Power-Up

After the power supplies reach their minimum required levels, the P0608R powers up by setting all input and output pins to known states:

- All the device's input configuration pins are set internally to VSS or VDD for 2-level pins and to VDD/2 for 3-level pins.

- High speed differential input and output pins, status output pins indicating signal detection at high speed inputs, and signal detection outputs depend on various conditions described below:

- High speed differential input and output pins are in high impedance if any of the following conditions is true:

- Powerdown is set (PDB pin = 0V) or

- · Channels containing high speed differential inputs are disabled via pins (eg. A0EN) or

In all other cases, high speed differential input and output pins are set to 50 ohms per pin, with 100 ohms differential impedance. Also refer to Table 5, Power Reducing Modes.

- Status output pins indicating signal detection at high speed inputs (A0SIGDET, A1SIGDET, etc.) are at 0V if:

- · Corresponding (A0, A1, etc.) channel inputs do not swing or swing below the programmed threshold levels or

- · Corresponding channel enable pins (A0EN, A1EN, etc.) are at 0V or

- Powerdown is set (PDB pin = 0V)

- In all other cases, these output pins are at VDD level.

- Other power-up settings:

- If INTMODE=VSS then the programming pins are ignored and the register values are used for programming P0608R settings (I<sup>2</sup>C slave mode).

- If INTMODE=VDD then the P0608R is in I<sup>2</sup>C master mode (used when external EEPROM is needed).

#### Power-Up/Power-Down Sequencing

To avoid potential damage to the part, adhere to the following sequence during power supply ramp-up:

- VDD3 supply must be ramped-up and stable at 3.3V prior to VDD supply reaching 1.2V

- Power ramp-up time for VDD should be less than 1ms to avoid potential I<sup>2</sup>C reset issues.

Note: VDD3 supply should be common to all devices communicating on the same I<sup>2</sup>C bus.

The power-down sequence can occur in any order.

### IDT EyeBoost™ Technology

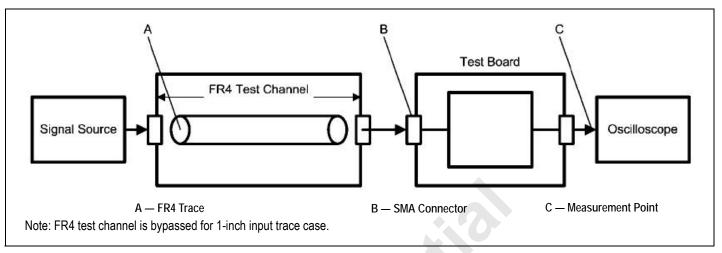

IDT EyeBoost™ technology is a method of data stream recovery of data stream even when the differential signal eye is completely closed due to cable or trace attenuation and ISI jitter. With IDT EyeBoost™ technology<sup>™</sup>, the system designer can both recover the incoming data and retransmit it to target device with a maximized eye width and amplitude. An example of IDT EyeBoost™ technology usage in a system application and eye diagram results are shown in Figure 4. In this figure, the (a) diagram shows incoming differential signal (closed eye) after 62 inch FR4 connection from signal source and the (b) diagram shows differential signal at the output of repeater maximized eye opening with IDT EyeBoost™ technology.

Figure 4 Eye Diagram

## Eye Diagram Parameters

| Feature                                                                | Feature Type                            | Parameter Names for<br>Programming via I <sup>2</sup> C                               |

|------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|

| Input equalization                                                     | Main eye optimization                   | EQ<br>Range: 0dB to 20dB (plus additional auto-boost up to 10dB for long connections) |

| Input equalization data rate                                           | Main eye optimization                   | EQDATARATE<br>Range: 2.5Gbps to 8Gbps                                                 |

| Output de-emphasis                                                     | Main eye optimization                   | TX_DEEMP<br>Range: 0dB to -8.5dB                                                      |

| Output differential signal swing (peak-to-peak)                        | Main eye optimization                   | TX_SWING<br>Range: 0.4V to 0.95V                                                      |

| Output slew rate                                                       | Main eye optimization                   | TX_SLEW<br>Range: 45ps to 150ps                                                       |

| Output de-emphasis delay                                               | Main eye optimization                   | TX_EMP_DELAY<br>Range: 166ps to 400ps                                                 |

| DC gain of Input amplifier                                             | Eye optimization for large swing inputs | DC_GAIN<br>Range: -2dB to -14dB                                                       |

| Equalizer DC gain                                                      | Eye optimization for large swing inputs | EQDCGAIN<br>Range: -3dB to 3dB                                                        |

| Limiting Amplifier swing (intermediate stage)                          | Fine optimization                       | LA_SWING<br>Range: 560mV to 840mV                                                     |

| Output de-emphasis<br>delay cell offset cancella-<br>tion loop control | Fine optimization                       | TX_OC_ENA<br>Range: enable / disable                                                  |

| Channel speed control optimization                                     | Fine optimization                       | CHEN<br>Range: Disable and 3Gpbs to<br>6Gbps                                          |

Table 3 Quick Reference: Parameters Used for Eye Optimization

| Feature                                                                                                    | Feature Type | Parameter Names for Programming via I <sup>2</sup> C                 |

|------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

| Rx loss of signal detec-<br>tion threshold used for<br>loss of signal mode, dif-<br>ferential peak-to-peak | NA           | SIG_THRESH<br>Range: 50mV to 170mV                                   |

| Input and output differential termination resistance                                                       | NA           | TERM_CTL<br>Range: 80 ohm to 110 ohm                                 |

| Minimum loss of signal detection glitch removal                                                            | NA           | SIG_GLITCHRM<br>Range: 2.6ns to 4ns                                  |

| Channel transfer mode                                                                                      | NA           | CTRL options: multicast, direct-<br>connect, cross-connect, loopback |

Table 4 Quick Reference: Parameters Used for Functions other than Eye Optimization

#### Modes of Operation

The device supports several data transfer modes, loss of signal mode, loopback mode, and several power reducing modes.

#### **Loss of Signal Mode**

In loss of signal mode, the transmitter stops toggling and maintains its common-mode voltage level. The device enters loss of signal mode when the envelope of the incoming signal on a given channel has fallen below a programmable threshold level. This feature is not required for typical SRIO applications and should be disabled via Global Control register (address offset=12h) by setting bits 21 and 22 to 1.

#### **Power Reducing Modes**

The Repeater supports three power-down states and one active state as shown in Table 5. The user can choose between full chip power-down, channel based power-down, and one loss of signal mode. Power reducing modes can be selected via PDB and channel enable pins (A0EN, A1EN, etc.).

|                                                                         | Re                 | quired Signa          |                         |                                                                                                                                                                                 |

|-------------------------------------------------------------------------|--------------------|-----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         | Power-Down Control |                       | Signal Detect<br>Status |                                                                                                                                                                                 |

| Power<br>Reducing Mode                                                  | Global             | Per<br>Channel        | A[1:0]SIGDET,           | State Description                                                                                                                                                               |

|                                                                         | PDB                | A[1:0]EN,<br>B[1:0]EN | B[1:0]SIGDET            |                                                                                                                                                                                 |

| Full IC power-down                                                      | 0                  | Х                     | X                       | All channels are powered-down Rx termination is set to Hi-Z Tx termination is set to $1 \text{k}\Omega$ Tx common-mode is at VDD                                                |

| Individual channel power-down                                           | Х                  | 0                     | X                       | Rx termination is set to Hi-Z Tx termination is set to $1k\Omega$ Tx common-mode is at VDD                                                                                      |

| Channel enabled but inactive (loss of signal). Rx and Tx set to 50 Ohms | 1                  | 1                     |                         | Tx output is squelched if loss of signal is detected Receiver terminations set to $50\Omega$ Output common-mode is held at its active value Tx termination is set to $50\Omega$ |

| Channel enabled and active. No power-down                               | 1                  | 1                     | 15                      | Tx output is active Receiver terminations set to $50\Omega$ Transmitter terminations set to $50\Omega$                                                                          |

Table 5 Power Reducing Modes

#### **Loopback Mode**

The P0608R fully supports data loopbacks on all channels via I<sup>2</sup>C using the CTRL register. Refer to Table 13 for this parameter setting. While the device is in the loopback mode, all channels are enabled regardless of the A0/B0/A1/B1EN setting. Signal detect signals can also be looped back.

Figure 5 Diagram of P0608R Configuration in Loopback Mode

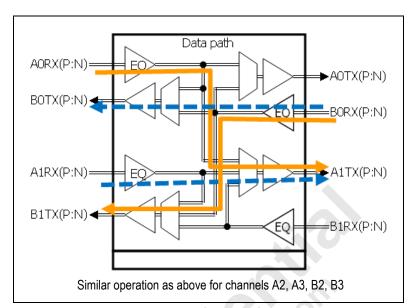

#### **Channel Muxing**

The P0608R repeater permits a variety of muxing, demuxing, and switching configurations. These configurations require the selection of specific pins for input and output ports. In the following sections, each configuration is described in terms of pin connectivity to external upstream and downstream devices. The configurations shown are those often used in system designs:

- Uni-directional 2:1 Mux (1 or 2 instances)

- Uni-directional 1:2 De-Mux (1 or 2 instances)

- Bi-directional 2:1 Mux/De-Mux

- Bi-directional Z-function (also called Partial Cross Function)

Channels A0, A1, B0, B1 programming via CTRL requires setting I2CA0=0 in the slave I2C address. Channels A2, A3, B2, B3 programming via CTRL requires setting I2CA0=1. Refer to the Serial Interface section for details.

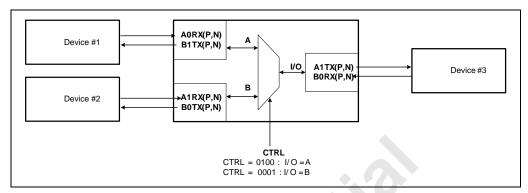

The P0608R supports channel muxing in both upstream and downstream channel directions via the mode control bits, CTRL, in the Global Control Register (address offset=12h). Figure 6 shows the channel/reference muxing modes and Tables 6 and 7 show how CTRL bits allow for various modes of data transfers: Multicast mode, Direct-connect, and Cross-connect, and Cross-connect modes are used to build uni-directional and bi-directional 2:1 mux and Z-switch functions.

While the part is in Multicast or Cross-connect mode, all channels are enabled regardless of the A0/B0/A1/B1EN setting.

Figure 6 Diagram of Channel/Reference Muxing Modes

| Input Pins                            |           |           |           |           | Outpu     | ıt Pins   |           |           |

|---------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| CTRL                                  | AORX[P,N] | A1RX[P,N] | BORX[P,N] | B1RX[P,N] | AOTX[P,N] | A1TX[P,N] | BOTX[P,N] | B1TX[P,N] |

| CTRL=0010<br>(Multicast Mode)         | A0 DATA   | X         | B0 DATA   | X         | A0 DATA   | A0 DATA   | B0 DATA   | B0 DATA   |

| CTRL=0001<br>(Direct-Connect<br>Mode) | A0 DATA   | A1 DATA   | B0 DATA   | B1 DATA   | A0 DATA   | A1 DATA   | B0 DATA   | B1 DATA   |

| CTRL=0100<br>(demux Mode)             | A0 DATA   | X         | B0 DATA   | Х         | Squelched | A0 DATA   | Squelched | B0 DATA   |

Table 6 Description of Channel Muxing/De-Muxing Functionality — Channels A0, A1, B0, B1

| I-                                    |           |           |           |           |             |           |           |           |

|---------------------------------------|-----------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|

| Input Pins                            |           |           |           |           | Output Pins |           |           |           |

| CTRL                                  | A2RX[P,N] | A3RX[P,N] | B2RX[P,N] | B3RX[P,N] | A2TX[P,N]   | A3TX[P,N] | B2TX[P,N] | B3TX[P,N] |

| CTRL=0010<br>(Multicast Mode)         | A2 DATA   | Х         | B2 DATA   | Х         | A2 DATA     | A2 DATA   | B2 DATA   | B2 DATA   |

| CTRL=0001<br>(Direct-Connect<br>Mode) | A2 DATA   | A3 DATA   | B2 DATA   | B3 DATA   | A2 DATA     | A3 DATA   | B2 DATA   | B3 DATA   |

| CTRL=0100<br>(demux Mode)             | A2 DATA   | Х         | B2 DATA   | Х         | Squelched   | A2 DATA   | Squelched | B2 DATA   |

Table 7 Description of Channel Muxing/De-Muxing Functionality — Channels A2, A3, B2, B3

The signal detect output pins support the functionality shown in Tables 8 and 9.

| Input Pins                            |           |           |           |           |                        | Output F               | Pin Value                 |                        |

|---------------------------------------|-----------|-----------|-----------|-----------|------------------------|------------------------|---------------------------|------------------------|

| CTRL                                  | AORX[P,N] | A1RX[P,N] | BORX[P,N] | B1RX[P,N] | AOSIGDET               | A1SIGDET               | BOSIGDET                  | B1SIGDET               |

| CTRL=0010<br>(Multicast Mode)         | A0 Data   | A1 Data   | B0 Data   | B1 Data   | Based on<br>A0RX Swing | 0                      | Based on<br>B0RX Swing    | 0                      |

| CTRL=0001<br>(Direct-Connect<br>Mode) | A0 Data   | A1 Data   | B0 Data   | B1 Data   | Based on<br>A0RX Swing | Based on<br>A1RX Swing | Based on<br>B0RX<br>Swing | Based on<br>B1RX Swing |

| CTRL=0100<br>(demux Mode)             | A0 Data   | Х         | B0 Data   | Х         | Based on<br>A0RX Swing | 0                      | Based on BORX Swing       | 0                      |

Table 8 Description of Signal Detect Muxing/De-Muxing Functionality — Channels A0, A1, B0, B1

| Input Pins                            |           |           |           |           |                        | Output F               | Pin Value                 |                        |

|---------------------------------------|-----------|-----------|-----------|-----------|------------------------|------------------------|---------------------------|------------------------|

| CTRL                                  | A2RX[P,N] | A3RX[P,N] | B2RX[P,N] | B3RX[P,N] | A2SIGDET               | A3SIGDET               | B2SIGDET                  | B3SIGDET               |

| CTRL=0010<br>(Multicast Mode)         | A2 Data   | A3 Data   | B2 Data   | B3 Data   | Based on<br>A2RX Swing | 0                      | Based on<br>B2RX Swing    | 0                      |

| CTRL=0001<br>(Direct-Connect<br>Mode) | A2 Data   | A3 Data   | B2 Data   | B3 Data   | Based on<br>A2RX Swing | Based on<br>A3RX Swing | Based on<br>B2RX<br>Swing | Based on<br>B3RX Swing |

| CTRL=0100<br>(demux Mode)             | A2 Data   | X         | B2 Data   | X         | Based on<br>A2RX Swing | 0                      | Based on<br>B2RX Swing    | 0                      |

Table 9 Description of Signal Detect Muxing/De-Muxing Functionality — Channels A2, A3, B2, B3

The following sections describe a system implementation of mux, demux, and Z-switch functions for channels A0, A1, B0, B 1. Analogous implementations can be applied to channels A2, A3, B2, B3 by programming those channels to the desired function via CTRL bits. For example, 2:1 mux from Figure 7 would have A2RX(P,N) and A3RX(P,N) ports on the left side and A3TX(P,N) port on the right side.

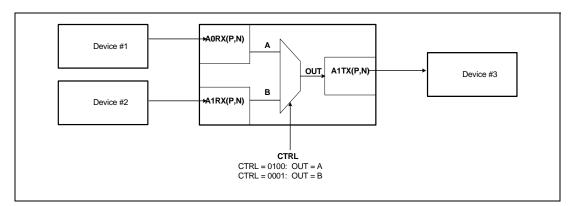

#### Uni-directional 2:1 Mux or Two Instances of Unidirectional 2:1 Mux

This function can be achieved by using the CTRL bits in the Global Control Register. The ports should be configured as indicated in Figure 7.

Figure 7 Implementation of Unidirectional 2:1 Mux

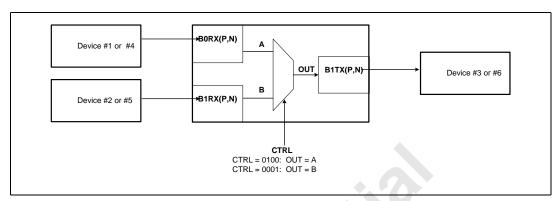

As an alternative, different chip channels can also be selected as shown in Figure 8. This solution can be combined with the previous one to obtain two instances of Uni-directional 2:1 Mux.

Figure 8 Implementation of Second Instance of Unidirectional 2:1 Mux

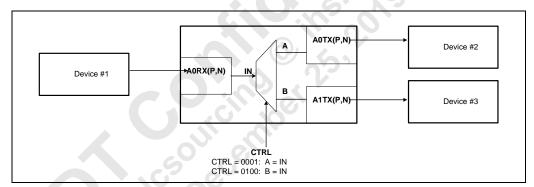

#### Uni-directional 1:2 De-mux or Two Instances of Unidirectional 1:2 De-Mux

This function can be achieved by using CTRL pin as a de-mux control signal. CTRL should be set to either 0001 or 0100. The ports should be configured as shown in Figure 9.

Figure 9 Implementation of Unidirectional 1:2 De-Mux

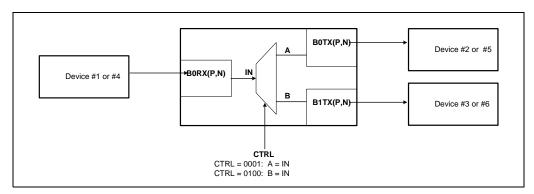

As an alternative, different chip channels can also be selected as shown in Figure 10. This solution can be combined with the previous one to obtain two instances of Uni-directional 1:2 De-Mux.

Figure 10 Implementation of Second Instance of Unidirectional 1:2 De-Mux

#### **Bi-directional 2:1 Mux/De-Mux**

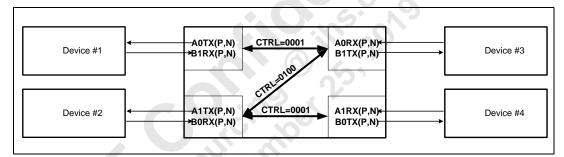

The bi-directional Mux and De-Mux function can also be achieved by using the CTRL bits. The ports should be configured as shown in Figure 11.

Figure 11 Implementation of Bi--directional 2:1 Mux/De-Mux

## **Bi-directional Z-function (also called Partial Cross Function)**

This function can also be achieved by using the CTRL bits. The ports should be configured as shown in Figure 12.

Figure 12 Implementation of Z-function

## I<sup>2</sup>C Registers

## I<sup>2</sup>C Register Description Summary

Table 10 provides a summary of the P0608R register set. Registers are organized as 4-bytes (Dword). Channel-specific parameters are assigned one byte for each channel within the Dword. The following sections describe the serial slave and master/EEPROM modes of operation.

Note: Two identical register sets are implemented in the P0608R: one set for channels A0, A1, B0, B1 as shown in Table 10 and one set for channels A2, A3, B2, B3 as shown in Table 11. To program values for channels A0, A1, B0, B1, set I2CA[0] to 0 in the P0608R I<sup>2</sup>C address. To program values for channels A2, A3, B2, B3, set I2CA[0] to 1 in the P0608R I<sup>2</sup>C address.

|                      |                         | Bi                | its             |                 |  |  |  |  |  |  |

|----------------------|-------------------------|-------------------|-----------------|-----------------|--|--|--|--|--|--|

|                      | [31:24]                 | [23:16]           | [15:08]         | [07:00]         |  |  |  |  |  |  |

| Address Offset (hex) | Channel B1              | Channel B0        | Channel A1      | Channel A0      |  |  |  |  |  |  |

| 00                   | Vendor ID (VID)         |                   |                 |                 |  |  |  |  |  |  |

| 01                   |                         | Device            | ID (DID)        |                 |  |  |  |  |  |  |

| 02                   |                         | Revision          | ID (RID)        |                 |  |  |  |  |  |  |

| 03                   | DC_GAIN                 | DC_GAIN           | DC_GAIN         | DC_GAIN         |  |  |  |  |  |  |

| 04                   | EQDATARATE              | EQDATARATE        | EQDATARATE      | EQDATARATE      |  |  |  |  |  |  |

| 05                   | EQDCGAIN                | EQDCGAIN          | EQDCGAIN        | EQDCGAIN        |  |  |  |  |  |  |

| 06                   | EQ                      | EQ                | EQ              | EQ              |  |  |  |  |  |  |

| 07                   | LA_SWING                | LA_SWING LA_SWING |                 | LA_SWING        |  |  |  |  |  |  |

| 08                   | SIG_THRESH              | SIG_THRESH        | SIG_THRESH      | SIG_THRESH      |  |  |  |  |  |  |

| 09                   | SIG_GLITCHRM            | SIG_GLITCHRM      | SIG_GLITCHRM    | SIG_GLITCHRM    |  |  |  |  |  |  |

| 0A                   | SIG_FORCESIGDET         | SIG_FORCESIGDET   | SIG_FORCESIGDET | SIG_FORCESIGDET |  |  |  |  |  |  |

| 0B                   | TX_SWING                | TX_SWING          | TX_SWING        | TX_SWING        |  |  |  |  |  |  |

| 0C                   | TX_DEEMP                | TX_DEEMP          | TX_DEEMP        | TX_DEEMP        |  |  |  |  |  |  |

| 0D                   | TX_SLEW                 | TX_SLEW           | TX_SLEW         | TX_SLEW         |  |  |  |  |  |  |

| 0E                   | TX_EMP_DELAY            | TX_EMP_DELAY      | TX_EMP_DELAY    | TX_EMP_DELAY    |  |  |  |  |  |  |

| 0F                   | TX_OC_ENA               | TX_OC_ENA         | TX_OC_ENA       | TX_OC_ENA       |  |  |  |  |  |  |

| 10                   | DET_STATUS              | DET_STATUS        | DET_STATUS      | DET_STATUS      |  |  |  |  |  |  |

| 11                   | CHEN                    | CHEN              | CHEN            | CHEN            |  |  |  |  |  |  |

| 12                   | Global control register |                   |                 |                 |  |  |  |  |  |  |

| 13                   | Reserved                |                   |                 |                 |  |  |  |  |  |  |

| 14                   | I2CSTS register         |                   |                 |                 |  |  |  |  |  |  |

| 15                   |                         | I2CCTL            | register        |                 |  |  |  |  |  |  |

| 16                   |                         | EEPROM co         | ontrol register |                 |  |  |  |  |  |  |

Table 10 I<sup>2</sup>C Register Description Summary for Channels A0, A1, B0, B1

|                      | Bits                    |                 |                 |                 |  |  |

|----------------------|-------------------------|-----------------|-----------------|-----------------|--|--|

|                      | [31:24]                 | [23:16]         | [15:08]         | [07:00]         |  |  |

| Address Offset (hex) | Channel B3              | Channel B2      | Channel A3      | Channel A2      |  |  |

| 00                   |                         | Vendor          | ID (VID)        |                 |  |  |

| 01                   |                         | Device I        | ID (DID)        |                 |  |  |

| 02                   |                         | Revision        | ID (RID)        |                 |  |  |

| 03                   | DC_GAIN                 | DC_GAIN         | DC_GAIN         | DC_GAIN         |  |  |

| 04                   | EQDATARATE              | EQDATARATE      | EQDATARATE      | EQDATARATE      |  |  |

| 05                   | EQDCGAIN                | EQDCGAIN        | EQDCGAIN        | EQDCGAIN        |  |  |

| 06                   | EQ                      | EQ              | EQ              | EQ              |  |  |

| 07                   | LA_SWING                | LA_SWING        | LA_SWING        | LA_SWING        |  |  |

| 08                   | SIG_THRESH              | SIG_THRESH      | SIG_THRESH      | SIG_THRESH      |  |  |

| 09                   | SIG_GLITCHRM            | SIG_GLITCHRM    | SIG_GLITCHRM    | SIG_GLITCHRM    |  |  |

| 0A                   | SIG_FORCESIGDET         | SIG_FORCESIGDET | SIG_FORCESIGDET | SIG_FORCESIGDET |  |  |

| 0B                   | TX_SWING                | TX_SWING        | TX_SWING        | TX_SWING        |  |  |

| 0C                   | TX_DEEMP                | TX_DEEMP        | TX_DEEMP        | TX_DEEMP        |  |  |

| 0D                   | TX_SLEW                 | TX_SLEW         | TX_SLEW         | TX_SLEW         |  |  |

| 0E                   | TX_EMP_DELAY            | TX_EMP_DELAY    | TX_EMP_DELAY    | TX_EMP_DELAY    |  |  |

| 0F                   | TX_OC_ENA               | TX_OC_ENA       | TX_OC_ENA       | TX_OC_ENA       |  |  |

| 10                   | DET_STATUS              | DET_STATUS      | DET_STATUS      | DET_STATUS      |  |  |

| 11                   | CHEN                    | CHEN            | CHEN            | CHEN            |  |  |

| 12                   | Global control register |                 |                 |                 |  |  |

| 13                   | Reserved                |                 |                 |                 |  |  |

| 14                   | I2CSTS register         |                 |                 |                 |  |  |

| 15                   |                         | I2CCTL          | register        |                 |  |  |

| 16                   |                         | EEPROM co       | ontrol register |                 |  |  |

Table 11 I<sup>2</sup>C Register Description Summary for Channels A2, A3, B2, B3

The I<sup>2</sup>C registers are implemented in 32-bit wide format (DWord).

Note: The following register descriptions apply to both the A0, A1, B0, B1 and the A2, A3, B2, B3 register sets.

### **Vendor Identification Register**

| Address<br>Offset<br>(hex) | Field Name | Туре | Default<br>Value | Description              |

|----------------------------|------------|------|------------------|--------------------------|

| 00h                        | VID        | R0   | 111Dh            | 16 bit Vendor ID for IDT |

## **Device Identification Register**

| Address<br>Offset<br>(hex) | Field Name | Туре | Default<br>Value | Description                 |

|----------------------------|------------|------|------------------|-----------------------------|

| 01h                        | DID        | R0   | 80AAh            | 16 bit Device ID for P0608R |

## **Revision Identification Register**

| Address<br>Offset<br>(hex) | Field Name | Туре | Default<br>Value | Description                    |

|----------------------------|------------|------|------------------|--------------------------------|

| 02h                        | RID        | R0   | 08h              | Revision ID for device version |

## **Channel Based Register**

The I<sup>2</sup>C register shown below is implemented in a 32-bit wide format. For each register, bits 31:24 are for channel B1, 23:16 for B0, 15:8 for A1, and 7:0 for A0.

| Address<br>Offset<br>(hex) | Register Name | Туре | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------|---------------|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03h                        | DC_GAIN       | RW   | 01h              | DC Gain of Input Amplifier. Used for reducing input signal swings to adapt them better to internal RX circuits. 1 00h: -2dB                                                                                                                                                                                                                                                         |

| 04h                        | EQDATARATE    | RW   | 02h              | Input Equalization Data Rate 00h: 2.5 to 3 Gbps data rate 01h: 5 Gbps data rate 02h: 6 Gpbs data rate 03h: 8 Gpbs data rate Usage details: Set to the data rate used in end application. Sometimes, a minor improvement can be seen by setting 5Gbps at 6Gbps speeds (or vice versa). This depends on the number of connectors and line length. Corresponding programming pins: N/A |

| 05h                        | EQDCGAIN      | RW   | 01h              | Equalizer DC Gain Control. Used for large swing input signals.  00h: -3dB  01h: -1dB (default)  02h: 1dB  03h: 3dB  Usage details: Typically left at default, but might need to be set to -3db if the input swing is above 1000mVppdiff.  Corresponding programming pins: N/A                                                                                                       |

| 06h                        | EQ            | RW   | 03h              | Input Equalization at selected F=EQDATARATE/2  00h: +0dB                                                                                                                                                                                                                                                                                                                            |

Table 12 P0608R I<sup>2</sup>C Register (Part 1 of 3)

| Address<br>Offset<br>(hex) | Register Name   | Туре | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-----------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07h                        | LA_SWING        | RW   | 02h              | Internal Limiting Amplifier Programmable Swing. Used for fine optimization.  00h: 700mV <sub>diff-pkpk</sub> - 20%  01h: 700mV <sub>diff-pkpk</sub> 02h: 700mV <sub>diff-pkpk</sub> (default) 03h: 700mV <sub>diff-pkpk</sub> + 20%  Usage details: Typically left at default. Used for fine optimization. May slightly reduce jitter for some combinations of connectors and line lengths. Does not interact with TX_SWING settings.  Corresponding programming pins: N/A                                                                                                       |

| 08h                        | SIG_THRESH      | RW   | 03h              | Rx Loss of Signal Detection Threshold 00h: 50mV <sub>diff-pkpk</sub> 01h: 70mV <sub>diff-pkpk</sub> 02h: 90mV <sub>diff-pkpk</sub> 03h: 110mV <sub>diff-pkpk</sub> 03h: 110mV <sub>diff-pkpk</sub> 05h: 120mV <sub>diff-pkpk</sub> 05h: 140mV <sub>diff-pkpk</sub> 05h: 150mV <sub>diff-pkpk</sub> 06h: 150mV <sub>diff-pkpk</sub> 07h: 170mV <sub>diff-pkpk</sub> Usage details: Set to desired value based on end application. Loss of signal can be disabled completely via SIG_PD_TRANDET and SIG_PD_LVLDET bits. Corresponding programming pins: N/A                        |

| 09h                        | SIG_GLITCHRM    | RW   | 00h              | Minimum Loss of Signal Detection Glitch Removal. Advanced feature.  00h: 2.6n (default)  01h: 3.1n  02h: 3.5n  03h: 4.0n  Usage details: Typically left at default (2.6ns).  Corresponding programming pins: N/A                                                                                                                                                                                                                                                                                                                                                                 |

| 0Ah                        | SIG_FORCESIGDET | RW   | 00h              | Force Output of Signal Detection 00h: Normal operation 01h: Force RX_SIGNALDET to 1 Usage details: Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0Bh                        | TX_SWING        | RW   | 04h              | Transmitter Differential Swing Peak-to-Peak (typical) (see V <sub>TX-DIFF-PP</sub> and V <sub>TX-DIFF-PP-LOW</sub> transmitter specifications) 00h - 0.4Vdiff-pkpk 01h - 0.5Vdiff-pkpk 02h - 0.6Vdiff-pkpk 02h - 0.6Vdiff-pkpk 03h - 0.7Vdiff-pkpk 04h - 0.8Vdiff-pkpk 05h - 0.85Vdiff-pkpk 05h - 0.95Vdiff-pkpk 06h - 0.90Vdiff-pkpk 07h - 0.95Vdiff-pkpk 07h - 0.95Vdiff-pkpk 07h - 0.95Vdiff-pkpk Usage details: Set to desired TX driver amplitude. Typically, higher values are recommended when TX has to drive over longer distances. Corresponding programming pins: N/A |

Table 12 P0608R I<sup>2</sup>C Register (Part 2 of 3)

| Address<br>Offset<br>(hex) | Register Name | Туре | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                               |

|----------------------------|---------------|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0Ch                        | TX_DEEMP      | RW   | 02h              | Output De-emphasis. Defined as 20log(V <sub>TX-DE-EMP</sub> / V <sub>TX-DIFF</sub> ) [dB] 00h: +0dB 01h: -2.5dB 02h: -3.5dB (default) 03h: -4.5dB 04h: -5.5dB 05h: -6.5dB 06h: -7.5dB 07h: -8.5dB Usage details: Typically, value should be more negative when TX has to drive over longer distances. Corresponding programming pins: N/A |

| 0Dh                        | TX_SLEW       | RW   | 00h              | Output Rise/Fall (20% - 80% levels) 00h: 45ps (default) 01h: 50ps 02h: 70ps 03h: 150ps Usage details: Set to desired TX slew rate Corresponding programming pins: N/A                                                                                                                                                                     |

| 0Eh                        | TX_EMP_DELAY  | RW   | 00h              | Output De-emphasis Delay 00h: 166ps, 6Gbps mode (default) 01h: 200ps, 5Gbps mode 02h: 333ps, 3Gbps mode 03h: 400ps, 2.5Gbps mode Usage details: Needed only when de-emphasis is used. Select delay closest to data rate period (example: 5Gb->200ps). See Figure 22. Corresponding programming pins: N/A                                  |

| 0Fh                        | TX_OC_ENA     | RW   | 01h              | Transmitter De-emphasis Delay Cell Offset Cancellation Loop Control. Used for fine optimization. 00h: disable the loop 01h: enable the loop (default) Usage details: Left at default (enabled). Corresponding programming pins: N/A                                                                                                       |

| 10h                        | DET_STATUS    | R    | 00h              | Input Loss of Signal Detection Bit 0: 1 = input has signal Bit 1: 1 = reserved                                                                                                                                                                                                                                                            |

| 11h                        | CHEN          | RW   | 03h              | Channel Enable and Speed Control Bit 0: 1 = enable, 0 = disable Bit 1: 1 = 6Gbps and below, 0 = 3Gbps and below Usage details: Based on channel usage and frequencies of operation required in end applications. Corresponding programming pins: bit 0 = A0EN, A1EN, etc.; bit 1 = NA                                                     |

## Table 12 P0608R I<sup>2</sup>C Register (Part 3 of 3)

<sup>1.</sup> During the readout of this register for channels A0 and A2 only: Readout value = (Last value written into DC-GAIN register) + 08h (e.g. 00h setting reads out as 08h).

## Global Control Register (address offset=12h)

| Bit<br>Field | Field Name     | Туре | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|----------------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0          | TERM_CTL       | RW   | 10               | Input and Output Differential Termination (typical) $00-80\Omega \ \text{differential impedance} \\ 01-90\Omega \ \text{differential impedance} \\ 10-100\Omega \ \text{differential impedance} \ (\text{default}) \\ 11-110\Omega \ \text{differential impedance} \\ \text{Usage details: Set to value 2 times higher than line impedance.} \\ \text{Corresponding programming pins: N/A}$ |

| 5:2          | CTRL           | RW   | 0001             | Data Transfer Control 0001: direct connect (default) 0010: multicast mode 0100: cross connect mode 1000: loopback mode Usage details: Set to desired mode of transfer. Corresponding programming pins: N/A                                                                                                                                                                                  |

| 11:6         | Reserved       | RO   | 000000           | Reserved bits                                                                                                                                                                                                                                                                                                                                                                               |

| 12           | RXDET_EXT      | RW   | 0                | Write 1 to this bit to extend the time allowed for Tx common mode voltage negative step from 800µs to 1.2ms. Advanced feature.                                                                                                                                                                                                                                                              |

| 20:13        | Reserved       | RO   | 00h              | Reserved bits                                                                                                                                                                                                                                                                                                                                                                               |

| 21           | SIG_PD_TRANDET | RW   | 0                | Transition Detection in Input Signal Detector 0: enable 1: disable Usage details: Typically left at default. Signal detection can be disabled completely via SIG_PD_TRANDET and SIG_PD_LVLDET bits. Corresponding programming pins: N/A                                                                                                                                                     |

| 22           | SIG_PD_LVLDET  | RW   | 0                | Level Detection in Input Signal Detector 0: enable 1: disable Usage details: Typically left at default. Signal detection can be disabled completely via SIG_PD_TRANDET and SIG_PD_LVLDET bits. Corresponding programming pins: N/A                                                                                                                                                          |

| 23           | LA_EQ_ENA      | RW   | 1                | Limiting Amplifier Equalization Peaking Control. Advanced feature. 0: disable 1: enable Usage details: Typically left at default. Corresponding programming pins: N/A                                                                                                                                                                                                                       |

| 24           | Reserved       | RW   | 1                | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                |

| 31:25        | Reserved       | RO   | 0000000          | Reserved bits                                                                                                                                                                                                                                                                                                                                                                               |

Table 13 Global Control Register (OFFSET = 12h)

Test Control Register — Reserved (address offset=13h)

I<sup>2</sup>C Status Register (I2CSTS) (address offset=14h)

| Bit<br>Field | Field Name | Туре | Default<br>Value | Description                                                                                                                            |

|--------------|------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0            | Reserved   | RO   | 0                | Reserved                                                                                                                               |

| 7:1          | SI2CADDR   | RO   | HWINIT           | Slave I <sup>2</sup> C address                                                                                                         |

| 8            | Reserved   | RO   | 0                | Reserved                                                                                                                               |

| 15:9         | MI2CADDR   | RO   | HWINIT           | Master I <sup>2</sup> C address                                                                                                        |

| 16           | MODE       | RO   | HWINIT           | This field specifies the mode that the device's I <sup>2</sup> C master interface initialize in. 0x0: talking mode 0x1: listening mode |

| 21:17        | Reserved   | RO   | 00000            | Reserved                                                                                                                               |

| 22           | BLANK      | RW1C | 0                | Blank Serial EEPROM                                                                                                                    |

| 23           | ROLLOVER   | RW1C | 0                | EEPROM rolled over                                                                                                                     |

| 24           | EEPROMDONE | RO   | 0                | EEPROM_DONE                                                                                                                            |

| 25           | NAERR      | RW1C | 0                | No Acknowledge Error                                                                                                                   |

| 26           | Reserved   | RO   | 0                | Reserved                                                                                                                               |

| 27           | OTHERERR   | RW1C | 0                | Other Error                                                                                                                            |

| 28           | CSERR      | RW1C | 0                | Checksum Error                                                                                                                         |

| 29           | URIA       | RW1C | 0                | Unmapped register initialization attempt                                                                                               |

| 31:30        | Reserved   | RO   | 0                | Reserved                                                                                                                               |

Table 14 I<sup>2</sup>C Status Register (OFFSET=14h)

## I<sup>2</sup>C Control Register (I2CCTL) (address offset=15h)

| Bit<br>Field | Field Name | Туре | Default<br>Value | Description                                                                                                                        |

|--------------|------------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 15:0         | MI2CCP     | RO   |                  | Master I <sup>2</sup> C clock prescaler Final Master I <sup>2</sup> C clk freq = msmbcp x 8 x oscillator_clk_period                |

| 16           | Reserved   | RO   | 0                | Reserved                                                                                                                           |

| 17           | ICHECKSUM  | RW   | 0                | Ignore checksum error                                                                                                              |

| 19:18        | SI2CMODE   | RW   | 01               | Slave I <sup>2</sup> C mode 00: Glitch counters operate with 1 us delay 01: Glitch counters operate with 100 ns delay 10: Disabled |

Table 15 I<sup>2</sup>C Control Register (OFFSET=15h)

| Bit<br>Field | Field Name | Туре | Default<br>Value | Description                                                                   |

|--------------|------------|------|------------------|-------------------------------------------------------------------------------|

| 21:20        | MI2CMODE   | RW   | 00               | Master I <sup>2</sup> C mode<br>Same encodings as Slave I <sup>2</sup> C mode |

| 22           | I2CDTO     | RW   | 0                | I <sup>2</sup> C disable timeout                                              |

| 31:23        | Reserved   | RO   | 000000000        | Reserved                                                                      |

Table 15 I<sup>2</sup>C Control Register (OFFSET=15h)

## EEPROM Control Register (address offset=16h)

| Bit<br>Field | Field Name | Туре   | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

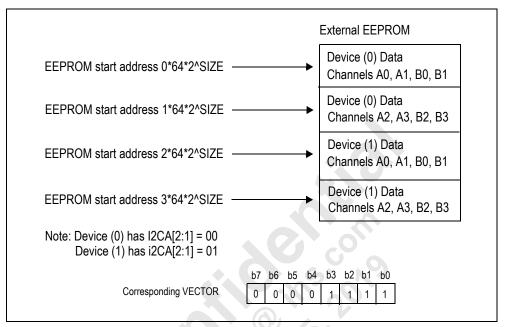

|--------------|------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0          | SIZE       | HWINIT | 00h              | This field sets the size of each partition in EEPROM, according to 64*2^SIZE: 00h: 64 bytes 01h: 128 bytes 02h: 256 bytes 03h: 512 bytes 04h: 1024 bytes 05h: 2048 bytes 06h: 4096 bytes 07h: 8192 bytes 08h: 16384 bytes 0thers: reserved  This field, and the other fields in this register are critical for external EEPROM operation and must be stored at the address 0 of EEPROM memory space using single Doubleword format. Other register configurations must be stored in EEPROM space after this register configuration.                                                                                                                                                                  |

| 15:8         | VECTOR     | HWINIT | FFh              | This field indicates which P0608Rs are present on the shared I2C bus.  Bit 8: P0608R(0) is present (I2CA[2:1]=00) channels A0, A1, B0, B1  Bit 9: P0608R(0) is present (I2CA[2:1]=00) channels A2, A3, B2, B3  Bit10: P0608R(1) is present (I2CA[2:1]=01) channels A0, A1, B0, B1   Bit 15: P0608R(3) is present (I2CA[2:1]=11) channels A2, A3, B2, B3  Note: 2 bits must be set for every P0608R present.  This field, and the other fields in this register are critical for external EEPROM operation and must be stored at the address 0 of EEPROM memory space using single Doubleword format. Other register configurations must be stored in EEPROM space after this register configuration. |

| 31:16        | Reserved   | RO     | 0000h            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 16 External EEPROM Control Register (OFFSET=16h)

### Serial Interface

The P0608R interface supports I<sup>2</sup>C interfaces. The P0608R has two interface operating modes, slave and master. The slave I<sup>2</sup>C mode provides full access to all software-visible registers, allowing every register in the device to be read or written by an external I<sup>2</sup>C master. The master I<sup>2</sup>C mode provides connection for an optional external serial EEPROM used for initialization. Once initialized, the P0608R switches to slave mode. I<sup>2</sup>C interfaces contain an I<sup>2</sup>C clock pin and an I<sup>2</sup>C data pin. The master and slave interfaces share the same set of address pins I2CA[2:1].

The pin INTMODE controls if the  $I^2C$  is in the master or the slave mode. When INTMODE=low, the interface is in the slave mode, when INTMODE=high, it is in the master mode.

Note that the register array is not fully contiguous for all registers. The register array appears as two identical blocks, each identified by the state of the I<sup>2</sup>C A0 address bit. For I2CA0=0, the lower four channels (A0, A1, B0, B1) are accessed. When I2CA0=1, the upper four channels (A2, A3, B2, B3) are accessed.

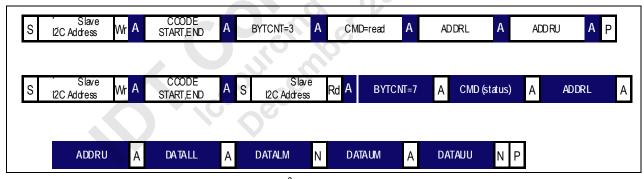

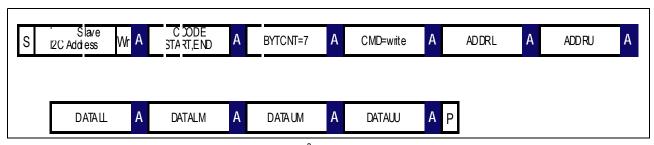

#### I<sup>2</sup>C Slave Mode

The slave  $I^2C$  mode provides the P0608R with a configuration, management, and debug interface. Using the slave  $I^2C$  mode, an external master can read or write any software-visible register in the device.

#### Initialization

Slave I<sup>2</sup>C initialization occurs during a switch fundamental reset. During the switch fundamental reset initialization sequence, the slave I<sup>2</sup>C address is initialized. The address is specified by the I2CA[2:1] signals as shown in Table 17. The I2CA[0] bit is used to select programming for A0, A1, B0, B1 channels when I2CA0=0 or to select programming for A2, A3, B2, B3 channels when I2CA0=1.

| Address<br>Bit | Address Bit Value                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------|

| 1              | I2CA0=0: selects access to A0, A1, B0, B1 channels I2CA0=1: selects access to A2, A3, B2, B3 channels |

| 2              | I2CA1                                                                                                 |

| 3              | I2CA2                                                                                                 |

| 4              | 0                                                                                                     |

| 5              | 1                                                                                                     |

| 6              | 1                                                                                                     |

| 7              | 1                                                                                                     |

Table 17 Slave I<sup>2</sup>C Address

#### I<sup>2</sup>C Transactions

The slave  $I^2C$  interface responds to the following  $I^2C$  transactions initiated by an  $I^2C$  master. Refer to the  $I^2C$  2.0 specification for a detailed description of these transactions.

- Byte and Word Write/Read

- Block Write/Read

Initiation of any I<sup>2</sup>C transaction other than those listed above to the slave I<sup>2</sup>C interface produces undefined results. Associated with each of the above transactions is a command code. The command code format for operations supported by the slave I<sup>2</sup>C interface is shown in Table 18 and described in Table 19.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|----------|-------|-------|-------|

| PEC   | SI    | ZE    |       | FUNCTION |       | START | END   |

Table 18 Slave I<sup>2</sup>C Command Code Format

| Bit Field | Name     | Description                                                                                                                                                                                                                                                                 |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | END      | End of transaction indicator. Setting both START and END signifies a single transaction sequence 0 - Current transaction is not the last read or write sequence. 1 - Current transaction is the last read or write sequence.                                                |

| 1         | START    | Start of transaction indicator. Setting both START and END signifies a single transaction sequence  0 - Current transaction is not the first of a read or write sequence.  1 - Current transaction is the first of a read or write sequence.                                |

| 4:2       | FUNCTION | This field encodes the type of I <sup>2</sup> C operation. 0 - CSR register read or write operation 1 - 7 Reserved                                                                                                                                                          |

| 6:5       | SIZE     | This field encodes the data size of the I <sup>2</sup> C transaction.  0 - Byte 1 - Word 2 - Block 3 - Reserved                                                                                                                                                             |

| 7         | PEC      | This bit controls whether packet error checking is enabled for the current I <sup>2</sup> C transaction.  0 - Packet error checking disabled for the current I <sup>2</sup> C transaction.  1 - Packet error checking enabled for the current I <sup>2</sup> C transaction. |

Table 19 Slave I<sup>2</sup>C Command Code Fields