Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3000W/3500W; 5 Vdc @ 10W

## **Applications**

- 48V<sub>DC</sub> distributed power architectures

- Routers/ VoIP/Soft and other Telecom Switches

- LAN/WAN/MAN applications

- File servers, Enterprise Networks, Indoor wireless

- SAN/NAS/iSCSI applications

#### **Features**

- Efficiency meets 80 plus Titanium requirements

- Compact 1RU form factor with 40 W/in<sup>3</sup> density

- Constant power from 52 58V<sub>DC</sub>

- 3000 or 3500W from nominal 200-277V<sub>AC</sub>

- 1500W from nominal 100 120V<sub>AC</sub>

- Output voltage programmable from 42V 58V<sub>DC</sub>

- ON/OFF control of the main output

- Comprehensive input, output and overtemp. protection

- PMBus compliant dual I<sup>2</sup>C serial bus and RS485

- Precision measurement reporting such as input power consumption, input/output voltage & current

- Remote firmware upgrade capable

- Power factor correction (meets EN/IEC 61000-3-2 and EN 60555-2 requirements)

- Redundant, parallel operation with active load sharing

- Redundant +5V @ 2A Aux power

- Internally controlled Variable-speed fan

- Hot insertion/removal (hot plug)

- Four front panel LED indicators

- UL\* Recognized, CAN/ CSA<sup>†</sup> C22.2 to IEC60950-1,

- CE mark meets 2006/95/EC directive§

- CB report available

### Description

The CP3000/3500AC54TEP Rectifiers provide significantly higher power density in the same form factor and efficiency improvements in the Compact Power Line of Rectifiers. The only difference between these rectifiers is output power limit. High-density front-to-back airflow is designed for minimal space utilization and is highly expandable for future growth. Wide-input enables the rectifier to be deployed internationally into a wide range of commercially available voltage sources. Configured with both dual-redundant  $^{12}$ C and RS485 based communications busses, so that it could be positioned into a broad range of applications. Feature set flexibility makes this rectifier an excellent choice for applications requiring modular AC to -  $^{48}$ VDC intermediate voltages, such as in distributed power.

- $^{\star}~$  UL is a registered trademark of Underwriters Laboratories, Inc.

- † CSA is a registered trademark of Canadian Standards Association.

- \* *VDE* is a trademark of Verband Deutscher Elektrotechniker e.V.

- § This product is intended for integration into end-user equipment. All CE marking procedures of end-user equipment should be followed. (The CE mark is placed on selected products.)

- \*\* ISO is a registered trademark of the International Organization of Standards

- + The *PMBus* name and logo are registered trademarks of the System Management Interface Forum (SMIF)

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability.

| Parameter                                                   | Symbol           | Min | Max  | Unit            |

|-------------------------------------------------------------|------------------|-----|------|-----------------|

| Input Voltage: Continuous                                   | $V_{\text{IN}}$  | 0   | 300  | $V_{AC}$        |

| Operating Ambient Temperature <sup>1</sup>                  | TA               | -10 | 75   | °C              |

| Storage Temperature                                         | T <sub>stg</sub> | -40 | 85   | °C              |

| I/O Isolation voltage to Frame (100% factory Hi-Pot tested) |                  |     | 1500 | V <sub>AC</sub> |

## **Electrical Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage,  $Vo=54V_{DC}$ , resistive load, and temperature conditions.

| INPUT                                                                                                          |                 |                      |                        |            |                 |

|----------------------------------------------------------------------------------------------------------------|-----------------|----------------------|------------------------|------------|-----------------|

| Parameter                                                                                                      | Symbol          | Min                  | Тур                    | Max        | Unit            |

| Startup Voltage Low-line Operation High-line Operation                                                         |                 | 80                   | 85                     | 90<br>185  |                 |

| Operating Voltage Range<br>Low-line Configuration<br>High-line Configuration                                   | V <sub>IN</sub> | 90<br>185            | 100 - 120<br>200 - 277 | 140<br>300 | V <sub>AC</sub> |

| Voltage Swell (no damage)                                                                                      |                 | 305                  |                        |            |                 |

| Turn OFF Voltage Hysteresis                                                                                    |                 | 75<br>5              | 80                     | 85         |                 |

| Frequency                                                                                                      | Fin             | 47                   |                        | 66         | Hz              |

| Source Impedance (NEC allows 2.5% of source voltage drop inside a building)                                    |                 |                      | 0.2                    |            | Ω               |

| Operating Current; at 110V <sub>AC</sub> at 240V <sub>AC</sub>                                                 | I <sub>IN</sub> |                      | 15.5<br>16             |            | A <sub>AC</sub> |

| Inrush Transient (220V <sub>RMS</sub> , 25°C, excluding X-Capacitor charging)                                  | I <sub>IN</sub> |                      | 25                     | 40         | Apk             |

| Idle Power (at 240V <sub>AC,</sub> 25°C) 54V OFF<br>54V ON @ Io=0                                              | P <sub>IN</sub> |                      | 9<br>18                |            | w               |

| Leakage Current (300V <sub>AC</sub> , 60Hz)                                                                    | I <sub>IN</sub> |                      | 2.5                    | 3.5        | mA              |

| Power Factor (50 – 100% load)                                                                                  | PF              | 0.97                 | 0.995                  |            |                 |

| Efficiency <sup>2</sup> , 240V <sub>AC</sub> @ 25°C 10% of FL<br>20% of FL<br>50% of FL<br>FL                  | η               | 90<br>94<br>96<br>91 |                        |            | %               |

| Holdup time (output allowed to decay down to 40V <sub>DC</sub> )<br>For loads below 1500W                      | Т               |                      | 10<br>15               |            | ms              |

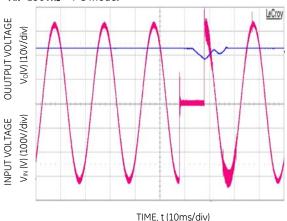

| Ride through (at 240V <sub>AC</sub> , 25°C)                                                                    | T               | 1/2                  | 1                      |            | cycle           |

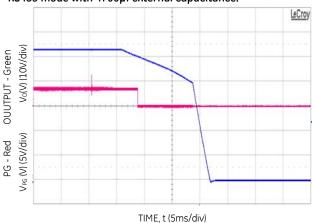

| Power Good Warning <sup>3</sup> (main output allowed to decay to 40V <sub>DC</sub> )                           | PG              | 3                    | 5                      |            | ms              |

| Isolation (per EN60950) (consult factory for testing to this requirement) Input-Chassis/Signals Input - Output | V               | 1500<br>3000         |                        |            | V <sub>AC</sub> |

March 23, 2016

$<sup>^{\, 1}\,</sup>$  See the derating guidelines under the Environmental Specifications section

$<sup>^{\</sup>rm 2}~$  Fan disabled, 5V output at 0 load.

<sup>&</sup>lt;sup>3</sup> Internal protection circuits may override the PG signal and may trigger an immediate shutdown. PG should not indicate normal (HI) until the main output is within regulation. PG should be asserted if the main output is about to shut down for any detectible reason.

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

Electrical Specifications (continued)

| Parameter                                                                                                                                                                                                                                                                                                       | Symbol                                | Min                                 | Тур             | Max                                       | Unit                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------|

| Output Power @ low line input 100 – 120V <sub>AC</sub><br>@ high line input 200 – 277V <sub>AC</sub>                                                                                                                                                                                                            | W                                     | 1500<br>3000/3500                   |                 |                                           | W <sub>DC</sub>                                                                 |

| Factory set default set point                                                                                                                                                                                                                                                                                   |                                       |                                     | 54              |                                           | V <sub>DC</sub>                                                                 |

| Overall regulation (load, temperature, aging) 0 - 45°C LOAD > 2.5A > 45°C                                                                                                                                                                                                                                       | Vouт                                  | -1<br>-2                            |                 | +1<br>+2                                  | %                                                                               |

| Output Voltage Set Range <sup>a</sup> - analog margining<br>- Set either by I <sup>2</sup> C or RS485                                                                                                                                                                                                           |                                       | 44<br>42                            |                 | 58<br>58                                  | V <sub>DC</sub>                                                                 |

| Output Current - @ 1500W (100 – 120Vac), 54V/52V<br>@ 3000W (200 – 277V <sub>AC</sub> ), 54V/52V<br>@ 3500W (200 – 277V <sub>AC</sub> ), 54V/52V                                                                                                                                                                | lout                                  | 1<br>1<br>1                         |                 | 27.8/28.9<br>55.5/57.8<br>64.8/67.3       | A <sub>DC</sub>                                                                 |

| Current Share ( > 50% FL)                                                                                                                                                                                                                                                                                       |                                       | -5                                  |                 | 5                                         | %FL                                                                             |

| Proportional Current Share between different rectifiers <sup>5</sup> ( > 50% FL)                                                                                                                                                                                                                                |                                       |                                     | <7              |                                           | %FL                                                                             |

| Output Ripple (20MHz bandwidth, load > 1A) RMS (5Hz to 20MHz) Peak-to-Peak (5Hz to 20MHz) Psophometric Noise                                                                                                                                                                                                    | V <sub>OUT</sub>                      |                                     |                 | 100<br>250 <sup>6</sup><br>9 <sup>7</sup> | mV <sub>rms</sub><br>mV <sub>p-p</sub><br>mV <sub>rms</sub>                     |

| External Bulk Load Capacitance                                                                                                                                                                                                                                                                                  | Соит                                  | 0                                   |                 | 5,000                                     | μF                                                                              |

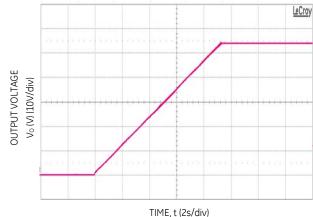

| Turn-On (monotonic turn-ON from 30 – 100% of Vnom above 5°C) Delay Rise Time – PMBus mode Rise Time - RS-485 mode <sup>8</sup> Output Overshoot                                                                                                                                                                 | T<br>V <sub>out</sub>                 |                                     | 5<br>100<br>5   | 2                                         | s<br>ms<br>s<br>%                                                               |

| Load Step Response ( $I_{O.START} > 2.5A$ )<br>$\Delta I^{9}$<br>$\Delta V$ , $V_{AC} < 285_{AC}$<br>$\Delta V$ , $V_{AC} \ge 285_{AC}$<br>Response Time                                                                                                                                                        | Iouт<br>Vouт<br>Vouт<br>T             |                                     | 2.0<br>3.2<br>2 | 50                                        | %FL<br>V <sub>DC</sub><br>V <sub>DC</sub><br>ms                                 |

| Overload - Power limit @ high line down to 52V <sub>DC</sub> Power limit @ low line down to 52V <sub>DC</sub> High line current limit <sup>10</sup> if V <sub>out</sub> > 39V <sub>DC</sub> [3000W/3500W] Low line current limit Output shutdown (commences as voltage decays below this level) System power up | Pout Pout lout lout Vout Upon inserti | 3000/3500<br>1500<br>59/68<br>30    | vill delay an o | 36<br>verload shutdo                      | W <sub>DC</sub> W <sub>DC</sub> A <sub>DC</sub> A <sub>DC</sub> V <sub>DC</sub> |

|                                                                                                                                                                                                                                                                                                                 | seconds allo<br>within a syst         | wing for the inse<br>em.            | ertion and sto  | artup of multiple                         | e rectifiers                                                                    |

| Overvoltage - 200ms delayed shutdown<br>Immediate shutdown                                                                                                                                                                                                                                                      | Vouт                                  | > 65                                |                 | < 60                                      | $V_{DC}$                                                                        |

| Latched shutdown                                                                                                                                                                                                                                                                                                |                                       | t attempts are ir<br>ched shutdown. |                 | within a 1 minu                           | te windov                                                                       |

| Over-temperature warning (prior to commencement of shutdown) Shutdown (below the max device rating being protected) Restart attempt Hysteresis (below shutdown level)                                                                                                                                           | Т                                     |                                     | 5<br>20<br>10   |                                           | °C                                                                              |

|                                                                                                                                                                                                                                                                                                                 | V                                     | 500<br>2250                         |                 |                                           | V <sub>DC</sub>                                                                 |

$<sup>^4</sup>$  When  $V_O > 57V_{DC}$  or when  $V_{IN} > 270V_{AC}$  and  $V_O < 48V_{DC}$  power derating starts at 50°C

<sup>&</sup>lt;sup>5</sup> With existing CP platform of rectifiers

$<sup>^{6}</sup>$  500mVp-p max above 280V<sub>AC</sub> , 300mV<sub>p-p</sub> max for POE product

$<sup>^{7}</sup>$  Complies with ANSI TI.523-2001 section 4.9.2 emissions max limit of 20mV flat unweighted wideband noise limits

$<sup>^{\</sup>rm 8}~$  Below -5°C, the rise time is approximately 5 minutes to protect the bulk capacitors.

$<sup>^{9}\,</sup>$  di/dt (output current slew rate) 1A/ $\mu$ s.

$<sup>^{10}</sup>$  Above 280V<sub>AC</sub> the current limit reduces to 50A when V<sub>OUT</sub>  $\leq$  45V<sub>DC</sub> and to 25A when V<sub>OUT</sub>  $\leq$  45V<sub>DC</sub> and T<sub>AMB</sub> > 55C.

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

| 5V <sub>DC</sub> Auxiliary output  |                  |       |     |     |                   |

|------------------------------------|------------------|-------|-----|-----|-------------------|

| Parameter                          | Symbol           | Min   | Тур | Max | Unit              |

| Output Voltage Setpoint            | V <sub>OUT</sub> |       | 5   |     | $V_{DC}$          |

| Overall Regulation                 |                  | -3    |     | +3  | %                 |

| Output Current                     |                  | 0.005 |     | 2   | Α                 |

| Ripple and Noise (20mHz bandwidth) |                  |       | 50  | 100 | mV <sub>p-p</sub> |

| Over-voltage Clamp                 |                  |       |     | 7   | V <sub>DC</sub>   |

| Over-current Limit                 |                  | 110   |     | 175 | %FL               |

The  $5V_{DC}$  should be ON before availability of the  $54V_{DC}$  main output and should turn OFF only if insufficient input voltage exists to provide reliable 5Vpc power. The PG# signal should have indicated a warning that power would get turned OFF and the 54Vpc main output should be OFF way before interruption of the 5V<sub>DC</sub> output.

## **General Specifications**

| Parameter        | Min                                                                 | Тур      | Max | Units   | Notes                                                                                                         |  |

|------------------|---------------------------------------------------------------------|----------|-----|---------|---------------------------------------------------------------------------------------------------------------|--|

| Reliability      |                                                                     | 450,000  |     | Hours   | Full load, 25°C; MTBF per SR232 Reliability protection for electronic equipment, issue 2, method I, case III, |  |

| Service Life     |                                                                     | 10       |     | Years   | Full load, excluding fans                                                                                     |  |

| Unpacked Weight  |                                                                     | 2.18/4.8 |     | Kgs/Lbs |                                                                                                               |  |

| Packed Weight    |                                                                     | 2.45/5.4 |     | Kgs/Lbs |                                                                                                               |  |

| Heat Dissipation | 190 Watts or 648 BTUs @ 80% load, 250 Watts or 853 BTUs @ 100% load |          |     |         |                                                                                                               |  |

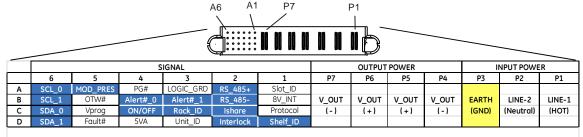

## **Signal Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. Signals are referenced to Logic\_GRD unless noted otherwise. Fault, PG#, OTW, and Alert need to be pulled HI through external pull-up resistors.

| Parameter                                                     | Symbol           | Min                | Тур              | Max     | Unit            |

|---------------------------------------------------------------|------------------|--------------------|------------------|---------|-----------------|

| ON/OFF 54V output OFF                                         | V <sub>out</sub> | 0.7V <sub>DD</sub> | _                | 5       | $V_{DC}$        |

| 54V output ON (should be connected to Logic_GRD)              | $V_{\text{out}}$ | 0                  | _                | 0.5     | $V_{DC}$        |

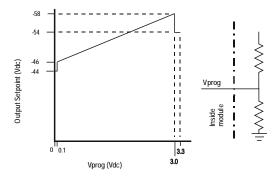

| Margining (through adjusting Vprog)                           |                  | 44                 |                  | 58      | $V_{DC}$        |

| Voltage control range                                         | $V_{control}$    | 0                  |                  | 3.3     | $V_{DC}$        |

| Programmed output voltage range                               | V <sub>OUT</sub> | 44                 |                  | 58      | $V_{DC}$        |

| Voltage adjustment resolution (8-bit A/D)                     | $V_{control}$    |                    | 3.3              |         | $mV_{DC}$       |

| Output configured to 54V <sub>DC</sub>                        | $V_{control}$    | 3.0                |                  | 3. 3    | $V_{DC}$        |

| Output configured to 44V <sub>DC</sub>                        | $V_{control}$    | 0                  |                  | 0.1     | $V_{DC}$        |

| Interlock                                                     | (short pin sh    | norted to VOU      | Γ( - ) on system | n side] |                 |

| Module Present                                                | [short pin to    | o Logic_GRD ir     | nternally]       |         |                 |

| Over Temperature Warning (OTW#) Logic HI (temperature normal) | V                | 0.7V <sub>DD</sub> | _                | 12      | $V_{DC}$        |

| Sink current [note: open collector output FET]                | 1                | _                  | _                | 5       | mA              |

| Logic LO (temperature is too high)                            | V                | 0                  | _                | 0.4     | $V_{DC}$        |

| Power Good (PG) Logic HI (temperature normal)                 | V                | 0.7V <sub>DD</sub> |                  | 12      | $V_{DC}$        |

| Sink current [note: open collector output FET]                | 1                | _                  | _                | 5       | mA              |

| Logic LO (temperature is too high)                            | V                | 0                  | _                | 0.4     | $V_{DC}$        |

| Protocol select Logic HI - Analog/PMBus™ mode                 | V <sub>IH</sub>  | 2.7                |                  | 3.5     | V <sub>DC</sub> |

| Logic – intermediate – RS485 mode                             | VII              | 1.0                |                  | 2.65    | $V_{DC}$        |

| Logic LO – DSP reprogram mode                                 | V <sub>IL</sub>  | 0                  | _                | 0.4     | V <sub>DC</sub> |

| Fault# Logic HI (No fault is present)                         | V                | 0.7V <sub>DD</sub> | _                | 12      | $V_{DC}$        |

| Sink current                                                  | 1                | _                  | —                | 5       | mA              |

| Logic LO (Fault is present)                                   | V                | 0                  |                  | 0.4     | $V_{DC}$        |

| Alert# (Alert#_0, Alert#_1) Logic HI (No Alert - normal)      | V                | 0.7V <sub>DD</sub> | _                | 12      | $V_{DC}$        |

| Sink current [note: open collector output FET]                | 1                | _                  | _                | 5       | mA              |

| Logic LO (Alert# is set)                                      | V                | 0                  | _                | 0.4     | $V_{DC}$        |

| SCL, SDA (SCL_0/1, SDA_0/1) Logic HI                          | V                | 0.7V <sub>DD</sub> | _                | 12      | V <sub>DC</sub> |

| Sink current [note: open collector output FET]                | 1                | _                  | _                | 5       | mA              |

| Logic LO (Alert# is set)                                      | V                | 0                  | _                | 0.4     | $V_{DC}$        |

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

**Digital Interface Specifications**

| Parameter                                                             | Conditions                                   | Symbol                | Min                 | Тур            | Max                | Unit            |

|-----------------------------------------------------------------------|----------------------------------------------|-----------------------|---------------------|----------------|--------------------|-----------------|

| PMBus Signal Interface Characteristics <sup>11</sup>                  |                                              |                       |                     |                |                    |                 |

| Input Logic High Voltage (CLK, DATA)                                  |                                              | V                     | 1.5                 |                | 3.6                | V <sub>DC</sub> |

| Input Logic Low Voltage (CLK, DATA)                                   |                                              | V                     | 0                   |                | 0.8                | V <sub>DC</sub> |

| Input high sourced current (CLK, DATA)                                |                                              | I                     | 0                   |                | 10                 | μΑ              |

| Output Low sink Voltage (CLK, DATA, ALERT#)                           | I <sub>OUT</sub> =3.5mA                      | V                     |                     |                | 0.4                | $V_{DC}$        |

| Output Low sink current (CLK, DATA, ALERT#)                           |                                              | Ţ                     | 3.5                 |                |                    | mA              |

| Output High open drain leakage current (CLK,DATA,<br>ALERT#)          | V <sub>OUT</sub> =3.6V                       | 1                     | 0                   |                | 10                 | μΑ              |

| PMBus Operating frequency range                                       | Slave Mode                                   | FPMB                  | 10                  |                | 400                | kHz             |

| Measurement System Characteristics                                    | •                                            |                       |                     |                |                    |                 |

| Clock stretching                                                      |                                              | T <sub>stretch</sub>  |                     |                | 25                 | ms              |

| lout measurement range                                                |                                              | I <sub>rng</sub>      | 0                   |                | 80                 | ADC             |

| l <sub>out</sub> measurement accuracy 25°C                            | > 12.8A<br>< 12.8A                           | lout(acc)             | -1<br>5             |                | +1<br>5            | % of FL<br>%    |

| I <sub>OUT</sub> measurement accuracy 0 - 40°C12                      | > 12.8A                                      | I <sub>out(acc)</sub> | -2                  |                | +2                 | % of FL         |

| V <sub>OUT</sub> measurement range                                    |                                              | V <sub>out(rng)</sub> | 0                   |                | 70                 | V <sub>DC</sub> |

| V <sub>OUT</sub> measurement accuracy <sup>13</sup>                   |                                              | V <sub>out(acc)</sub> | -1                  |                | +1                 | %               |

| Temp measurement range                                                |                                              | Temp <sub>(rng)</sub> | 0                   |                | 150                | °C              |

| Temp measurement accuracy <sup>14</sup>                               |                                              | Temp <sub>(acc)</sub> | -4                  |                | +4                 | °C              |

| V <sub>IN</sub> measurement range                                     |                                              | V <sub>in(rng)</sub>  | 0                   |                | 320                | V <sub>AC</sub> |

| V <sub>IN</sub> measurement accuracy @ 25°C                           | $V_{IN} > 120V_{AC}$<br>$V_{IN} < 120V_{AC}$ | V <sub>in(acc)</sub>  | -1.25<br>-2         |                | +1.25<br>2         | %               |

| I <sub>IN</sub> measurement range                                     |                                              | lin(rng)              | 0                   |                | 30                 | I <sub>AC</sub> |

| I <sub>IN</sub> measurement accuracy -<br>standard measurement @ 25°C |                                              | l <sub>in(acc)</sub>  | -4                  |                | +4                 | % of FL         |

| I <sub>IN</sub> measurement accuracy -<br>improved measurement @ 25°C | > 1A<br>≤ 1A                                 | l <sub>in(acc)</sub>  | -2.5<br>-400        |                | 2.5<br>400         | %<br>mA         |

| P <sub>IN</sub> measurement range                                     |                                              | P <sub>in(rng)</sub>  | 0                   |                | 4000               | Win             |

| P <sub>IN</sub> measurement accuracy –<br>standard measurement @ 25°C | > 350W<br>< 350W                             | P <sub>in(acc)</sub>  | -5                  | 35             | +5<br>50           | %<br>W          |

| P <sub>IN</sub> measurement accuracy –<br>improved measurement @ 25°C | > 500W<br>100 - 500W<br>< 100W               | P <sub>in(acc)</sub>  | -1.5<br>-2.0<br>-20 | 1<br>1.5<br>15 | +1.5<br>+2.0<br>20 | %<br>%<br>W     |

|                                                                       |                                              |                       |                     |                |                    |                 |

| Fan Speed measurement range                                           |                                              |                       | 0                   |                | 30k                | RPM             |

| Fan Speed measurement accuracy                                        |                                              |                       | -10                 |                | 10                 | %               |

| Fan speed control range                                               |                                              |                       | 0                   |                | 100                | %               |

$<sup>^{11}\,</sup>$  Clock, Data, and Alert# need to be pulled up to  $V_{DD}$  externally.

$<sup>^{12}</sup>$  Below 20% of FL;  $^{10}$  - 20% of FL:  $^{\pm}0.64A$ ;  $^{5}$  - 10% of FL:  $^{\pm}0.45A$ ;  $^{2}$ .5 - 5% of FL:  $^{\pm}0.32A$ .

<sup>&</sup>lt;sup>13</sup> Above 2.5A of load current

$<sup>^{14}</sup>$  Within 30° of the default warning and fault levels.

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

## **Environmental Specifications**

| Parameter                        | Min    | Тур     | Max              | Units                  | Notes                                           |

|----------------------------------|--------|---------|------------------|------------------------|-------------------------------------------------|

| Ambient Temperature              | -4015  |         | 55 <sup>16</sup> | °C                     | Air inlet from sea level to 5,000 feet.         |

| Exhaust Air Temperature          |        |         | 15               | °C                     | Maximum allowed internal temperature rise       |

| Storage Temperature              | -40    |         | 85               | °C                     |                                                 |

| Operating Altitude               |        |         | 1524/5000        | m/ft                   |                                                 |

| Non-operating Altitude           |        |         | 8200/30k         | m/ft                   |                                                 |

| Power Derating with Temperature  |        |         | 2.0              | %/°C                   | 55°C to 75°C                                    |

| Power Derating with Altitude     |        |         | 2.0              | °C/305 m<br>°C/1000 ft | Above 1524/5000 m/ft; 3962/13000 m/ft max       |

| Acoustic noise                   |        | 55      |                  | dbA                    | Full load                                       |

| Over Temperature Protection      |        | 125/110 |                  | °C                     | Shutdown / restart [internally measured points] |

| Humidity<br>Operating<br>Storage | 5<br>5 |         | 95<br>95         | %<br>%                 | Relative humidity, non-condensing               |

| Shock and Vibration acceleration |        |         | 2.4              | Grms                   | IPC-9592B, Class II                             |

| EMC                    |                     |                                                                                                            |                        |                             |

|------------------------|---------------------|------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|

| Parameter              | Measurement         | Standard                                                                                                   | Level                  | Test                        |

| AC input <sup>17</sup> | Conducted emissions | EN55022, FCC Docket 20780 part 15, subpart J<br>EN61000-3-2<br>Meets Telcordia GR1089-CORE by a 3dB margin | A +6dB                 | 0.15 – 30MHz<br>0 – 2 KHz   |

|                        | Radiated emissions  | EN55022                                                                                                    | A +6dB                 | 30 – 10000MHz               |

| Parameter              | Measurement         | Standard                                                                                                   | Criteria <sup>18</sup> | Test                        |

|                        | Line sags and       | EN61000-4-11                                                                                               | В                      | -30%, 10ms                  |

|                        | interruptions       |                                                                                                            | В                      | -60%, 100ms                 |

|                        |                     |                                                                                                            | В                      | -100%, 5sec                 |

|                        |                     | Output will stay above 40V <sub>DC</sub> @ 75% load                                                        | ٨                      | 25% line sag for 2 seconds  |

| AC Input<br>Immunity   |                     | Sag must be higher than 80Vrms.                                                                            | А                      | 1 cycle interruption        |

| ĺ                      | Lightning surge     | EN61000-4-5, Level 4, 1.2/50µs – error free                                                                | А                      | 4kV, common mode            |

|                        |                     |                                                                                                            | А                      | 2kV, differential mode      |

|                        |                     | ANSI C62.41 - level A3                                                                                     | В                      | 6kV, common & differential  |

|                        | Fast transients     | EN61000-4-4, Level 3                                                                                       | В                      | 5/50ns, 2kV (common mode)   |

|                        | Conducted RF fields | EN61000-4-6, Level 3                                                                                       | Α                      | 130dBµV, 0.15-80MHz, 80% AM |

| Enclosure              | Radiated RF fields  | ed RF fields EN61000-4-3, Level 3                                                                          |                        | 10V/m, 80-1000MHz, 80% AM   |

| immunity               |                     | ENV 50140                                                                                                  |                        |                             |

|                        | ESD                 | EN61000-4-2, Level 4                                                                                       | В                      | 8kV contact, 15kV air       |

<sup>15</sup> Designed to start and work at an ambient as low as -40°C, but may not meet operational limits until above -5°C

March 23, 2016

<sup>16</sup> At 277V input line operation the maximum ambient is reduced to 50°C. See operational limitations in other sections of this document

<sup>17</sup> Emissions requirements can be verified using either the J2007001 or J85480 GE shelf. Standalone the additional margin is not required.

<sup>18</sup> Criteria A: The product must maintain performance within specification limits. Criteria B: Temporary degradation which is self recoverable. Criteria C: Temporary degradation which requires operator intervention.

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

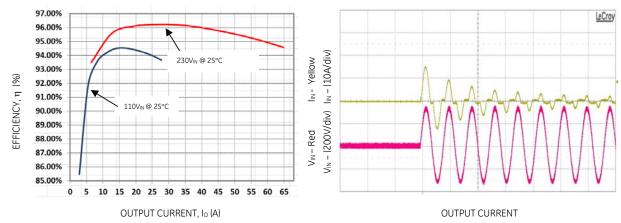

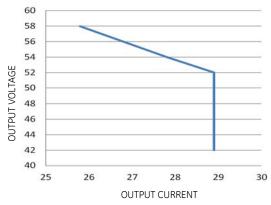

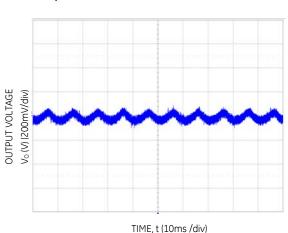

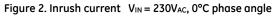

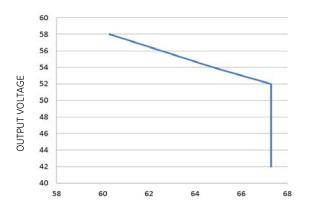

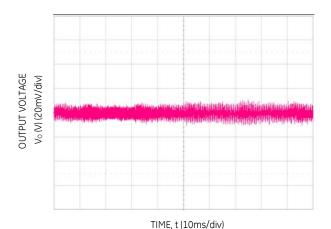

#### **Characteristic Curves**

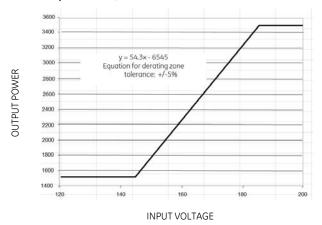

The following figures provide typical characteristics for the CP3500AC54TE rectifier and 25°C.

Figure 1. Rectifier Efficiency versus Output Current.

Figure 3.  $54V_{DC}$  output: Power limit, Current limit and shutdown profile at  $V_{IN} = 90V_{AC}$ .

Figure 5.  $54V_{DC}$  output ripple and noise, full load,  $V_{IN}\!=\!185V_{AC}$ , 20MHz bandwidth

Figure 4.  $54V_{DC}$  output: Power limit, Current limit and shutdown profile at  $V_{IN} = 185V_{AC}$ .

Figure 6.  $5V_{DC}$  output ripple and noise, all full load,  $V_{\text{IN}}\!=\,185V_{AC},20MHz$  bandwidth

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

### **Characteristic Curves (continued)**

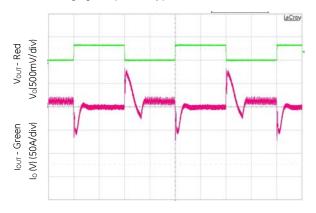

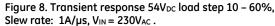

The following figures provide typical characteristics for the CP3500AC54TE rectifier and 25°C.

LeCroy V<sub>0</sub>(500mV/div) Io (V) (50A/div) וחחו - כוענו

TIME, t (2ms/div)

Figure 7. Transient response 54V<sub>DC</sub> load step 10 - 60%, Slew rate:  $1A/\mu s$ ,  $V_{IN} = 230V_{AC}$

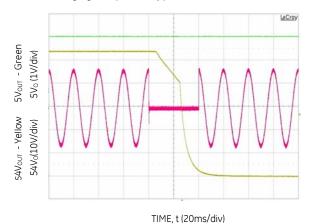

TIME, t (200ms/div)

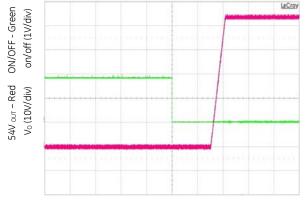

Figure 9. 54V<sub>DC</sub> soft start delay when ON/OFF is asserted, V<sub>IN</sub>=230V<sub>AC</sub> - I<sup>2</sup>C mode.

Figure 10.  $54V_{DC}$  soft start, full load,  $V_{IN} = 230V_{AC}$  -RS485 mode with 4700µf external capacitance.

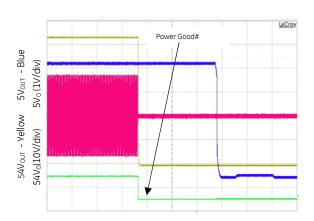

Figure 12. PG# alarmed 10ms prior to Vo < 40V,  $V_{\text{IN}} = 230 V_{\text{AC}}$ , Output at Full load

Figure 11. Ride through missing ½ cycle, full load,  $V_{IN} = 230V_{AC}$ .

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the CP3500AC54TE rectifier and 25°C.

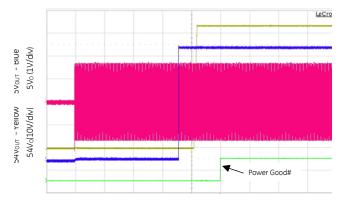

Figure 13. 40ms AC dropout @ full load, VIN = 230VAC.

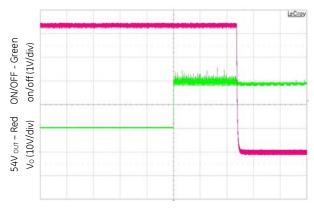

TIME, t (500ms/div) Figure 15. Turn-OFF at full load,  $V_{IN}=230V_{AC}$

TIME, t (1s/div)

Figure 14. Turn-ON at full load  $V_{IN} = 230V_{AC}$ .

TIME, t (200ms/div)

Figure 16. 54V<sub>DC</sub> turn-OFF delay when ON/OFF is diasserted,  $V_{IN}=230V_{AC}$  -  $I^2C$  mode.

Figure 17. Output power derating below  $V_{IN}$  of 185 $V_{AC}$

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

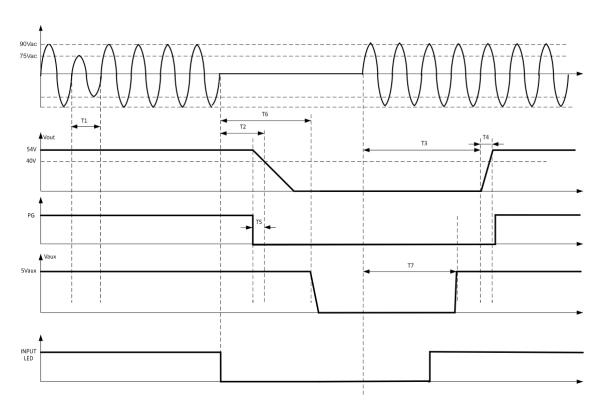

## **Timing diagrams**

### Response to input fluctuations

T1 - ride through time - 0.5 to 1 cycles [ 10 - 20ms] VouT remains within regulation - load dependent

T2 – hold up time - 15ms –  $V_{OUT}$  stays above  $40V_{DC}$

T3 - delay time - 10s - from when the AC returns within regulation to when the output starts rising in I2C mode

T4 - rise time - 120ms - the time it takes for Vout to rise from 10% to 90% of regulation in I2C mode

T5 – power good warning – 3ms – the time between assertion of the PG signal and the output decaying below 40V<sub>DC</sub>.

T6 - hold up time of the 5VAUX output @ full load - 1s - from the time AC input failed

T7 - rise time of the 5VAUX output - 3.65ms - 5VAUX is available at least 450ms before the main output is within regulation Blinking of the input/AC LED –  $V_{IN}$  <  $80V_{AC}$  (the low transitioned signal represents blinking of the input LED.

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

#### **Control and Status**

The Rectifier provides three means for monitor/control: analog, PMBus™, or the GE Galaxy-based RS485 protocol. Details of analog control and the PMBus™ based protocol are provided in this data sheet. GE will provide separate application notes on the Galaxy RS485 based protocol for users to interface to the rectifier. Contact your local GE representative for details.

**Control hierarchy:** Some features, such as output voltage, can be controlled both through hardware and firmware. For example, the output voltage is controlled both by a signal pin (Vprog) and a PMBus command, (OPERATION).

Using output voltage as an example; the Vprog signal pin has ultimate control of the output voltage until the Vprog is either >  $3V_{DC}$  or a no connect. When the programming signal via Vprog is either a no connect or >  $3V_{DC}$ , it is ignored, the output voltage is set at its nominal  $54V_{DC}$ .

Unless otherwise noted, the signal pin controls the feature until the firmware command is executed. However, once the firmware command has been executed, the signal pin is ignored. In the above example, the rectifier will no longer 'listen' to the Vprog pin if the OPERATION command has been executed.

In summary, Vprog is utilized for initialized configuration of the output voltage and to change the output voltage when PMBus is not used for that function.

**Analog controls:** Details of analog controls are provided in this data sheet under Feature Specifications.

Signal Reference: Unless otherwise noted, all signals are referenced to Logic\_GRD. See the Signal Definitions Table at the end of this document for further description of all the signals.

Logic\_GRD is isolated from the main output of the rectifier for PMBus communications. Communications and the 5V standby output are not connected to main power return (Vout(-)) and can be tied to the system digital ground point selected by the user. (Note that RS485 communications is referenced to Vout(-), main power return of the rectifier).

Logic\_GRD is capacitively coupled to Frame\_GRD inside the rectifier. The maximum voltage differential between Logic GRD and Frame GRD should be less than 100V<sub>DC</sub>.

## **Control Signals**

**Protocol:** This signal pin defines the communications mode setting of the rectifier. Two different states can be configured. State #1 is the I²C application in which case the protocol pin should be left a no-connect. State #2 is the RS485 mode application in which case a resistor value between  $1k\Omega$  and  $5k\Omega$  should be present between this pin and Vout ( - ).

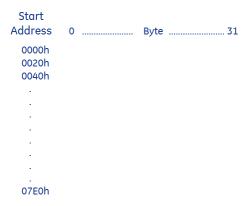

Device address in I<sup>2</sup>C mode: Address bits A3, A2, A1, A0 set the specific address of the  $\mu$ P in the rectifier. With these four bits, up to sixteen (16) rectifiers can be independently addressed on a single I<sup>2</sup>C bus. These four bits are configured

by two signal pins, Unit\_ID and Rack\_ID. The least significant bit x (LSB) of the address byte is set to either write [0] or read [1]. A write command instructs the rectifier. A read command accesses information from the rectifier.

| Device    | Address | Address Bit Assignments<br>(Most to Least Significant) |   |   |     |    |    |    |     |

|-----------|---------|--------------------------------------------------------|---|---|-----|----|----|----|-----|

|           |         | 7                                                      | 6 | 5 | 4   | 3  | 2  | 1  | 0   |

| μΡ        | 40 – 4F | 1                                                      | 0 | 0 | Α3  | A2 | A1 | Α0 | R/W |

| Broadcast | 00      | 0                                                      | 0 | 0 | 0   | 0  | 0  | 0  | 0   |

|           |         | MSB L                                                  |   |   | LSB |    |    |    |     |

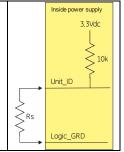

Unit\_ID: Up to 10 different units are selectable

A voltage divider between 3.3V and Logic\_GRD configures Unit\_ID. Internally a  $10 \mathrm{k}\Omega$  resistor is pulled up to  $3.3 \mathrm{VDC}$ . A pull down resistor Rs needs to be connected between pin Unit\_ID and Logic\_GRD.

| Unit_ID | Voltage level | Rs (± 0.1%) |

|---------|---------------|-------------|

| Invalid | 3.30          |             |

| 1       | 3.00          | 100k        |

| 2       | 2.67          | 45.3k       |

| 3       | 2.34          | 24.9k       |

| 4       | 2.01          | 15.4k       |

| 5       | 1.68          | 10.5k       |

| 6       | 1.35          | 7.15k       |

| 7       | 1.02          | 4.99k       |

| 8       | 0.69          | 2.49k       |

| 9       | 0.36          | 1.27k       |

| 10      | 0             | 0           |

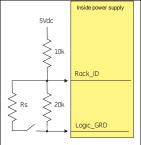

Rack\_ID: Up to 8 different combinations are selectable.

A voltage divider between  $5V_{DC}$  and  $Logic\_GRD$  configures Rack\_ID. The  $10k-20k\Omega$  divider sets the initial voltage level to  $3.3V_{DC}$ . A switch between each  $R_S$  value changes the Rack\_ID level according to the table below.

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

| Rack_ID | Voltage level | Rs (± 0.1%) |

|---------|---------------|-------------|

| 1       | 3.3           | open        |

| 2       | 2.8           | 35.2k       |

| 3       | 2.3           | 15k         |

| 4       | 1.8           | 8k          |

| 5       | 1.4           | 4.99k       |

| 6       | 1             | 2.87k       |

| 7       | 0.5           | 1.27k       |

| 8       | 0             | 0           |

**Configuration of the A3 – A0 bits:** The rectifier will determine the configured address based on the Unit\_ID and Rack\_ID voltage levels as follows (the order is A3 – A0):

|         |   |      | · ·  | Jnit_ID |      |      |

|---------|---|------|------|---------|------|------|

|         |   | 1    | 2    | 3       | 4    | 5    |

|         | 1 | 0000 | 0001 | 0010    | 0011 |      |

|         | 2 | 0100 | 0101 | 0110    | 0111 |      |

|         | 3 | 1000 | 1001 | 1010    | 1011 |      |

| Dook ID | 4 | 1100 | 1101 | 1110    | 1111 |      |

| Rack_ID | 5 |      |      |         |      |      |

|         | 6 | 0000 | 0001 | 0010    | 0011 | 0100 |

|         | 7 | 0101 | 0110 | 0111    | 1000 | 1001 |

|         | 8 | 1010 | 1011 | 1100    | 1101 | 1110 |

Unit  $\times$  Rack:  $4 \times 4$  and  $5 \times 3$

|         |   |      | Unit_ID |      |      |      |  |  |  |  |  |  |

|---------|---|------|---------|------|------|------|--|--|--|--|--|--|

|         |   | 6    | 7       | 8    | 9    | 10   |  |  |  |  |  |  |

|         | 1 | 0000 | 0001    |      |      |      |  |  |  |  |  |  |

|         | 2 | 0010 | 0011    |      |      |      |  |  |  |  |  |  |

|         | 3 | 0100 | 0101    |      |      |      |  |  |  |  |  |  |

| Dook ID | 4 | 0110 | 0111    | 0000 | 0001 | 0010 |  |  |  |  |  |  |

| Rack_ID | 5 | 1000 | 1001    | 0011 | 0100 | 0101 |  |  |  |  |  |  |

|         | 6 | 1010 | 1011    | 0110 | 0111 | 1000 |  |  |  |  |  |  |

|         | 7 | 1100 | 1101    | 1001 | 1010 | 1011 |  |  |  |  |  |  |

|         | 8 | 1110 | 1111    | 1100 | 1101 | 1110 |  |  |  |  |  |  |

Unit  $\times$  Rack:  $2 \times 8$  and  $3 \times 5$

Address detection: The Slot\_ID pin must be shorted to Vout(-) in order to deliver output power. This connection provides a second interlock feature. (In RS485 mode the slot\_ID resistance to Vout(-) is sufficient to sense the interlock feature)

**Device address in RS485 mode:** The address in RS485 mode is divided into three components; Bay\_ID, Slot\_ID and Shelf\_ID

**Bay\_ID:** The Unit\_ID definition in I<sup>2</sup>C mode becomes the bay id in RS485 mode.

$\textbf{Slot\_ID:}$  Up to 10 different rectifiers could be positioned across a 19" shelf if the rectifiers are located vertically within the shelf. The resistor below needs to be placed between Slot\_ID and Vout ( - ). Internal pull-up to 3.3V is  $10 k\Omega.$

| Slot    | Resistor | Voltage |

|---------|----------|---------|

| invalid | none     | 3.3V    |

| 1       | 100k     | 3V      |

| 2       | 45.3k    | 2.67V   |

| 3       | 24.9k    | 2.34V   |

| 4       | 15.4k    | 2.01V   |

| 5       | 10.5k    | 1.68V   |

| Slot | Resistor | Voltage |

|------|----------|---------|

| 6    | 7.15k    | 1.35V   |

| 7    | 4.99k    | 1.02V   |

| 8    | 2.49k    | 0.69V   |

| 9    | 1.27k    | 0.36V   |

| 10   | 0        | 0       |

|      |          |         |

**Shelf\_ID:** When placed horizontally up to 10 shelves can be stacked on top of each other in a fully configured rack. The shelf will generate the precision voltage level tabulated below referenced to Vout ( - ).

| Shelf | V <sub>MIN</sub> | $V_{NOM}$ | V <sub>MAX</sub> |

|-------|------------------|-----------|------------------|

| 1     | 2.3              | 2.5       | 2.7              |

| 2     | 4.7              | 5.0       | 5.3              |

| 3     | 7.4              | 7.5       | 7.6              |

| 4     | 9.5              | 10.0      | 10.5             |

| 5     | 11.8             | 12.5      | 13.2             |

| 6     | 14.2             | 15.0      | 15.8             |

| 7     | 16.6             | 17.5      | 18.4             |

| 8     | 19               | 20.0      | 21               |

| 9     | 21.3             | 22.5      | 23.6             |

| 10    | 23.8             | 25.0      | 26.3             |

**Global Broadcast:** This is a powerful command because it instruct all rectifiers to respond simultaneously. A **read** instruction should never be accessed globally. The rectifier should issue an 'invalid command' state if a 'read' is attempted globally.

For example, changing the 'system' output voltage requires the global broadcast so that all paralleled rectifiers change their output simultaneously. This command can also turn OFF the 'main' output or turn ON the 'main' output of all rectifiers simultaneously. Unfortunately, this command does have a side effect. Only a single rectifier needs to pull down the ninth *acknowledge* bit. To be certain that each rectifier responded to the global instruction, a *READ* instruction should be executed to each rectifier to verify that the command properly executed. The GLOBAL BROADCAST command should only be executed for write instructions to slave devices.

**Voltage programming (V**<sub>prog</sub>): Hardware voltage programming controls the output voltage until a software command to change the output voltage is executed. Software voltage programming permanently overrides the hardware margin setting and the rectifier no longer listens

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

to any hardware margin settings until power to the controller is interrupted, for example if input power or bias power is recycled.

When bias power is recycled to the controller the controller restarts into its default configuration, programmed to set the output as instructed by the  $V_{\text{prog}}$  pin. Again, subsequent software commanded settings permanently override the margin setting. As an example, adding a resistor between  $V_{\text{prog}}$  and Logic\_GRD is an effective way of changing the factory set point of the rectifier to whatever voltage level is desired by the user during initial start-up.

The Vprog pin level should be set by a divider from 3.3Vdc to Logic\_GRD external to the rectifier as shown in the graph. Programming can be accomplished either by a resistor divider or by a voltage source injecting a precision voltage level into the Vprog pin. Above 3Vdc the rectifier sets the output to its default state.

An analog voltage on this signal can vary the output voltage from 44 Vdc to 58 Vdc.

Factory default setting driven by Vprog

Load share (Ishare): This is a single wire analog signal that is generated and acted upon automatically by rectifiers connected in parallel. Ishare pins should be connected to each other for rectifiers, if active current share among the rectifiers is desired. No resistors or capacitors should get connected to this pin.

**ON/OFF:** Controls the main 54V<sub>DC</sub> output when either analog control or PMBus protocols are selected, as configured by the Protocol pin. This pin must be pulled low to turn **ON** the rectifier. The rectifier will turn **OFF** if either the **ON/OFF** or the **Interlock** pin is released. This signal is referenced to Logic\_GRD. Note that in RS485 mode this pin is ignored.

Interlock: This is a shorter pin utilized for hot-plug applications to ensure that the rectifier turns **OFF** before the power pins are disengaged. It also ensures that the rectifier turns **ON** only after the power pins have been engaged. Must be connected to V\_OUT(-) for the rectifier to be ON.

**8V\_INT:** Single wire connection between rectifiers, Provides bias to the DSP of an unpowered rectifier.

### **Status Signals**

**Module Present:** This signal is tied to Logic\_GRD inside the rectifier. It's intent is to provide a signal to the system that a rectifier is physically present in the slot.

Power Good Warning (PG#): This signal is HI when the main output is being delivered and goes LO if the main output is about to decay below regulation. Note that should a catastrophic failure occur, the signal may not be fast enough to provide a meaningful warning. PG# also pulses at a 1ms duty cycle if the unit is in overload.

**Fault#:** A TTL compatible status signal representing whether a Fault occurred. This signal needs to be pulled HI externally through a resistor. This signal goes LO for any failure that requires rectifier replacement. These faults may be due to:

- Fan failure

- Over-temperature shutdown

- Over-voltage shutdown

- Internal Rectifier Fault

Over temp warning (OTW#): A TTL compatible status signal representing whether an over temperature exists. This signal needs to be pulled HI externally through a resistor.

If an over temperature should occur, this signal would pull LO for approximately 10 seconds prior to shutting down the rectifier. In its default configuration, the unit would restart if internal temperatures recover within normal operational levels. At that time the signal reverts back to its open collector (HI) state.

Power\_CAP: This signal is HI when the main output is 3000w and goes LO when the main output is 1400w.

#### **Serial Bus Communications**

The I<sup>2</sup>C interface facilitates the monitoring and control of various operating parameters within the unit and transmits these on demand over an industry standard I<sup>2</sup>C Serial bus.

All signals are referenced to 'Logic\_GRD'.

**Pull-up resistors:** The clock, data, and Alert# lines do not have any internal pull-up resistors inside the rectifier. The customer is responsible for ensuring that the transmission impedance of the communications lines complies with I<sup>2</sup>C and SMBus standards.

Serial Clock (SCL): The clock pulses on this line are generated by the host that initiates communications across the I<sup>2</sup>C Serial bus. This signal needs to be pulled HI externally through a resistor as necessary to ensure that rise and fall time timing and the maximum sink current is in compliance to the I<sup>2</sup>C /SMBus specifications.

Serial Data (SDA): This line is a bi-directional data line. This signal needs to be pulled HI externally through a resistor as

## CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

necessary to ensure that rise and fall time timing and the maximum sink current is in compliance to the I $^2$ C /SMBus specifications.

**SMBUSAlert#:** This hardware signal pin is normally HI. When asserted (logic LO) it signifies to the system controller that the state of the power supply has changed or that communication errors occurred.

The SMBusAlert# line exciting the rectifier combines the Alert# functions of rectifier control and dual\_bus\_control.

### **Digital Feature Descriptions**

PMBus™ compliance: The rectifier is fully compliant to the Power Management Bus (PMBus™) rev1.2 requirements. This Specification can be obtained from <a href="https://www.pmbus.org">www.pmbus.org</a>.

'Manufacturer Specific' commands are used to support additional instructions that are not in the PMBus<sup>TM</sup> specification.

All communication over the PMBus interface must support the Packet Error Checking (PEC) scheme. The PMBus master must generate the correct PEC byte for all transactions, and check the PEC byte returned by the rectifier.

Non-volatile memory is used to store configuration settings. Not all settings programmed into the device are automatically saved into this non-volatile memory. Only those specifically identified as capable of being stored can be saved. (see the Table of Commands for which command parameters can be saved to non-volatile storage).

**Non-supported commands:** Non supported commands are flagged by setting the appropriate STATUS bit and issuing an Alert# to the 'host' controller.

If a non-supported read is requested the rectifier will return 0x00h for data.

**Data out-of-range:** The rectifier validates data settings and sets the data out-of-range bit and Alert# if the data is not within acceptable range.

Master/Slave: The 'host controller' is always the MASTER. Rectifiers are always SLAVES. SLAVES cannot initiate communications or toggle the Clock. SLAVES also must respond expeditiously at the command of the MASTER as required by the clock pulses generated by the MASTER.

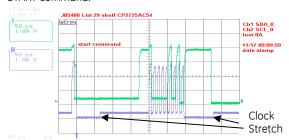

Clock stretching: The 'slave' µController inside the rectifier may initiate clock stretching if it is busy and it desires to delay the initiation of any further communications. During the clock stretch the 'slave' may keep the clock LO until it is ready to receive further instructions from the host controller. The maximum clock stretch interval is 25ms.

The host controller needs to recognize this clock stretching, and refrain from issuing the next clock signal, until the clock line is released, or it needs to delay the next clock pulse beyond the clock stretch interval of the rectifier. Note that clock stretching can only be performed after completion of transmission of the 9th ACK bit, the exception being the START command.

Figure 15. Example waveforms showing clock stretching.

I<sup>2</sup>C Bus Lock-Up detection: The device will abort any transaction and drop off the bus if it detects the bus being held low for more than 35ms.

**Communications speed:** Both 100kHz and 400kHz clock rates are supported. The rectifiers default to the 100kHz clock rate.

Packet Error Checking (PEC): The rectifier will not respond to commands without the trailing PEC. The integrity of communications is compromised if packet error correction is not employed. There are many functional features, including turning OFF the main output, that require validation to ensure that the desired command is executed.

PEC is a CRC-8 error-checking byte, based on the polynomial  $C(x) = x^8 + x^2 + x + 1$ , in compliance with PMBus<sup>TM</sup> requirements. The calculation is based in all message bytes, including the originating write address and command bytes preceding read instructions. The PEC is appended to the message by the device that supplied the last byte.

Alert#: The rectifier can issue Alert# driven from either its internal micro controller ( $\mu$ C) or from the I²C bus master selector stage. That is, the Alert# signal of the internal  $\mu$ C funnels through the master selector stage that buffers the Alert# signal and splits the signal to the two Alert# signal pins exiting the rectifier. In addition, the master selector stage signals its own Alert# request to either of the two Alert# signals when required.

The  $\mu$ C driven Alert# signal informs the 'master/host' controller that either a STATE or ALARM change has occurred. Normally this signal is HI. The signal will change to its LO level if the rectifier has changed states and the signal will be latched LO until the rectifier receives a 'clear\_faults' instruction.

The signal will be triggered for any state change, including the following conditions;

- VIN under or over voltage

- Vout under or over voltage

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

- IOUT over current

- Over Temperature warning or fault

- Fan Failure

- Communication error

- PEC error

- Invalid command

- Internal faults

- Both Alert#\_0 and -1 are asserted during power up to notify the master that a new rectifier has been added to the hus

The rectifier will clear the Alert# signal (release the signal to its HI state) upon the following events:

- Receiving a CLEAR\_FAULTS command

- Bias power to the processor is recycled

The rectifier will re-assert the Alert line if the internal state of the rectifier has changed, even if that information cannot be reported by the status registers until a clear\_faults is issued by the host. If the Alert asserts, the host should respond by issuing a clear\_faults to retire the alert line (this action also provides the ability to change the status registers). This action triggers another Alert assertion because the status registers changed states to report the latest state of the rectifier. The host is now able to read the latest reported status register information and issue a clear\_faults to retire the Alert signal.

**Re-initialization:** The I<sup>2</sup>C code is programmed to re-initialize if no activity is detected on the bus for 5 seconds. Re-initialization is designed to guarantee that the I<sup>2</sup>C  $\mu$ Controller does not hang up the bus. Although this rate is longer than the timing requirements specified in the SMBus specification, it had to be extended in order to ensure that a re-initialization would not occur under normal transmission rates. During the few  $\mu$ seconds required to accomplish re-initialization the I<sup>2</sup>C  $\mu$ Controller may not recognize a command sent to it. (i.e. a start condition).

Read back delay: The rectifier issues the Alert# notification as soon as the first state change occurred. During an event a number of different states can be transitioned to before the final event occurs. If a read back is implemented rapidly by the host a successive Alert# could be triggered by the transitioning state of the rectifier. In order to avoid successive Alert# s and read back and also to avoid reading a transitioning state, it is prudent to wait more than 2 seconds after the receipt of an Alert# before executing a read back. This delay will ensure that only the final state of the rectifier is captured.

Successive read backs: Successive read backs to the rectifier should not be attempted at intervals faster than every one second. This time interval is sufficient for the internal processors to update their data base so that successive reads provide fresh data.

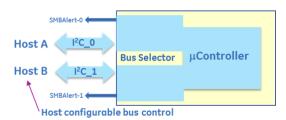

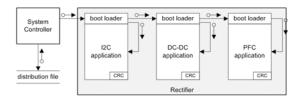

#### **Dual Master Control:**

Two independent  $I^2C$  lines provide true communications bus redundancy and allow two independent controllers to

sequentially control the rectifier. For example, a short or an open connection in one of the I<sup>2</sup>C lines does not affect communications capability on the other I<sup>2</sup>C line. Failure of a 'master' controller does not affect the rectifiers and the second 'master' can take over control at any time.

Conceptually a Digital Signal Processor (DSP) referenced to Vout(-) of the rectifier provides secondary control. A Bidirectional Isolator provides the required isolation between power GRD, Vout(-) and signal GRD (Logic\_GRD). A secondary micro controller provides instructions to and receives operational data from the DSP. The secondary micro controller also controls the communications over two independent I<sup>2</sup>C lines to two independent system controllers.

The secondary micro controller is designed to default to  $1^2C_0$  when powered up. If only a single system controller is utilized, it should be connected to  $1^2C_0$ . In this case the  $1^2C_1$  line is totally transparent as if it does not exist.

If two independent system controllers are utilized, then one of them should be connected to  $I^2C\_0$  and the other to  $I^2C\_1$ .

At power up the master connected to  $1^2C_0$  has control of the bus. See the section on Dual Master Control for further description of this feature.

Conceptual representation of the dual I<sup>2</sup>C bus system.

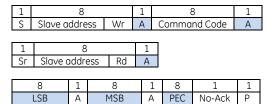

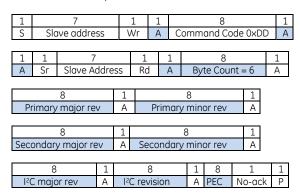

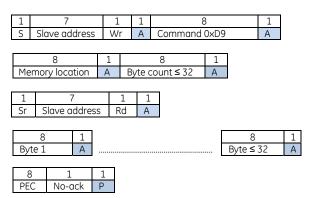

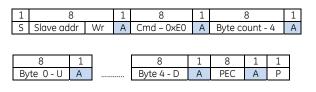

#### **PMBus™** Commands

**Standard instruction:** Up to two bytes of data may follow an instruction depending on the required data content.

Analog data is always transmitted as LSB followed by MSB.

PEC is mandatory and includes the address and data fields.

|   | 1 0           |   |          | 1 0          | O   |     |   |   |

|---|---------------|---|----------|--------------|-----|-----|---|---|

| S | Slave address | , | A Comman | d Code       | e A |     |   |   |

|   |               |   |          |              |     |     |   |   |

|   | 8             | 1 |          | 8            | 1   | 8   | 1 | 1 |

| L | ow data byte  | Α | Hiç      | gh data byte | Α   | PEC | Α | Р |

Master to Slave [1] Slave to Master

SMBUS annotations; S – Start , Wr – Write, Sr – re-Start, Rd –

A – Acknowledge, NA – not-acknowledged, P – Stop

# CP3000/3500AC54TE Global Platform High Efficiency Rectifier

Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3500W; 5 Vdc @ 10W

**Standard READ:** Up to two bytes of data may follow a READ request depending on the required data content. Analog data is always transmitted as LSB followed by MSB. PEC is mandatory and includes the address and data fields.

| 1 |     | 7             |              |   | 1     |  | 1  |       | 8        |    | 1 |

|---|-----|---------------|--------------|---|-------|--|----|-------|----------|----|---|

| S |     | Slave address |              |   | Wr    |  | Α  | Commo | and Code | (D | Α |

|   |     |               |              |   |       |  |    |       |          |    |   |

|   | 1 7 |               |              |   | 1 1 8 |  | 3  | 1     |          |    |   |

|   | S   | r             | Slave Addres | S | Rd    |  | Α  | LS    | SB       | Α  |   |

|   |     |               |              |   |       |  |    |       |          |    |   |

|   | 8   |               |              | 1 |       |  | 8  | 3     | 1        |    | 1 |

|   | MSB |               |              | Α | ١     |  | PE | EC    | NA       |    | Р |

Block communications: When writing or reading more than two bytes of data at a time BLOCK instructions for WRITE and READ commands are used instead of the Standard Instructions above to write or read any number of bytes greater than two.

#### Block write format:

| 1 | 7              | 7    |        |   |   |   | 8     |     |   | 1 |   |

|---|----------------|------|--------|---|---|---|-------|-----|---|---|---|

| S | Slave add      | ress | Wr     | Α |   |   | Comm  | ode | Α |   |   |

|   |                |      |        |   |   |   |       |     |   |   | _ |

|   | 8              | 1    | . 8    |   | 1 |   | 8     | 1   |   |   |   |

|   | Byte count = N | J A  | Data   | 1 | Α | D | ata 2 | A   | ٨ |   |   |

|   |                |      |        |   |   |   |       |     |   |   |   |

|   | 8              | 1    | 8      |   | 1 |   | 8     | 3   | 1 | 1 | 1 |

|   |                | Α    | Data I | V | 4 | ١ | PEC   |     | Α | Р | 1 |

#### Block read format:

| 1 |    | 7            |      |   | 1   | 1   |   | 8      |      |      | 1 |

|---|----|--------------|------|---|-----|-----|---|--------|------|------|---|

| S | S  | lave addres  | S    | V | ۷r  | Α   |   | Commar | nd ( | Code | Α |

|   |    |              |      |   |     |     |   |        |      |      |   |

|   | 1  | 7            |      |   | 1   |     | 1 |        |      |      |   |

|   | Sr | Slave Ad     | dres | S | Ro  | t   | Α |        |      |      |   |

|   |    |              |      |   |     |     |   |        |      |      |   |

|   |    | 8            |      | 1 | 8   | 3   | 1 | 8      |      | 1    |   |

|   | Ву | te count = N | J    | Α | Dat | a 1 | Α | Data 2 |      | Α    |   |

|   |    |              |      |   |     |     |   |        |      |      |   |

|   |    | 8            | 1    |   | 8   |     | 1 | 8      |      | 1    | 1 |

**Linear Data Format:** The definition is identical to Part II of the PMBus Specification. All standard PMBus values, with the exception of output voltage related functions, are represented by the linear format described below. Output voltage functions are represented by a 16 bit mantissa. Output voltage has a E=9 constant exponent.

A Data N

The Linear Data Format is a two byte value with an 11-bit, two's complement mantissa and a 5-bit, two's complement exponent or scaling factor, its format is shown below.

|     | Data Byte High    |  |  |  |  |  |  |   | Data Byte Low |     |       |       |   |   |   |   |

|-----|-------------------|--|--|--|--|--|--|---|---------------|-----|-------|-------|---|---|---|---|

| Bit | Bit 7 6 5 4 3 2 1 |  |  |  |  |  |  | 0 | 7             | 6   | 5     | 4     | 3 | 2 | 1 | 0 |

|     | Exponent (E)      |  |  |  |  |  |  |   |               | Man | tisso | (M) c |   |   |   |   |

The relationship between the Mantissa, Exponent, and Actual Value (V) is given by the following equation:

$$V = M * 2^{E}$$

Where: V is the value, M is the 11-bit, two's complement mantissa, E is the 5-bit, two's complement exponent

### Standard features

**Supported features that are not readable:** The commands below are supported at the described setting but they cannot be read back through the command set.

| Command               | Comments                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| ON_OFF_CONFIG (0x02)  | Both the CNTL pin, and the OPERATION command, enabling or disabling the output, are supported. Other options are not supported. |

| Capability (0×19)     | 400KHz, ALERT#                                                                                                                  |

| PMBus revision (0x98) | 1.2                                                                                                                             |

Status and Alarm registers: The registers are updated with the latest operational state of the rectifier. For example, whether the output is ON or OFF is continuously updated with the latest state of the rectifier. However, alarm information is maintained until a clear\_faults command is received from the host. For example, the shutdown or OC\_fault bits stay in their alarmed state until the host clears the registers.

A clear\_faults clears all registers. If a fault still persists after the clear\_faults is commanded, the register bit annunciating the fault is reset again.

#### PMBus™ Command set:

| Command                  | Hex<br>Code | Data<br>Field | Non-<br>Volatile<br>Memory<br>Storage <sup>19</sup><br>/ Default |

|--------------------------|-------------|---------------|------------------------------------------------------------------|

| Operation                | 0x01        | 1             | Yes/80                                                           |

| Clear_Faults             | 0x03        | -             |                                                                  |