# PI3HDX1204D

## HDMI 2.0 6Gbps Linear ReDriver

#### **Features**

- Support HDMI 2.0 Serial Link per each channels

- Dual-mode Displayport to HDMI 2.0 level shifter support

- 1Gbps up to 8Gbps linear equalizer

- Increases high-frequency signal level to help Receiver DFE achieve low BER

- Very Low Additive Jitter: 6ps @ 6Gb/s

- Transparent to DDC Source-side to Sink-side device communication

- Per Channel selectable adjustment of receiver equalization, output swing and flat gain

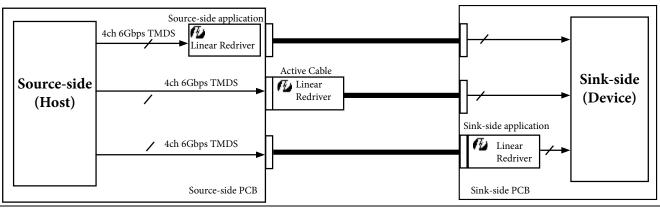

- Flexible ReDriver location; Source, Sink and Active Cable

- Pin mode or I2C selectable device programming

- I2C Master or slave selection

- Each channel polarity or channel order swap

- 4-bit selectable address for I<sup>2</sup>C

- Power Supply voltage: 3.3V

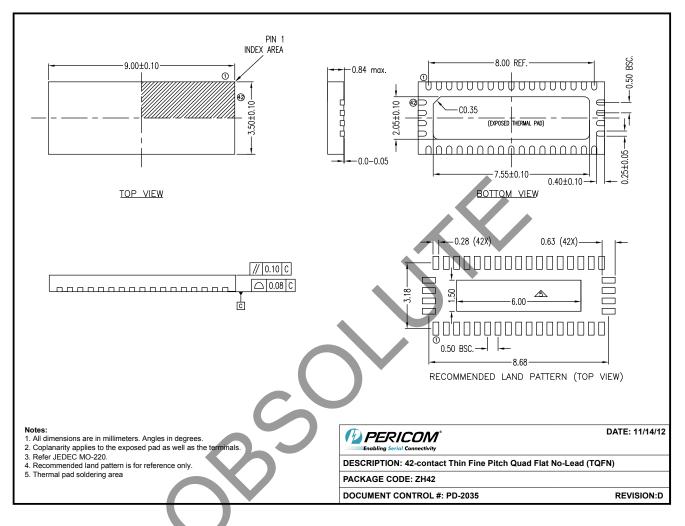

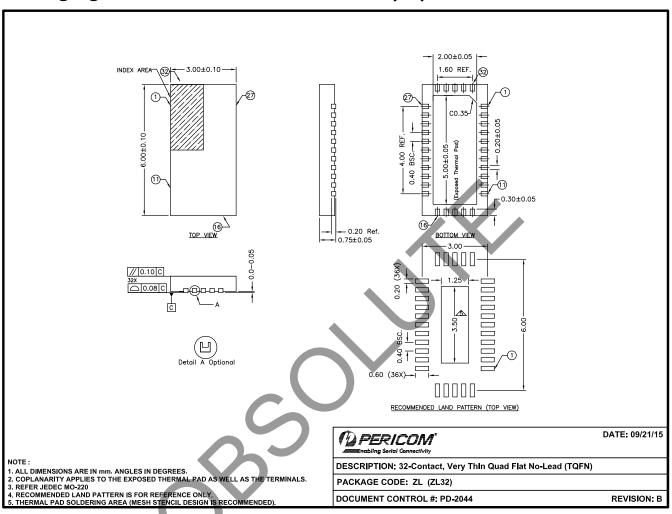

- Package (Pb-Free & Green): 42-pin TQFN, 32-pin TQFN

#### **General Description**

Pericom Semiconductor's PI3HDX1204D linear redriver is suitable for HDMI 2.0 Redriver and Dual mode Displayport level shifter application.

The linear redriver offers unique advantage of the flexible placement between the source and sink-side devices. The linearity enables redriver to place at any location of the signal transmission trace such as on the Source or Sink-side PCB trace, inside of the Active cable. Pericom linear redriver technology provide 2 times better RJ and DJ jitter performance (Additive RJ = 0.23 ps <sub>RMS</sub>, Additive DJ = 6.5 ps)

Linear redriver allows DDC channel to connect directly between Source and Sink device. This end-to-end sideband channel connection natively eliminates the potential interrupt compatibility issues caused by the EDID configuration registers exchange. Also it does not require special detection program handling for the Active cable application like Adaptor ID bits.

PI3HDX1204D extends 4 channels  $100\Omega$  DC or AC differential signals across the other distant data pathways on the user's platform.

#### Applications

- PC, AV Receiver, Set Top Box, Video Players

- TV, Display Monitors, Active Cables

#### **Ordering Information**

| Part Number     | Package Description                                        |

|-----------------|------------------------------------------------------------|

| PI3HDX1204DZHEX | 42-TQFN (3.5x9mm), Pb-free, Tape/Reel, Package code: ZH 42 |

| PI3HDX1204DZLEX | 32-pin TQFN(3x6mm), Pb-free, Tape/Reel, Package code:ZL 42 |

#### **Typical Application Block Diagram**

1

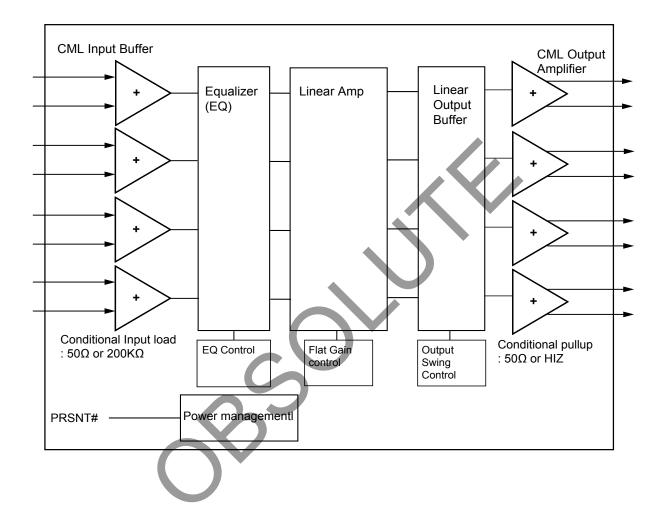

## **Block Diagram**

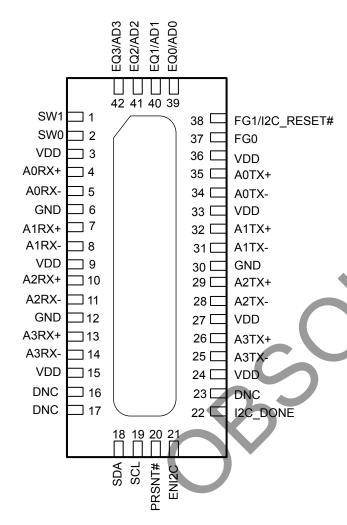

## Pin Configuration (42-pin TQFN)

**Note:** In TMDS Data and Clock Differential Pairs of Input and Output, the polarity (+/- or P/N) of each pairs and data A0, A1, A2, A3 channels can use interchangeably. Output pins of polarity and data channel will always follow the input polarity and data channel changes.

As following are examples for Source and Sink-side application.

1) Source-side polarity +/- swap per each channel from **AxRx+/-:AxTx+/-** to **AxRX-/+:AxTx-/+.** "x" means each channel numbers 0, 1, 2, 3.

| Pin# | Pin Name   | Pin# | Pin Name   |

|------|------------|------|------------|

| 4    | A0RX-      | 35   | A0TX-      |

| 5    | A0RX+      | 34   | A0TX+      |

| 7    | A1RX-      | 32   | A1TX-      |

| 8    | A1RX+      | 31   | A1TX+      |

| 10   | A2RX-      | 29   | A2TX-      |

| 11   | A2RX+      | 28   | A2TX+      |

| 13   | A3RX-(clk) | 26   | A3TX-(clk) |

| 14   | A3RX+(clk) | 25   | A3TX+(clk) |

2) Sink-side channel order swap from <u>AxRX/AyRX/AzRX/</u> <u>A3RX(clk): AxTX/AyTX/AzTX/A3TX(clk)</u> to <u>A3RX(clk)/</u> <u>AxRX/AyRX/AzRX: A3TX(clk)/AxTX/AyTX/AzTX</u>.

| Pin# | Pin Name   | Pin# | Pin Name   |

|------|------------|------|------------|

| 4    | A3RX+(clk) | 35   | A3TX+(clk) |

| 5    | A3RX-(clk) | 34   | A3TX-(clk) |

| 7    | AxRX+      | 32   | AxTX+      |

| 8    | AxRX-      | 31   | AxTX-      |

| 10   | AyRX+      | 29   | AyTX+      |

| 11   | AyRX-      | 28   | АуТХ-      |

| 13   | AzRX+      | 26   | AzTX+      |

| 14   | AzRX-      | 25   | AzTX-      |

3

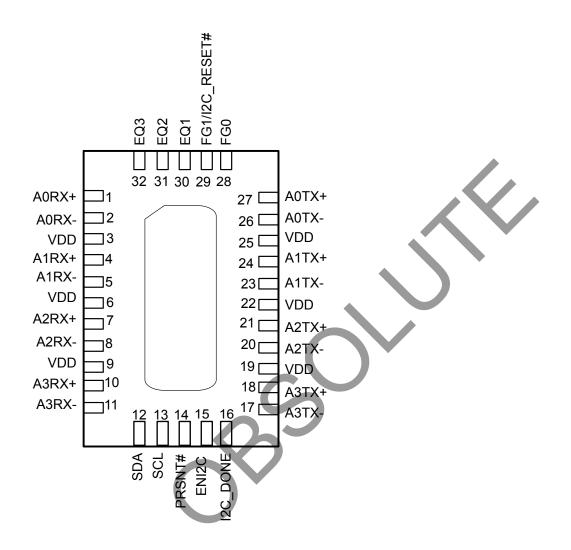

## Pin Configuration (32-pin TQFN)

HDMI 2.0 6Gbps Linear ReDriver

## Pin Description (42-pin TQFN)

| Pin #           | Pin Name        | Туре | Description                                                                                                                                                                                                                                                                                |

|-----------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Sig        | nals            |      |                                                                                                                                                                                                                                                                                            |

| 4<br>5          | A0RX+<br>A0RX-  | I    | TMDS inputs for Channel A0; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                        |

| 35<br>34        | A0TX+,<br>A0TX- | 0    | TMDS outputs for Channel A0; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                         |

| 7<br>8          | A1RX+,<br>A1RX- | I    | TMDS inputs for Channel A1; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                        |

| 32<br>31        | A1TX+,<br>A1TX- | 0    | TMDS outputs for Channel A1; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                         |

| 10<br>11        | A2RX+,<br>A2RX- | I    | TMDS inputs for Channel A2; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                        |

| 29<br>28        | A2TX+,<br>A2TX- | 0    | TMDS outputs for Channel A2; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                         |

| 13<br>14        | A3RX+,<br>A3RX- | Ι    | TMDS inputs for Channel A3; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                        |

| 26<br>25        | A3TX+,<br>A3TX- | 0    | TMDS outputs for Channel A3; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                         |

| Control S       | Signals         |      |                                                                                                                                                                                                                                                                                            |

| 16,17           | DNC             |      | Do Not Connect                                                                                                                                                                                                                                                                             |

| 19              | SCL             | I/O  | I <sup>2</sup> C SCL Clock. In Master mode (ENI2C floating), SCL is an output. Otherwise it is an input.                                                                                                                                                                                   |

| 18              | SDA             | I/O  | J <sup>2</sup> C SDA data input/output.                                                                                                                                                                                                                                                    |

| 23              | DNC             |      | Do Not Connect                                                                                                                                                                                                                                                                             |

| 20              | PRSNT#          | Ι    | This pin is active in both PIN mode (ENI2C=LOW) and I2C mode (ENI2C=HIGH). Cable present detect input. This pin has internal 100k $\Omega$ pull-up. When High, a cable is not present, and the device is put in lower power mode. When LOW, the device is enabled and in normal operation. |

| 21              | ENI2C           | Ι    | Enable I2C; When LOW, each channel is programmed by the external pin voltage.<br>When HIGH, each channel is<br>programmed by the data stored in the I <sup>2</sup> C bus. When floating, master mode (Read<br>External EEPROM)                                                             |

| 39,40,<br>41,42 | EQ[3:0]         | Ι    | EQ setting; Inputs with internal $100$ k $\Omega$ pull-up. This pins set the amount of Equalizer Boost in all channels, when ENI2C is LOW.                                                                                                                                                 |

| 41,42           | AD[3:0]         | Ι    | $I^2C$ programmable address bits with internal 100k $\Omega$ pull-up.                                                                                                                                                                                                                      |

| 1,2             | SW[1:0]         | Ι    | Swing Control; Inputs with internal $100k\Omega$ pull-up. This pin sets the output Voltage Level in all channel when ENI2C is LOW.                                                                                                                                                         |

| 38,37           | FG[1:0]         | Ι    | Flat Gain Control; Inputs with internal $100$ k $\Omega$ pull up resistor. Sets the output flat gain level on all channels when ENI2C is low.                                                                                                                                              |

## PI3HDX1204D

HDMI 2.0 6Gbps Linear ReDriver

| Pin #                          | Pin Name   | Туре | Description                                                                                                                                                                                         |

|--------------------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38                             | I2C_RESET# | Ι    | I2C reset pin; Inputs with internal 100k $\Omega$ pull up resistor. Reset pin for I <sup>2</sup> C. When set low, reset the registers to default state.                                             |

| 22                             | I2C_DONE   | 0    | <ul> <li>I2C EEPROM load done pin; Valid register load status output, use for daisy chain master.</li> <li>Low = External EEPROM load failed</li> <li>HIGH = External EEPROM load passed</li> </ul> |

| Power Pins                     | S          |      |                                                                                                                                                                                                     |

| 3, 9, 15,<br>24, 27, 33,<br>36 | VDD        | PWR  | 3.3V Power Supply                                                                                                                                                                                   |

| 6, 12, 30,                     | GND        | GND  | Ground                                                                                                                                                                                              |

| Center<br>Pad                  | GND        | GND  | Exposed Ground pad.                                                                                                                                                                                 |

All trademarks are property of their respective owners.

HDMI 2.0 6Gbps Linear ReDriver

## Pin Description (32-pin TQFN)

| Pin #       | Pin Name            | Туре | Description                                                                                                                                                                                                                                                                                         |

|-------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Signa  | ls                  | •    |                                                                                                                                                                                                                                                                                                     |

| 1<br>2      | A0RX+<br>A0RX-      | I    | TMDS inputs for Channel A0; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                 |

| 27<br>26    | A0TX+,<br>A0TX-     | 0    | TMDS outputs for Channel A0; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                  |

| 4<br>5      | A1RX+,<br>A1RX-     | Ι    | TMDS inputs for Channel A1; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                 |

| 24<br>23    | A1TX+,<br>A1TX-     | 0    | TMDS outputs for Channel A1; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                  |

| 7<br>8      | A2RX+,<br>A2RX-     | Ι    | TMDS inputs for Channel A2; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                 |

| 21<br>20    | A2TX+,<br>A2TX-     | 0    | TMDS outputs for Channel A2; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                  |

| 10<br>11    | A3RX+,<br>A3RX-     | Ι    | TMDS inputs for Channel A3; with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                 |

| 18<br>17    | A3TX+,<br>A3TX-     | 0    | TMDS outputs for Channel A3; with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                                                  |

| Control Sig | gnals               |      |                                                                                                                                                                                                                                                                                                     |

| 12          | SDA                 | I/O  | I <sup>2</sup> C SDA data input/output.                                                                                                                                                                                                                                                             |

| 13          | SCL                 | I/O  | 1 <sup>2</sup> C SCL Clock; In master mode (ENI2C floating), SCL is an output. Otherwise it is an input.                                                                                                                                                                                            |

| 14          | PRSNT#              | Ι    | Cable Present Detect pin;<br>This pin is active in both PIN mode (ENI2C=LOW) and I2C mode<br>(ENI2C=HIGH). This pin has internal $100K\Omega$ pull-up. When High, a cable is not<br>present, and the device is put in lower power mode. When LOW, the device is<br>enabled and in normal operation. |

| 15          | ENI2C               | I    | Enable I2C pin; When LOW, each channel is programmed by the external pin voltage. When HIGH, each channel is programmed by the data stored in the $I^2C$ bus. When floating, master mode (Read External EEPROM)                                                                                     |

| 32,31,30    | EQ[3:1]             | I    | EQ Control pin; Inputs with internal $100k\Omega$ pull-up. This pins set the amount of Equalizer Boost in all channel when ENI2C is LOW. Note: EQ0 tied "high", i.e. always "1".                                                                                                                    |

|             | AD[3:1]             | Ι    | I <sup>2</sup> C programmable address bits with internal 100kΩ pull-up. Note: AD0 tied "high", i.e. always "1".                                                                                                                                                                                     |

| 29          | FG1/I2C_RE-<br>SET# | I    | Flat Gain Control [1] or I2C Reset pin;<br>Inputs with internal 100k $\Omega$ pull up resistor. Sets the output flat gain level on all<br>channels when ENI2C is low.                                                                                                                               |

| 28          | FG0                 | Ι    | Flat Gain Control [0] pin; Inputs with internal $100k\Omega$ pull up resistor. Reset pin for I <sup>2</sup> C. When set low with reset the registers to default state.                                                                                                                              |

## PI3HDX1204D

HDMI 2.0 6Gbps Linear ReDriver

| Pin #                  | Pin Name | Туре | Description                                                                                                                              |

|------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 16                     | I2C_DONE | 0    | Valid register load status output, use for daisy chain master<br>Low = External EEPROM load failed<br>HIGH = External EEPROM load passed |

| Power Pins             |          |      |                                                                                                                                          |

| 3,6,9,<br>19,22,<br>25 | VDD      | PWR  | 3.3V Power Supply                                                                                                                        |

| Center Pad             | GND      | GND  | Exposed Ground pad.                                                                                                                      |

## **Functional Description**

#### **Power Enable function:**

One pin control or I2C control, when PRSNT# is set to HIGH, the IC goes into power down mode, both input and output termination set to  $200k\Omega$  and High impedance respectively. Individual Channel Enabling is done through the I2C register programming.

#### **Equalization Setting:**

EQ[3:0] are the selection pins for the equalization selection for each channel.

| EQ3 | EQ2 | EQ1 | EQ0 | 6Gbps Input EQ(dB) |   |

|-----|-----|-----|-----|--------------------|---|

| 0   | 0   | 0   | 0   | 3.6                |   |

| 0   | 0   | 0   | 1   | 4.0                |   |

| 0   | 0   | 1   | 0   | 4.4                |   |

| 0   | 0   | 1   | 1   | 4.7                |   |

| 0   | 1   | 0   | 0   | 5.1                |   |

| 0   | 1   | 0   | 1   | 5.5                |   |

| 0   | 1   | 1   | 0   | 5.9                |   |

| 0   | 1   | 1   | 1   | 6.2                | • |

| 1   | 0   | 0   | 0   | 6.6                |   |

| 1   | 0   | 0   | 1   | 6.9                |   |

| 1   | 0   | 1   | 0   | 7.3                |   |

| 1   | 0   | 1   | 1   | 7.6                |   |

| 1   | 1   | 0   | 0   | 8.0                |   |

| 1   | 1   | 0   | 1   | 8.2                |   |

| 1   | 1   | 1   | 0   | 8.6                |   |

| 1   | 1   | 1   | 1   | 8.9                |   |

#### **Equalization Setting**

#### **Output -1 dB Compression Setting:**

SW1 and SW0 affect the linearity of the output when input amplitude changes.

| SW1 | SW0 | mVpp @100MHz | mVpp @3GHz (equ. @6Gbps) |

|-----|-----|--------------|--------------------------|

| 0   | 0   | 1100         | 1000                     |

| 0   | 1   | 1200         | 1100                     |

| 1   | 0   | 1300         | 1200                     |

| 1   | 1   | 1400         | 1300                     |

Note: This device support input swings up to 1.4V.

#### Flat Gain Setting:

| Flat Gain |     | its for the DC value. |  |

|-----------|-----|-----------------------|--|

| FG1       | FG0 | Gain                  |  |

| 0         | 0   | -3.5 dB               |  |

| 0         | 1   | -1.5 dB               |  |

| 1         | 0   | +0.5 dB               |  |

| 1         | 1   | +2.5 dB               |  |

|           |     |                       |  |

All trademarks are property of their respective owners.

## PI3HDX1204D

HDMI 2.0 6Gbps Linear ReDriver

## **I2C Programming**

| Address assignment |    |    |     |     |     |     |          |

|--------------------|----|----|-----|-----|-----|-----|----------|

| A6                 | A5 | A4 | A3  | A2  | A1  | A0  | R/W      |

| 1                  | 1  | 1  | AD3 | AD2 | AD1 | AD0 | 1=R, 0=W |

| Bit    | Туре | Power up condition | Control affected | Comment        |

|--------|------|--------------------|------------------|----------------|

| 7:0    | R    | Reserved           |                  |                |

| BYTE 1 |      |                    |                  | ·              |

| Bit    | Туре | Power up condition | Control affected | Comment        |

| 7:0    | R    | Reserved           |                  |                |

| BYTE 2 | 2    |                    |                  |                |

| Bit    | Туре | Power up condition | Control affected | Comment        |

| 7      | R/W  | 0                  | A3 Power down    |                |

| 6      | R/W  | 0                  | A2 Power down    |                |

| 5      | R/W  | 0                  | A1 Power down    |                |

| 4      | R/W  | 0                  | A0 Power down    |                |

| 3      | R/W  | 0                  | Reserved         | 1 = Power down |

| 2      | R/W  | 0                  | Reserved         |                |

|        | R/W  | 0                  | Reserved         |                |

| 1      |      | 0                  | Reserved         |                |

HDMI 2.0 6Gbps Linear ReDriver

| BYTE 3 |      |                    |                          |                  |                            |  |

|--------|------|--------------------|--------------------------|------------------|----------------------------|--|

| Bit    | Туре | Power up condition |                          | Control affected | Comment                    |  |

| 7      | R/W  | 0                  |                          | EQ3              |                            |  |

| 6      | R/W  | 0                  |                          | EQ2              |                            |  |

| 5      | R/W  | 0                  |                          | EQ1              | – Equalizer                |  |

| 4      | R/W  | 0                  |                          | EQ0              |                            |  |

| 3      | R/W  | 0                  | Channel A0 configuration | FG1              |                            |  |

| 2      | R/W  | 0                  |                          | FG0              | – Flat gain                |  |

| 1      | R/W  | 0                  |                          | SW1              | 0.                         |  |

| 0      | R/W  | 0                  |                          | SW0              | Swing                      |  |

| BYTE 4 | :    |                    |                          |                  |                            |  |

| Bit    | Туре | Power up condition |                          | Control affected | Comment                    |  |

| 7      | R/W  | 0                  |                          | EQ3              |                            |  |

| 6      | R/W  | 0                  |                          | EQ2              | – Equalizer<br>– Flat gain |  |

| 5      | R/W  | 0                  |                          | EQ1              |                            |  |

| 4      | R/W  | 0                  |                          | EQ0              |                            |  |

| 3      | R/W  | 0                  | Channel A1 configuration | FG1              |                            |  |

| 2      | R/W  | 0                  |                          | FG0              |                            |  |

| 1      | R/W  | 0                  |                          | SW1              | C .                        |  |

| 0      | R/W  | 0                  |                          | SW0              | Swing                      |  |

| BYTE 5 |      | Ch                 |                          |                  |                            |  |

| Bit    | Туре | Power up condition |                          | Control affected | Comment                    |  |

| 7      | R/W  | 0                  |                          | EQ3              |                            |  |

| 6      | R/W  | 0                  |                          | EQ2              | Equalizar                  |  |

| 5      | R/W  | 0                  |                          | EQ1              | – Equalizer                |  |

| 4      | R/W  | 0                  | Channel A2 and formation | EQ0              |                            |  |

| 3      | R/W  | 0                  | Channel A2 configuration | FG1              | Elat coir                  |  |

| 2      | R/W  | 0                  |                          | FG0              | – Flat gain                |  |

| 1      | R/W  | 0                  |                          | SW1              | Suring                     |  |

| 0      | R/W  | 0                  |                          | SW0              | Swing                      |  |

HDMI 2.0 6Gbps Linear ReDriver

| Bit    | Туре | Power up condition |                          | Control affected | Comment     |

|--------|------|--------------------|--------------------------|------------------|-------------|

| 7      | R/W  | 0                  |                          | EQ3              |             |

| 6      | R/W  | 0                  |                          | EQ2              |             |

| 5      | R/W  | 0                  |                          | EQ1              | Equalizer   |

| 4      | R/W  | 0                  |                          | EQ0              |             |

| 3      | R/W  | 0                  | Channel A3 configuration | FG1              |             |

| 2      | R/W  | 0                  |                          | FG0              | – Flat gain |

| 1      | R/W  | 0                  | 1                        | SW1              | . ·         |

| 0      | R/W  | 0                  |                          | SW0              | Swing       |

| BYTE 7 | ,    |                    |                          |                  | ·           |

| Bit    | Туре | Power up condition |                          | Control affected | Comment     |

| 7:0    | R/W  | Reserved           |                          |                  |             |

|        |      | 1                  |                          |                  |             |

3

### **PI3HDX1204D** HDMI 2.0 6Gbps Linear ReDriver

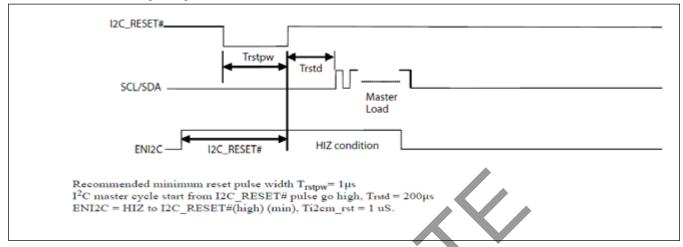

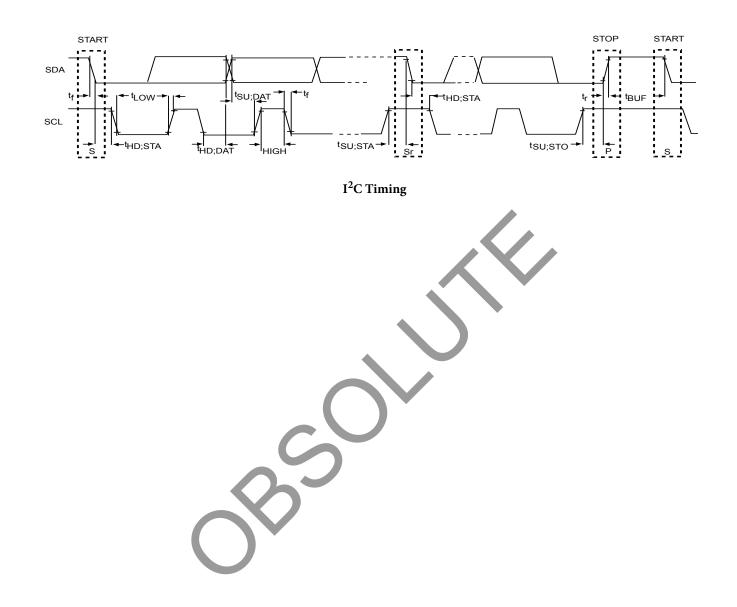

#### **Reset and I2C Timing Diagram**

#### **I2C Operation**

The integrated I2C interface operates as a master or slave

device depending on the pin ENI2C being HIZ or HIGH respectively. Standard mode (100Kbps) is supported with 7-bit addressing.

In the Slave mode (ENI2C = HIGH), the device supports Read/Write. The bytes must be accessed in sequential order from the lowest to the highest byte with the ability to stop after any complete byte has been transferred.

Address bits A3 to A0 are programmable to support multiple chips environment. The Data is loaded until a Stop sequence is issued.

Master mode (ENI2C = HIZ) supports up to 16 masters connected in daisy chain through connecting I2C\_DONE pin to I2C\_RESET# pin of the next part.

Master EEPROM data starting address for device address:

| I2C address:<br>AD3, AD2, AD1, AD0 | Data starting location |

|------------------------------------|------------------------|

| 0000                               | 00H                    |

| 0001                               | 10H                    |

| 0010                               | 20H                    |

| 0011                               | 30H                    |

| 0100                               | 40H                    |

| 0101                               | 50H                    |

| 0110                               | 60H                    |

| 0111                               | 70H                    |

| 1000                               | 80H                    |

| 1001                               | 90H                    |

| 1010                               | A0H                    |

| 1011                               | ВОН                    |

| 1100                               | С0Н                    |

| 1101                               | D0H                    |

| 1110                               | ЕОН                    |

| 1111                               | F0H                    |

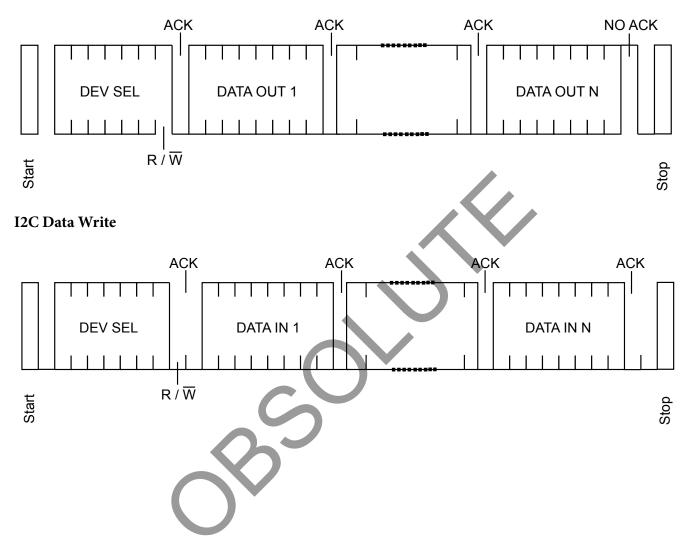

#### Transferring Data

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I2C Data Transfer diagram). It will never hold the clock line SCL LOW to force the master into a wait state.

#### Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, it will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I<sup>2</sup>C Data Transfer diagram. It will generate an acknowledge after each byte has been received.

#### Data Transfer

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, it will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit.

#### I2C Data Transfer

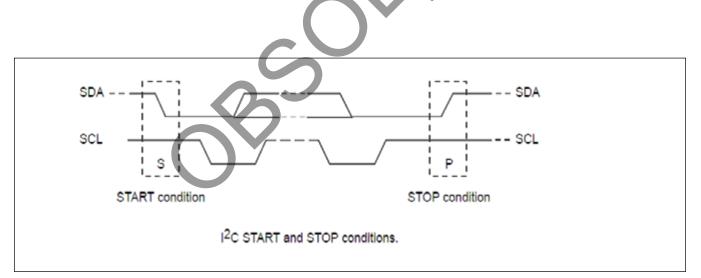

#### **Start & Stop Conditions**

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition, as shown in the figure below

## PI3HDX1204D

HDMI 2.0 6Gbps Linear ReDriver

#### I2C Data Read

### **Absolute Maximum Ratings**

| Storage Temperature65 °C to +150 °C |

|-------------------------------------|

| Supply Voltage to Ground Potential  |

| DC SIG Voltage                      |

| Current Output25 mA to +25 mA       |

| Power Dissipation Continuous1.63W   |

| Operating Temperature0 to +70 °C    |

| ESD, HBM                            |

Note:

$\langle \vee$

Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Electrical characteristics**

#### LVCMOS I/O DC Specifications

| Symbol           | Parameter                           | Conditions |   | Min.                  | Тур. | Max                      | Units |  |  |

|------------------|-------------------------------------|------------|---|-----------------------|------|--------------------------|-------|--|--|

| V <sub>IH</sub>  | DC input logic high                 |            |   | $V_{\rm DD}/2 + 0.7$  |      | V <sub>DD</sub> + 0.3    | V     |  |  |

| V <sub>IL</sub>  | DC input logic low                  |            |   | -0.3                  |      | V <sub>DD</sub> /2 - 0.7 | V     |  |  |

| V <sub>OH</sub>  | At I <sub>OH</sub> = -200µA         |            |   | V <sub>DD</sub> + 0.2 |      |                          | V     |  |  |

| V <sub>OL</sub>  | At $I_{OL} = -200 \mu A$            |            | / |                       |      | 0.2                      | V     |  |  |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger input | 0          |   | 0.8                   |      |                          | V     |  |  |

| Power Co         | ower Consumption                    |            |   |                       |      |                          |       |  |  |

#### **Power Consumption**

| Symbol | Parameter                | Conditions                    | Min. | Тур. | Max. | Units |

|--------|--------------------------|-------------------------------|------|------|------|-------|

| VDD    | Power supply voltage     |                               | 3.0  | 3.3  | 3.6  | V     |

| IDD    | Maximum supply current   | PRSNT#=0                      |      | 225  | 290  | mA    |

| IDDQ   | Quiescent supply current | PRSNT#=1, TMDS Output Disable |      | 2.0  | 4.2  | mA    |

17

Note: "Supply current IDDmax data" on page 18.

#### **Inputs Control Pins DC Specifications**

| Symbol          | Parameter           | Conditions | Min.             | Тур. | Max.                     | Units |

|-----------------|---------------------|------------|------------------|------|--------------------------|-------|

| V <sub>IH</sub> | DC input logic high |            | $V_{DD}/2 + 0.7$ |      | V <sub>DD</sub> + 0.3    | V     |

| V <sub>IL</sub> | DC input logic low  |            | -0.3             |      | V <sub>DD</sub> /2 - 0.7 | V     |

### SDA and SCL I/O Pins for I<sup>2</sup>C-bus

| Symbol          | Parameter           | Conditions     | Min.             | Max.                     | Units |

|-----------------|---------------------|----------------|------------------|--------------------------|-------|

| V <sub>IH</sub> | DC input logic high |                | $V_{DD}/2 + 0.7$ | V <sub>DD</sub> + 0.3    | V     |

| V <sub>IL</sub> | DC input logic low  |                | -0.3             | V <sub>DD</sub> /2 - 0.7 | V     |

| V <sub>OL</sub> | DC output logic low | $I_{OL} = 3mA$ |                  | 0.4                      | V     |

|                 | · · · ·             | ·              | XV               | / ·                      |       |

#### **TMDS Differential Pins**

| Symbol             | Parameter                                 | Conditions                         | Min.                 | Тур. | Max.                     | Units |

|--------------------|-------------------------------------------|------------------------------------|----------------------|------|--------------------------|-------|

| V <sub>OH</sub>    | Single-ended High Level Output<br>Voltage |                                    | V <sub>DD</sub> -10  |      | V <sub>DD</sub> +10      | mV    |

| V <sub>OL</sub>    | Single-ended Low Level Output<br>Voltage  | VDD = 3.3 V,<br>Rout = 50 $\Omega$ | V <sub>DD</sub> -600 |      | V <sub>DD</sub> -<br>400 | mV    |

| V <sub>swing</sub> | Output Voltage Swing                      |                                    | 400                  |      | 600                      | mVppd |

| I <sub>OS</sub>    | Short Circuit Current Limit (Ios)         |                                    |                      |      | 12                       | mA    |

| R <sub>T</sub>     | Input Termination Resistance              | $V_{IN} = 2.9V$                    | 45                   | 50   | 55                       | Ω     |

| I <sub>OZ</sub>    | Leakage Current with Hi-Z I/O             | $V_{DD} = 3.6V$                    |                      |      | 10                       | uA    |

|                    | Characteristics                           | VDD - 5.0V                         |                      |      | 10                       | uA    |

## Switching Characteristics

| Symbol                | Parameter                                       | Conditions                                                         | Min. | Тур. | Max. | Units |

|-----------------------|-------------------------------------------------|--------------------------------------------------------------------|------|------|------|-------|

| T <sub>pd</sub>       | Propagation Delay                               |                                                                    |      |      | 2000 | ps    |

| T <sub>sk(p)</sub>    | Pulse Skew                                      |                                                                    |      | 10   | 50   | ps    |

| T <sub>sk(D)</sub>    | Intra-pair Differential Skew                    |                                                                    |      | 23   | 50   | ps    |

| T <sub>sk(O)</sub>    | Inter-pair Differential Skew                    |                                                                    |      |      | 100  | ps    |

| T <sub>Jit-Clk</sub>  | Peak-to-peak Output Jitter for Clock<br>channel | Pre-/De-EMP =<br>0 dB                                              |      | 15   | 30   | ps    |

| T <sub>Jit-Data</sub> | Peak-to-peak Output Jitter for Data channels    | Data Input = 6<br>Gbps HDMI Pat-<br>tern, Clock input =<br>150 MHz |      | 18   | 50   | ps    |

| t <sub>sx</sub>       | Select to switch Output                         |                                                                    |      |      | 10   | ns    |

18

All trademarks are property of their respective owners.

| Symbol           | Parameter    | Conditions | Min. | Тур. | Max. | Units |

|------------------|--------------|------------|------|------|------|-------|

| t <sub>en</sub>  | Enable Time  |            |      |      | 200  | ns    |

| t <sub>dis</sub> | Disable Time |            |      |      | 10   | ns    |

#### Add-in Jitter Information

|     | Parameters                | Input Jitter (TP1)                                 | Output Jitter (TP2)                       | Add-in Jitter                                                                   | Units    |

|-----|---------------------------|----------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------|----------|

| RJ  | Random Jitter 6Gb/s       | 0.74                                               | 0.775                                     | 0.23                                                                            | RMS ps   |

| DJ  | Deterministic Jitter      | 9.13                                               | 15.70                                     | 6.57                                                                            | ps       |

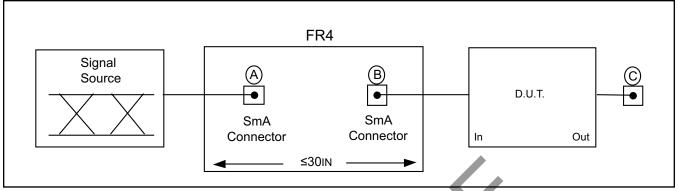

| HDM | MI and Dual-mode DisplayP | ort Test Circuit                                   | 3 1 2                                     | 2                                                                               | 1        |

| D   | Dual-mode DP Source       | VDD         VDD           50         50         50 | Test Phobo<br>+ 3v8<br>50 50 Oscilloscope |                                                                                 | c        |

| с   | EQ[3:0], SW[1:0], FG[1    |                                                    |                                           |                                                                                 | C        |

| В   | HDMI Source               | PI3HDX1204D                                        | Test Probe<br>+3V3<br>50 50 Oscilloscope  |                                                                                 | Ĩ        |

| A   | EQ(3:0), SW(1:0), FG(1    |                                                    | 3                                         | Tile PISHDX1204D TMDS Test<br>Sce Document Number<br>Date: Tupeday, May 05, 201 | Rev<br>A |

AC Test Circuit Referenced in the Electrical Characteristic Table

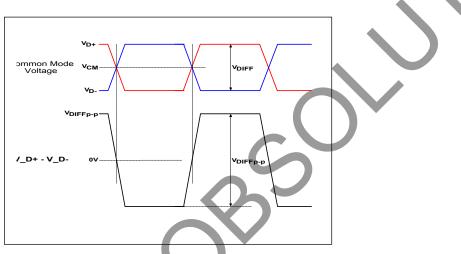

Definition of Peak-to-Peak Differential Voltage

## **PI3HDX1204D** HDMI 2.0 6Gbps Linear ReDriver

## I<sup>2</sup>C BUS SCL/SDA

| Symbol          | Parameter                                                                                            | Conditions                  | Min.                     | Тур. | Max                      | Units |

|-----------------|------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|------|--------------------------|-------|

| V <sub>IH</sub> | DC input logic high                                                                                  |                             | V <sub>DD</sub> /2 + 0.7 |      | V <sub>DD</sub> + 0.3    | v     |

| V <sub>IL</sub> | DC input logic low                                                                                   |                             | -0.3                     |      | V <sub>DD</sub> /2 - 0.7 | V     |

| V <sub>OL</sub> | DC output logic low                                                                                  | $I_{OL} = 3mA$              |                          |      | 0.4                      | V     |

| Ipullup         | Current Through Pull-Up Resistor<br>or Current Source                                                | High Power<br>specification | 3.0                      |      | 3.6                      | mA    |

| VDD             | Nominal Bus Voltage                                                                                  |                             | 3.0                      |      | 3.6                      | V     |

| Ileak-bus       | Input leakage per bus segment                                                                        |                             | -200                     |      | 200                      | uA    |

| Ileak-pin       | Input leakage per device pin                                                                         |                             |                          | -15  |                          | uA    |

| CI              | Capacitance for SDA/SCL                                                                              |                             |                          |      | 10                       | pF    |

| Freq            | Bus Operation Frequency                                                                              |                             |                          |      | 100k                     | Hz    |

| TBUF            | Bus Free Time<br>Between Stop and Start condition                                                    |                             | 1.3                      |      |                          | us    |

| THD:STA         | Hold time after (Repeated) Start condi-<br>tion. After this period, the first clock is<br>generated. | At pull-up, Max             | 0.6                      |      |                          | us    |

| TSU:STA         | Repeated start condition setup time                                                                  |                             | 0.6                      |      |                          | us    |

| TSU:STO         | Stop condition setup time                                                                            |                             | 0.6                      |      |                          | us    |

| THD:DAT         | Data hold time                                                                                       |                             | 0                        |      |                          | ns    |

| TSU:DAT         | Data setup time                                                                                      |                             | 100                      |      |                          | ns    |

| Tlow            | Clock low period                                                                                     |                             | 1.3                      |      |                          | us    |

| Thigh           | Clock high period                                                                                    |                             | 0.6                      |      | 50                       | us    |

| tF              | Clock/Data fall time                                                                                 |                             |                          |      | 300                      | ns    |

| tR              | Clock/Data rise time                                                                                 |                             |                          |      | 300                      | ns    |

| tPOR            | Time in which a device must be opera-<br>tion after power-on reset                                   |                             |                          |      | 500                      | ms    |

Note: (1) Recommended value.

(2) Recommended maximum capacitance load per bus segment is 400pF.

15-0053

(3) Compliant to I2C physical layer specification.

(4) Ensured by Design. Parameter not tested in production.

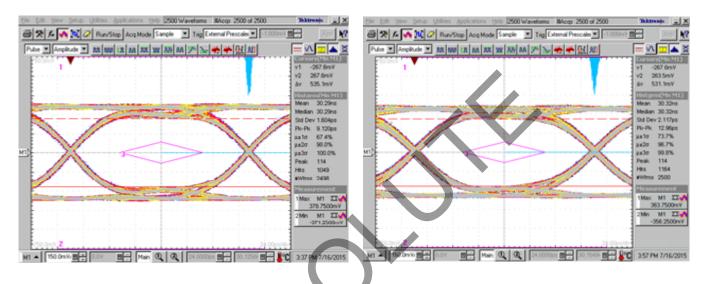

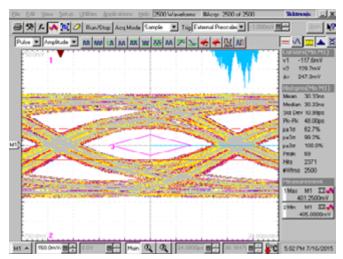

## **Output Eye Diagram with different Trace lengths & Input EQ settings**

Using PRBS 2^23-1 pattern, Input Swing=800mVd, Output Swing= 1000mVdiff,

• FG = 10 (+0.5dB), EQ=4.7dB, Trace length =18-in

Using PRBS 2^23-1 pattern, Input Swing=800mVd, Output Swing= 1000mVdiff,

• FG =11 (+0.5dB), EQ=6.2dB, Trace length = 24-in

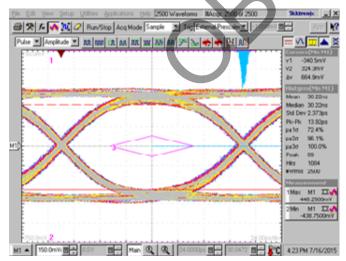

Using PRBS 2^23-1 pattern, Input Swing=800mVdiff, Output Swing= 1000mVdiff,

• FG = 11 (+2.5dB), EQ=8.9dB, Trace length = 30-in

Using PRBS 2^23-1 pattern, Input Swing=800mVd, Output Swing= 1000mVdiff,

• FG = 11 (+2.5dB), EQ=8.9dB Trace length = 48-in

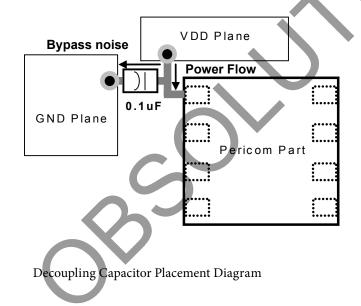

## **Layout and Decoupling Capacitor Placement Guidelines**

- Each 0.1µF decoupling capacitor should be placed as close as possible to each VDD pin.

- VDD and GND planes should be used to provide a low impedance path for power and ground.

- Via holes should be placed to connect to VDD and GND planes directly.

- Trace should be as wide as possible

- Trace should be as short as possible.

- The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- 10µF capacitor should also be placed closed to our part and should be placed in the middle location of 0.1µF capacitors.

- Avoid the large current circuit placed close to our part; especially when it is shared the same VDD and GND planes. Since large current flowing on our VDD or GND planes will generate a potential variation on the VDD or GND of our part.

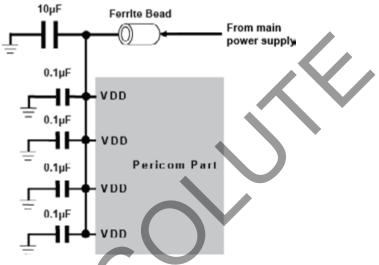

#### **Power Supply Decoupling Circuit**

It is recommended to put 0.1  $\mu$ F decoupling capacitors on each VDD pins of our part, there are four 0.1  $\mu$ F decoupling capacitors are put in Figure 1 with an assumption of only four VDD pins on our part, if there is more or less VDD pins on our Pericom parts, the number of 0.1  $\mu$ F decoupling capacitors should be adjusted according to the actual number of VDD pins. On top of 0.1  $\mu$ F decoupling capacitors on each VDD pins, it is recommended to put a 10  $\mu$ F decoupling capacitor near our part's VDD, it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Recommended Power Supply Decoupling Capacitor Diagram

#### **Requirements on the Decoupling Capacitors**

There is no special requirement on twhe material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

25

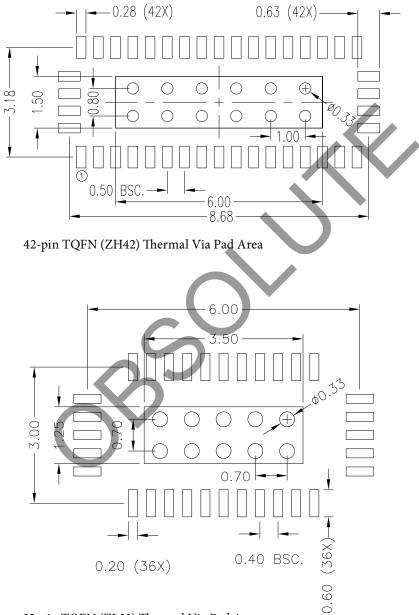

#### GND via on the thermal pad area Recommendation

Several GND via are "must" required on thermal area. The via size is 12/24 mil. Below are the recommendations

32-pin TQFN (ZL32) Thermal Via Pad Area

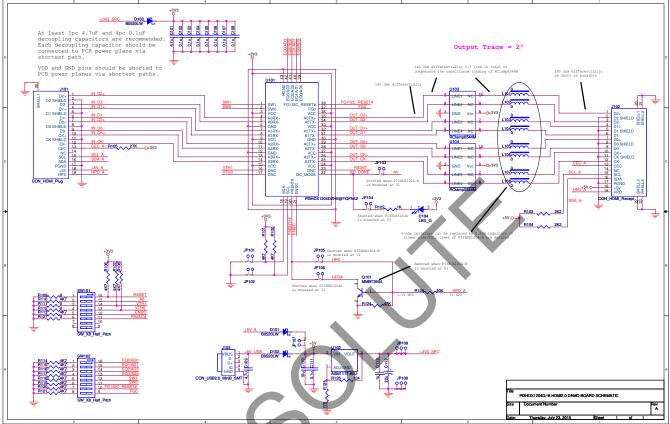

#### **Reference Schematic**

Note: Keep VTH0, VTH1 and RXDET pins as DNC(Do Not Connect) for PI3HDX1204D.

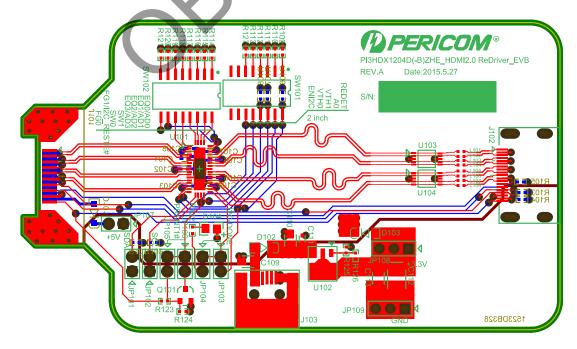

#### **Evaluation Board PCB Layout**

### HDMI 2.0 Compliance Test Report

## **HDMI Test Report**

Overall Result: PASS

| Device ID<br>Fixture Type<br>Probe Connection<br>Probe Head Type | Device Description Transmitter Other 4 Probes N5444A 1 Data Lane 2.0                                                                                                                                                        |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixture Type<br>Probe Connection<br>Probe Head Type              | Other<br>4 Probes<br>N5444A<br>1 Data Lane                                                                                                                                                                                  |

| Probe Connection<br>Probe Head Type                              | 4 Probes<br>N5444A<br>1 Data Lane                                                                                                                                                                                           |

| Probe Head Type                                                  | N5444A<br>1 Data Lane                                                                                                                                                                                                       |

|                                                                  | 1 Data Lane                                                                                                                                                                                                                 |

|                                                                  |                                                                                                                                                                                                                             |

| Lane Connection                                                  | 2.0                                                                                                                                                                                                                         |

| HDMI Specification                                               |                                                                                                                                                                                                                             |

| HDMI Test Type                                                   | TMDS Physical Layer Tests                                                                                                                                                                                                   |

|                                                                  | Test Session Details                                                                                                                                                                                                        |

| Infiniium SW Version                                             | 05.20.0013                                                                                                                                                                                                                  |

| Infiniium Model Number                                           | DSOX92504A                                                                                                                                                                                                                  |

| Infiniium Serial Number                                          | MY54410104                                                                                                                                                                                                                  |

| Application SW Version                                           | 2.11                                                                                                                                                                                                                        |

| Debug Mode Used                                                  | No                                                                                                                                                                                                                          |

| Probe (Channel 1)                                                | Model: N2801A<br>Serial: US54094067<br>Head: N5444A<br>Atten: Calibrated (18 FEB 2015 11:16:48), Using Cal Atten (5.7831E+000)<br>Skew: Calibrated (18 FEB 2015 11:16:56), Using Cal Skew                                   |

| Probe (Channel 2)                                                | Model: N2801A<br>Serial: US54094054<br>Head: N5444A<br>Atten: Calibrated (18 FEB 2015 11:19:29), Using Cal Atten (5.5882E+000)<br>Skew: Calibrated (18 FEB 2015 11:13:57), Using Cal Skew                                   |

| Probe (Channel 3)                                                | Model: N2801A<br>Serial: US54094059<br>Head: N5444A<br>Atten: Calibrated (18 FEB 2015 11:15:19), Using Cal Atten (5.7320E+000)<br>Skew: Calibrated (18 FEB 2015 11:15:29), Using Cal Skew                                   |

| Probe (Channel 4)                                                | Model: N2801A<br>Serial: US54094057<br>Head: N5444A<br>Atten: Calibrated (18 FEB 2015 11:11:30), Using Cal Atten (5.5123E+000)<br>Skew: Calibrated (18 FEB 2015 11:12:12), Using Cal Skew<br>2015-05-27 14:58:02 UTC +08:00 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | #<br>Trials | Test Name                                                     | Actual Value         | Margin     | Pass Limits                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|---------------------------------------------------------------|----------------------|------------|---------------------------------------------------|

| <b>√</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 | 1           | HF1-2: Clock Rise Time                                        | 162.046 ps           | 116.1<br>% | VALUE >= 75.000 ps                                |

| <ul> <li>Image: A set of the set of the</li></ul>  | 0 | 1           | HF1-2: Clock Fall Time                                        | 152.277 ps           | 103.0<br>% | VALUE >= 75.000 ps                                |

| <ul> <li>Image: A second s</li></ul> | 0 | 1           | HF1-6: Clock Duty Cycle(Minimum)                              | 49.640               | 24.1 %     | >=40%                                             |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 | 1           | HF1-6: Clock Duty Cycle(Maximum)                              | 50.190               | 16.4 %     | <=60%                                             |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 | 1           | HF1-6: Clock Rate                                             | 148.562300000<br>MHz | 2.2 %      | 85.000000000 MHz <= VALUE <=<br>150.000000000 MHz |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 | 1           | HF1-5: D0 Maximum Differential Voltage                        | 648 m                | 16.9 %     | VALUE <= 780 m                                    |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 | 1           | HF1-5: D0 Minimum Differential Voltage                        | -659 m               | 15.5 %     | VALUE >= -780 m                                   |

| >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 | 1           | HF1-2: D0 Rise Time                                           | 145.660 ps           | 242.7<br>% | VALUE >= 42.500 ps                                |

| <ul> <li>Image: A set of the set of the</li></ul>  | 0 | 1           | HF1-2: D0 Fall Time                                           | 143.400 ps           | 237.4<br>% | VALUE >= 42.500 ps                                |

| <ul> <li>Image: A second s</li></ul> | 0 | 1           | HF1-8: D0 Mask Test (TP2_EQ with Worst<br>Case Positive Skew) | 0.000                | 50.0 %     | No Mask Failures                                  |

| <ul> <li>Image: A second s</li></ul> | 0 | 1           | HF1-8: D0 Mask Test (TP2 EQ with Worst<br>Case Negative Skew) | 0.000                | 50.0 %     | No Mask Failures                                  |