#### 2-Port USB3.1 Gen-2 10Gbps ReDriver

#### **Features**

- → 5 & 10Gbps serial link with linear equalizer

- → USB3.1 and USB3.0 Compatible

- → Full Compliancy to USB3.1 Super Speed Standard

- → Four 10Gbps differential signal pairs

- → Pin Adjustable Receiver Equalization

- → Pin Adjustable Flat Gain

- → 100Ω Differential CML I/O's

- ➔ Automatic Receiver Detect

- → Auto "Slumber" mode for adaptive power management

- → Single Supply Voltage: 3.3V

- → Packaging:

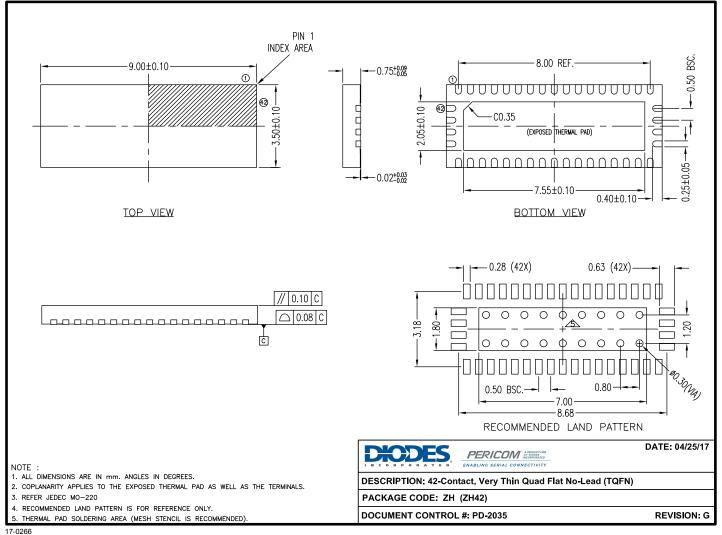

- ◆ 42-pin, TQFN 3.5 x 9mm (ZH42)

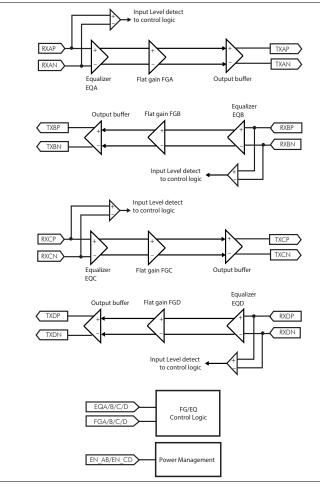

#### **Block Diagram**

# Description

The PI3EQX1004B1 is a low power, high performance 10.0 Gbps 2-Port USB 3.1 linear ReDriver<sup>™</sup> designed specifically for the USB 3.1 protocol.

The device provides programmable equalization, and flat gain to optimize performance over a variety of physical mediums by reducing Inter-Symbol Interference. PI3EQX1004B1 supports two 100Ω Differential CML data I/O's between the Protocol ASIC to a switch fabric, over cable, or to extend the signals across other distant data pathways on the user's platform.

The integrated equalization circuitry provides flexibility with signal integrity of the signal before the ReDriver. Each channel operates fully independently. The channels' input signal level determines whether the output is active.

The PI3EQX1004B1 also includes an automatic receiver detect function. The receiver detection loop will be active again if the corresponding channel's signal detector is idle for longer than 7.3ms. The channel will then move to Unplug Mode if load not detected, or it will return to Low Power Mode (Slumber Mode) due to inactivity.

#### Figure1

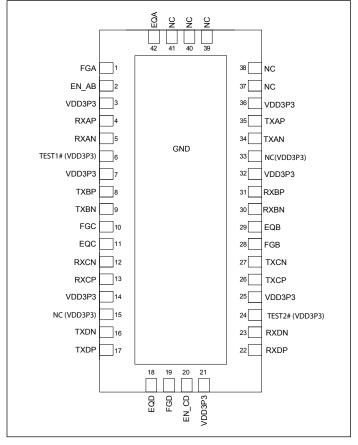

#### Pin Diagram (42-pin, TQFN 3.5x9mm) ZH42

| Pin #                       | Pin Name   | Туре   | Description                                                                           |  |  |  |

|-----------------------------|------------|--------|---------------------------------------------------------------------------------------|--|--|--|

| 3, 7, 14, 21, 25,<br>32, 36 | VDD        | Power  | 3.3V power supply, +/-0.3V                                                            |  |  |  |

| 1, 28                       | FGA, FGB   | Innut  | The DC flat gain selection. 4-level input pins. With internal 100k $\Omega$ pull-up   |  |  |  |

| 10, 19                      | FGC, FGD   | Input  | resistor and 200k $\Omega$ pull-down resistor.                                        |  |  |  |

| 42, 29                      | EQA, EQB   | Input  | The EQ selection. 4-level input pins. With internal $100k\Omega$ pull-up resistor and |  |  |  |

| 11, 18                      | EQC, EQD   | Input  | 200kΩ pull-down resistor.                                                             |  |  |  |

| 4, 5                        | RXAP, RXAN |        |                                                                                       |  |  |  |

| 31, 30                      | RXBP, RXBN | Innut  | CML input terminals. With selectable input termination between 50 $\Omega$ to VDD,    |  |  |  |

| 13, 12                      | RXCP, RXCN | Input  | 67kΩ to VbiasRx or $67$ kΩ to GND.                                                    |  |  |  |

| 22, 23                      | RXDP, RXDN |        |                                                                                       |  |  |  |

| 35, 34                      | TXAP, TXAN |        |                                                                                       |  |  |  |

| 8, 9                        | TXBP, TXBN | Output | CML output terminals. With selectable output termination between 50 $\Omega$ to       |  |  |  |

| 26, 27                      | TXCP, TXCN | Output | VDD, $6k\Omega$ to VDD, $6k\Omega$ to VbiasTx or Hi-Z.                                |  |  |  |

| 17, 16                      | TXDP, TXDN |        |                                                                                       |  |  |  |

| 2                           | EN_AB      |        | Channel Enable. With internal 300k $\Omega$ pull-up resistor.                         |  |  |  |

| 20                          | EN_CD      | Input  | "High" – Channel is in normal operation.                                              |  |  |  |

| 20                          | EN_CD      |        | "Low" – Channel is in power down mode.                                                |  |  |  |

| Center Pad                  | GND        | GND    | Supply Ground                                                                         |  |  |  |

| 6                           | Test1#     | Innut  | Connect to VDD is recommended                                                         |  |  |  |

| 24                          | Test2#     | Input  | Connect to VDD is recommended                                                         |  |  |  |

| 15, 33                      | NC         | NC     | NC pin connect to VDD is recommended                                                  |  |  |  |

| 37, 38, 39, 40, 41          | NC         | NC     | NC                                                                                    |  |  |  |

#### Pin Description (42-pin, TQFN 3.5x9mm)

## **Power Management**

Notebooks, netbooks, and other power sensitive consumer devices require judicious use of power in order to maximize battery life. In order to minimize the power consumption of our devices, Diodes has added an additional adaptive power management feature. When a signal detector is idle for longer than 1.3ms, the corresponding channel will move to low power mode ONLY. (It means both channels will move to low power mode individually).

In the low power mode, the signal detector will still be monitoring the input channel. If a channel is in low power mode and the input signal is detected, the corresponding channel will wake-up immediately. If a channel is in low power mode and the signal detector is idle longer than 6ms, the receiver detection loop will be active again. If load is not detected, then the Channel will move to Device Unplug Mode and monitor the load continuously. If load is detected, it will return to Low Power Mode and receiver detection will be active again per 6ms.

## **Operating Modes**

| Mode              | R <sub>IN</sub>                  | R <sub>OUT</sub>  |

|-------------------|----------------------------------|-------------------|

| PD                | $67 \mathrm{k}\Omega$ to GND     | HIZ               |

| Unplug Mode       | $67 \mathrm{k}\Omega$ to VbiasRx | 6kΩ to VbiasTx    |

| Deep Slumber Mode | $50\Omega$ to Vdd                | 6kΩ to VbiasTx    |

| Slumber Mode      | $50\Omega$ to Vdd                | $6k\Omega$ to Vdd |

| Active Mode       | $50\Omega$ to Vdd                | $50\Omega$ to Vdd |

# **Equalization Setting:**

EQA/B/C/D are the selection pins for the equalization selection

|                          | Equalizer s | setting (dB) |

|--------------------------|-------------|--------------|

| EQA/B/C/D                | @2.5GHz     | @5GHz        |

| 0 (Tie $0\Omega$ to GND) | 6.7         | 12.4         |

| R (Tie Rext to GND)      | 3.5         | 8.0          |

| F (Leave Open)           | 5.3         | 10.6         |

| 1 (Tie $0\Omega$ to VDD) | 8.4         | 14.6         |

# **Flat Gain Setting:**

FGA/B/C/D are the selection pins for the DC gain

|                          | Flat Gain Settings |

|--------------------------|--------------------|

| FGA/B/C/D                | dB                 |

| 0 (Tie $0\Omega$ to GND) | -1.6               |

| R (Tie Rext to GND)      | -0.5               |

| F (Leave Open)           | 1.0                |

| 1 (Tie $0\Omega$ to VDD) | 2.7                |

# **Channel Enable Setting:**

EN\_AB/EN\_CD are the channel enable pins for channels A&B and C&D respectively

|    | Channel Enable Setting |

|----|------------------------|

| EN | Setting                |

| 0  | Disabled               |

| 1  | Enabled (Default)      |

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.) Note:

| , , , , ,                          | 0 1 1                      |

|------------------------------------|----------------------------|

| Storage Temperature                | 65°C to +150°C             |

| Supply Voltage to Ground Potential | -0.5V to +3.8V             |

| DC SIG Voltage                     | $-0.5V$ to $V_{DD} + 0.5V$ |

| Output Current                     | –25mA to +25mA             |

| ESD, Human Body Model              | -2kV to +2kV               |

| Power Dissipation Continuous       |                            |

| Max Junction Temperature           |                            |

|                                    |                            |

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### Control pin Specifications (VDD = $3.3 \pm 0.3$ V TA = 0 to 70°C)

| Symbol          | Parameter                                       | Min.     | Тур.     | Max.     | Units |

|-----------------|-------------------------------------------------|----------|----------|----------|-------|

| 2-level contro  | ol pins                                         | ·        |          |          | ·     |

| V <sub>IH</sub> | DC input logic High                             | VDD*0.65 |          |          | V     |

| V <sub>IL</sub> | DC input logic Low                              |          |          | VDD*0.35 | V     |

| I <sub>IH</sub> | Input High current                              |          |          | 25       | uA    |

| I <sub>IL</sub> | Input Low current                               | -25      |          |          | uA    |

| 4-level contro  | ol pins                                         |          |          |          |       |

| V <sub>IH</sub> | DC input logic "High"                           | 0.92*VDD | VDD      |          | V     |

| V <sub>IF</sub> | DC input logic "Float"                          | 0.59*VDD | 0.67*VDD | 0.75*VDD | V     |

| V <sub>IR</sub> | DC input logic "With Rext to GND"               | 0.25*VDD | 0.33*VDD | 0.41*VDD | v     |

| V <sub>IL</sub> | DC input logic "Low"                            |          | GND      | 0.08*VDD | V     |

| I <sub>IH</sub> | Input High current                              |          |          | 50       | uA    |

| I <sub>IL</sub> | Input Low current                               | -50      |          |          | uA    |

| Rext            | External resistor connects to GND ( $\pm 5\%$ ) | 64.6     | 68       | 71.4     | kΩ    |

#### AC/DC Electrical Characteristics (VDD = $3.3 \pm 0.3$ V TA = 0 to 70°C)

| Power and Lat            | Power and Latency                          |                                                                           |      |      |      |       |

|--------------------------|--------------------------------------------|---------------------------------------------------------------------------|------|------|------|-------|

| Symbol                   | Parameter                                  | Conditions                                                                | Min. | Тур. | Max. | Units |

| V <sub>dd-3.3</sub>      | Supply voltage                             |                                                                           | 3.0  | 3.3  | 3.6  | V     |

| I <sub>active</sub>      | Active mode current consumption            | EN_AB & EN_CD = 1, 10Gbps, compli-<br>ance test pattern                   |      | 260  | 334  | mA    |

| I <sub>slumber</sub>     | Slumber mode current consumption           | EN_AB & EN_CD = 1, no input signal longer than $T_{slumber}$              |      | 32   | 38   |       |

| I <sub>DeepSlumber</sub> | Deep slumber mode current con-<br>sumption | EN_AB & EN_CD = 1 no input signal<br>longer than T <sub>DeepSlumber</sub> |      | 0.8  | 1.2  | mA    |

| I <sub>unplug</sub>      | Unplug mode current consumption            | EN_AB & EN_CD = 1, no output load is detected                             |      | 0.6  | 0.9  |       |

| I <sub>pd</sub>          | Power down mode current consump-<br>tion   | $EN_AB \& EN_CD = 0$                                                      |      | 20   | 100  | μA    |

| t <sub>pd</sub>          | Latency                                    | From input to output                                                      |      |      | 2    | ns    |

### **AC/DC Electrical Characteristics Cont.**

| Symbol                                         | Parameter                                                                                                                                 | Conditions                                                                                                        | Min.       | Тур. | Max.  | Units   |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|------|-------|---------|

| CML Receiver In                                | put (100 $\Omega$ differential)                                                                                                           |                                                                                                                   |            |      |       |         |

| Receiver Electrica                             | l Specification                                                                                                                           |                                                                                                                   |            |      |       |         |

| C <sub>rxparasitic</sub>                       | The parasitic capacitor for RX                                                                                                            |                                                                                                                   |            |      | 1.0   | pF      |

| R <sub>RX-DIFF-DC</sub>                        | DC Differential Input Impedance                                                                                                           |                                                                                                                   | 72         |      | 120   |         |

| R <sub>RX-SINGLE_DC</sub>                      | DC single ended input impedance                                                                                                           | DC impedance limits are need to guar-<br>antee RxDet. Measured with respect to<br>GND over a voltage of 500mV max | 18         |      | 30    | Ω       |

| Z <sub>RX-HIZ-DC-PD</sub>                      | DC input CM input impedance for<br>V>0 during reset or power down                                                                         | (Vcm=0 to 500mV)                                                                                                  | 25         |      |       | kΩ      |

| Cac_coupling                                   | AC coupling capacitance                                                                                                                   |                                                                                                                   | 75         |      | 265   | nF      |

| V <sub>RX-CM-AC-P</sub>                        | Common mode peak voltage                                                                                                                  | AC up to 5GHz                                                                                                     |            |      | 150   | mVpeak  |

| V <sub>RX-CM-DC-Ac-</sub><br>tive-Idle-Delta-P | Common mode peak voltage<br> Avguo( V <sub>TX-D+</sub> + V <sub>TX-D-</sub>  )/2-Avgu1( V <sub>TX-D+</sub> +<br>V <sub>TX-D-</sub>  )/2   | Between U0 and U1. AC up to 5GHz                                                                                  |            |      | 200   | mVpeak  |

| Transmitter Elect                              | rical Specification                                                                                                                       |                                                                                                                   |            |      |       |         |

| V <sub>TX-DIFF-PP</sub>                        | Ouput differential p-p voltage swing                                                                                                      | Differential Swing  V <sub>TX-D+</sub> -V <sub>TX-D-</sub>                                                        |            |      | 1.2   | Vppd    |

| R <sub>TX-DIFF-DC</sub>                        | DC Differential TX Impedance                                                                                                              |                                                                                                                   | 72         |      | 120   | Ω       |

| V <sub>TX-RCV-DET</sub>                        | The amount of voltage change al-<br>lowed during RxDet                                                                                    |                                                                                                                   |            |      | 600   | mV      |

| Cac_coupling                                   | AC coupling capacitance                                                                                                                   |                                                                                                                   | 75         |      | 265   | nF      |

| T <sub>TX-EYE</sub> (10Gbps)                   | Transmitter eye, Include all jittter                                                                                                      | At the silicon pad. 10Gbps                                                                                        | 0.646      |      |       | UI      |

| T <sub>TX-EYE</sub> (5Gbps)                    | Transmitter eye, Include all jittter                                                                                                      | At the silicon pad. 5Gbps                                                                                         | 0.625      |      |       | UI      |

| T <sub>TX-DJ-</sub><br>DD(10Gbps)              | Transmitter deterministic jittter                                                                                                         | At the silicon pad. 10Gbps                                                                                        |            |      | 0.17  | UI      |

| T <sub>TX-DJ-DD(5Gbps)</sub>                   | Transmitter deterministic jittter                                                                                                         | At the silicon pad. 5Gbps                                                                                         |            |      | 0.205 | UI      |

| C <sub>txparasitic</sub>                       | The parasitic capacitor for TX                                                                                                            |                                                                                                                   |            |      | 1.1   | pF      |

| R <sub>TX-DC-CM</sub>                          | Common mode DC output Imped-<br>ance                                                                                                      |                                                                                                                   | 18         |      | 30    | Ω       |

| V <sub>TX-DC-CM</sub>                          | The instantaneous allowed DC com-<br>mon mode voltage at the connector<br>side of the AC coupling capacitors                              | V <sub>TX-D+</sub> +V <sub>TX-D-</sub>  /2                                                                        | 0          |      | 2.2   | V       |

| V <sub>TX-C</sub>                              | Common-Mode Voltage                                                                                                                       | V <sub>TX-D+</sub> +V <sub>TX-D-</sub>  /2                                                                        | VDD-<br>2V |      | VDD   | V       |

| V <sub>TX-CM-AC-PP-</sub><br>Active            | Active mode TX AC common mode voltage                                                                                                     | $V_{TX\text{-}D\text{+}}\text{+}V_{TX\text{-}D\text{-}}$ for both time and amplitude                              |            |      | 100   | mVpp    |

| V <sub>TX-CM-DC-</sub><br>Active_Idle-Delta    | Common mode delta voltage<br> Avguo( V <sub>TEX-D+</sub> + V <sub>TX-D-</sub> ])/2-Avgu1( V <sub>TX-D+</sub><br>+ V <sub>TX-D-</sub> ])/2 | Between U0 to U1                                                                                                  |            |      | 200   | mV-peak |

## **AC/DC Electrical Characteristics Cont.**

| Symbol                                                       | Parameter                                                                                           | Conditions                                                                                                                                 | Min. | Тур.                        | Max. | Units             |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------|------|-------------------|

| VTX-Idle-Diff-AC-<br>pp                                      | Idle mode AC common mode delta<br>voltage V <sub>TX-D+</sub> -V <sub>TX-D-</sub>                    | Between Tx+ and Tx- in idle mode. Use<br>the HPF to remove DC components. =1/<br>LPF. No AC and DC signals are applied<br>to Rx terminals. |      |                             | 10   | mVppd             |

| V <sub>TX-Idle-Diff-DC</sub>                                 | Idle mode DC common mode delta<br>voltage V <sub>TX-D+</sub> -V <sub>TX-D-</sub>                    | Between Tx+ and Tx- in idle mode. Use<br>the LPF to remove DC components. =1/<br>HPF. No AC and DC signals are applied<br>to Rx terminals. |      |                             | 10   | mV                |

| Channel Perform                                              | ance                                                                                                |                                                                                                                                            |      |                             |      |                   |

| Gp                                                           | Peaking gain (Compensation at<br>5GHz, relative to 100MHz, 100mV <sub>p-p</sub><br>sine wave input) | EQx=0<br>EQx=R<br>EQx=F<br>EQx=1                                                                                                           |      | 12.4<br>8.0<br>10.6<br>14.6 |      | dB                |

|                                                              |                                                                                                     | Variation around typical                                                                                                                   | -3   |                             | +3   | dB                |

| G <sub>F</sub>                                               | Flat gain (100MHz, EQx=F)                                                                           | FQx=0<br>FQx=R<br>FQx=F<br>FQx=1<br>Variation around typical                                                                               | -3   | -1.6<br>-0.5<br>1.0<br>2.7  | +3   | dB<br>dB          |

| V <sub>SW_100M</sub>                                         | -1dB compression point output swing<br>(at 100MHz)                                                  |                                                                                                                                            |      | 1000                        |      | mVppd             |

| V <sub>SW_5G</sub>                                           | -1dB compression point output swing<br>(at 5GHz)                                                    |                                                                                                                                            |      | 850                         |      | mVppd             |

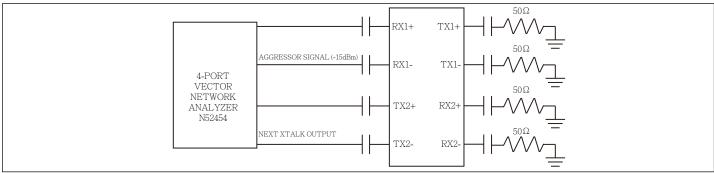

| DDNEXT                                                       | Differential near-end crosstalk <sup>1</sup>                                                        | 100MHz to 5GHz, Figure2                                                                                                                    |      | -40                         |      | dB                |

| V                                                            | Input referred ratio                                                                                | 100MHz to 5GHz, FGx=1, EQx=R,<br>Figure 3                                                                                                  |      | 0.6                         |      |                   |

| Vnoise-input                                                 | Input-referred noise                                                                                | 100MHz to 5GHz, FGx=1, EQx=1,<br>Figure 3                                                                                                  |      | 0.5                         |      | mV <sub>RMS</sub> |

| \$7                                                          | Output of the interaction                                                                           | 100MHz to 5GHz, FGx=1, EQx=R,<br>Figure 3                                                                                                  |      | 0.8                         |      |                   |

| V <sub>noise-output</sub> Output-referred noise <sup>2</sup> |                                                                                                     | 100MHz to 5GHz, FGx=1, EQx=1,<br>Figure 3                                                                                                  |      | 1                           |      | mV <sub>RMS</sub> |

| Signal and Frequ                                             | ency Detectors                                                                                      | ·                                                                                                                                          |      |                             |      |                   |

| V <sub>th_upm</sub>                                          | Unplug mode detector threshold                                                                      | Threshold of LFPS when the input<br>impedance of the redriver is 67kohm<br>to VbiasRx only. Used in the unplug<br>mode.                    | 200  |                             | 800  | mVppd             |

| V <sub>th_dsm</sub>                                          | Deep slumber mode detector threshold                                                                | LFPS signal threshold in Deep slumber mode                                                                                                 | 100  |                             | 600  | mVppd             |

# AC/DC Electrical Characteristics Cont.

| Symbol             | Parameter                      | Conditions                                    | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------|-----------------------------------------------|------|------|------|-------|

| V <sub>th_am</sub> | Active mode detector threshold | Signal threshold in Active and slumber mode   | 45   |      | 175  | mVppd |

| F <sub>th</sub>    | LFPS frequency detector        | Detect the frequency of the input CLK pattern | 100  |      | 400  | MHz   |

Note:

1. Measured using a vector-network analyzer (VNA) with -15dBm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with  $50\Omega$ .

2. Guaranteed by design and characterization.

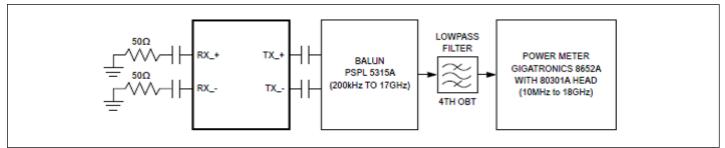

Figure2. Channel-isolation test configuration

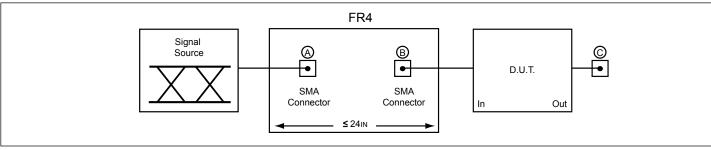

#### Figure3. Noise test configuration

Figure4. Test Condition Referenced in the Electrical Characteristic Table

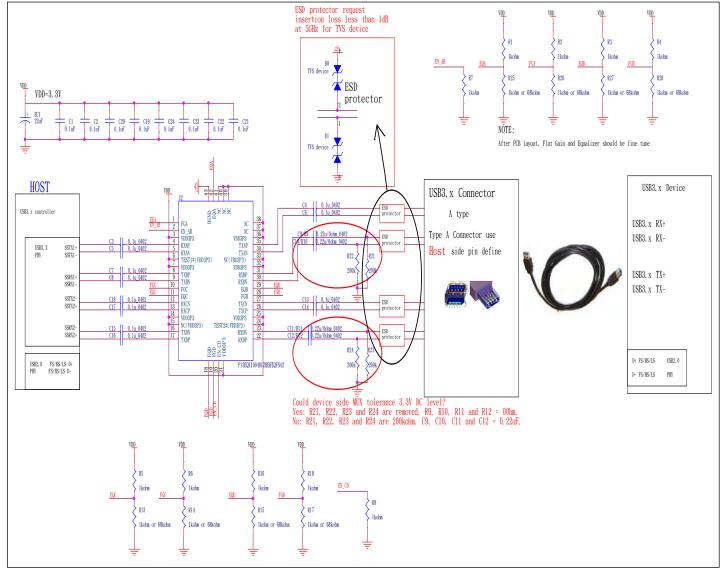

# **Application Schematics**

# **Part Marking**

ZH Package

YY: Year WW: Workweek 1st X: Assembly Code 2nd X: Fab Code

# Packaging Mechanical: 42-TQFN (ZH)

For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Ordering Number Pa | Package Code | Package Description                            |

|--------------------|--------------|------------------------------------------------|

| PI3EQX1004B1ZHEX   | ZH           | 42-contact, Very Thin Quad Flat No-Lead (TQFN) |

#### Notes:

1. EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. All applicable RoHS exemptions applied.

2. See http://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

3. E = Pb-free and Green

4. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com