# Product Document

### **Datasheet**

DS000734

# **CMV2000**

**Global Shutter CMOS Image Sensor for Machine Vision**

v5-00 • 2023-Jan-23

# **Content Guide**

| 1                                      | General Description 3                               |

|----------------------------------------|-----------------------------------------------------|

| 1.1<br>1.2<br>1.3                      | Key Benefits & Features3Applications4Block Diagram4 |

| 2                                      | Ordering Information5                               |

| 3                                      | Absolute Maximum Ratings 7                          |

| 4                                      | Electrical Characteristics 8                        |

| 5                                      | Specification Overview 10                           |

| 5.1                                    | Spectral Characteristics11                          |

| 6                                      | Functional Description15                            |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Sensor Architecture                                 |

| 7                                      | Register Description 61                             |

| 7.1<br>7.2                             | Register Overview61 Recommended Register Settings66 |

| 8                                      | Application Information 69                          |

| 8.1<br>8.2<br>8.3            | Color Filter                        | 69       |

|------------------------------|-------------------------------------|----------|

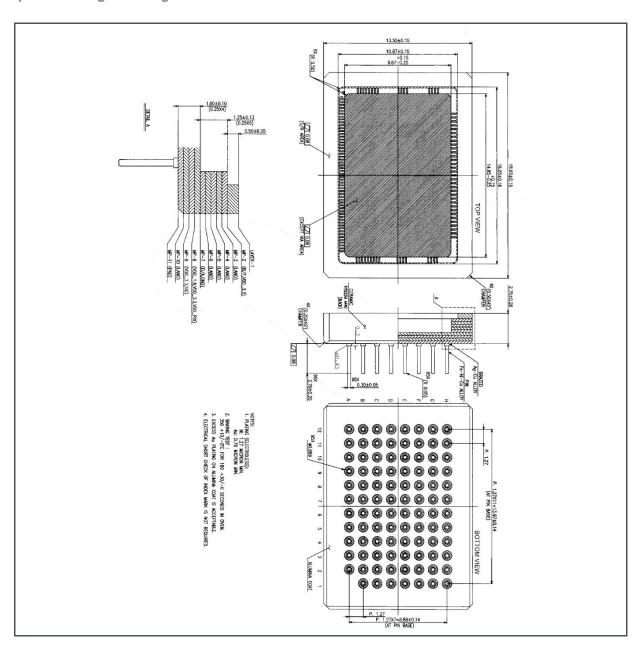

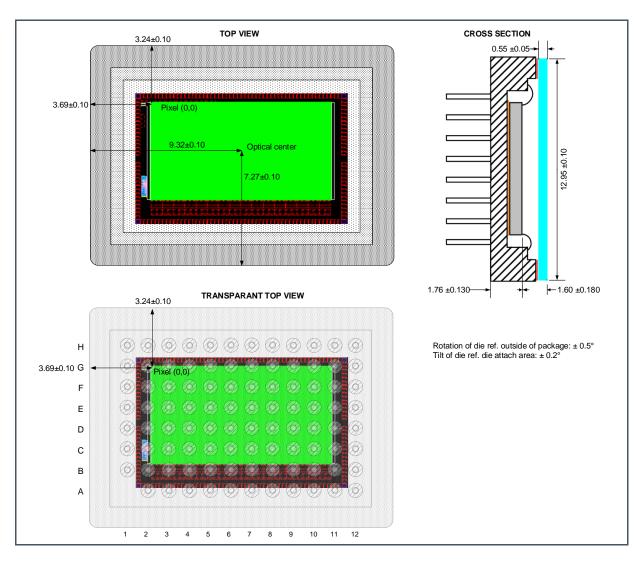

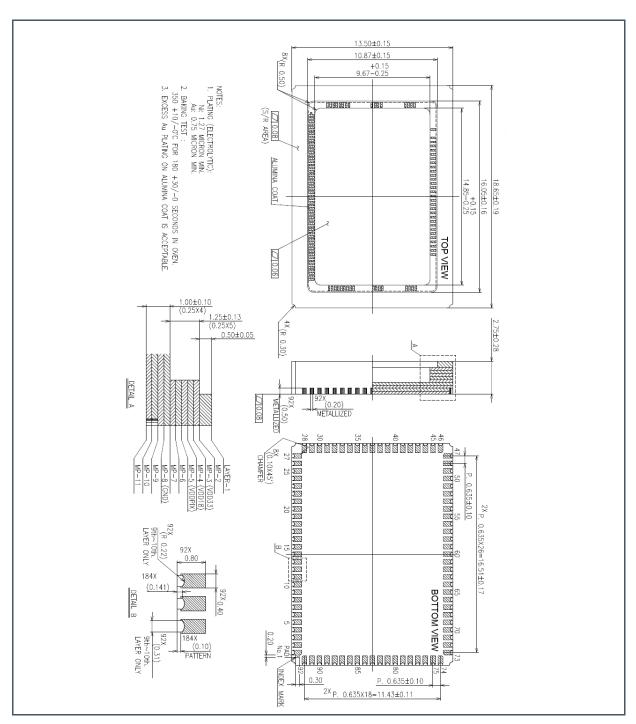

| 9                            | Package Drawings & Markings.        | 76       |

| 9.1<br>9.2                   | 95 Pins µPGA and LGA<br>92 Pins LCC | 76<br>78 |

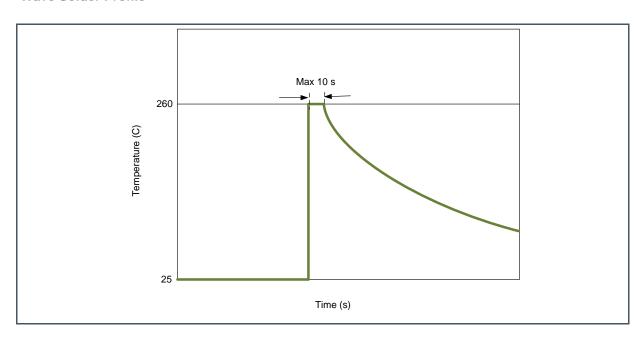

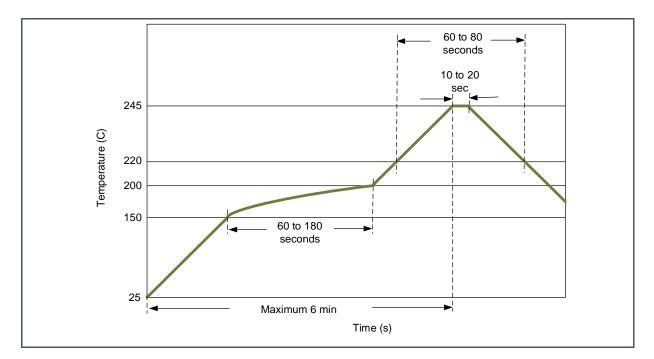

| 10                           | Soldering & Storage Informatio      | n 79     |

| 10.1<br>10.2<br>10.3<br>10.4 | Manual Soldering                    | 79<br>80 |

| 11                           | Revision Information                | 81       |

| 12                           | Legal Information                   | 82       |

# 1 General Description

The CMV2000 is a high sensitivity, pipelined global shutter CMOS image sensor with 2048 by 1088 pixels (2/3 optical inch) developed for machine vision applications. Pipeline global shutter pixels allow exposure during read-out, while performing CDS operation. The image sensor has sixteen 10 or 12-bit digital LVDS outputs (serial). The image sensor also integrates a programmable gain amplifier and offset regulation. Each channel runs at 480 Mbps maximum which results in 340 fps frame rate at full resolution. Higher frame rates can be achieved in row-windowing mode or row-subsampling mode. These modes are all programmable using the SPI interface. All internal exposure and read-out timings are generated by a programmable on-board sequencer. External triggering and exposure programming is also possible. Extended optical dynamic range can be achieved by multiple integrated high dynamic range modes.

### 1.1 Key Benefits & Features

The benefits and features of CMV2000, Global Shutter CMOS Image Sensor for Machine Vision are listed below:

Figure 1: Added Value of Using CMV2000

| Benefits                                                                    | Features                                                                        |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Freeze moving objects                                                       | Global shutter with excellent parasitic light sensitivity of 1/50000            |

| Track moving objects accurately and high inspection rate                    | High speed 340 fps                                                              |

| Easy HW design                                                              | Pin compatible to CMV4000                                                       |

| Choose between maximum frame rate (10-bit) or better image quality (12-bit) | Selectable ADC Resolution                                                       |

| See bright and dark objects at the same time                                | High dynamic range mode with dual exposure and piecewise linear response option |

### 1.2 Applications

- Machine Vision

- 3D Imaging

- Motion Capture

- Bar and 2D Code Scanning

- Intelligent traffic systems

- Video and Broadcast

- Biometrics

### 1.3 Block Diagram

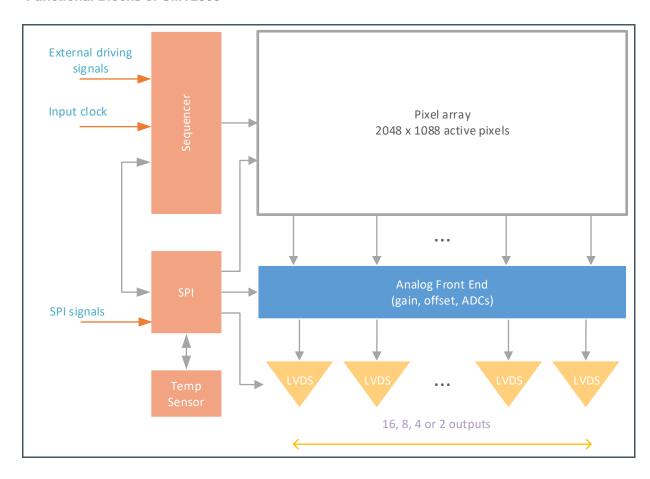

The functional blocks of this device are shown below:

Figure 2 : Functional Blocks of CMV2000

# 2 Ordering Information

| Marking          | Mono/Color | Glass Type  | Package | Delivery Quantity |

|------------------|------------|-------------|---------|-------------------|

| CMV2000-2E12M1PP | Mono       | Plain glass | PGA     | 60 pcs/tray       |

| CMV2000-2E5C1PP  | Color      | Plain glass | PGA     | 60 pcs/tray       |

| CMV2000-2E5M1LP  | Mono       | Plain glass | LGA     | 60 pcs/tray       |

| CMV2000-2E5C1LP  | Color      | Plain glass | LGA     | 60 pcs/tray       |

| CMV2000-2E5M1PP  | Mono       | Plain glass | PGA     | 60 pcs/tray       |

| CMV2000-3E12M1CA | Mono       | AR coating  | LCC     | 60 pcs/tray       |

| CMV2000-3E12M1PP | Mono       | Plain glass | PGA     | 60 pcs/tray       |

| CMV2000-3E5C1CA  | Color      | AR coated   | LCC     | 60 pcs/tray       |

| CMV2000-3E5C1PP  | Color      | Plain glass | PGA     | 60 pcs/tray       |

| CMV2000-3E5M1CA  | Mono       | AR coated   | LCC     | 60 pcs/tray       |

| CMV2000-3E5M1PA  | Mono       | AR coated   | PGA     | 60 pcs/tray       |

| CMV2000-3E5M1PP  | Mono       | Plain glass | PGA     | 60 pcs/tray       |

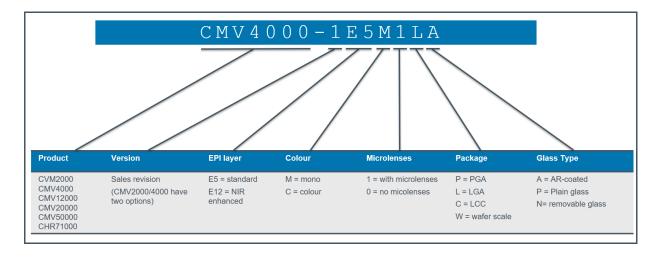

Figure 3: Ordering Code Information

Figure 4: **Differences Between Versions**

| Topic                             | Version2                                                                                                      | Version3                                                                                                                |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| PLL                               |                                                                                                               | Improved PLL                                                                                                            |

| PGA                               |                                                                                                               | Additional gain steps                                                                                                   |

| Horizontal line effect            | There shall not be a line read out when exposure starts                                                       | Horizontal line effect can be avoided by inserting dummy lines at the moment the exposure of the next frame is started. |

| Black sun effect                  | Avoiding effect with reduction of the brightness of light falling on the sensor                               | Actively removing effect                                                                                                |

| Electrical black columns          |                                                                                                               | Enable by setting the appropriate SPI register for reducing the row noise.                                              |

| Register settings                 | The registers addresses and contents are chapter 7 "Register Description". Version 3 settings than version 2. |                                                                                                                         |

| Integration in single shot mode   |                                                                                                               | Improved integration single shot mode to reduce horizontal line artifact.                                               |

|                                   |                                                                                                               | The pattern will only be visible in grey images starting from around 150DN.                                             |

| PRNU pattern                      |                                                                                                               | Correction can be done with applying a gain correction to each column, which compensates the FPN.                       |

| Column patterns in the non-linear |                                                                                                               | This can be solved by increasing gain to clip the response in its linear part.                                          |

| part of the response curve        |                                                                                                               | But setting it too high can cause a drop in saturation value and full well capacity.                                    |

# 3 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5

Absolute Maximum Ratings of CMV2000

| Symbol             | Parameter                                  | Min | Max | Unit | Comments           |  |

|--------------------|--------------------------------------------|-----|-----|------|--------------------|--|

| Electrical Pa      | Electrical Parameters                      |     |     |      |                    |  |

| VDD20              | Digital supply LVDS, ADC                   | 2.0 | 2.2 | V    |                    |  |

| VDD33              | Analog Supply ADC, PGA                     | 3.0 | 3.6 | V    |                    |  |

| VDDPIX             | Analog Pixel Supply                        | 2.3 | 3.6 | V    |                    |  |

| Vres_h             | Analog Pixel Reset Supply                  | 3.0 | 3.6 | V    |                    |  |

| Continuous         | Power Dissipation (T <sub>A</sub> = 70 °C) |     |     |      |                    |  |

| P <sub>T</sub>     | Continuous Power Dissipation               |     | 4.2 | W    | At max. frame rate |  |

| Electrostation     | Discharge                                  |     |     |      |                    |  |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM                | ±   | : 2 | kV   | JS-001-2014        |  |

| Temperature        | Ranges and Storage Conditions              |     |     |      |                    |  |

| TJ                 | Operating Junction Temperature             | -30 | 70  | °C   |                    |  |

| T <sub>STRG</sub>  | Storage Temperature Range                  | 20  | 40  | °C   |                    |  |

| RH <sub>NC</sub>   | Relative Humidity (non-<br>condensing)     | 30  | 60  | %    |                    |  |

|                    |                                            |     |     |      |                    |  |

# 4 Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics of CMV2000

| Symbol           | Parameter                    | Conditions                          | Min  | Тур | Max   | Unit |

|------------------|------------------------------|-------------------------------------|------|-----|-------|------|

| Power Supplies   |                              |                                     |      |     |       |      |

| \/DD00           | Digital supply               | Version2                            | 2.05 | 2.1 | 2.15  | V    |

| VDD20            | LVDS, ADC                    | Version3                            | 2.0  | 2.0 | 2.15  | V    |

| VDD33            | Analog Supply<br>ADC, PGA    |                                     | 3.2  | 3.3 | 3.4   | V    |

| VDDPIX           | Analog Pixel<br>Supply       |                                     | 2.9  | 3.0 | 3.1   | V    |

| Vres_h           | Analog Pixel Reset<br>Supply |                                     | 3.2  | 3.3 | 3.4   | V    |

| IDD20            | Supply current               | Readout @ Version2                  |      | 370 |       | mA   |

| 10020            | Supply current               | Readout @ Version3                  |      | 300 |       | mA   |

| IDD33            | Cupply ourrant               | Readout @ Version2                  |      | 65  |       | mA   |

| נטטט             | Supply current               | Readout @ Version3                  |      | 80  |       | mA   |

| IDDDIV           | Complex accompany            | Readout @ Version2                  |      | 20  |       | mA   |

| IDDPIX           | Supply current               | Readout @ Version3                  |      | 20  |       | mA   |

| Ires_h           | Supply current               | Readout                             |      | 15  |       | mA   |

| Doo              | Power                        | Version2                            |      | 780 |       | mW   |

| P20              | consumption                  | Version3                            |      | 640 |       | mW   |

| Daa              | Power                        | Version2                            |      | 220 |       | mW   |

| P33              | consumption                  | Version3                            |      | 270 |       | mW   |

| PPIX             | Power consumption            |                                     |      | 60  |       | mW   |

| Pres_h           | Power consumption            |                                     |      | 50  |       | mW   |

| Digital I/O CMOS | /TTL DC                      |                                     |      |     |       |      |

| V <sub>IH</sub>  | High level input voltage     |                                     | 2.0  |     | VDD33 | V    |

| V <sub>IL</sub>  | Low level input voltage      |                                     | GND  |     | 0.8   | V    |

| V <sub>OH</sub>  | High level output voltage    | VDD=3.3 V<br>I <sub>OH</sub> =-2 mA | 2.4  |     |       | V    |

| V <sub>OL</sub>  | Low level output voltage     | VDD=3.3 V<br>I <sub>OL</sub> =2 mA  |      |     | 0.4   | V    |

| Ci               | Input load                   |                                     |      |     | 2     | pF   |

|                  | ·                            |                                     |      |     |       | •    |

| Symbol                         | Parameter                                                                  | Conditions                                                           | Min        | Тур     | Max  | Unit |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|------------|---------|------|------|

| Со                             | Output load                                                                |                                                                      |            |         | 2    | pF   |

| f <sub>CLK_IN</sub>            | CLK_IN frequency                                                           |                                                                      | 5          |         | 48   | MHz  |

| TIA/EIA-644A LV                | DS - DRIVER SPECIFICA                                                      | TIONS (OUTX_N/P, OUTCLK_                                             | _N/P, OUTC | TR_N/P) |      |      |

| V <sub>OD</sub>                | Differential output voltage                                                | Steady State, RL = 100 $\Omega$                                      | 247        | 350     | 454  | mV   |

| $\Delta V_{OD}$                | Difference in V <sub>OD</sub><br>between<br>complementary<br>output states | Steady State, RL = 100 $\Omega$                                      |            |         | 50   | mV   |

| V <sub>oc</sub> <sup>(1)</sup> | Common mode voltage                                                        | Steady State, RL = 100 $\Omega$                                      | 1.26       | 1.37    | 1.50 | V    |

| ΔV <sub>oc</sub>               | Difference in V <sub>oc</sub><br>between<br>complementary<br>output states | Steady State, RL = 100 $\Omega$                                      |            |         | 50   | mV   |

| I <sub>OS,GND</sub>            | Output short circuit current to ground                                     | V <sub>OUTP</sub> =V <sub>OUTN</sub> =GND                            |            |         | 24   | mA   |

| I <sub>OS,PN</sub>             | Output short circuit current                                               | V <sub>OUTP</sub> =V <sub>OUTN</sub>                                 |            |         | 12   | mA   |

| TIA/EIA-644A LV                | DS-RECEIVER SPECIFIC                                                       | ATIONS (LVDS_CLK_N/P)                                                |            |         |      |      |

| V <sub>ID</sub>                | Differential input voltage                                                 | Steady state                                                         | 100        | 350     | 600  | mV   |

| V <sub>IC</sub>                | Receiver input range                                                       | Steady state                                                         | 0.0        |         | 2.4  | V    |

| I <sub>ID</sub>                | Receiver input current                                                     | V <sub>INP INN</sub> =1.2 V±50 mV,<br>0≤ V <sub>INP INN</sub> ≤2.4 V |            |         | 20   | μΑ   |

| $\Delta I_{ID}$                | Receiver input current difference                                          | $ I_{\text{INP}} - I_{\text{INN}} $                                  |            |         | 6    | μΑ   |

| Timing                         |                                                                            |                                                                      |            |         |      |      |

| CLK_IN                         |                                                                            |                                                                      | 5          |         | 48   | MHz  |

| _                              |                                                                            |                                                                      |            |         |      |      |

| LVDS_CLK_N/P                   |                                                                            |                                                                      | 50         |         | 480  | MHz  |

$V_{oc}$  is dependent on the 2.1 V supply voltage; therefore, these values differ from the TIA/EIA-644A spec.

# **5** Specification Overview

Below are the typical electro-optical specifications of CMV2000. These are typical values with typical supplies at room temperature.

Figure 7: Electro-Optical Characteristics of CMV2000

| Specification                  | Value                     | Comment                                                                                                    |

|--------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------|

| Effective pixels               | 2048 x 1088               |                                                                                                            |

| Pixel pitch                    | 5.5 x 5.5 µm <sup>2</sup> |                                                                                                            |

| Optical format                 | 2/3"                      |                                                                                                            |

| Full well charge               | 13.5 ke <sup>-</sup>      | Pinned photodiode pixel                                                                                    |

| Conversion gain                | 0.075 LSB/e <sup>-</sup>  | 10-bit mode, unity gain                                                                                    |

| Sensitivity                    | 5.56 V/lux.s<br>0.27 A/W  | With microlenses @ 550 nm                                                                                  |

| Temporal noise (analog domain) | 13 e <sup>-</sup>         | Pipelined global shutter (GS) with correlated double sampling (CDS). Read noise                            |

| Dynamic range                  | 60 dB                     |                                                                                                            |

| Pixel type                     | Global shutter pixel      | Allows fixed pattern noise correction and reset (kTC) noise canceling through correlated double sampling.  |

| Shutter type                   | Pipelined global shutter  | Exposure of next image during read-out of the previous image.                                              |

| Parasitic light sensitivity -  | <1/50 000                 |                                                                                                            |

| Shutter efficiency             | >99.998%                  |                                                                                                            |

| Color filters                  | Optional                  | RGB Bayer pattern                                                                                          |

| Micro lenses                   | Yes                       |                                                                                                            |

| Fill factor                    | 42%                       | w/o micro lens                                                                                             |

| QE * FF                        | 60%                       | @ 550 nm with micro lenses.                                                                                |

| Dark current signal            | 125 e <sup>-</sup> /s     | @ 25 °C die temperature. The dark current doubles with every 6.5 °C increase                               |

| DSNU                           | 3 LSB/s                   | 10-bit mode                                                                                                |

| Fixed pattern noise            | <1 LSB RMS                | <0.1% of full swing, 10-bit mode                                                                           |

| PRNU                           | < 1% RMS of signal        |                                                                                                            |

| LVDS output channel            | 16                        | Each data output running @ 480 Mbit/s. 8, 4 and 2 outputs selectable at reduced frame rate                 |

| Frame rate                     | 340 frames/s              | Using a 10-bit/pixel and 480 Mbit/s LVDS. Higher frame rate possible in row windowing mode.                |

| Timing generation              | On-chip                   | Possibility to control exposure time through external pin.                                                 |

| PGA                            | Yes                       | 4 analog gain settings                                                                                     |

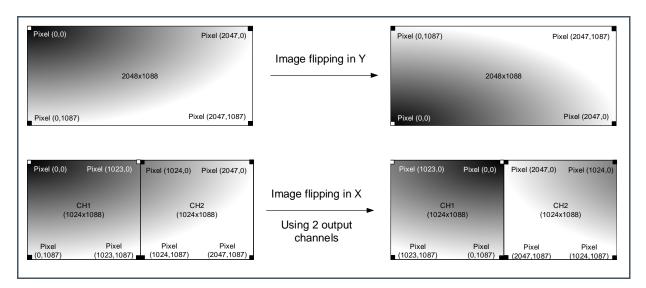

| Programmable registers         | Sensor parameters         | Window coordinates, Timing parameters, Gain & offset, Exposure time, flipped read-out in X and Y direction |

| Specification       | Value                                             | Comment                                                                                                                                                                                                                   |

|---------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Multi-frame read-out with different exposure time | Successive frames are read out with increasing exposure times. The final image is a combination (externally) of these frames.                                                                                             |

| Supported HDR modes | Interleaved integration times                     | Interleaved exposure times for different rows: Odd rows (double rows for color) have a different exposure compared to even rows (double rows for color). Final image is a combination of the two (through interpolation). |

|                     | Piecewise linear response                         | Response curve with two knee points.                                                                                                                                                                                      |

| ADC                 | 10-bit/12-bit                                     | Column ADC                                                                                                                                                                                                                |

| Interface           | LVDS                                              | Serial output data + synchronization signals                                                                                                                                                                              |

| I/O logic levels    | LVDS = 1.8 V<br>Dig. I/O = 3.3 V                  |                                                                                                                                                                                                                           |

|                     | Version 2: 2.1 V<br>Version 3: 2.0                | LVDS, ADC                                                                                                                                                                                                                 |

| Supply voltages     | 3.0 V                                             | Pixel array supply                                                                                                                                                                                                        |

|                     | 3.3 V                                             | Dig. I/O, SPI, PGA                                                                                                                                                                                                        |

|                     | CLK_IN                                            | Between 5 and 48 MHz                                                                                                                                                                                                      |

| Clock inputs        | LVDS_CLK_N/P                                      | Between 50 and 480 MHz, LVDS                                                                                                                                                                                              |

|                     | SPI_CLK                                           | Max. 48 MHz                                                                                                                                                                                                               |

| Power               | 550 mW to 1200 mW                                 | Actual wattage is dependent on the used configuration                                                                                                                                                                     |

|                     |                                                   | μPGA (95 pins)                                                                                                                                                                                                            |

| Package             | Custom ceramic package                            | LGA (95 pins)                                                                                                                                                                                                             |

|                     | paonago                                           | LCC (92 pins)                                                                                                                                                                                                             |

| Operating range     | -30 °C to 70 °C                                   | Dark current and noise performance will degrade at higher temperature                                                                                                                                                     |

| Cover glass         | D263                                              | Plain or AR glass, no IR cut-off filter on color devices                                                                                                                                                                  |

| FCD                 | Class 1A HBM                                      |                                                                                                                                                                                                                           |

| ESD                 | Class 4C CDM                                      |                                                                                                                                                                                                                           |

| RoHS                | Compliant                                         |                                                                                                                                                                                                                           |

### 5.1 Spectral Characteristics

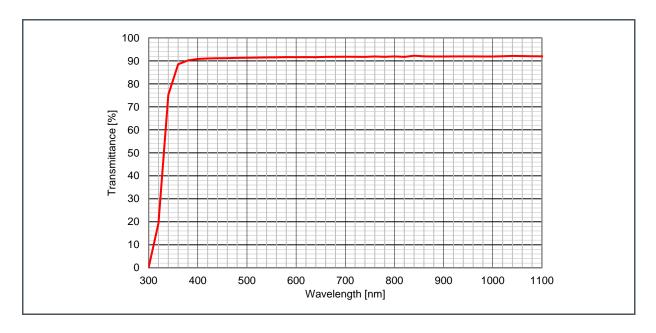

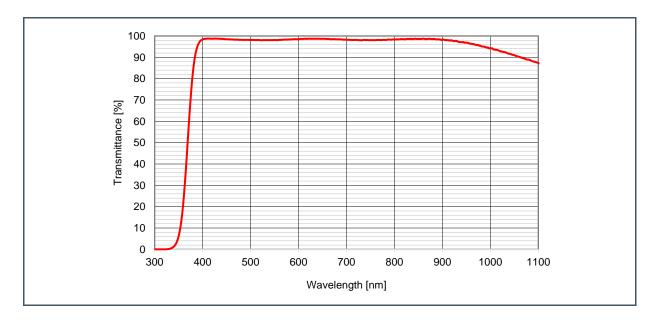

The cover glass of the CMV2000 is plain D263 glass with a transmittance as shown in Figure 8. Refraction index of the glass is 1.52.

When a color sensor is used an IR-cutoff filter should be placed in the optical path of the sensor.

Figure 8: Transmittance Curve Offer D263 Cover Plain Glass

Figure 9: Transmittance Curve for D263 AR Coated Glass

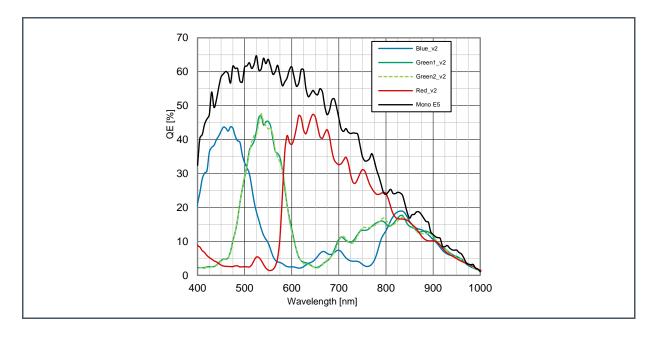

When a color version of the CMV2000 is used, the color filters are applied in a Bayer pattern. The color version of the CMV2000 always has microlenses. The typical spectral response of the CMV with color filters and D263 cover glass is shown in Figure 10. The use of an IR cut-off filter in the optical path of the CMV2000 image sensor is necessary to obtain good color separation when using light with an NIR component. The typical spectral response of a monochrome CMV2000 with microlenses can be found in Figure 10 as well.

Figure 10:

Typical Spectral Response of CMV2000 with RGB Color Filters and D263 Cover Glass

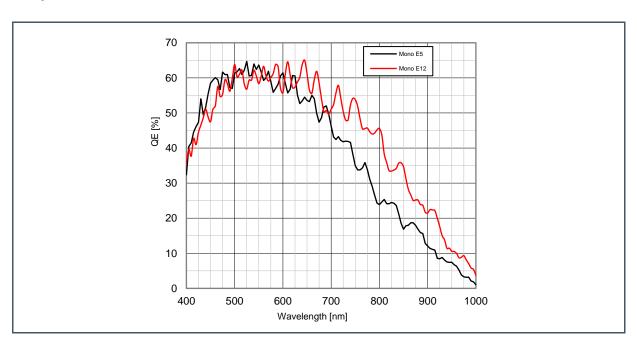

A variation from the standard CMV2000 image sensors is processed on 12  $\mu$ m epi (E12) Si wafers. The thicker epi-layer wafer starting material increases significantly the QE for wavelengths above 600 nm. Around 900 nm the QE is about doubled and increases from 8% to 16%. This is shown in Figure 11.

Figure 11:

Response of E12 Devices and Normal Devices

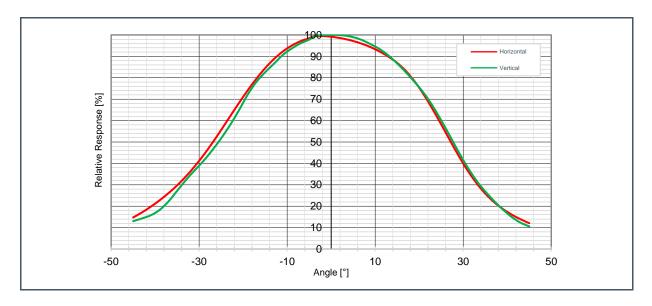

The typical angular response for a CMV2000 sensor can be seen in Figure 12.The data includes the horizontal and vertical angles.

Figure 12: Horizontal and Vertical Angular Response

# **6** Functional Description

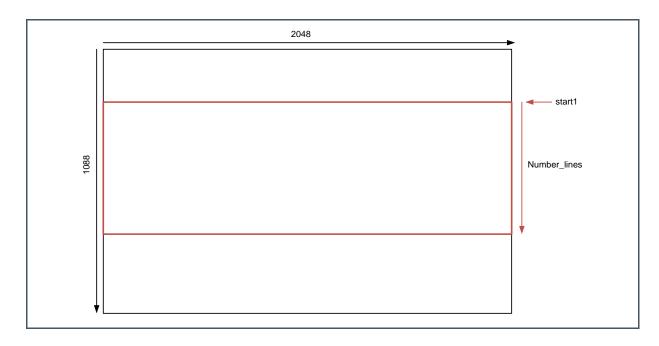

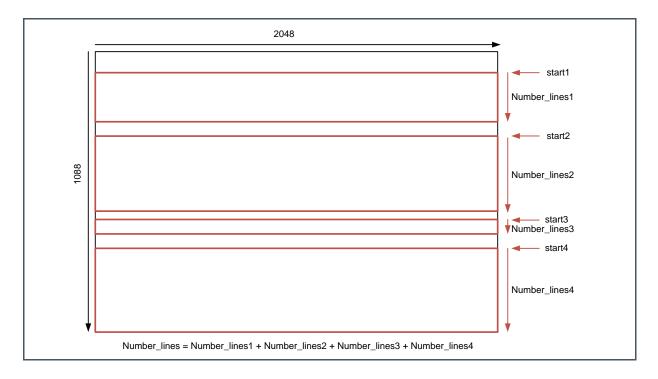

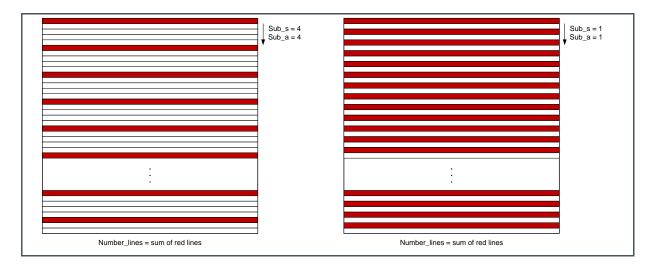

#### 6.1 Sensor Architecture

Figure 2 shows the image sensor architecture. The internal sequencer generates the necessary signals for image acquisition. The image is stored in the pixel (global shutter) and is then read out sequentially, row-by-row. On the pixel output, an analog gain of x1, x1.2, x1.4 and x1.6 is possible. The pixel values then passes to a column ADC cell, in which ADC conversion is performed. The digital signals are then read out over multiple LVDS channels. Each LVDS channel reads out 128 adjacent columns of the array. In the Y-direction, rows of interest are selected through a row-decoder which allows a flexible windowing. Control registers are foreseen for the programming of the sensor. These register parameters are uploaded via a four-wire SPI interface. A temperature sensor which can be read out over the SPI interface is also included.

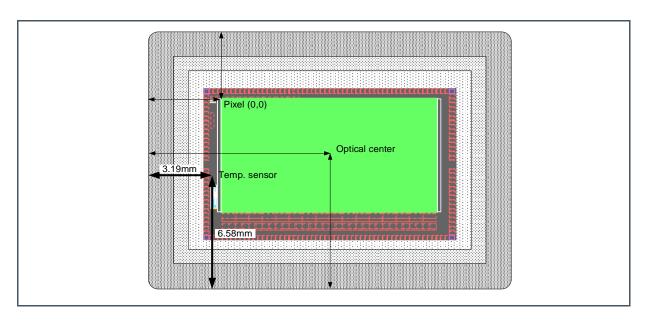

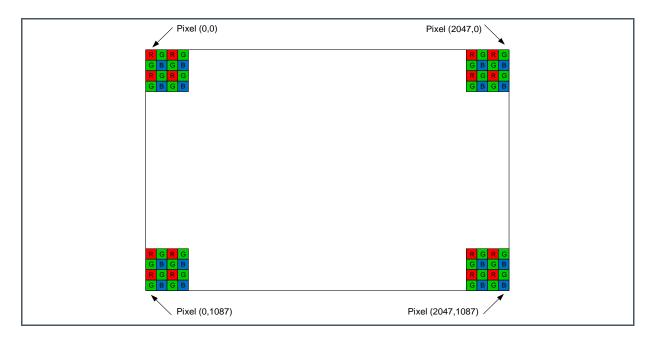

#### 6.1.1 Pixel Array

The pixel array consists of 2048 x 1088 square global shutter pixels with a pitch of 5.5  $\mu$ m (5.5  $\mu$ m x 5.5  $\mu$ m). This results in an optical area of close to 2/3 optical inch (12.7 mm). This means that most off-the-shelf C-mount lenses can be used.

The pixels are designed to achieve maximum sensitivity with low noise and low PLS specifications. Micro lenses are placed on top of the pixels for improved fill factor and quantum efficiency (>50%).

#### 6.1.2 Analog Front End

The analog front end consists of 2 major parts, a column amplifier block and a column ADC block.

The column amplifier prepares the pixel signal for the column ADC and applies analog gain if desired (programmable using the SPI interface). The column ADC converts the analog pixel value to a 10 or 12-bit value. A digital offset can also be applied to the output of the column ADC's. All gain and offset settings can be programmed using the SPI interface.

#### 6.1.3 LVDS Block

The LVDS block converts the digital data coming from the column ADC into standard serial LVDS data running at maximum 480 Mbps. The sensor has 18 LVDS output pairs:

- 16 Data channels

- 1 Control channel

- 1 Clock channel

The 16 data channels are used to transfer 10-bit or 12-bit data words from sensor to receiver. The output clock channel transports a DDR clock, synchronous to the data on the other LVDS channels.

This clock can be used at the receiving end to sample the data. The data on the control channel contains status information on the validity of the data on the data channels, among other useful sensor status information. Details on the LVDS timing and format can be found in chapter 6.3 of this document.

LVDS requires parallel termination at the receiver side. So between LVDS\_CLK\_P (pin D1) and LVDS\_CLK\_N (pin D2) should be an external  $100\Omega$  resistor. Also all the LVDS outputs should all be externally terminated at the receiver side. See the TIA/EIA-644A standard for details.

#### 6.1.4 Sequencer

The on-chip sequencer will generate all required control signals to operate the sensor from only a few external control clocks. This sequencer can be activated and programmed through the SPI interface. A detailed description of the SPI registers and sensor (sequencer) programming can be found in chapter 6.4 of this document.

#### 6.1.5 SPI Interface

The SPI interface is used to load the sequencer registers with data. The data in these registers are used by the sequencer while driving and reading out the image sensor. Features like windowing, subsampling, gain and offset are programmed using this interface. The data in the on-chip registers can also be read back for test and debug of the surrounding system. Chapter 6.2.8 contains more details on SPI programming and timing.

#### 6.1.6 Temperature Sensor

A 16-bit digital temperature sensor is included in the image sensor and can be controlled by the SPI-interface. The on-chip temperature can be obtained by reading out the registers with address 126 and 127 (in burst mode, see chapter SPI Read for more details on this mode).

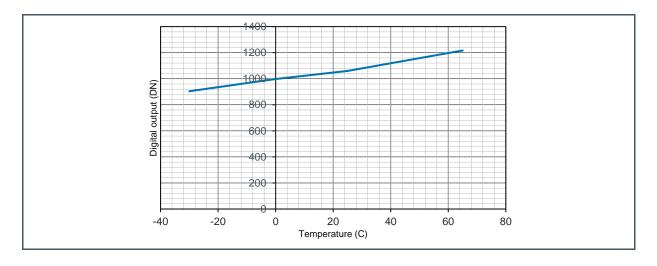

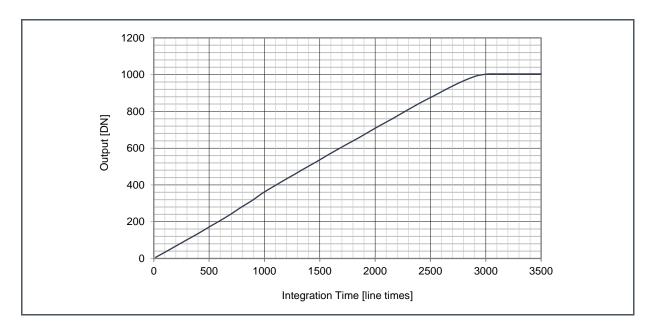

A calibration of the temperature sensor is needed for absolute temperature measurements per device because the offset differs from device to device. The temperature sensor requires a running input clock (CLK\_IN), the other functions of the image sensor can be operational or in standby mode. The output value of the sensor is dependent on the input clock. A typical temperature sensor output vs. temperature curve at 40 MHz can be found in Figure 13. The die temperature will be about 10 °C~15 °C higher than ambient temperature. The ceramic package has about the same temperature as the die.

The typical (offset) value of the temperature sensor at 0 °C would be: 1000\* (f [MHz])/40 DN. This offset can differ per device. A typical slope would be around 0.3\*40/f[MHz] °C/DN.

Figure 13:

Typical Output of the Temperature Sensor of the CMV2000

Figure 14:

Location of the Temperature Sensor

### 6.2 Operating the Sensor

This section explains how to connect and power the sensor, as well as basic recipes of how to configure the sensor in a certain operation mode.

#### 6.2.1 Power Supplies

To power the sensor, eight externally generated supplies are required as listed in Figure 6.

Figure 15:

Different Power Supplies

| Supply Name | Usage                    | Description               |

|-------------|--------------------------|---------------------------|

| VDD20       | LVDS, ADC                | Digital supply            |

| VDD33       | Dig. I/O, PGA, SPI, ADC  | Analog supply             |

| VDDPIX      | Pixel array power supply | Analog pixel supply       |

| Vres_h      | Pixel reset pulse        | Analog pixel reset supply |

The power figures are measured at 48 MHz CLK\_IN speed in 16 channels mode while constantly grabbing images. When idle, the sensor will consume about 30% less energy. Reducing the amount of output channels will reduce power consumption of the VDD20 supply and will have the biggest impact on the power consumption.

All variations on the VDD33 and VDDPIX can contribute to variations (noise) on the analog pixel signal, which is seen as noise in the image. During the camera design, precautions have to be taken to supply the sensor with very stable supply voltages to avoid this additional noise.

Because of the peak currents, decoupling is advised. Place large decoupling capacitors directly at the output of the voltage regulator to filter low noise and improve peak current supply. We advise 1x 330  $\mu$ F electrolytic, 1x 33  $\mu$ F tantalum and a 10  $\mu$ F ceramic capacitor per supply, directly at the output of the regulator.

Place small decoupling capacitors as close as possible to the sensor between supply pins and ground. We advise 1x 4.7  $\mu$ F and 1x 100 nF ceramic capacitor per power supply pin (see pin list) and 1x 100  $\mu$ F ceramic capacitor per power supply plane (VDD20, VDDPIX, VDD33). Vres\_h does not need a 100  $\mu$ F capacitor. See the pin list for exact pin numbers for every supply. Analog and digital ground can be tied together.

#### 6.2.2 Biasing

For optimal performance, some pins need to be decoupled to ground or to VDD. Please refer to the pin list for a detailed description for every pin and the appropriate decoupling if applicable.

#### 6.2.3 Digital Input Pins

Figure 16 gives an overview of the external pins used to drive the sensor. The digital signals are sampled on the rising edge of the CLK\_IN, therefore the length of the signal applied to an input should be at least 1 CLK\_IN period to assure it has been detected. All digital I/O's have a capacitance of 2 pF max.

Figure 16:

Digital Input Pins Description

| Pin Name     | Description                                                                                                                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_IN       | Master input clock, frequency range between 5 and 48 MHz.                                                                                                                                                                                   |

| LVDS_CLK_N/P | High speed LVDS input clock, frequency range between 50 and 480 MHz.                                                                                                                                                                        |

| SYS_RES_N    | System reset pin, active low signal. Resets the on-board sequencer and must be kept low during start-up. This signal should be at least one period of CLK_IN long to assure detection on the rising edge of CLK_IN.                         |

| FRAME_REQ    | Frame request pin. When a high level is detected on this pin the programmed number of frames is captured and sent by the sensor. This signal should be at least one period of CLK_IN long to assure detection on the rising edge of CLK_IN. |

| SPI_IN       | Data input pin for the SPI interface. The data to program the image sensor is sent over this pin.                                                                                                                                           |

| SPI_EN       | SPI enable pin. When this pin is high the data should be written/read on the SPI.                                                                                                                                                           |

| SPI_CLK      | SPI clock. This is the clock on which the SPI runs.                                                                                                                                                                                         |

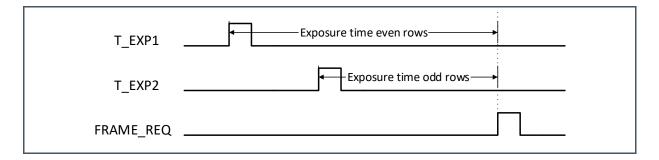

| T_EXP1       | Input pin to program the exposure time externally. Optional                                                                                                                                                                                 |

| T_EXP2       | Input pin to program the exposure time externally in HDR mode. Optional                                                                                                                                                                     |

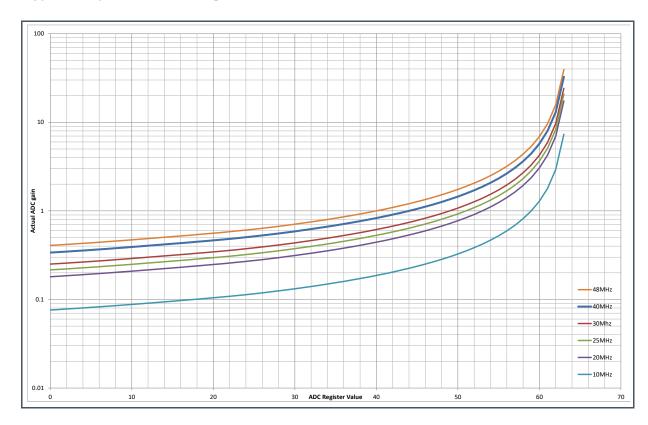

#### 6.2.4 Input Clock

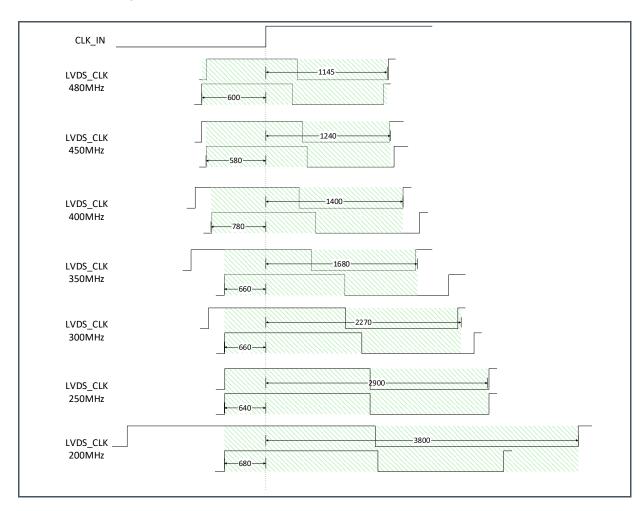

The high-speed LVDS input clock (LVDS\_CLK\_N/P) defines the output data rate of the CMV2000. The master clock (CLK\_IN) must be 10 or 12 times slower depending on the programmed bit mode setting. The maximum data rate of the output is 480 Mbps which results in a LVDS\_CLK\_N/P of 480 MHz and a CLK\_IN of 48 MHz in 10-bit mode and 40 MHz in 12-bit mode. The minimum frequencies are 5 MHz for CLK\_IN and 50MHz for LVDS\_CLK\_N/P. Any frequency between the minimum and maximum can be applied by the user and will result in a corresponding output data rate, like showed in Figure 17.

Figure 17:

Output Data Rate Depending on the CLK\_IN and Bit Mode

| CLK_IN | LVDS_CLK 10-Bit | LVDS_CLK 12-Bit |

|--------|-----------------|-----------------|

| 5 MHz  | 50 MHz          | 60 MHz          |

| 40 MHz | 400 MHz         | 480 MHz         |

| 48 MHz | 480 MHz         | N/A             |

The rising edge LVDS input clock can have a limited delay with respect to the rising edge of the master input clock, depending on clock speed. In Figure 18, the skew limits are shown for different clock speeds and for an LVDS clock that rises before and after the master input clock. To assure

proper working of the sensor, the skew of the LVDS clock should always fall within these limits, shown as the green area.

Figure 18: LVDS Clock Delay Versus Master Clock

Only for the version 3 of this image sensor, the SPI registers with address 114 and 116 must be programmed to the correct frequency range when the CLK\_IN frequency is changed.

#### 6.2.5 Frame Rate Calculation

The frame rate is defined by 2 main factors:

- Exposure time

- Read-out time

To simplify the calculation we will assume that the exposure time is shorter than the read-out time and that the sensor is operating at default settings, taking a full resolution 10-bit image at 48 MHz through 16 outputs. This means that the frame rate will be defined only by the read-out time because the exposure time happens in parallel with the read-out. The read-out time is defined by:

Output clock speed: Max 240 MHz

ADC mode: 10-bit or 12-bit

Number of lines read-out

Number of LVDS outputs used: Max 16 outputs

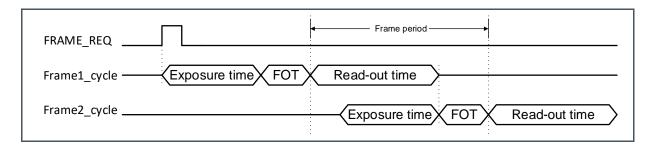

If any of these parameters is changed, it will have an impact on the frame rate. In default operation this will result in 340 fps. The total read-out time is composed of two parts: FOT (frame overhead time) and image read-out time.

The FOT is defined as shown in Equation 1:

#### **Equation 1:**

$$FOT = \left( fot\_length + \left( 2 * \frac{16}{\#outputs \ used} \right) \right) * 129 * master \ clock \ period$$

With fot\_length (register 73) at its default value of 10, this results in 32.25 µs frame overhead time.

The image read-out time is defined as shown in Equation 2:

#### **Equation 2:**

$$Image\ read-out\ time = \left(129*master\ clock\ period*\frac{1}{\#outputs\ used}\right)*nr\_lines$$

Reading out a full resolution image, this results in 2.924 ms image read-out time.

The total read-out time is now the sum of the FOT and the image read-out time, which results in  $32.25 \,\mu s + 2.924 \,ms$  or  $2.9525 \,ms$  to read out a single full resolution image. The frame rate is thus  $338 \,ps$ .

Figure 19 gives some examples of how the frame rate increases when reading out a smaller frame in 10-bit mode.

Figure 19: Frame Rate for Different Frame Size

| Number of Columns | Number of Lines | Frame Rate |

|-------------------|-----------------|------------|

| 2048              | 1088            | 338        |

| 2048              | 512             | 710        |

| 2048              | 70              | 4537       |

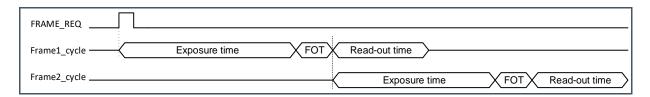

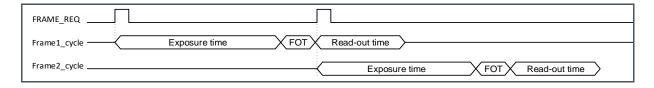

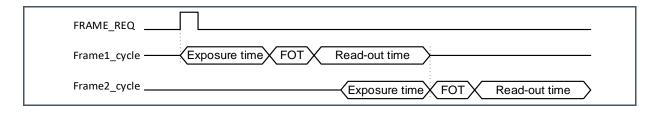

Figure 20 shows the frame period for 2 consecutive frame cycle.

Figure 20: Frame Period

When the exposure time is greater than the read-out time, the frame rate is mostly defined by the exposure time itself (because the exposure time would be much longer than the FOT).

#### 6.2.6 Start-Up Sequence

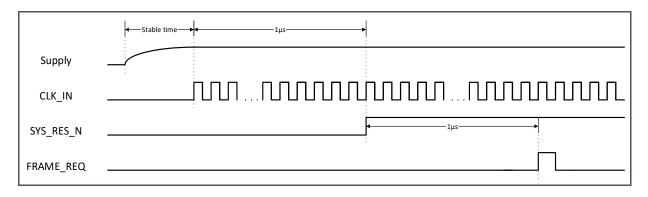

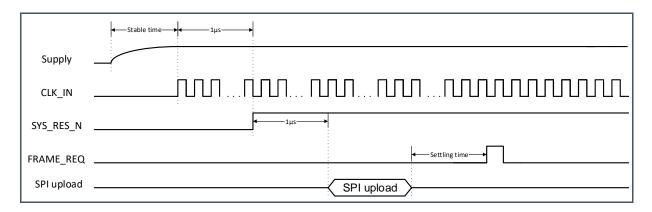

The sequence, shown in Figure 21 should be followed when the CMV2000 is started up in default output mode (480 Mbps, 10-bit resolution). There is no specific startup sequence for the power supplies needed.

Figure 21: Start-Up Sequence for 480 Mbps @ 10-Bit

The CLK\_IN master clock (48 MHz for 480 Mbps in 10-bit mode) should only start after the rise time of the supplies. The external reset pin should be released at least 1 µs after the supplies have become stable. The first frame can be requested 1 µs after the reset pin has been released.

If the register settings need to be changed (e.g. when using 12-bit mode), this can be done through an SPI upload 1 µs after the rising edge on the SYS\_RES\_N pin, as described in Figure 22. In this case, the FRAME\_REQ pulse must not be sent until after the SPI upload is completed, plus a settling time. This settling time is to ensure that the changes programmed in the SPI upload have taken effect before an image is captured. The main factor that determines this settling time is the change in ADC gain, because the voltage over the ramp capacitor has to settle. For typical applications, where the

ADC gain is changed from the default value of 32 to a value that saturates the ADC output (40 to 45 at 48 MHz), the settling time is 5 ms. In extreme cases, when the gain is changed from default to the maximum value, the settling time will increase to 20 ms.

Figure 22: Start-Up Sequence for 12-Bit Mode

#### 6.2.7 Reset Sequence

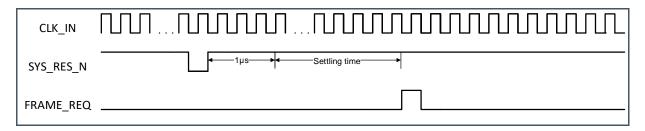

If a sensor reset is necessary while the sensor is running, the sequence in Figure 23 should be followed. The on-board sequencer will be reset and all programming registers will return to their default start-up values when a falling edge is detected on the SYS\_RES\_N pin. As with the start-up sequence, there is a minimum time of 1 µs plus a settling time needed before a FRAME\_REQ pulse can be sent, to allow the gain settings to settle at their default value.

Figure 23: Reset Sequence

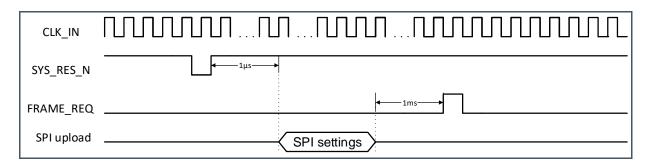

When register settings are uploaded after the reset (e.g. when changing the bit mode), the sequence of Figure 24 should be followed.

Figure 24:

Reset Sequence When Changing Bit Mode

#### 6.2.8 SPI Programming

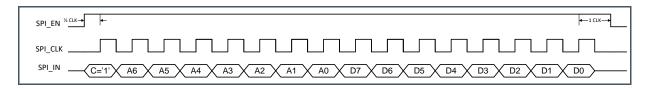

Programming the sensor is done by writing the appropriate values to the on-board registers. These registers can be written over a simple serial interface (SPI). The details of the timing and data format are described below. The data written to the programming registers can also be read out over this same SPI interface.

The details of the timing and data format are described in following paragraphs.

#### **SPI Write**

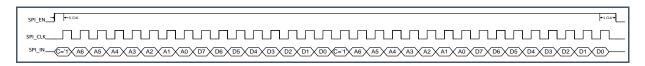

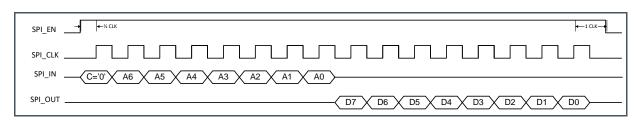

The timing to write data over the SPI interface can be found in Figure 25.

Figure 25: SPI Write Timing

The data is sampled by the CMV2000 on the rising edge of the SPI\_CLK. The SPI\_CLK has a maximum frequency of 48 MHz. The SPI\_EN signal has to be high for half a clock period before the first data bit is sampled. After the last data bit is sent, SPI\_EN has to remain high for 1 clock period and SPI\_CLK has to receive a final falling edge to complete the write operation.

One write action contains 16 bits:

- One control bit: First bit to be sent, indicates whether a read ('0') or write ('1') will occur on the SPI interface.

- 7 address bits: These bits form the address of the programming register that needs to be written. The address is sent MSB first.

• 8 data bits: These bits form the actual data that will be written in the register selected with the address bits. The MSB data is written first.

When several sensor registers need to be written, the timing above can be repeated with SPI\_EN remaining high all the time. See the Figure 26 for an example of 2 registers being written in burst.

Figure 26: SPI Write Timing for 2 Registers in Burst

All registers should be updated during IDLE time. The sensor is not IDLE during a frame burst (between start of integration of first frame and read-out of last pixel of last frame).

Registers 35-38, 40-69, 100-103 can be updated during IDLE or FOT. Registers 1-34 and 70-71 can always be updated but it is recommended to update these during IDLE or FOT to minimize image effects. Registers 78-79 can always be updated without disrupting the imaging process.

#### **SPI Read**

The timing to read data from the registers over the SPI interface can be found in Figure 27.

Figure 27: SPI Read Timing

To indicate a read action over the SPI interface, the control bit on the SPI\_IN pin is made '0'. The address of the register being read out is sent immediately after this control bit (MSB first). After the LSB of the address bits, the data is launched on the SPI\_OUT pin on the falling edge of the SPI\_CLK. This means that the data should be sampled by the receiving system on the rising edge of the SPI\_CLK. The data comes over the SPI\_OUT with MSB first. When reading out the temperature sensor over the SPI, addresses 126 and 127 should de read-out in burst mode (keep SPI\_EN high).

#### 6.2.9 Requesting a Frame

After starting up the sensor (see chapter 6.2.6), a number of frames can be requested by sending a FRAME\_REQ pulse. The number of frames can be set by programming the appropriate register (addresses 70 and 71). The default number of frames to be grabbed is 1.

In internal-exposure-time mode, the exposure time will start after this FRAME\_REQ pulse. In the external-exposure-time mode, the read-out will start after the FRAME\_REQ pulse. Both modes are explained into detail in the chapters below.

#### **Internal Exposure Control**

In this mode, the exposure time is set by programming the appropriate registers (address 42-44).

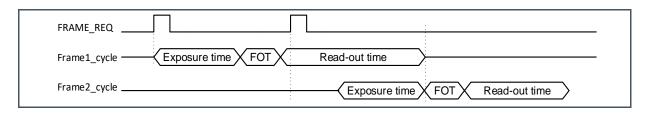

After the high state of the FRAME\_REQ pulse is detected, the exposure time will start after a delay of 133 clock cycles, see AN16 – Exposure timings for all timing details. When the exposure time ends (as programmed in the registers), the pixels are being sampled and prepared for read-out. This sequence is called the frame overhead time (FOT). Immediately after the FOT, the frame is read-out automatically. If more than one frame is requested, the exposure of the next frame starts already during the read-out of the previous one (see Figure 28).

Figure 28:

Request for 2 Frames in Internal- Exposure-Time Mode

Figure 29:

Two Requests for 1 Frame in Internal Exposure Mode<sup>(1)</sup>

(1) This request form is just applicable to Version 3.

When the exposure time is shorter than the read-out time, the FOT and read-out of the next frame will start immediately after the read-out of the previous frame. Keep in mind that the next FRAME\_REQ pulse has to occur after the FOT of the current frame. For an exact calculation of the exposure time, see chapter 6.4.1.

When a new FRAME\_REQ is applied, the exposure of the next frame will be delayed so that the FOT begins right after the read-out time of the current frame.

Figure 30:

Request for 2 Frames in Internal Exposure Mode with Exposure Time < Read-Out Time

Figure 31:

Two Requests for 1 Frame in Internal Exposure Mode<sup>(1)</sup>

(1) Only applicable for Version 3.

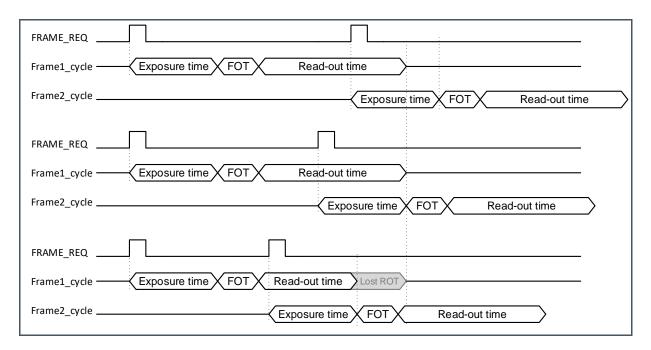

#### Timing Calculation for Version2:

If the exposure time is shorter than the read-out time, keep in mind that when you apply a next FRAME\_REQ pulse during the read-out of the current frame, the exposure of that new frame will start immediately. Therefore, you have to keep enough time between the two FRAME\_REQ pulses so the read-out times do not overlap. If the FOT of the next frame starts during the read-out of the current frame, that read-out will be aborted immediately, as shown in Figure 32. If the exposure time is longer than the read-out time, the read-out times of two consecutive frames cannot overlap and will not cause a problem. The minimum time between two FRAME\_REQ pulses is given by Equation 3:

#### **Equation 3:**

$min.time = exposure\ time + FOT + (Readout\ time - Exposure\ time) = FOT + Readout\ time$

Figure 32:

The Timing Effect of Two Requests for 1 Frame in Internal Exposure Mode

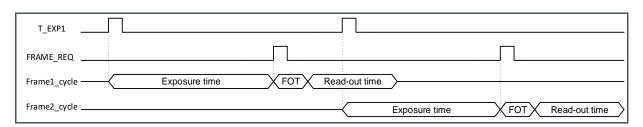

#### **External Exposure Time**

The exposure time can also be programmed externally by using the T\_EXP1 input pin. This mode needs to be enabled by setting the appropriate register (address 41). In this case, the exposure starts when a high state is detected on the T\_EXP1 pin. When a high state is detected on the FRAME\_REQ input, the exposure time stops and the read-out will start automatically. A new exposure can start by sending a pulse to the T\_EXP1 pin during or after the read-out of the previous frame. The minimum time between T\_EXP1 and FRAME\_REQ is 1 master clock cycle, the minimum time between FRAME\_REQ and T\_EXP1 pulse is FOT. For an exact calculation of the exposure time see chapter 6.4.1.

Figure 33:

Request for 2 Frames Using External-Exposure-Time Mode

#### 6.3 Sensor Readout Format

#### 6.3.1 LVDS Data Outputs

The CMV2000 has LVDS (low voltage differential signaling) outputs to transport the image data to the surrounding system. Next to 16 data channels, the sensor also has two other LVDS channels for control and synchronization of the image data. In total, the sensor has 18 LVDS output pairs (2 pins for each LVDS channel):

- 16 Data channels

- 1 Control channel

- 1 Clock channel

This means that a total of 36 pins of the CMV2000 are used for the LVDS outputs (32 for data + 2 for LVDS clock + 2 for control channel). See the pin list for the exact pin numbers of the LVDS outputs.

The 16 data channels are used to transfer the 10-bit or 12-bit pixel data from the sensor to the receiver in the surrounding system.

The output clock channel transports a clock, synchronous to the data on the other LVDS channels. This clock can be used at the receiving end to sample the data. This clock is a DDR clock which means that the frequency will be half of the output data rate. When 480 Mbps output data rate is used, the LVDS output clock will be 240 MHz.

The data on the control channel contains status information on the validity of the data on the data channels. Information on the control channel is grouped in 10-bit or 12-bit words that are transferred synchronous to the 16 data channels.

#### 6.3.2 Low-Level Pixel Timing

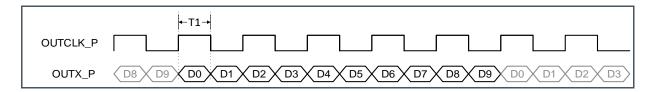

Figure 34 and Figure 35 show the timing for transfer of 10-bit and 12-bit pixel data over one LVDS output. To make the timing more clear, the figures show only the p-channel of each LVDS pair. The data is transferred LSB first, with the transfer of bit D0 during the high phase of the DDR output clock OUTCLK.

Figure 34: 10-Bit Pixel Data on an LVDS Channel

The time 'T1' in Figure 34 is 1/10<sup>th</sup> of the period of the CLK\_IN input clock. If a frequency of 48 MHz is used for CLK\_IN (max in 10-bit mode), this results in a 240 MHz OUTCLK frequency.

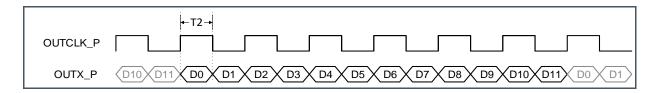

Figure 35: 12-Bit Pixel Data on an LVDS Channel

The time 'T2' in Figure 35 is 1/12<sup>th</sup> of the period of the CLK\_IN input clock. If a frequency of 40 MHz is used for CLK\_IN (max in 12-bit mode), this results in a 240 MHz OUTCLK frequency.

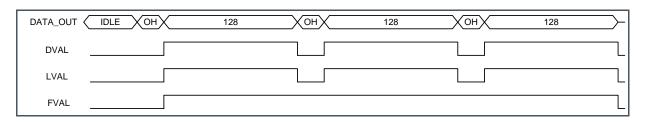

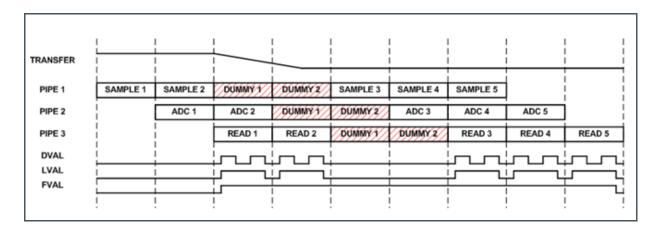

#### 6.3.3 Read-Out Timing

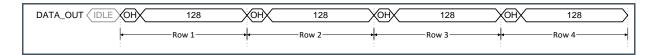

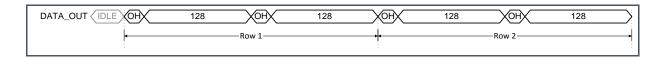

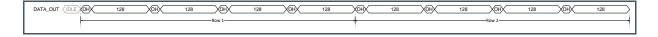

The read-out of image data is grouped in bursts of 128 pixels per channel. Each pixel is either 10 or 12 bits of data (see Chapter 6.3.2). One complete pixel period equals one period of the input clock CLK\_IN. For details on pixel remapping and pixel vs. channel location please see chapter 6.3.4 of this document. An overhead time exists between two bursts of 128 pixels. This overhead time has the same length of one pixel read-out (i.e. the length of 10 or 12 bits at the selected data rate or one CLK\_IN period). For details on how to program the sequencer for different output modes, see chapter 6.5.1.

#### 10-Bit Mode

In this section, the read-out timing for the default 10-bit mode is explained. In this mode the maximum frame rate of 340 fps can be reached.

For simplification, the timing for only one LVDS channel is shown in every case in the following paragraphs:

- 16 Output Channels

- 8 Output Channels

- 4 Output Channels

- 2 Output Channels

#### 16 Output Channels:

By default, all 16 data output channels are used to transmit the image data. This means that an entire row of image data is transferred in one slot of 128 pixel periods (16 x 128 = 2048). This results in a maximum frame rate of 340 fps.

Figure 36:

Output Timing in Default 16 Channels Mode

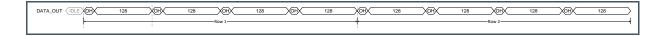

#### 8 Output Channels:

When only 8 LVDS output channels are used, the read-out of one row takes (2\*128) + (2\*1) CLK\_IN periods. The maximum frame rate is reduced with a factor of 2 compared to 16 channels mode.

Figure 37:

Output Timing in 8 Channels Mode

#### 4 Output Channels:

When only 4 LVDS output channels are used, the read-out of one row takes (4\*128) + (4\*1) CLK\_IN periods. The maximum frame rate is reduce with a factor of 4 compared to 16 channels mode.

Figure 38:

Output Timing in 4 Channels Mode

#### 2 Output Channels:

When only 2 LVDS output channels are used, the read-out of one row takes (8\*128) + (8\*1) CLK\_IN periods. The maximum frame rate is reduced with a factor of 8 compared to 16 channels mode.

Figure 39:

Output Timing in 2 Channels Mode

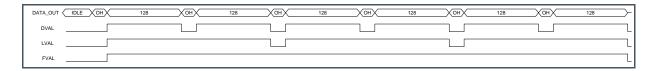

#### 12-Bit Mode:

In 12-bit mode, the analog-to-digital conversion takes 4x longer to complete. This causes the frame rate to drop to 70 fps when 480 MHz is used for LVDS\_CLK\_N/P. Due to this extra conversion time,

the sensor automatically multiplexes to 4 outputs when 12-bit is used. To simplify the figures below, the timing for only one LVDS channel is shown in every case.

For simplification, the timing for only one LVDS channel is shown in every case in the following paragraphs:

- 4 Output Channels

- 2 Output Channels

#### 4 Output Channels:

By default, the CMV2000 uses only 4 LVDS output channels in 12-bit mode. This means that the readout of one row takes (4\*128) + (4\*1) CLK\_IN periods.

#### Figure 40:

**Output Timing in 4 Channels Mode**

#### 2 Output Channels:

When only 2 LVDS output channels are used, the read-out of one row takes (8\*128) + (8\*1) CLK\_IN periods. The maximum frame rate is reduced with a factor of 2 compared to 4 channels mode.

#### Figure 41:

**Output Timing in 2 Channels Mode**

#### 6.3.4 Pixel Remapping

Depending on the number of output channels, the pixels are read out by different channels and come out at a different moment in time. With the details from the next chapters, the end user is able to remap the pixel values at the output to their correct image array location.

#### 16 Outputs

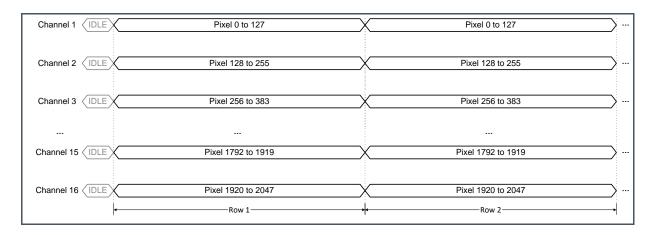

Figure 42 shows the location of the image pixels versus the output channel of the image sensor.

16 bursts of 128 pixels happen in parallel on the data outputs. This means that one complete row is read out in one burst. The amount of rows that will be read out depends on the value in the corresponding register. By default there are 1088 rows being read out.

Figure 42: Pixel Remapping for 16 Output Channels

#### 8 Outputs

When only 8 outputs are used, the pixel data is placed on the outputs as detailed in Figure 43. 8 bursts of 128 pixels happen in parallel on the data outputs. This means that one complete row is read out in two bursts. The time needed to read out one row is doubled compared to when 16 outputs are used. Channel 2, 4, 6...16 are not being used in this mode, so they can be turned off by setting the correct bits in the register with addresses 80-82. Turning off these channels will reduce the power consumption of the chip.

The amount of rows that will be read out can be set in the register. By default 1088 rows are read out.

Figure 43: Pixel Remapping for 8 Output Channels

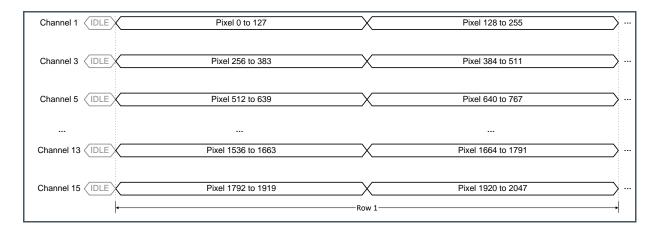

#### 4 Outputs

When only 4 outputs are used, the pixel data is placed on the outputs as detailed Figure 44. 4 bursts of 128 pixels happen in parallel on the data outputs. This means that one complete row is read out in four bursts. The time needed to read out one row is 4x longer compared to when 16 outputs are used. Only channel 1, 5, 9 and 13 are being used in this mode, so the remaining channels can be turned off by setting the correct bits in the register with addresses 80-82. Turning off these channels will reduce the power consumption of the chip.

The amount of rows that will be read out can be set in the register. By default there are 1088 rows being read out.

Figure 44:

Pixel Remapping for 4 Output Channels

| Channel 1 (IDLE) | Pixel 0 to 127     | Pixel 128 to 255   | Pixel 256 to 383   | Pixel 384 to 511   |

|------------------|--------------------|--------------------|--------------------|--------------------|

|                  |                    |                    |                    |                    |

| Channel 5 (IDLE) | Pixel 512 to 639   | Pixel 640 to 767   | Pixel 768 to 895   | Pixel 896 to 1023  |

| Channel 9 IDLE   | Pixel 1024 to 1151 | Pixel 1152 to 1279 | Pixel 1280 to 1407 | Pixel 1408 to 1535 |

|                  |                    |                    |                    |                    |

| Channel 13 IDLE  | Pixel 1536 to 1663 | Pixel 1664 to 1791 | Pixel 1792 to 1919 | Pixel 1920 to 2047 |

|                  |                    | — Ro               | w 1                | 1                  |

#### 2 Outputs

When only 2 outputs are used, the pixel data is placed on the outputs as detailed in Figure 45. 2 bursts of 128 pixels happen in parallel on the data outputs. This means that one complete row is read out in 8 bursts. The time needed to read out one row is 8x longer compared to when 16 outputs are used. Only channels 1 and 9 are being used in this mode, so the remaining channels can be turned off by setting the correct bits in the register with addresses 80-82. Turning off these channels will reduce the power consumption of the chip.

The amount of rows that will be read out can be set in the register. By default 1088 rows are read out.

Figure 45: Pixel Remapping for 2 Output Channels

#### Overview

All outputs are always used to send data, but if you use less than 16 channels, some channels will have duplicate data. For example if you multiplex to 4 channels, outputs 6, 7 and 8 will have identical data as output 5.

Figure 46 shows an overview of which channel data is on which output at a certain output mode.

Figure 46:

Overview Channel Data – Output Mode

| MUX<br>to | OUT<br>1 | OUT<br>2 | OUT<br>3 | OUT<br>4 | OUT<br>5 | OUT<br>6 | OUT<br>7 | OUT<br>8 | OUT<br>9 | OUT<br>10 | OUT<br>11 | OUT<br>12 | OUT<br>13 | OUT<br>14 | OUT<br>15 | OUT<br>16 |

|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 16        | CH1      | CH2      | CH3      | CH4      | CH5      | CH6      | CH7      | CH8      | CH9      | CH10      | CH11      | CH12      | CH13      | CH14      | CH15      | CH16      |

| 8         | CH1      | CH1      | СНЗ      | СНЗ      | CH5      | CH5      | CH7      | CH7      | CH9      | CH9       | CH11      | CH11      | CH13      | CH13      | CH15      | CH15      |

| 4         | CH1      | CH1      | CH1      | CH1      | CH5      | CH5      | CH5      | CH5      | CH9      | CH9       | CH9       | CH9       | CH13      | CH13      | CH13      | CH13      |

| 2         | CH1      | CH9      | CH9       | CH9       | CH9       | CH9       | CH9       | CH9       | CH9       |

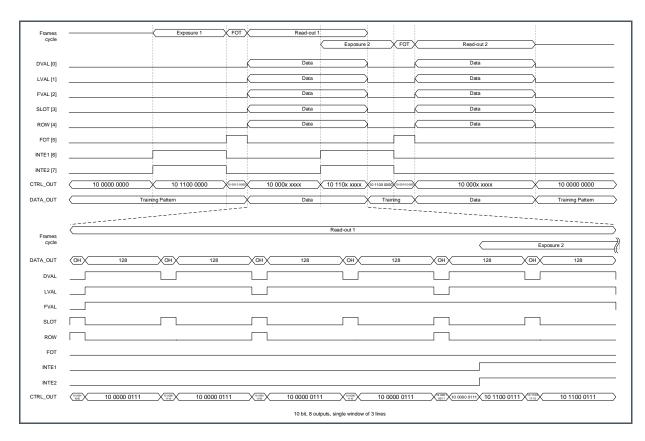

#### 6.3.5 Control Channel

The CMV2000 has one LVDS output channel dedicated for the valid data synchronization and timing of the output channels. The end user must use this channel to know when valid image data or training data is available on the data output channels.

The control channel transfers status information in 10-bit or 12-bit word format. Every bit of the word has a specific function. Next table describes the function of the individual bits, but only the DVAL, LVAL and FVAL signal are necessary to know when to sample the image data.

Figure 47: Function of the Individual Bits

| Bit  | Function | Description                                                                           |

|------|----------|---------------------------------------------------------------------------------------|

| [0]  | DVAL     | Indicates valid pixel data on the outputs                                             |

| [1]  | LVAL     | Indicates validity of the read-out of a row                                           |

| [2]  | FVAL     | Indicates the validity of the read-out of a frame                                     |

| [3]  | SLOT     | Indicates the overhead period before 128-pixel bursts (*)                             |

| [4]  | ROW      | Indicates the overhead period before the read-out of a row <sup>(1)</sup>             |

| [5]  | FOT      | Indicates when the sensor is in FOT (sampling of image data in pixels) <sup>(1)</sup> |

| [6]  | INTE1    | Indicates when pixels of integration block 1 are integrating <sup>(1)</sup>           |

| [7]  | INTE2    | Indicates when pixels of integration block 2 are integrating <sup>(1)</sup>           |

| [8]  | '0'      | Constant zero                                                                         |

| [9]  | '1'      | Constant one                                                                          |

| [10] | '0'      | Constant zero                                                                         |

| [11] | '0'      | Constant zero                                                                         |

(1) The status bits are purely informational. These bits are not required to know when the data is valid. The DVAL, LVAL and FVAL signals are sufficient to know when to sample the image data.

INTE1/2 will be low when FOT is high, so the exposure during the small 0.43\*reg73 overlap (see formulas in 6.4.1), will not be visible in the INTE1/2 bits.

Pins H2 (TDIG1) and G2 (TDIG2) can be programmed to map the state of control channel bits [0] (DVAL), [1] (LVAL), [2] (FVAL), [6] (INTE1) or [7] (INTE2) with registers 108 (T\_dig1) and 109 (T\_dig2).

Figure 48: Register 108/109 Value

| Register 108/109 Value | TDIG1 | TDIG2 |

|------------------------|-------|-------|

| 0                      | INTE1 | INTE1 |

| 1                      | INTE2 | INTE2 |

| 2                      | DVAL  | DVAL  |

| 3                      | LVAL  | LVAL  |

| 4                      | FVAL  | FVAL  |

### **DVAL, LVAL, FVAL**

The first three bits of the control word must be used to identify valid data and the read-out status.

Figure 49 shows the timing of the DVAL, LVAL and FVAL bits of the control channel with an example of the read-out of a frame of 3 rows (default is 1088 rows). This example uses the default mode of 16 outputs in 10-bit mode.

Figure 49: DVAL, LVAL and FVAL Timing in 16 Outputs Mode

When only 8 outputs are used, the line read-out time is 2x longer. The control channel takes this into account and the timing in this mode are shown in Figure 50 and Figure 51. The timing extrapolates identically for 4 and 2 outputs.

Figure 50: DVAL, LVAL and FVAL Timing in 8 Outputs Mode

Figure 51:

Detailed Timings of the Control Channel (8 outputs, 3 lines window)

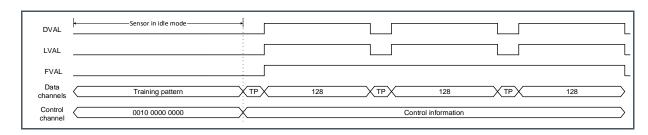

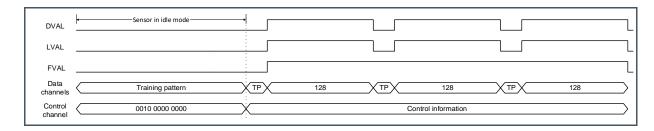

## 6.3.6 Training Data

To synchronize the receiving side with the LVDS outputs of the CMV2000, a known data pattern can be put on the output channels. This pattern "trains" the LVDS receiver of the surrounding system to achieve correct word alignment of the image data. This training pattern is put on all 16 output channels when no valid image data is being sent, even in between bursts of 128 pixels. The training pattern is a 10-bit or 12-bit word that replaces the pixel data. The sensor has a 12-bit sequencer register (address 78-79) that can be used to change the contents of the 12-bit training pattern.

The control channel does not send a training pattern, because it is used to send control information at all time. Word alignment can be done on this channel when the sensor is idle (not exposing or sending

image data). In this case all bits of the control word are zero, except for bit [9] (= 0010 0000 0000 or 512 decimal).

Figure 52 shows the location of the training pattern (TP) on the data channels when the sensor is idle and when reading out 3 rows. The default mode of 16 outputs is selected.

Figure 52:

Training Pattern Location in the Data and Control Channels.

# 6.4 Configuring Exposure and Readout

This section explains how the CMV2000 can be programmed using the on-board sequencer registers.

## 6.4.1 Exposure Modes

The exposure time can be programmed in two ways, externally or internally. Externally, the exposure time is defined as the time between the rising edge of T\_EXP1 and the rising edge of FRAME\_REQ (see External Exposure Time for more details). Internally, the exposure time is set by uploading the desired value to the corresponding sequencer register.

Figure 53:

Time Settings of Exposure Mode

| Register Name | Register Address              | Default Value | Description of the Value                                                                                               |

|---------------|-------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------|

| Exp_ext       | 41[0]                         | 0             | O: Value in Exp_time register defines exposure time  1: Time between T_EXP1 and FRAME_REQ pulses defines exposure time |

| Exp_time      | 42[7:0]<br>43[7:0]<br>44[7:0] | 2048          | If Exp_ext = 0: Defines the exposure time according to the following formula:                                          |

|               |                               |               | $129*clk\_per(0.43*fot\_length + Exp\_time)$                                                                           |

|               |                               |               | Where clk_per is the period of the master input clock and fot_length is the value in register 73.                      |

|               |                               |               | <u>If Exp_ext = 1:</u>                                                                                                 |

|               |                               |               | The exposure time is:                                                                                                  |

|               |                               |               | 129 * clk_per(0.43 * fot_length)<br>+ external exposure time                                                           |

|               |                               |               | Where external exposure time is the time between T_EXP1 and FRAME_REQ.                                                 |

To calculate back from actual exposure time to the register value for internal exposure can use the following formula (exposure time and clk\_per should have the same time unit):

$$Exp\_time = \frac{exposure\ time}{129*clk\_per} - 0.43*fot\_length$$

For very short integration times, the fot\_length should be lowered to 5 and the maximum clock speed should be used. In internal exposure mode, the shortest exposure time is limited by the exp\_time register, when this is set to 1, the shortest exposure time is  $14.24 \, \mu s$ , or  $8.47 \, \mu s$  for fot\_length = 5.

In external exposure mode, the time between T\_EXP1 and FRAME\_REQ can be as short as one clock cycle, reducing the shortest exposure time even more to  $11.58 \mu s$ , or  $5.80 \mu s$  for fot\_length = 5.

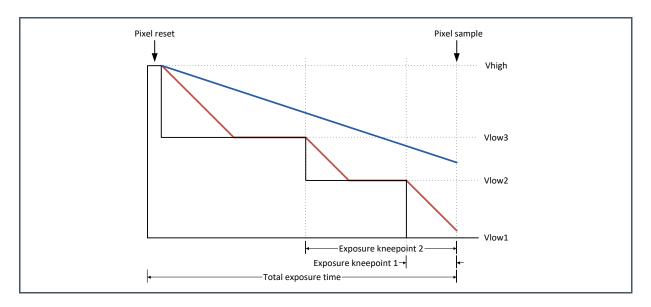

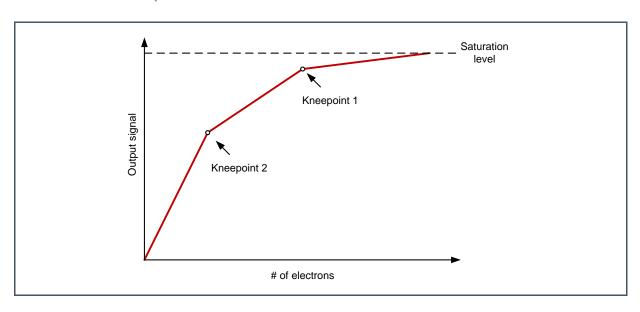

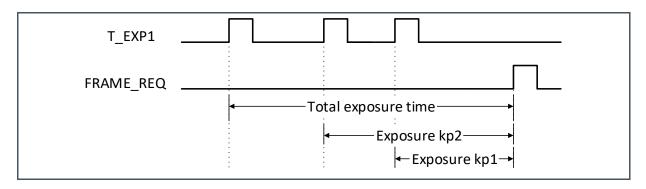

### 6.4.2 High Dynamic Range Modes

The sensor has different ways to achieve high optical dynamic range in the grabbed image.

- Interleaved read-out: the odd and even rows have a different exposure time.

- Piecewise linear response: pixels respond to light with a piecewise linear response curve.

- Multi-frame read-out: Different frames are read-out with increasing exposure time.

All the HDR modes mentioned above can be used in both the internal and external exposure time mode.

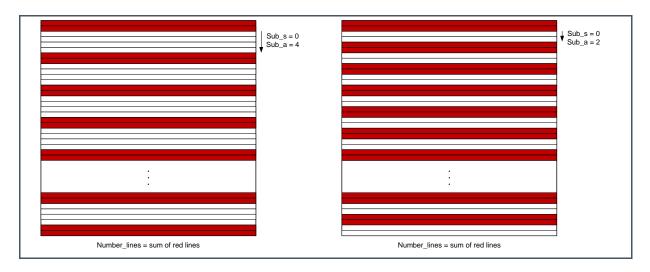

#### Interleaved Read-Out

In this HDR mode, the odd and even rows of the image sensors will have a different exposure time. This mode can be enabled by setting the register Exp\_dual.

Figure 54: Interleaved Read-Out – HDR Mode Enabling

| Register Name | Register Address | Default Value | Description of the Value                                                                             |

|---------------|------------------|---------------|------------------------------------------------------------------------------------------------------|

| Exp_dual      | 41[1]            | 0             | <ul><li>0: Interleaved exposure mode disabled</li><li>1: Interleaved exposure mode enabled</li></ul> |

The surrounding system can combine the image of the odd rows with the image of the even rows which results in a high dynamic range image. In this image, very bright and very dark objects are made visible without clipping. The Figure 55 gives an overview of the registers involved in the interleaved read-out when the internal exposure mode is selected.

Figure 55: Interleaved Read-Out – HDR Mode Timing

| Register<br>Name | Register<br>Address           | Default<br>Value                                       | Description of the Value                                                                                                                |

|------------------|-------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|